第7章 Nios II常用外设编程

- 格式:pdf

- 大小:392.90 KB

- 文档页数:23

第1节并行输入/输出内核并行输入/输出(PIO)内核提供了Avalon存储器映射从端口和通用IO端口直接的接口。

I/O端口连接到片内的用户逻辑或是连到与FPGA片外设备相连的引脚上。

PIO内核提供对用户逻辑或外部设备简单的I/O访问,应用实例如下:∙控制LED∙获取开关数据∙控制显示设备∙配置并与片外设备通信,例如专用标准产品(ASSP)的设备。

PIO内核可以基于输入信号而发出中断请求 (IRQ) 输出。

SOPC Builder 中提供了现成的 PIO内核,可以很容易地将PIO内核集成到SOPC Builder生成的系统中。

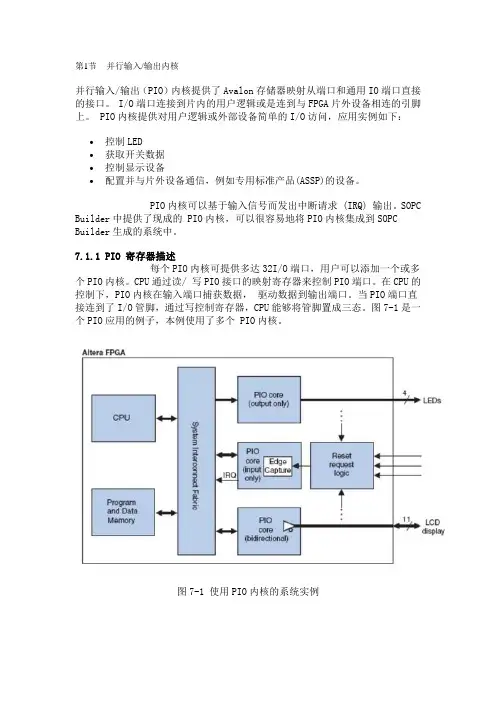

7.1.1 PIO 寄存器描述每个PIO内核可提供多达32I/O端口,用户可以添加一个或多个PIO内核。

CPU通过读/ 写PIO接口的映射寄存器来控制PIO端口。

在CPU的控制下,PIO内核在输入端口捕获数据,驱动数据到输出端口。

当PIO端口直接连到了I/O管脚,通过写控制寄存器,CPU能够将管脚置成三态。

图7-1是一个PIO应用的例子,本例使用了多个 PIO内核。

图7-1 使用PIO内核的系统实例当集成到SOPC Builder生成的系统中,PIO内核有两个特性对用户是可见的。

∙具有四个寄存器的存储器映射的寄存器空间,4个寄存器是data、direction、 interruptmask和edgecapture。

∙1到32个的I/O端口。

有些寄存器在某些硬件配置下不是必需的,这时相应的寄存器就不存在了。

对一个不存在的寄存器进行读操作,则返回一个未定义的值;一个不存在寄存器进行写操作则没有任何结果。

表7-1给出了PIO寄存器的描述。

1. 数据寄存器(Data Input & Output)PIO内核I/O端口可以连接到片上或片外的逻辑。

内核可以配置成仅有输入端口,或仅有输出端口,或两者都有。

如果内核用于控制设备上的双向I/O 管脚,内核提供具有三态控制的双向模式。

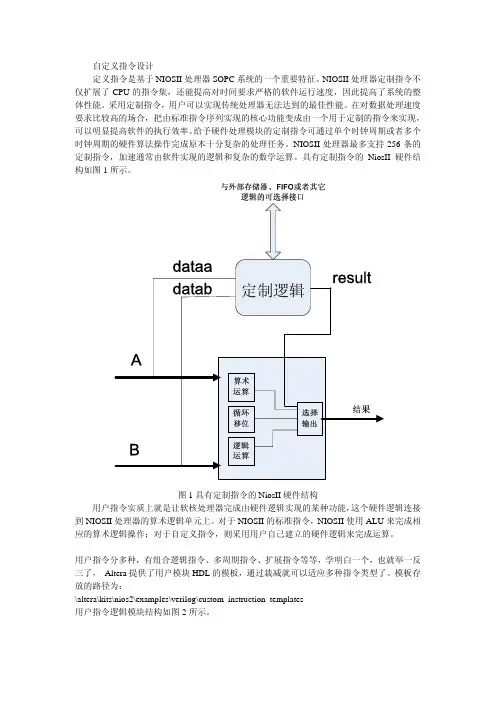

自定义指令设计定义指令是基于NIOSII处理器SOPC系统的一个重要特征。

NIOSII处理器定制指令不仅扩展了CPU的指令集,还能提高对时间要求严格的软件运行速度,因此提高了系统的整体性能。

采用定制指令,用户可以实现传统处理器无法达到的最佳性能。

在对数据处理速度要求比较高的场合,把由标准指令序列实现的核心功能变成由一个用于定制的指令来实现,可以明显提高软件的执行效率。

给予硬件处理模块的定制指令可通过单个时钟周期或者多个时钟周期的硬件算法操作完成原本十分复杂的处理任务。

NIOSII处理器最多支持256条的定制指令,加速通常由软件实现的逻辑和复杂的数学运算。

具有定制指令的NiosII硬件结构如图1所示。

图1具有定制指令的NiosII硬件结构用户指令实质上就是让软核处理器完成由硬件逻辑实现的某种功能,这个硬件逻辑连接到NIOSII处理器的算术逻辑单元上。

对于NIOSII的标准指令,NIOSII使用ALU来完成相应的算术逻辑操作;对于自定义指令,则采用用户自己建立的硬件逻辑来完成运算。

用户指令分多种,有组合逻辑指令、多周期指令、扩展指令等等,学明白一个,也就举一反三了, Altera提供了用户模块HDL的模板,通过裁减就可以适应多种指令类型了。

模板存放的路径为:\altera\kits\nios2\examples\verilog\custom_instruction_templates用户指令逻辑模块结构如图2所示。

z图2 用户指令逻辑结构例子:// Verilog Custom Instruction Template File for Combinatorial Logicmodule ci_nand(dataa, // Operand A (always required)datab, // Operand B (optional)result // result (always required));//INPUTSinput [31:0] dataa;input [31:0] datab;//OUTPUTSoutput [31:0] result;// custom instruction logic (note: no external interfaces are allowed in combinatorial logic)assign result = ~(dataa&datab);endmodule#include "stdio.h"#include "system.h"#include "sys/alt_timestamp.h"#include "alt_types.h"int main(void){alt_u32 time1,time2;alt_u32 a,b,c;a = 0xff00ff00;b = 0xf0f0f0f0;if (alt_timestamp_start() < 0){ //开启时间标记服务printf("Can't Start Timestamp...\n");}time1 = alt_timestamp(); //测试时间点1c = ALT_CI_CI_NAND(a,b); //通过宏使用定制指令time2 = alt_timestamp(); //测试时间点2printf("The Instruction ci_nand runs %ld\n",time2-time1);printf("c = %x\n",c);time1 = alt_timestamp(); //测试时间点1c = ~(a&b); //通过NiosII指令实现与非功能time2 = alt_timestamp(); //测试时间点2printf("The ~(a&b) runs %ld\n",time2-time1);printf("c = %x\n",c);return 0;}在生成的system.h文件中,关于CRC自定义指令的宏如下:#define ALT_CI_CI_NAND_N 0x00000000#define ALT_CI_CI_NAND(A,B) __builtin_custom_inii(ALT_CI_CI_NAND_N,(A),(B))。

NIOS II 软件开发手册本文仅限于个人学习使用版权所有编辑:DiDy2006-11-29Email:wedidy@目录第一部分 Nios II软件的发展 (4)第一章概述 (4)1.1引言 (4)1.2 Nios II简介 (4)1.3开发环境 (4)1.4第三方支持 (5)1.5第一代Nios处理器的移植 (6)第二章 Niso II IDE (7)引言 (7)Nios II IDE 工作台 (7)建立新的工程 (7)组建并编辑工程: (9)运行和调试程序 (10)编辑Flash (13)帮助系统 (14)第二部分 HAL系统库 (16)第三章 HAL系统库简介 (16)引言 (16)开始设计 (16)HAL的结构 (16)第四章使用HAL进行程序开发 (19)引言: (19)Nios II IDE工程结构 (19)System.h系统说明文件 (20)数据宽度和HAL类型定义 (20)UNIX风格的接口 (21)文件系统 (22)使用字符模式器件 (23)使用定时器器件 (24)使用Flash器件 (26)使用DMA器件 (30)缩减代码 (34)引导程序序列和入口 (36)存储器的使用 (37)HAL系统库文件路径 (41)第一部分 Nios II软件的发展这一部分主要介绍Nios II软件发展的相关信息。

包括以下两章:第一章 概述第二章 Nios II IDE 简介第一章概述1.1引言这一章从较高的角度为Nios II软件开发人员总体介绍Nios II处理器。

对Nios II软件的开发环境,用户可以使用的工具和相应的设计过程进行讲解。

1.2 Nios II简介基于Nios II处理器同使用其他微处理器的软件设计相似。

最简单有效的方法是从Altera公司购买一套开发工具,其中包括相应的文档,开发板和编写Nios II程序相应的开发工具。

Nios II软件开发者手册是针对那些对Nios II处理器有一定了解的用户。

最小的Nios2系统前言2003年Altera推出了第一代32位Nios系统,开创了FPGA内构建高性能单片机的先河。

随之2004年,Nios系统升级为Nios2系统,解决了软硬件开发中一些不方便的问题,软件开发环境从命令行编译转移到Eclips的IDE集成开放环境。

Nios2开发环境从1.0、1.1到1.2逐步升级。

后来为了和QuartusII软件升级同步,从QuartusII5.0版本开始Nios2的版本号正式和QuartusII统一。

作者我亲身经历过整个Nios2发展历程,深知Nios2的不同版本发生的巨大变化。

目前网上流行的Nios2教程针对的版本相对较老,已经对初学者学习Nios2起不到指导作用,并且应广大爱好者的强烈要求,我在此使用QuartusII和Nios2的8.0版本详细叙述Nios2的开发流程。

构建一个Nios2最小系统需要什么构建一个Nios2最小系统需要具备以下资源:★ Nios2软核处理器★ 内存★ Jtag_uart调试接口软核处理器:这就是Nios2处理器的核心CPU,所有的外1. Nios2设都是和这个CPU通过Avalon总线连接到一起的。

2. 内存:编译后的程序代码需要通过下载线下载到该内存中,然后CPU的程序指针跳转到内存的首地址开始执行程序。

3. Jtag_uart调试接口:想要用单步调试等调试功能控制程序执行和查看程序变量,那么就需要这个调试接口。

开始构建一个再简单不过的Nios2工程整个步骤由2部分组成,第一部分建立Nios2硬件SOPC工程,第二部分建立Nios2软件工程。

1.建立Nios2硬件SOPC工程建立Nios2硬件SOPC工程就是设计一个软核CPU和它的外设,编译成硬件电路放到FPGA芯片里面。

这时候可以认为FPGA就是一个32位的单片机了,下面的软件开发都是针对这个单片机的。

打开QuartusII软件,新建一个工程选择EP2C8Q208C8芯片。

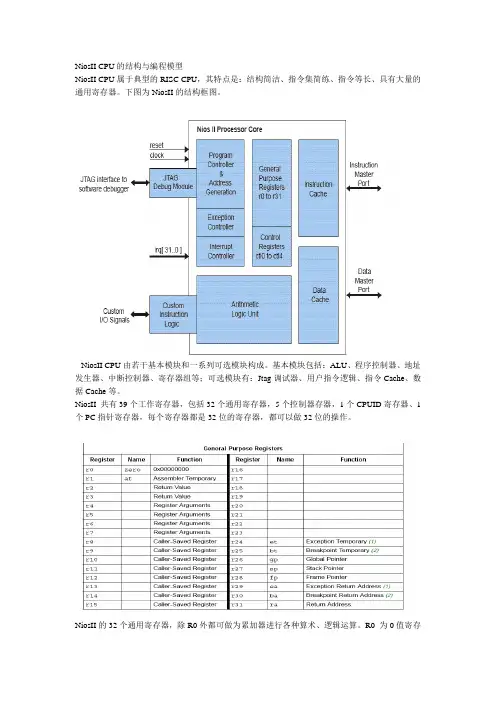

NiosII CPU的结构与编程模型NiosII CPU属于典型的RISC CPU,其特点是:结构简洁、指令集简练、指令等长、具有大量的通用寄存器。

下图为NiosII的结构框图。

NiosII CPU由若干基本模块和一系列可选模块构成。

基本模块包括:ALU、程序控制器、地址发生器、中断控制器、寄存器组等;可选模块有:Jtag调试器、用户指令逻辑、指令Cache、数据Cache等。

NiosII 共有39个工作寄存器,包括32个通用寄存器,5个控制器存器,1个CPUID寄存器、1个PC指针寄存器,每个寄存器都是32位的寄存器,都可以做32位的操作。

NiosII的32个通用寄存器,除R0外都可做为累加器进行各种算术、逻辑运算。

R0 为0值寄存器,对其进行读操作返回值是0,写操作对其没有影响,这一寄存器在指令集中有特殊的应用。

R24是中断处理程序专用寄存器,它是给中断处理程序专用的,虽然在用户程序中许访问,但不要用来保存数据,因为其中数据有可能被中断处理程序覆盖掉。

同样,R25是调试代理专用寄存器,也不要在用户程序中使用。

R29是PC指针的中断堆栈寄存器,当有中断发生时,这一寄存器用来保留一个返回地址,以便从中断处理程序返回到被中断的程序。

R30是PC指针的断点堆栈寄存器,用于系统调试。

当程序运行过程中遇到断点,这一寄存器中保留一个返回地址,以便从调试代理程序返回。

R31是PC指针的调用堆栈,用于子程序调用。

执行子程序调用指令时,这一寄存器中保留返回地址,以便从子程序返回。

R26、R27、R28在C开发系统中付予了一些特殊的应用,其中R27被作堆栈指针。

NiosII 有5个控制寄存器和一个CPUID寄存器。

Ctl0是程序状态字,目前只有BIT0、BIT1两位是有效的,高30位保留。

BIT0是全局中断控制位,用于中断的全局管理,1为允许,0为禁止。

BIT1是工作模式控制位。

当这一位为1时,系统工作于用户模式,当其为0时,系统工作于管理模式。

NIOSII教程NIOS II 是一种基于软核的处理器,可用于 FPGA 设计中。

它是由Altera 公司所开发的。

NIOS II 可以在 FPGA 中进行快速原型设计,并且具有高度可配置性和可扩展性。

本文将介绍 NIOS II 的基本架构和使用方法。

NIOSII架构基于RISC架构,它是一个32位的处理器,并且具有可选的指令扩展。

它的流水线深度可以根据设计的需求进行配置,以实现不同的性能要求。

NIOSII支持多种功能,包括硬件中断、异常处理以及浮点运算等。

在开始使用NIOSII进行开发之前,首先要进行软核处理器的配置。

配置包括选择所需的指令集、流水线深度和其他性能参数。

配置完成后,可以将软核处理器添加到FPGA设计中。

一旦软核处理器被添加到FPGA设计中,就可以开始编写应用程序。

NIOSII支持标准的C/C++语法,并且还提供了一些特殊的函数和指令,用于访问FPGA的硬件资源。

例如,可以使用特殊函数来配置GPIO引脚、读取和写入存储器以及执行其他与硬件交互的操作。

使用NIOSII进行FPGA开发具有许多优点。

首先,它提供了一种快速原型设计的方法,可以大大加快开发进程。

其次,NIOSII的可扩展性和高度可配置性使得它适用于各种不同的FPGA设计需求。

最后,NIOSII的开发工具和调试接口使得开发和调试过程更加简单和高效。

总结起来,NIOS II 是一种基于软核的处理器,适用于 FPGA 设计中。

它具有灵活性和可配置性,可以使用 C/C++ 或 HDL 进行开发,并通过Altera 公司提供的工具链进行编译和调试。

NIOS II 提供了一种快速原型设计的方法,并且适用于各种不同的 FPGA 设计需求。

NIOS II S沧1、。

沧2、 minio@yeah址net minio@yeah址net沧沧NIOS II :1. LED_ PIO_BASE个个 SOPC PIO(Parallel I/O)( Avalon Modules -> Other , LED_PIO, PIO_0IOWR_ALTERA_AVALON_PIO_DATA(LED_PIO_BASE, led); 1. sopc PIO LED_PIO ;2. hello_led.c LED_PIO_BASE #define LED_PIO_BASE 0x00001800 SOPC .2. NIOSII PIO个个 hello_led.c IOIOWR_ALTERA_AVALON_PIO_DATA(LED_PIO_BASE, led);altera_avalon_pio_regs.hi nclude#define IORD_ALTERA_AVALON_PIO_DATA(base) IORD(base, 0)#define IOWR_ALTERA_AVALON_PIO_DATA(base, data) IOWR(base, 0, data)NIOSII i nclude IORD/IOWR PIOsmallsoftwarehello_led_0_syslibDebugsystem_des cription system.h, :#define LED_PIO_TYPE "altera_avalon_pio"#define LED_PIO_BASE 0x00004000LED_PIO_BASE IO 0x00004000 SOPCBuilder !( SopcBuilder NiosII , system.h IDE !)IOWR(0x00004000, 0, led);IOWR_ALTERA_AVALON_PIO_DATA(LED_PIO_BASE, led); , , !3. :Linking hello_world_0.elf.../cygdrive/e/DE2Project_restored/software/hello_world_0_syslib/Debug/libhello_world_0_syslib.a(alt_main.o)(.text+0x60): In function `alt_main':/cygdrive/c/altera/72/nios2eds/components/altera_hal/HAL/src/alt_main.c:163: undefined reference to `main'collect2: ld returned 1 exit statusmake: *** [hello_world_0.elf] Error 1Build completed in 1.953 seconds: .int main(void), int mian()!!!!!!4.IOWR_ALTERA_AVALON_PIO_DATA ?:IOWR_ALTERA_AVALON_PIO_DATA altera_avalon_pio_regs.h io.h NiosII IDE NiosII Cache IO ( IOWR_ PIO IORD_ PIO )LED_PIO_BASE system.h LED_PIOIOWR_ALTERA_AVALON_PIO_DATA(LED_PIO_BASE,led) LED_PIO ledAltera_embeded_peripherals PIONiosII_software_developer's_handbook AlteraNIOS_II :<stdio.h> "system.h"system.h HALIDE “altera_avalon_pio_regs.h ” I/O.IOWR_ALTERA_AVALON_PIO_DATA(LED_PIO_BASE, led)led LED_PIO_BASE I/O led LEDFPGA “alt_types.h”alt_8 8alt_u8 8alt_16 16alt_u16 16alt_32 32alt_u32 32IOWR_ALTERA_AVALON_PIO_IRQ_MASK(BUTTON_PIO_BASE,0xf);IOWR_ALTERA_AVALON_PIO_EDGE_CAP(BUTTON_PIO_BASE,0x0);IORD_ALTERA_AVALON_PIO_EDGE_CAP(BUTTON_PIO_BASE)alt_irq_register(BUTTON_PIO_IRQ,edge_capture_ptr,handle_button_interrupts)"altera_avalon_pio_regs.h"#define IOWR_ALTERA_AVALON_PIO_IRQ_MASK(base,data)IOWR(base,2,data)#define IOWR_ALTERA_AVALON_PIO_EDGE_CAP(base,data)IOWR(base,3,data)#define IORD_ALTERA_AVALON_PIO_EDGE_CAP(base)IORD(base,3)0xf 0x73alt_irq_register ISR IRS extern int alt_irq_register(alt_u32 id,void*context,void(*irq_handler)(void*,alt_u32));handle_button_interrupts init_button_pio():1.#include "system.h"#include "altera_avalon_pio_regs.h"#include "alt_types.h"#include "stdio.h"#include "unistd.h"int main (void) __attribute__ ((weak, alias ("alt_main")));int alt_main (void){unsigned char led = 0;while (1){for(led=0;led<8;led++){IOWR_ALTERA_AVALON_PIO_DATA(LED_GREEN_BASE, 1<<led);usleep(500000); // 0.5}}return 0;}2.count_binary.h#ifndef COUNT_BINARY_H_#define COUNT_BINARY_H_#include "alt_types.h"#include <stdio.h>#include <unistd.h>#include "system.h"#include "sys/alt_irq.h"#include "altera_avalon_pio_regs.h" #define ESC 27#define ESC_TOP_LEFT "[1;0H"#define ESC_COL2_INDENT5 "[2;5H" #define ESC_CLEAR "K"#define ECS_COL1_INDENT5 "[1;5H" #endif /*COUNT_BINARY_H_*/main.c :#include "count_binary.h"int main(void){int i;int data;while(1){i=0;data=0x80;for(i=0;i<8;i++){IOWR(LED_GREEN_BASE,0,data);data>>=1;usleep(500000);}}}/*:IOWR(BASE, REGNUM, DATA)BASE REGNUM DATAREGNUM*/3.count_binary.hmain.c/*:DE24 4 ( ,4 ) */#include "count_binary.h"int alt_main(){int key,data;data=0x00;while(1){key=IORD(BUTTON_PIO_BASE,0);if(key==0x7)data=0x80;key=IORD(BUTTON_PIO_BASE,0);if(key==0xb)data=0x40;key=IORD(BUTTON_PIO_BASE,0);if(key==0xd)data=0x20;key=IORD(BUTTON_PIO_BASE,0);if(key==0xe)data=0x10;IOWR(LED_GREEN_BASE,0,data);}}/*IOIORD(BASE, REGNUM)BASE REGNUMBASE REGNUM*/:, ptf , DE2 , !4./*:DE2*/#include "count_binary.h"volatile int edge_capture;/* ( , )*/static void handle_button_interrupts(void *context,alt_u32 id);/* */static void init_button_pio(){void *edge_capture_ptr=(void*)&edge_capture;/* ( )*/IOWR_ALTERA_AVALON_PIO_IRQ_MASK(BUTTON_PIO_BASE,0xf);/* */IOWR_ALTERA_AVALON_PIO_EDGE_CAP(BUTTON_PIO_BASE,0x0);/* */alt_irq_register(BUTTON_PIO_IRQ,edge_capture_ptr,handle_button_interrupts); }/* */int main(void){init_button_pio();while(1){switch(edge_capture){/* 3 8 1*/case 0x08:IOWR(SEG7_DISPLAY_BASE,0,0x11111111);break;case 0x04:IOWR(SEG7_DISPLAY_BASE,0,0X22222222);break;case 0x02:IOWR(SEG7_DISPLAY_BASE,0,0X33333333);break;/* 0 8 4*/case 0x01:IOWR(SEG7_DISPLAY_BASE,0,0x44444444);break;}}}/* */static void handle_button_interrupts(void *context,alt_u32 id) {volatile int * edge_capture_ptr=(volatile int *)context;/* */*edge_capture_ptr=IORD_ALTERA_AVALON_PIO_EDGE_CAP(BUTTON_PIO_BASE);/* */IOWR_ALTERA_AVALON_PIO_EDGE_CAP(BUTTON_PIO_BASE,0);}5.#include "count_binary.h"int alt_main(){int second=0;while(1){usleep(100000);second++;IOWR(SEG7_DISPLAY_BASE,0,second);}}6.1602lcd.h#ifndef LCD_H_#define LCD_H_#define lcd_write_cmd(base,data) IOWR(base,0,data)#define lcd_read_cmd(base) IORD(base,1)#define lcd_write_data(base,data) IOWR(base,2,data) #define lcd_read_data(base) IORD(base,3)void lcd_init();void lcd_show_text(char * text);void lcd_line2();void lcd_test();#endif /*LCD_H_*/main.c/* :DE2* :quaters II 7.2,NIOS II 7.2* :1602*/#include <unistd.h>#include <string.h>#include <io.h>#include "system.h"#include "lcd.h"void lcd_init(){/* 8 , */lcd_write_cmd(LCD_16207_0_BASE,0X38);usleep(2000);/* , */lcd_write_cmd(LCD_16207_0_BASE,0X0C);usleep(2000);/* */lcd_write_cmd(LCD_16207_0_BASE,0X01);usleep(2000);/* , */lcd_write_cmd(LCD_16207_0_BASE,0X06);usleep(2000);/* */lcd_write_cmd(LCD_16207_0_BASE,0X80);usleep(2000);}/* */void lcd_show_text(char * text){int i;for(i=0;i<strlen(text);i++){lcd_write_data(LCD_16207_0_BASE,text[i]);usleep(2000);}}void lcd_line1(){lcd_write_cmd(LCD_16207_0_BASE,0X80);usleep(2000);}/* , */void lcd_line2(){lcd_write_cmd(LCD_16207_0_BASE,0XC0);usleep(2000);}int main(){char text1[16]="Wu Qin De Shi";char text2[16]="Jie,Wu Qin De Ni";lcd_init();//while(1){/* */lcd_line1();/* */lcd_show_text(text1);/* */lcd_line2();/* */lcd_show_text(text2);usleep(4000000);lcd_write_cmd(LCD_16207_0_BASE,0X01);//usleep(2000);/* */lcd_line1();lcd_show_text("Liu Ya Li,");lcd_line2();/* */lcd_show_text("I Love You!");usleep(4000000);}return 0;}7.1602 NIOS II fprintf/* :DE2* :quaters II 7.2,NIOS II 7.2* :1602* NIOS II fprintf lcd !*/#include <unistd.h>#include <stdio.h>#include <string.h>#include <io.h>#include "system.h"int main(void){FILE *lcd;lcd=fopen("/dev/lcd_16207_0","w");/*1602 */fprintf(lcd,"I love NIOS II!\n");/*1602 */fprintf(lcd,"I love you!");fclose(lcd);return 0;}8.count_binary.h#ifndef COUNT_BINARY_H_#define COUNT_BINARY_H_#include "alt_types.h"#include <stdio.h>#include <unistd.h>#include "system.h"#include "sys/alt_irq.h"#include "altera_avalon_pio_regs.h"#define ESC 27#define ESC_TOP_LEFT "[1;0H"#define ESC_COL2_INDENT5 "[2;5H"#define ESC_CLEAR "K"#define ECS_COL1_INDENT5 "[1;5H"#endif /*COUNT_BINARY_H_*/main.c#include "count_binary.h"static alt_u8 count;volatile int edge_capture;#ifdef BUTTON_PIO_BASEstatic void handle_button_interrupts(void *context,alt_u32 id){volatile int *edge_capture_ptr=(volatile int *)context;*edge_capture_ptr=IORD_ALTERA_AVALON_PIO_EDGE_CAP(BUTTON_PIO_BASE);IOWR_ALTERA_AVALON_PIO_EDGE_CAP(BUTTON_PIO_BASE,0);}static void init_button_pio(){void *edge_capture_ptr=(void *)&edge_capture;IOWR_ALTERA_AVALON_PIO_IRQ_MASK(BUTTON_PIO_BASE,0XF);IOWR_ALTERA_AVALON_PIO_EDGE_CAP(BUTTON_PIO_BASE,0X0);alt_irq_register(BUTTON_PIO_IRQ,edge_capture_ptr,handle_button_interrupts);}#endif#ifdef SEG7_DISPLAY_BASEstatic void sevenseg_set_hex(int hex){static alt_u8 segments[16]={0x81,0xcf,0x92,0x86,0xcc,0xa4,0xa0,0x8f,0x80,0x84, 0x88,0xe0,0xf2,0xc2,0xb0,0xb8};unsigned int data=segments[hex&15]|(segments[(hex>>4)&15]<<8);IOWR_ALTERA_AVALON_PIO_DATA(SEG7_DISPLAY_BASE,data);}#endifstatic void lcd_init(FILE *lcd){fprintf(lcd,"%c%s Counting will be displayed below...",ESC,ESC_TOP_LEFT);}static void initial_message(){}static void count_led(){#ifdef LED_RED_BASEIOWR_ALTERA_AVALON_PIO_DATA(LED_RED_BASE,count);#endif}static void count_sevenseg(){#ifdef SEG7_DISPLAY_BASEsevenseg_set_hex(count);#endif}static void count_lcd(void *arg){FILE *lcd=(FILE*)arg;fprintf(lcd,"%c%s 0x%x\n",ESC,ESC_COL2_INDENT5,count); }static void count_all(void *arg){count_led();count_sevenseg();count_lcd(arg);printf("%02x, ",count);}static void handle_button_press(alt_u8 type,FILE *lcd){if(type=='c'){switch(edge_capture){case 0x1:count_led();break;case 0x2:count_sevenseg();break;case 0x4:count_lcd(lcd);break;case 0x8:count_all(lcd);break;default:count_all(lcd);break;}}}int main(void){int i;int wait_time;FILE *lcd;count=0;lcd=fopen("/dev/lcd_16207_0","w");#ifdef BUTTON_PIO_BASE//init_button_pio();init_button_pio();#endifinitial_message();while(1){usleep(100000);if(edge_capture!=0){handle_button_press('c',lcd);}else{count_all(lcd);}if(count==0xff){fprintf(lcd,"%c%s Waiting...\n",ESC,ESC_TOP_LEFT,ESC,ESC_CLEAR, ESC,ESC_COL2_INDENT5);edge_capture=0;fprintf(lcd,"%c%s",ESC,ESC_COL2_INDENT5,ESC,ESC_CLEAR);wait_time=0;for(i=0;i<70;++i){wait_time=i/10;fprintf(lcd,"%c%s",ESC,ESC_COL2_INDENT5,wait_time);if(edge_capture!=0){handle_button_press('w',lcd);usleep(100000);}}initial_message();lcd_init(lcd);}count++;}fclose(lcd);return(0);}9. 1 +#include <stdio.h>#include <sys/unistd.h>#include <io.h>#include <string.h>#include "system.h"#include "altera_avalon_pio_regs.h"#include "altera_avalon_timer_regs.h"#include "alt_types.h"#include "sys/alt_irq.h"static void timer1_init(void); //int i = 0;/* */int main(void){// Timertimer1_init();while(1);return 0;}/* 1 */static void ISR_timer1(void *context, alt_u32 id){// 8 LEDIOWR_ALTERA_AVALON_PIO_DATA(LED_GREEN_BASE, 1<<i);i++;if(i == 8)i = 0;// TimerIOWR_ALTERA_AVALON_TIMER_STATUS(TIMER_1_BASE, 0x00);}/* 1 */void timer1_init(void) //{// Timer1IOWR_ALTERA_AVALON_TIMER_STATUS(TIMER_1_BASE, 0x00);// Timer1 T=25000000/5000000=0.5s// 16IOWR_ALTERA_AVALON_TIMER_PERIODL(TIMER_1_BASE,25000000);// 16IOWR_ALTERA_AVALON_TIMER_PERIODH(TIMER_1_BASE,25000000 >> 16);//Timer1IOWR_ALTERA_AVALON_TIMER_CONTROL(TIMER_1_BASE, 0x07);// Timer1alt_irq_register(TIMER_1_IRQ, (void *)TIMER_1_BASE, ISR_timer1);}10. 1+#include <stdio.h>#include <sys/unistd.h>#include <io.h>#include <string.h>#include "system.h"#include "altera_avalon_pio_regs.h"#include "altera_avalon_timer_regs.h"#include "alt_types.h"#include "sys/alt_irq.h"static void timer1_init(void); //unsigned long int i = 0;/* */int main(void){// Timertimer1_init();while(1);return 0;}/* 1 */static void ISR_timer1(void *context, alt_u32 id){// 8 7IOWR(SEG7_DISPLAY_BASE,0,i);i++;// TimerIOWR_ALTERA_AVALON_TIMER_STATUS(TIMER_1_BASE, 0x00);}/* 1 */void timer1_init(void) //{// Timer1IOWR_ALTERA_AVALON_TIMER_STATUS(TIMER_1_BASE, 0x00);// Timer1 T=25000000/5000000=0.5s// 16IOWR_ALTERA_AVALON_TIMER_PERIODL(TIMER_1_BASE,25000000);// 16IOWR_ALTERA_AVALON_TIMER_PERIODH(TIMER_1_BASE,25000000 >> 16);//Timer1IOWR_ALTERA_AVALON_TIMER_CONTROL(TIMER_1_BASE, 0x07);// Timer1alt_irq_register(TIMER_1_IRQ, (void *)TIMER_1_BASE, ISR_timer1);}11. 1 2+ +/* :DE2* :NIOS II7.2,QUATERS II 7.2* 1* 2 1* */#include <stdio.h>#include <sys/unistd.h>#include <io.h>#include <string.h>#include "system.h"#include "altera_avalon_pio_regs.h"#include "altera_avalon_timer_regs.h"#include "alt_types.h"#include "sys/alt_irq.h"/* : DE2 system.h TIMER_0 TIMER_1** system.h* #define TIMER_0_BASE 0x00681020* #define TIMER_0_IRQ 3* #define TIMER_1_BASE 0x00681040* #define TIMER_1_IRQ 4* :*/#define TIMER1_IRQ 3#define TIMER2_IRQ 4#define TIMER1_BASE 0x00681020#define TIMER2_BASE 0x00681040static void timer_init(void); //int i = 0,j = 0,flag;alt_u32 timer_prd[4] = {5000000, 10000000, 50000000, 100000000};// //T1 0.1s,0.2s,1s,2sint main(void){// Timertimer_init();while(1);return 0;}static void ISR_timer1(void *context, alt_u32 id){// 8 LEDIOWR(LED_GREEN_BASE,0,i);//IOWR(SEG7_DISPLAY_BASE,0,i);i++;if(i == 255)i = 0;// TimerIOWR_ALTERA_AVALON_TIMER_STATUS(TIMER1_BASE, 0x00);}/* 2 1 */static void ISR_timer2(void *context, alt_u32 id){// 1 T1=timer_prd[j]/50M( : )IOWR_ALTERA_AVALON_TIMER_PERIODL(TIMER1_BASE, timer_prd[j]);IOWR_ALTERA_AVALON_TIMER_PERIODH(TIMER1_BASE, timer_prd[j] >> 16);//IOWR_ALTERA_AVALON_TIMER_CONTROL(TIMER1_BASE, 0x07);//if(j == 0)flag = 0;if(j == 3)flag = 1;if(flag == 0){j++;}else{j--;}//IOWR_ALTERA_AVALON_TIMER_STATUS(TIMER2_BASE, 0);}void timer_init(void) //{// Timer1IOWR_ALTERA_AVALON_TIMER_STATUS(TIMER1_BASE, 0x00);// Timer1IOWR_ALTERA_AVALON_TIMER_PERIODL(TIMER1_BASE,80000000);IOWR_ALTERA_AVALON_TIMER_PERIODH(TIMER1_BASE, 80000000 >> 16);// Timer1IOWR_ALTERA_AVALON_TIMER_CONTROL(TIMER1_BASE, 0x07);// Timer1alt_irq_register(TIMER1_IRQ, (void *)TIMER1_BASE, ISR_timer1);// Timer2IOWR_ALTERA_AVALON_TIMER_STATUS(TIMER2_BASE, 0x00);// Timer2 T2=400M/50M=8s;IOWR_ALTERA_AVALON_TIMER_PERIODL(TIMER2_BASE,400000000);IOWR_ALTERA_AVALON_TIMER_PERIODH(TIMER2_BASE, 400000000 >> 16);// Timer2IOWR_ALTERA_AVALON_TIMER_CONTROL(TIMER2_BASE, 0x07);// Timer2alt_irq_register(TIMER2_IRQ, (void *)TIMER2_BASE, ISR_timer2);}12./* DE2* NIOS II 7.2,QUATERS II 7.2** 1. 1* 2. 0-9 9 0-9* *//* 115200*/#include "altera_avalon_uart_regs.h"#include "system.h"#include "altera_avalon_pio_regs.h"#include "alt_types.h"#include "sys/alt_irq.h"#include <stdio.h>#include <string.h>#define UART_BASE 0x00681000#define UART_IRQ 2#define TIME_DELAY 1000000//1M,//UARTvoid Uart_send(unsigned char data){alt_u16 status;status=IORD_ALTERA_AVALON_UART_STATUS(UART_BASE);while(!(status&0x0040))//status=IORD_ALTERA_AVALON_UART_STATUS(UART_BASE);IOWR_ALTERA_AVALON_UART_TXDATA(UART_BASE,data);}//UARTvoid Uart_send_n(unsigned char *ptr){while(*ptr){Uart_send(*ptr);ptr++;}Uart_send(0x0a);//}//UARTint Uart_receive(void){alt_u16 status;int temp;status=IORD_ALTERA_AVALON_UART_STATUS(UART_BASE);while(!(status&0x0080))//status=IORD_ALTERA_AVALON_UART_STATUS(UART_BASE);temp=IORD_ALTERA_AVALON_UART_RXDATA(UART_BASE);return temp;}//void Uart_ISR(void * context,alt_u32 id){unsigned char temp;temp=IORD_ALTERA_AVALON_UART_RXDATA(UART_BASE);switch(temp){case '0':IOWR(SEG7_DISPLAY_BASE,0,0x00000000);break;case '1':IOWR(SEG7_DISPLAY_BASE,0,0x11111111);break;case '2':IOWR(SEG7_DISPLAY_BASE,0,0x22222222);break;case '3':IOWR(SEG7_DISPLAY_BASE,0,0x33333333);break;case '4':IOWR(SEG7_DISPLAY_BASE,0,0x44444444);break;case '5':IOWR(SEG7_DISPLAY_BASE,0,0x55555555);break;case '6':IOWR(SEG7_DISPLAY_BASE,0,0x66666666);break;case '7':IOWR(SEG7_DISPLAY_BASE,0,0x77777777);break;case '8':IOWR(SEG7_DISPLAY_BASE,0,0x88888888);break;case '9':IOWR(SEG7_DISPLAY_BASE,0,0x99999999);break;}}//void Uart_init(){IOWR_ALTERA_AVALON_UART_CONTROL(UART_BASE, 0x80);// IOWR_ALTERA_AVALON_UART_STATUS(UART_BASE, 0x0);//// IOWR_ALTERA_AVALON_UART_RXDATA(UART_BASE, 0x0);// alt_irq_register(UART_IRQ,0,Uart_ISR);}int main(){Uart_init();while(1){Uart_send_n("Liu Ya Li,I love u!");//Uart_send_n(64);usleep(TIME_DELAY);//}}13. 1 2 timer0 timer1 timer2 2#define timer2#ifdef timer2#include <stdio.h>#include <sys/unistd.h>#include <io.h>#include <string.h>#include "system.h"#include "altera_avalon_pio_regs.h"#include "altera_avalon_timer_regs.h"#include "alt_types.h"#include "sys/alt_irq.h"//#define TIMER_2_BASE 0x01b02060//#define TIMER_2_IRQ 9static void timer2_init(void); //unsigned long int i = 0;/* */int main(void){// Timertimer2_init();while(1);return 0;}/* 2 */static void ISR_timer2(void *context, alt_u32 id){// 8 7IOWR(SEG7_DISPLAY_BASE,0,i);i++;// Timer2IOWR_ALTERA_AVALON_TIMER_STATUS(TIMER_2_BASE, 0x00);}/* 1 */void timer2_init(void) //{// Timer2IOWR_ALTERA_AVALON_TIMER_STATUS(TIMER_2_BASE, 0x00);// Timer2 T=1s// 16IOWR_ALTERA_AVALON_TIMER_PERIODL(TIMER_2_BASE,100000000);// 16IOWR_ALTERA_AVALON_TIMER_PERIODH(TIMER_2_BASE,100000000 >> 16);//Timer1IOWR_ALTERA_AVALON_TIMER_CONTROL(TIMER_2_BASE, 0x07);// Timer2alt_irq_register(TIMER_2_IRQ, (void *)TIMER_2_BASE, ISR_timer2);}#else#include <stdio.h>#include <sys/unistd.h>#include <io.h>#include <string.h>#include "system.h"#include "altera_avalon_pio_regs.h"#include "altera_avalon_timer_regs.h"#include "alt_types.h"#include "sys/alt_irq.h"static void timer1_init(void); // unsigned long int i = 0;/* */int main(void){// Timertimer1_init();while(1);return 0;}/* 1 */static void ISR_timer1(void *context, alt_u32 id) {// 8 7IOWR(SEG7_DISPLAY_BASE,0,i);i++;// TimerIOWR_ALTERA_AVALON_TIMER_STATUS(TIMER_1_BASE, 0x00);}/* 1 */void timer1_init(void) //{// Timer1IOWR_ALTERA_AVALON_TIMER_STATUS(TIMER_1_BASE, 0x00);// Timer1 T=1s// 16IOWR_ALTERA_AVALON_TIMER_PERIODL(TIMER_1_BASE,100000000);// 16IOWR_ALTERA_AVALON_TIMER_PERIODH(TIMER_1_BASE,100000000 >> 16);//Timer1IOWR_ALTERA_AVALON_TIMER_CONTROL(TIMER_1_BASE, 0x07);// Timer1alt_irq_register(TIMER_1_IRQ, (void *)TIMER_1_BASE, ISR_timer1);}#endif14. SDRAMmemestmemest (please type "man memset" in your shell)void *memset(void *s, int c, size_t n);memset:: c n .char a[20] , memset(a, 0, 20)memset(a, 20, 0): memset, , , : char buffer[20];memset(buffer, 0, sizeof((char)*20));strcpy(buffer, "123");memset . , .: memset, memsetint some_func(struct something *a){……memset(a, 0, sizeof(a));…}: memset ?memset( &Address, 0, sizeof(Address)):1. ()char buf[5]CString str,str1 //memset(buf,0,sizeof(buf)) for(int i = 0 i<5 i++) { str.Format(“%d “,buf[i]) str1 +=str } TRACE(“%s\r\n“,str1)2. 0 memset MessageBox 0 NULL:demo 1#include <iostream>#include <cstring>using namespace std;int main(){char a[5];memset(a,'1',5);for(int i = 0;i < 5;i++)cout<<a[i]<<" ";system("pause");return 0;}#include <stdio.h>//#include "../inc/sopc.h"#include "system.h"#include "string.h"#include "unistd.h"#include "altera_avalon_pio_regs.h"/* DE2 system.h SDRAM_0_BASE* #define SDRAM_0_BASE 0x00800000,*/#define SDRAM_BASE 0x00800000unsigned short * ram = (unsigned short *)(SDRAM_BASE+0x10000); //SDRAM int main(void){int i;memset(ram,0,100);// SDRAM// ram ram ram (SDRAM_BASE+0x10100) for(i=0;i<100;i++){*(ram++) = i;}// ramfor(i=0;i<100;i++){printf("%d\n",*(--ram));}for(i=100;i<200;i++){*(ram++) = i;}// ramfor(i=100;i<200;i++){IOWR(SEG7_DISPLAY_BASE,0,*(--ram));printf("%d\n",*(--ram));usleep(1000000);}return 0;}15. API#include "system.h"#define _LEDtypedef struct{unsigned long int DATA;unsigned long int DIRECTION;unsigned long int INTERRUPT_MASK;unsigned long int EDGE_CAPTURE;} PIO_STR;#ifdef _LED#define LED ((PIO_STR *)LED_GREEN_BASE)#endif#include "unistd.h"#include "stdio.h"unsigned int i=0;CPU NIOS II/f none CPU16. 1+ptf ptf/* DE2* QUATERS II 7.2,NIOS II 7.2* 2010.7.17* 8 1* 1 T=timer_1_period/50000000* */#include "system.h"#include "altera_avalon_pio_regs.h"#include "altera_avalon_timer_regs.h"#include "sys/alt_irq.h"#include <io.h>#define timer_1_period 50000#define uint unsigned int#define uchar unsigned charalt_u32 count=0;uchar seg_table[11]={0x40,0x79,0x24,0x30,0x19,0x12,0x02,0x78,0x00,0x10,0x7f};void isr_timer_1();/* 1 */void timer_1_init(){/* 1 */IOWR_ALTERA_AVALON_TIMER_STATUS(TIMER_1_BASE,0X00);/* 16 */IOWR_ALTERA_AVALON_TIMER_PERIODL(TIMER_1_BASE,timer_1_period);/* 16 */IOWR_ALTERA_AVALON_TIMER_PERIODH(TIMER_1_BASE,timer_1_period>>16);/* 1 */IOWR_ALTERA_AVALON_TIMER_CONTROL(TIMER_1_BASE,0X07);/* 1 */alt_irq_register(TIMER_1_IRQ, (void *)TIMER_1_BASE, isr_timer_1);}/* 1 */void isr_timer_1(){count++;/* 1 */IOWR_ALTERA_AVALON_TIMER_STATUS(TIMER_1_BASE,0X00);}/* */void seg_display(alt_u32 z){if(z<10){IOWR(SEG0_DISPLAY_BASE,0,seg_table[z%10]);IOWR(SEG1_DISPLAY_BASE,0,seg_table[10]);IOWR(SEG2_DISPLAY_BASE,0,seg_table[10]);IOWR(SEG3_DISPLAY_BASE,0,seg_table[10]);IOWR(SEG4_DISPLAY_BASE,0,seg_table[10]);IOWR(SEG5_DISPLAY_BASE,0,seg_table[10]);IOWR(SEG6_DISPLAY_BASE,0,seg_table[10]);IOWR(SEG7_DISPLAY_BASE,0,seg_table[10]);}else if(z<100){IOWR(SEG0_DISPLAY_BASE,0,seg_table[z%10]);IOWR(SEG1_DISPLAY_BASE,0,seg_table[z%100/10]);IOWR(SEG2_DISPLAY_BASE,0,seg_table[10]);IOWR(SEG3_DISPLAY_BASE,0,seg_table[10]);IOWR(SEG4_DISPLAY_BASE,0,seg_table[10]);IOWR(SEG5_DISPLAY_BASE,0,seg_table[10]);IOWR(SEG6_DISPLAY_BASE,0,seg_table[10]);IOWR(SEG7_DISPLAY_BASE,0,seg_table[10]);}else if(z<1000){IOWR(SEG0_DISPLAY_BASE,0,seg_table[z%10]);IOWR(SEG1_DISPLAY_BASE,0,seg_table[z%100/10]);IOWR(SEG2_DISPLAY_BASE,0,seg_table[z%1000/100]);IOWR(SEG3_DISPLAY_BASE,0,seg_table[10]);。

NIOS?II的SOPC中存储器型外设接口的设计0 引言随着微电子设计技术与工艺的发展,数字集成电路由最初的电子管、晶体管逐步发展成专用集成电路(ASIC,Application Specific IntegratedCircuit),同时可编程逻辑器件也取得了长足进步。

如今,可完成超大规模的复杂组合逻辑与时序逻辑的FPGA器件不断推陈出新,从而为实现片上可编程系统(SOPC)提供了强大的硬件支持。

SOPC是Ahera公司提出的一种灵活、高效的片上系统(SOC)解决方案,它将处理器、存储器、I/O口等系统设计所需要的功能模块集成到一个可编程器件上,从而构成一个可编程的片上系统。

同时,Altera公司也提供了完整的开发套件(QuaItus II、SOPC Builder、Nios II IDE)和仿真工具等软件,并将其无缝地集成在一起。

利用Quartus II的SOPC Builder能够方便的构建一个基于FPGA 的SOPC系统,SOPC Builder的系统库中包含了一些常用的Nios II 外围设备,可以自动生成Avalon总线,以用于连接各个模块,从而形成SOPC系统。

但系统库中没有提供的器件,而需要用户根据器件的具体情况设计Avalon接口。

另外,对于一些没有逻辑功能的接口可以直接与总线相连,但需要根据Avalon总线规范和外设的控制时序来定制接口。

在实际工程中,通常可以使用的存储器有片上存储器和片外存储器,其中前者指的是FPGA内嵌的存储器,如片上RAM、FIFO、紧耦合存储器等;后者为FPGA片外存储器,如SRAM、SDRAM等。

本文介绍了将片内存储器FIFO、紧耦合存储器及16位的SRAM集成在SOPC系统中,并在FPGA开发板上实现的方法,其内容包括外设的接入方法,以及紧耦合存储器如何通过紧耦合从端口直接与处理器的紧耦合数据/指令主端口相连等。

1 SOPC中的Avalon总线Avalon交换式总线是由altera公司开发的一种专用的内部连线技术。

nios2课程设计一、课程目标知识目标:1. 理解Nios II处理器的核心概念和原理,掌握其基本架构和运作机制。

2. 学习并掌握基于Nios II处理器的嵌入式系统设计流程和方法。

3. 掌握Nios II处理器的编程技术,包括汇编语言和C语言的编程。

技能目标:1. 能够运用Nios II处理器设计简单的嵌入式系统,进行硬件描述和软件编程。

2. 能够运用Nios II处理器的开发工具进行系统仿真、调试和优化。

3. 能够分析并解决基于Nios II处理器的嵌入式系统问题,提高实际工程应用能力。

情感态度价值观目标:1. 培养学生对嵌入式系统设计和开发的兴趣,激发创新意识和探索精神。

2. 培养学生良好的团队合作精神和沟通能力,提高解决实际问题的自信心。

3. 增强学生对我国嵌入式产业发展的认识,树立为国家和民族科技事业做贡献的价值观。

课程性质分析:本课程为电子信息类专业课程,以实践性为主,注重培养学生的动手能力和实际应用能力。

学生特点分析:学生具备一定的电子技术和编程基础,对嵌入式系统有一定了解,但Nios II处理器相关知识掌握较少。

教学要求:结合学生特点,采用理论与实践相结合的教学方法,以项目驱动为导向,使学生在实践中掌握Nios II处理器的相关知识,提高嵌入式系统设计和开发能力。

通过课程学习,实现上述课程目标,为后续相关课程和实际工作打下坚实基础。

二、教学内容1. Nios II处理器概述:介绍Nios II处理器的背景、特点和应用领域,使学生对其有一个全面的了解。

教材章节:第一章2. Nios II处理器架构:讲解Nios II处理器的硬件架构、指令集和存储器结构等内容。

教材章节:第二章3. 嵌入式系统设计流程:介绍基于Nios II处理器的嵌入式系统设计流程,包括硬件描述、软件编程、系统集成和调试等。

教材章节:第三章4. Nios II处理器编程技术:学习Nios II处理器的编程方法,包括汇编语言和C语言的编程技巧。

NIOS ii 配置及例程使用教程本教程为nios ii在FPGA板上的配置入门教程,仅使用在xsyan设计制作EP2C5/EP2C8开发板上。

下面将会详细的说明如何使用nios ii在FPGA上配置一个altera公司提供的CPU,并利用这个CPU来调试和执行相应C程序。

并且,最后会有两个例程。

一,硬件要求:1,EP2C5/EP2C8开发板一块。

2,USB电源线一条。

3,并口线一条。

4,串口线一条。

二,软件要求:1,quartus II 7.0.2,MegaCore IP 7.0.3,Nios II EDS 7.0.三,主要步骤:1,在quartus上创建一个工程。

2,在此工程里面调用SOPC,并配置CPU。

3,创建cpu.4,定义FPGA引脚并综合。

5,调用NIOS,配置相应设置。

6,再次编译综合工程。

7,下载FPGA。

四,详细步骤:1,在quartus上创建一个工程。

a)打开quartus,选择File->New project wizard.b)在打开的窗口上选择Nextc)选择工程路径,并且指定工程名字。

d)添加文件,因为没有设计文档,所以跳过,直接Next。

e)选择器件,请根据自己的开发板选择EP2C5T144C8/ EP2C8T144C8f)然后直接点Finish,创建工程完毕。

2,用SOPC配置一个CPU。

a)在quartus里面调用SOPC。

b)在打开的SOPC里面,输入系统名字,选择HDL语言种类c)点确定后开始配置CPU,双击左边栏的Nios ii Processor.d)这里选择经济型,然后点Next,直到下个页面。

e)然后点finish,Process配置结束,双击UART,配置串口f)直接用默认配置,点Finish即可,然后双击on-chip-memory配置memory。

g)配置如上图配一个8K内部ram后点Finish,用来存放程序代码和初始化代码,然后继续创建memory用来存放变量,再创建两个4K内部ram,步骤同上。

矿产资源开发利用方案编写内容要求及审查大纲

矿产资源开发利用方案编写内容要求及《矿产资源开发利用方案》审查大纲一、概述

㈠矿区位置、隶属关系和企业性质。

如为改扩建矿山, 应说明矿山现状、

特点及存在的主要问题。

㈡编制依据

(1简述项目前期工作进展情况及与有关方面对项目的意向性协议情况。

(2 列出开发利用方案编制所依据的主要基础性资料的名称。

如经储量管理部门认定的矿区地质勘探报告、选矿试验报告、加工利用试验报告、工程地质初评资料、矿区水文资料和供水资料等。

对改、扩建矿山应有生产实际资料, 如矿山总平面现状图、矿床开拓系统图、采场现状图和主要采选设备清单等。

二、矿产品需求现状和预测

㈠该矿产在国内需求情况和市场供应情况

1、矿产品现状及加工利用趋向。

2、国内近、远期的需求量及主要销向预测。

㈡产品价格分析

1、国内矿产品价格现状。

2、矿产品价格稳定性及变化趋势。

三、矿产资源概况

㈠矿区总体概况

1、矿区总体规划情况。

2、矿区矿产资源概况。

3、该设计与矿区总体开发的关系。

㈡该设计项目的资源概况

1、矿床地质及构造特征。

2、矿床开采技术条件及水文地质条件。