TVP5150芯片寄存器设置

TVP5150主要信号引脚:

模拟输入:PAL制信号。

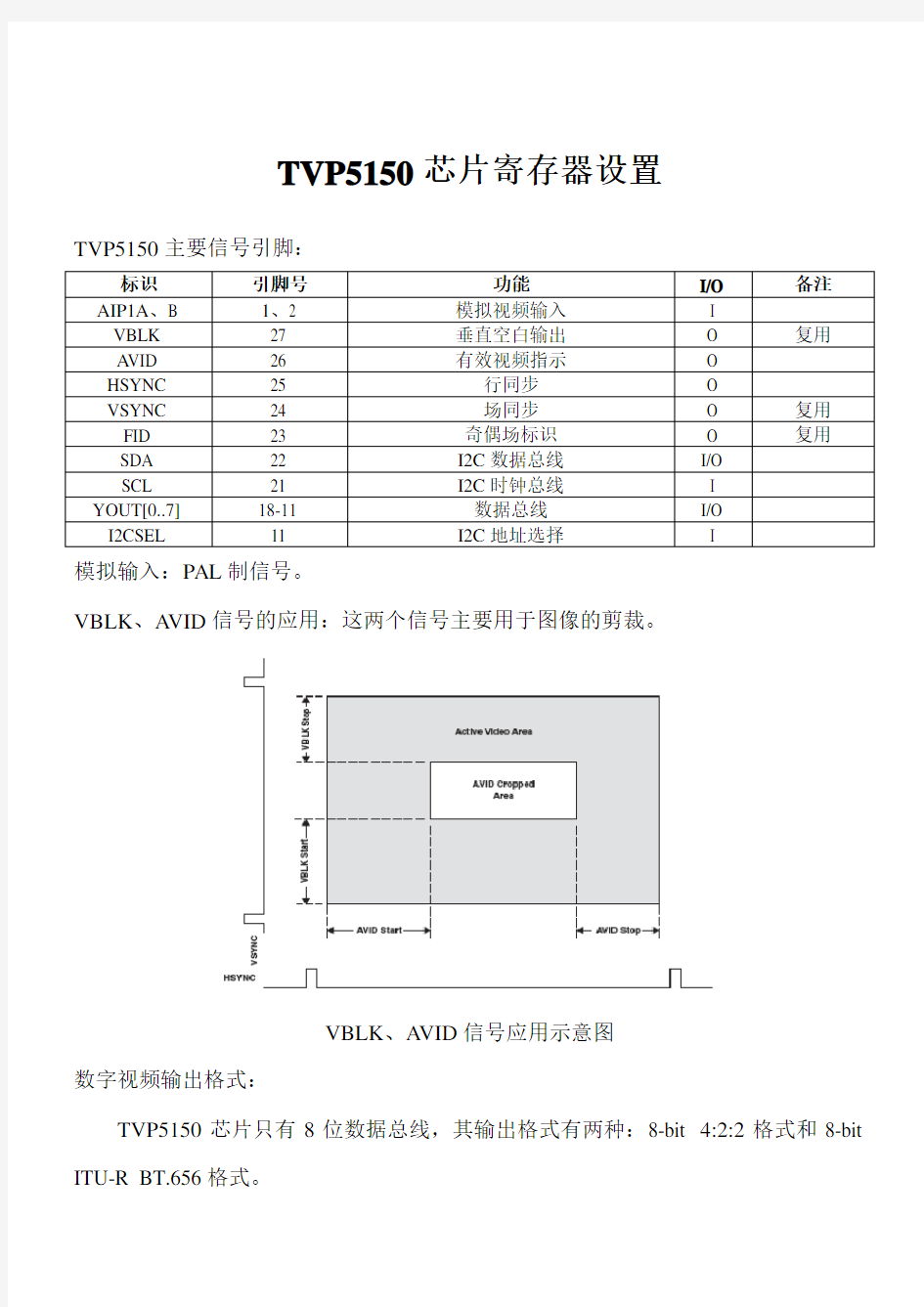

VBLK、A VID信号的应用:这两个信号主要用于图像的剪裁。

VBLK、A VID信号应用示意图

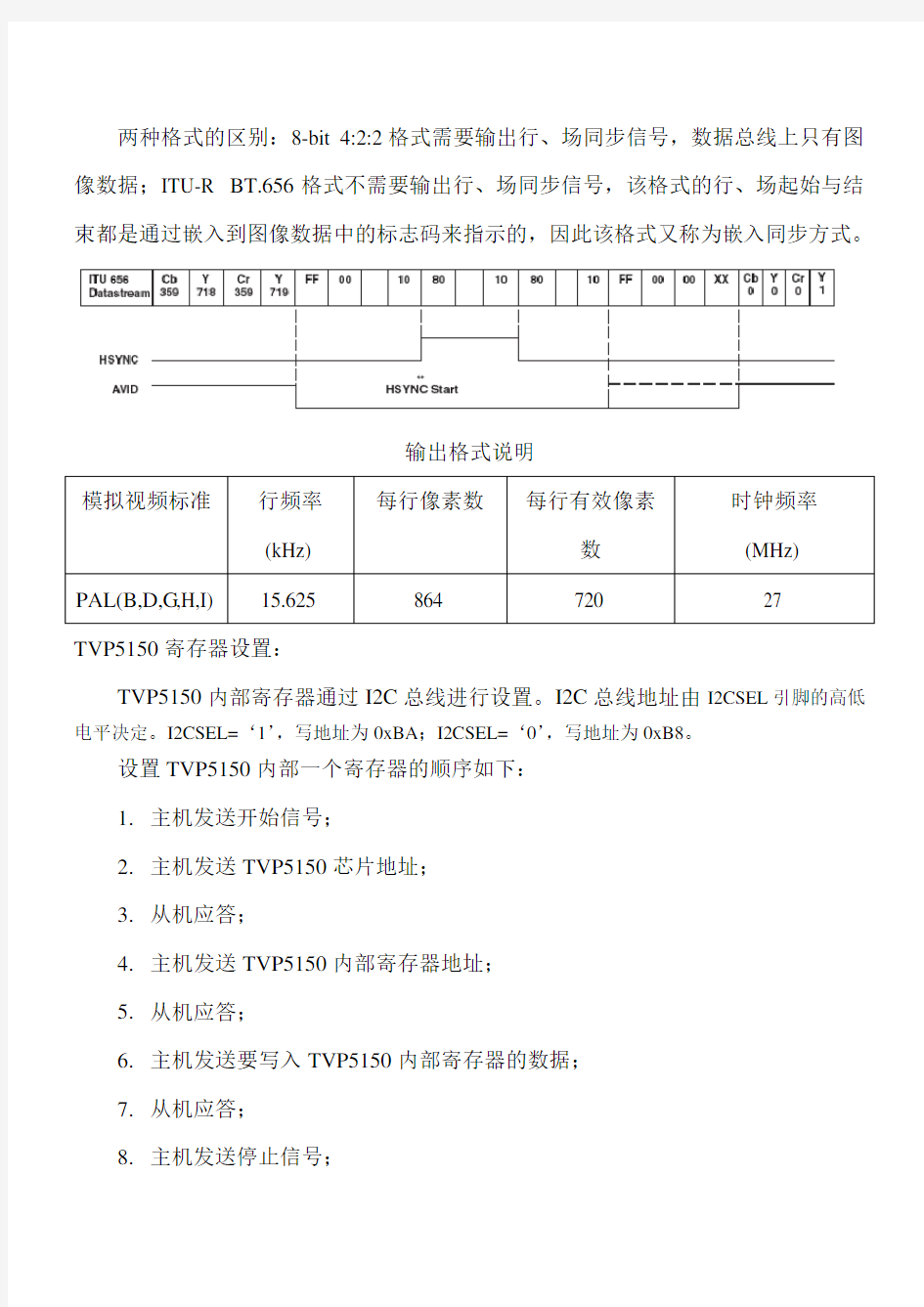

数字视频输出格式:

TVP5150芯片只有8位数据总线,其输出格式有两种:8-bit 4:2:2格式和8-bit ITU-R BT.656格式。

两种格式的区别:8-bit 4:2:2格式需要输出行、场同步信号,数据总线上只有图像数据;ITU-R BT.656格式不需要输出行、场同步信号,该格式的行、场起始与结束都是通过嵌入到图像数据中的标志码来指示的,因此该格式又称为嵌入同步方式。

输出格式说明

TVP5150寄存器设置:

TVP5150内部寄存器通过I2C总线进行设置。I2C总线地址由I2CSEL引脚的高低电平决定。I2CSEL=‘1’,写地址为0xBA;I2CSEL=‘0’,写地址为0xB8。

设置TVP5150内部一个寄存器的顺序如下:

1.主机发送开始信号;

2.主机发送TVP5150芯片地址;

3.从机应答;

4.主机发送TVP5150内部寄存器地址;

5.从机应答;

6.主机发送要写入TVP5150内部寄存器的数据;

7.从机应答;

8.主机发送停止信号;

注意:当向TVP5150内部地址为00h-8Fh的寄存器写入时,在上述第7、8步骤间TVP5150芯片需要一个延时,用以等待数据写入寄存器。有两种方法判断是否数据写入寄存器:1、完成第7步后检测SCL总线的状态,当SCL总线为高时表示数据已写入寄存器,执行第8步;2、完成第7步后,等待64uS后执行第8步。

常用寄存器设置说明:

1.视频输入源选择寄存器

寄存器地址:00h

默认值:00h

Bit0: 0=复合视频输入

1=S-video输入

Bit1: 0=选择AIP1A

1=选择AIP1B

Bit3: 0=正常操作

1=强制黑屏输出

2.杂项控制寄存器

寄存器地址:03h

默认值:01h

设置值:8Fh

Bit7:27引脚功能选择。

0=GPCL

1=VBLK

Bit6:GPCL输出值(该引脚是否是输出由该寄存器的bit5决定)。

0=输出0

1=输出1

Bit5:GPCL输出使能。

0=GPCL输出闲置

1=GPCL输出使能

Bit4:锁状态。

0=24引脚输出PAL指示信号,23引脚输出FID信号

1=24引脚输出PAL锁指示信号,23引脚输出场锁指示信号Bit3:数据总线输出使能

0=数据总线高阻

1=数据总线激活

Bit2:HSYNC、VSYNC、FID、A VID信号输出使能

0=HSYNC、VSYNC、FID、A VID信号输出高阻

1= HSYNC、VSYNC、FID、A VID信号输出使能

Bit1:场空白开/关

0=关

1=开

Bit0:时钟输出使能

0=高阻

1=使能

3.输出和数据比率选择寄存器

寄存器地址:0Dh

默认值:47h

设置值:40h

Bit6:YCbCr输出范围

0= ITU-R BT.601范围(Y值范围为16-235,U、V值范围为16-240) 1=扩展范围(1-254)

Bit5:CbCr值格式

0=补偿二进制

1=直接二进制

Bit4-3:YCbCr数据通路旁通

00=正常操作

01=Decimation filter的输出直接接到YCbCr输出引脚

10=数字化复合视频

11=保留

Bit2-0:YCbCr输出格式

000=带有外同步信号输出的8-bit 4:2:2格式

001-110=保留

111=ITU-R BT.656格式

4.配置复用引脚寄存器

寄存器地址:0Fh

默认值:08h

设置值:02h

Bit6:23引脚功能选择

0=FID

1=Lock indicator

Bit4:24引脚功能选择

0=PALI

1= Lock indicator

Bit3:23引脚功能选择

0=FID

1=GLCO

Bit2:24引脚功能选择

0=VSYNC

1=PALI

Bit1:27引脚功能选择

0=INTREQ

1=GPCL或者VBLK Bit0:输出时钟选择

0=2倍时钟(27MHz)

1=1倍时钟(13.5MHz)

课题9:寄存器的原理及应用 课型:讲授 教学目的: 掌握数码寄存器和移位寄存器的逻辑功能 教学重点:掌握中规模四位双向移位寄存器的逻辑功能 教学难点:掌握中规模四位双向移位寄存器的逻辑功能 复习、提问: 写出RS触发器、JK触发器、D触发器、T触发器、T`触发器的逻辑 功能、特性方程。 教学过程: 寄存器被广泛应用于数字系统和计算机中,它由触发器组成,是一种用来暂时存放二进制数码的逻辑部件。一个触发器可以存放一位二进制代码,因此n 位代码寄存器应由n个触发器组成。有些寄存器由门电路构成控制电路,以保证信号的接收和清除。 寄存器存放数据的方式有并行和串行两种。并行方式是数码从各对应输入端同时输入到寄存器中,串行方式是数码从一个输入端逐位输入到寄存器中。 寄存器取出数据的方式也有并行输出和串行输出两种。并行输出方式中,被取出的数码同时出现在各位的输出端。串行输出方式中,被取出的数码在一个输出端逐位出现。 寄存器分为数码寄存器和移位寄存器。 一、数码寄存器 数码寄存器具有存储二进制代码,并可输出所存二进制代码的功能。按接收数码的方式可分为:单拍式和双拍式。 单拍式:接收数据后直接把触发器置为相应的数据,不考虑初态。 双拍式:接收数据之前,先用复"0"脉冲把所有的触发器恢复为"0",第二拍把触发器置为接收的数据。 1、双拍工作方式的数码寄存器 双拍工作方式是指接收数码时,先清零,再接收数码。

分析下图四位数码寄存器逻辑图。它的核心部分是4个D 触发器。其工作过程: (1) 清零。CR=0,异步清零。即有:Q 3n+1Q 2n+1Q 1n+!Q 0n+1=0000 (2) 送数。CR=1时,CP 上升沿送数 Q 3n+1Q 2n+1Q 1n+!Q 0n+1=D 3D 2D 1 D 0 (3) 保持。在CR=1、CP 上升沿以外时间,寄存器内容将保持不变。实 现了数码寄存的功能。 2、单拍工作方式的数据寄存器 单拍工作方式是指只需一个接收脉冲就可以完成接收数码的工作方式。集成数码寄存器几乎都采用单拍工作方式。 数码寄存器要求所存的代码与输入代码相同,故由D 触发器构成。 分析下图D 触发器组成的4位数据寄存器的逻辑功能。 无论寄存器中原来的内容是什么,只要送数在控制时钟脉冲CP 上升沿到来时,加在并行数据输入端的数据D 0~D 3,就立即被送入进寄存器中,即有:Q 3n+1Q 2n+1Q 1n+!Q 0n+1=D 3D 2D 1D 0。 二、移位寄存器 移位寄存器具有数码寄存和移位两个功能,在移位脉冲的作用下,数码如向左移一位,则称为左移,反之称为右移。 移位寄存器具有单向移位功能的称为单向移位寄存器,即可向左移也可向右移的称为双向移位寄存器。 1、单向移位寄存器 (1)、右移寄存器

第29卷 第3期2006年9月 电子器件 Ch inese Jo urnal o f El ectro n D evices Vol.29 No.3Sep.2006 Driver Program Design for Video Decoder TVP5150Based on DM642 XU Zhi -wei ,M A Deng -j i ,L I NG Feng ,Z HU Shan -an ,H E Zheng -jun (College o f E lectr ica l Eng ineering ,Zhejiang Un iver sity ,H angz hou 310027,Ch ina ) A bstract :Aimed at embedded video surveillance sy stem co nsisted o f high -pow ered video pro cessing chip TM S320DM642and video decode r TVP5150of TI ,this paper intro duces the Class /Mini -Driver M odule of DM642,and designs the device driver prog rams for video capturing.Further mo re ,it provides the so lution of splitting -screen problem w hen DM 642is capturing video.This driver pro gram has been applied to the video surveillance sy stem and testing result indicate s that this prog ram runs stably.Key words :DM642;TVP5150;class /mini -driver m odule ;splitting -screen .EEACC :6140C 基于DM642的视频解码设备TVP5150驱动程序的设计 徐志伟,马登极,林 峰,朱善安,何正军 (浙江大学电气学院,杭州310027) 收稿日期:2005-10-13作者简介:马登极(1981-),男,河北人,工学硕士,主要从事嵌入式底层软件的研究,pony mdj @yaho o.co https://www.doczj.com/doc/ba5793899.html, ; 徐志伟(1978-),男,浙江富阳人工学硕士,主要从事嵌入式底层软件的研究。 摘 要:针对T I 推出的高端专用视频处理芯片T M S320D M 642和视频解码芯片T V P5150构建的嵌入式视频监控系统,介 绍了DM 642的类/微型驱动模型,在此基础上设计了视频采集底层设备驱动程序,并对DM 642在图像采集时产生的分屏现象提出了解决办法。本驱动程序已在视频监控系统中得到应用,运行稳定。 关键词: DM 642;T V P5150;类/微型驱动模型;分屏现象。中图分类号:O432.2;TP391.41文献标识码:B 文章编号:1005-9490(2006)03-0945-06 随着现代化图像处理技术的飞速发展,人们对图像采集系统的实时性和可靠性要求越来越高。嵌入式图像采集处理系统具有体积小、成本低、可靠性高、安装方便等优点,在交通、安防监控等领域都有广泛的应用。TMS320DM 642[1] 是TI (Texas In -strum ents )于2002年推出的一款高端专用视频处理芯片,由于它超强的单核处理性能,在视频领域将有非常广泛的应用,与之相应的外围视频设备也会越来越多。所以,为这些外围设备编写驱动程序已经成为依赖操作系统管理硬件设备的内在要求。 1 DM642系统整体构架和功能简介 如图1所示,DM 642有三个视频VPo rt 口,VP0和VP1与视频解码芯片相连作视频输入,V P2与视频编码芯片连接作视频输出。另外还有存储模 块,电源模块,网络模块等。VP0和V P1各被分成两个8bit 的视频输入接口,连接4片视频解码芯片,实现4路的视频采集功能。 图1 DM 642系统整体架构 2 视频解码芯片的选择和设计 目前被广泛使用的视频解码芯片是TI 推出的

74HC595是具有8位移位寄存器和一个存储器,三态输出功能。移位寄存器和存储器是分别的时钟。数据在SCHcp的上升沿输入,在STcp的上升沿进入的存储寄存器中去。如果两个时钟连在一起,则移位寄存器总是比存储寄存器早一个脉冲。移位寄存器有一个串行移位输入(Ds),和一个串行输出(Q7’),和一个异步的低电平复位,存储寄存器有一个并行8位的,具备三态的总线输出,当使能 OE时(为低电平),存储寄存器的数据输出到总线。74HC595各个引脚的功能:Q1~7 是并行数据输出口,即储寄存器的数据输出口Q7' 串行输出口,其应该接SPI总线的MISO接口STcp 存储寄存器的时钟脉冲输入口SHcp 移位寄存器的时钟脉冲输入口OE的非输出使能端MR的非芯片复位端Ds 串行数据输入端程序说明:每当spi_shcp上升沿到来时,spi_ds 引脚当前电平值在移位寄存器中左移一位,在下一个上升沿到来时移位寄存器中的所有位都会向左移一位,同时Q7'也会串行输出移位寄存器中高位的值,这样连续进行8次,就可以把数组中每一个数(8位的数)送到移位寄存器;然后当 spi_stcp上升沿到来时,移位寄存器的值将会被锁存到锁存器里,并从Q1~7引脚输出附子程序: void hc595send_data(uint8 data)//要传输的数据,建议用数组的方法来查询{ uint8 i; IO0CLR = spi_stcp; 12 脚 for(i=0;i<8;i++) { IO0CLR = spi_shcp; 11 脚 if((data&0x80)!=0)IO0SET = spi_ds; else IO0CLR = spi_ds; data <<= 1; IO0SET = spi_shcp; } IO0SET = spi_stcp;} 1 引言 单片机应用系统中使用的显示器主要有LED和LCD两种。近年来也有用CRT 显示的。前者价格低廉,配置灵活,与单片机接口方便;后者可进行图形显示,但接口较复杂,成本也较高。LED(Ling Emiting Diode)是发光二极管的缩写。实际应用非常普遍的是八段LED显示器。LED显示器在大型报时屏幕,银行利率显示,城市霓虹灯建设中,得到广泛应用。在这些需要多位LED显示的场合,怎样实现系统稳定,价格低廉的显示,成为决定其成本的关键所在。 2 74HC595实现LED静、动态显示基本原理 74HC595是美国国家半导体公司生产的通用移位寄存器芯片。并行输出端具有输出锁存功能。与单片机连接简单方便,只须三个I/O口即可。而且通过芯片的Q7引脚和SER引脚,可以级联。而且价格低廉,每片单价为1.5元左右. 2.1 静态显示 每位LED显示器段选线和74HC595的并行输出端相连,每一位可以独立显示。在同一时间里,每一位显示的字符可以各不相同(每一位由一个74HC595的并行输出口控制段选码)。 N位LED显示要求N个74HC595芯片及N+3条I/O口线,占用资源较多,而且成本较高。这对于多位LED显示很不利。 2.2 动态显示 在多位LED显示时,为了简化电路,降低成本,节省系统资源,将所有的N位段选码并联在一起,由一片74HC595控制。由于所有LED的段选码皆由一个74HC595并行输出口控制,因此,在每一瞬间,N位LED会显示相同的字符。想

成绩:计算机原理实验室实验报告 课程:计算机组成原理 姓名:李文周 专业:计算机科学与技术 学号:132054237 日期:2015.12 太原工业学院 计算机工程系

实验二:寄存器实验 实验环境PC机+Win7+74LS373+proteus仿真器实验日期2015.12一.实验内容 (1)基本内容 1.理解CPU运算器中寄存器的作用 2.设计并验证4位算数逻辑单元的功能 (2)扩展要求 1.实现更多的寄存器(至少8个)

二.理论分析或算法分析 74ls373是常用的地址锁存器芯片,它实质是一个是带三态缓冲输出的8D 触发器,在单片机系统中为了扩展外部存储器,通常需要一块74ls373芯片。74ls373工作原理简述: (1).1脚是输出使能(OE),是低电平有效,当1脚是高电平时,不管输入3、4、7、8、13、14、17、18如何,也不管11脚(锁存控制端,G)如何,输出2(Q0)、5(Q1)、6(Q2)、9(Q3)、12(Q4)、15(Q5)、16(Q6)、19(Q7)全部呈现高阻状态(或者叫浮空状态); (2).当1脚是低电平时,只要11脚(锁存控制端,G)上出现一个下降沿,输出2(Q0)、5(Q1)、6(Q2)、9(Q3)、12(Q4)、15(Q5)、16(Q6)、19(Q7)立即呈现输入脚3、4、7、8、13、14、17、18的状态.锁存端LE由高变低时,输出端8位信息被锁存,直到LE 端再次有效。当三态门使能信号OE为低电平时,三态门导通,允许Q0~Q7输出,OE为高电平时,输出悬空。

L——低电平;H——高电平;X——不定态;Q0——建立稳态前Q的电平;G——输入端,与8031ALE连高电平:畅通无阻低电平:关门锁存。图中OE——使能端,接地。当G=“1”时,74LS373输出端1Q—8Q与输入端1D—8D相同;当G 为下降沿时,将输入数据锁存。 三.实现方法(含实现思路、程序流程图、实验电路图和源程序列表等)

压片机 压片机主要用于制药工业的片剂工艺研究,其可以将颗粒状物压制成直径不大于13mm的圆形、异形和带有文字、符号,图形片状物的自动连续生产设备。压片机在制药生产过程中具有重要意义。 据了解,压片机在我国生产历史悠久,出口早,产量大,压片机制造商数量、品种规格,产量均位居世界前列。特别是近年来压片机制造企业开始重视产品质量,奉信“以质取胜”的经营理念,开发的压片机产品具有操作简单、清理方便快捷的特点。 进入21世纪,随着GMP认证的深入,完全符合GMP的ZP系列旋转式压片机相继出现。高速旋转式压片机在产量、压力信号采集、剔废等技术上有了长足的发展。另外,随着制造加工工艺水平、自动化控制技术的提高以及压片机使用厂家各种不同的特殊需求,各种特殊用途的压片机也相继出现。譬如,实验室用ZP5旋转式压片机、用于干粉压片的干粉旋转式压片机、用于药片剂的防爆型ZPYG51系列旋转式压片机等。 笔者获悉,针对单向压片机存在的裂片,片剂内部的密度不均匀等缺点,一种旋转式多冲双向压片机开始诞生。这种压片机上下冲同

时均匀地加压,使药物颗粒中的空气有充裕的时间逸出模孔,这提高了片剂密度的均匀性,减少了裂片现象。除此以外,旋转式压片机还具有机器振动小、噪声低、耗能少、效率高和压片重量准确等优点。 而高速旋转压片机则具有强迫供料机构,机器由PLC控制,有自动调节压力、控制片重、剔除废片、打印数据、显示故障停机等功能,除能控制片重差异在一定的范围内以外,对缺角、松裂片等质量问题能自动鉴别并能剔除。 如今我国压片机行业虽然取得了较大的成就,新产品也层出不穷,但是不得不承认的是,我国压片机技术含量较低、技术创新后力不足。真正技术水平高、附加值大的品种却寥寥无几。因此,面对医药市场需求的不断扩大,我国压片机企业还需不断进行技术创新,促进压片机设备向智能化方向发展。据了解,当前国外压片机技术发展的方向是智能化、柔性化、精密化。为推动压片机行业快速发展,更好的引用于制药生产等领域,我国压片机行业还需向国外高技术取经。

4.设BX=6D16H,AX=1100H,写出下列指令执行后BX 寄存器中的内容。 MOV CL,06H ROL AX,CL SHR BX,CL 解:第2条指令把AX 中内容循环左移6次,过程如下: CF AX ←---- ←-- ←-- | | ------------------------------------------------------------------------------------ 执行结果为AX=0100000000000100B=4004H,CF=0,第3条指令把BX 中内容逻辑右移6次,过程如下: BX-----→ CF 0----→ → 执行结果为BX=0000000110110100=01B4H,CF=0。 第二章 简答 11.有一双字87654321H 在内存中的地址是30101H ,画出其在8086系统中的内种存放的情况。 答:在8086系统中,双字在内存中连续4个字节,其中地位字节存于低地址,高位字节存于高地址如图: 30101H 30102H 30103H 30104H 第三章 简答 1.设下列程序段执行前,SS :SP 的值分别为1000H :2110H ,试求: (1)画出程序段执行后的堆栈存储情况示意图。 (2)给出当前栈顶SS 和SP 的值。 PUSHF 当前栈顶 PUSH AX SS:SP →1000H:2108H--CL PUSH [0250H] PUSH CX 答:(1)如图所示 SS:SP →1000H:2110H--...... 第四章 简答 8.简述DMA 控制器的特点及功能。 答:DMA 控制器是内存储器同外设之间进行高速数据的硬件控制电路,是一种实现直接数据传送的专用处理器,它必须能取代在程序控制传送中由CPU 和软件所完成的各项功能,它的主要功能是:(1)DMAC 同外设之间有一 0 0 0 1 0 0 0 1 0 0 0 0 0 0 0 0 0 1 1 0 1 1 0 1 0 0 0 1 0 1 1 0 21H 34H 65H 87H (CL ) (CH) (AL) (AH) (F1) (FH) ........

移位寄存器的工作原理是什么? 把若干个触发器串接起来,就可以构成一个移位寄存器。由4个边沿D 触发器构成的4位移位寄存器逻辑电路如图8.8.1所示。数据从串行输入端D1输入。左边触发器的输出作为右邻触发器的数据输入。假设移位寄存器的初始状态为0000,现将数码D3D2D1D0(1101)从高位(D3)至低位依次送到D1端,经过第一个时钟脉冲后,Q0=D3。由于跟随数码D3后面的数码是D2,则经过第二个时钟脉冲后,触发器FF0的状态移入触发器FF1,而FF0变为新的状态,即Q1=D3,Q0=D2。依此类推,可得4位右向移位寄存器的状态, 如表8.8.1所示。 由表可知,输入数码依次地由低位触发器移到高位触发器,作右向移动。经过4个时钟脉冲后,4个触发器的输出状态Q3Q2Q1Q0与输入数码D3D2D1D0相对应。为了加深理解,在图8.8.2中画出了数码1101(相当于D3=1,D2=1,D1=0 ,D0=1)在寄存器中移位的波形,经过了4个时钟脉冲后,1101出现在寄存器的输出端Q 3Q2Q1Q0。这样,就可将串行输入(从D1端输入)的数码转换为并行输出(从Q3、Q2、Q1、Q0端输出)的数码。这种转换方式特别适用于将接收到的串行输入信号转换为并行输出信号,以便于打印或由计 算机处理。 在图8.8.3中还画出了第5到第8个时钟脉冲作用下,输入数码在寄存器中移位的波形(如图8.8.2所示)。由图可见,在第8个时钟脉冲作用后,数码从Q3端已全部移出寄存器。这说明存入该寄存器中的数码也可以从Q端串行输出。根据需要,可用更多的触发器组成多位移位寄存器。

除了用边沿D 触发器外,还可用其他类型的触发器来组成移位寄存器,例如,用主从JK 触发器来组成移位寄存器,其级间连接方式如图8.8.3所示。根据JK触发器的特征方程,由图8.8.3可得: FF2和FF3的接法与FF1完全相似,所以各JK 触发器均以D 触发器的功能工作,图8.8.3和图8.8.1所 示电路具有相同的功能。 双向移位寄存器: 若将图8.8.1所示电路中各触发器间的连接顺序调换一下,让右边触发器的输出作为左邻触发器的数据输入,则可构成左向移位寄存器。若再增添一些控制门,则可构成既能右移(由低位向高位)、又能左移(由高位至低位)的双向移位寄存器。图8.8.4是双向移位寄存器的一种方案,它是利用边沿D 触发器组成的,每个触发器的数据输入端D 同与或非门组成的转换控制门相连,移位方向取决于移位控制端S的状态。 当S=1时,D0=DSR,D1=Q0,即FF0的D0端与右移串行输入端DSR接通,FF1的D1端与Q0接通,在时钟脉冲CP 作用下,由DSR端输入的数据将作右向移位;反之,当S=0时,D0=Q1 ,D1=Q2,在时钟脉冲CP作用下,Q2、Q1的状态将作左向移位。同理,可以分析其他两位触发器间的移位情况。由此

一、段寄存器的产生 段寄存器的产生源于Intel 8086 CPU体系结构中数据总线与地址总线的宽度不一致。 数据总线的宽度,也即是ALU(算数逻辑单元)的宽度,平常说一个CPU是“16位”或者“32位”指的就是这个。8086CPU的数据总线是16位。 地址总线的宽度不一定要与ALU的宽度相同。因为ALU的宽度是固定的,它受限于当时的工艺水平,当时只能制造出16位的ALU;但地址总线不一样,它可以设计得更宽。地址总线的宽度如果与ALU相同当然是不错的办法,这样CPU的结构比较均衡,寻址可以在单个指令周期内完成,效率最高;而且从软件的解决来看,一个变量地址的长度可以用整型或者长整型来表示会比较方便。 但是,地址总线的宽度还要受制于需求,因为地址总线的宽度决定了系统可寻址的范围,即可以支持多少内存。如果地址总线太窄的话,可寻址范围会很小。如果地址总线设计为16位的话,可寻址空间是2^16=64KB,这在当时被认为是不够的;Intel最终决定要让8086的地址空间为1M,也就是20位地址总线。 地址总线宽度大于数据总线会带来一些麻烦,ALU无法在单个指令周期里完成对地址数据的运算。有一些容易想到的可行的办法,比如定义一个新的寄存器专门用于存放地址的高4位,但这样增加了计算的复杂性,程序员要增加成倍的汇编代码来操作地址数据而且无法保持兼容性。 Intel想到了一个折中的办法:把内存分段,并设计了4个段寄存器,CS,DS,ES和SS,分别用于指令、数据、其它和堆栈。把内存分为很多段,每一段有一个段基址,当然段基址也是一个20位的内存地址。不过段寄存器仍然是16位的,它的内容代表了段基址的高16位,这个16位的地址后面再加上4个0就构成20位的段基址。而原来的16位地址只是段内的偏移量。这样,一个完整的物理内存地址就由两部分组成,高16位的段基址和低16位的段内偏移量,当然它们有12位是重叠的,它们两部分相加在一起,才构成完整的物理地址。 Base b15 ~ b12 b11 ~ b0 Offset o15 ~ o4 o3 ~ o0 Address a19 ~ a0 这种寻址模式也就是“实地址模式”。在8086中,段寄存器还只是一个单纯的16位寄存器,而且操作寄存器的指令也不是特权指令。通过设置段寄存器和段内偏移,程序就可以访问整个

机械设计创新设计 题目:干粉压片机 学校: 院系:机电学院 专业:工程机械 班级:09级2班 设计者: 指导老师:胡启国 2012年5月 前言 1.1 干粉压片机的概述 干粉压片机是指利用传动系统将电动机的转速降低带动执行机构对粉末物质采取 上下进行加压而成片状。根据干粉压片机的传动系统和执行机构不同,干粉压片机可以分为单片式压片机,旋转式压片机,亚高速旋转式压片机、全自动高速压片机以及旋转式包芯压片机。 干粉压片机的使用行业很广泛。如制药厂、电子元件厂、陶瓷厂、化工原料厂等等,而且压片机还能用来做冲压设备。 压片机在欧美压片机出现的较早。而在国内到1949年,上海市的天祥华记铁工厂仿造成英国式33冲压片机;1951年,根据美国16冲压片机改制成国产18冲压片机,这是国内制造的最早制药机械;1957年,设计制造了ZP25-4型压片机;1960年,自行设计制造成功60-30型压片机,具有自动旋转、压片的功能。同年还设计制造了ZP33型、ZP19型压片机。“七五”期间,航空航天部206所HZP26高速压片机研制成功。1980年,上海第一制药机械厂设计制造了ZP-21W型压片机,达到国际上世纪80年代初的先进水平,属国内首创产品。1987年,引进联邦德国Fette公

司微机控制技术,设计制造了P3100-37型旋转式压片机,具有自动控制片剂重量、压力、自动数片、自动剔除废片等功能,封闭结构严密、净化程度达到GMP要求。1997,年上海天祥健台制药机械有限公司研发了ZP100系列旋转式压片机、GZPK100系列高速旋转式压片机。进入21世纪,随着GMP认证的深入,完全符合GMP的ZP系列旋转式压片机相继出现:上海的ZP35A、山东聊城的ZP35D等。高速旋转式压片机在产量、压力信号采集、剔废等技术上有了长足的发展,最高产量一般都大于300000片/小时,最大预压力20kN,最大主压力80kN或10080kN。譬如,北京国药龙立科技有限公司的GZPLS-620系列高速旋转式压片机、上海天祥健台制药机械有限公司的GZPK3000系列高速旋转式压片机、北京航空制造工程研究所的PG50系列高速旋转式压片机等。随着制造加工工艺水平、自动化控制技术的提高以及压片机使用厂家各种不同的特殊需求,各种特殊用途的压片机也相继出现。譬如,实验室用ZP5旋转式压片机、用于干粉压片的干粉旋转式压片机、用于火药片剂的防爆型ZPYG51系列旋转式压片机等。 国内压片机的现状:(1)压片机规格众多、数量大;(2)操作简单;(3)技术含量较低,技术创新后力不足。国外压片机的现状:高速高产、密闭性、模块化、自动化、规模化及先进的检测技术是国外压片机技术最主要的发展方向。 1.2 干粉压片机的研究现状 1.2.1 压片机动力学分析及力的优化 文献[6]阐述了主加压机构的运动学分析。对机构进行运动学分析可采用图解法分析和解析法分析.在此,我们采用解析法,应用c语言程序进行分析。杆组法运动学分析原理,由机构的组成原理可知,任何平面机构都可分解为原动件、基本杆组和机架三个部分,每一个原动件为一个单杆构件.分别对单杆构件和常见的基本杆组进行运动学分析,并编制成相应的子程序,在对整个机构进行运动分析时,根据机构组成情况的不同,依次调用这些子程序,从而完成对整体机构的运动分析。 文献[10]阐述了各种方案的拟定。根据各功能元的解,动力源可以采用电动机、汽油机、蒸汽透平机、液压机、气动马达等;上下加压则可采用凸轮机构、齿轮机构、连杆机构、液压缸等;送料可采用连杆机构、齿轮机构、槽轮机构等.这样可组合的方案达上百种。 文献[7]阐述了谐响应分析。分析动态响应实际上是解一个完整的动力学方程,它是一个二阶常系数线性微分方程: [M]{x(t)}+[c]{x(t)}+[K]{x(t)}={P(t)} 式中:[M] 、[c]、[K]--质量矩阵、阻尼矩阵和刚度矩阵。x(t)、x(t)、x ( t)--结点的加速度、速度和位移向量,它们均为时间的函数。fP(t)卜一激振力向量,也是时问的函数。谐响应分析是用于确定线性结构在承受随时问按正弦规律变化载荷时稳态响应的一种技术。分析的目的是计算出结构在谐波激振力下的响应,即位移响应与应力响应,并得到系统的动态响应与系统激振力频率的曲线,称为幅频曲线。压片机工作时,冲头和压轮周期性接触,这样就会造成有周期性的激振力作用在整个结构上。当激振力的频率与压片机的固有频率接近时,就会发生共振。共振现象的发生不但不能保证冲压的加工精度,还会对冲头和压轮以致整个机床造成严重破坏,这是一定要避免的。通过以上分析,可以得到以下结论: (1)经过力的优化以后,避免了在第一、二阶固有频率处的共振现象的发生,虽然优化后,第三阶固有频率处的位移比其他频率处较大(1.8xlO4),但小于优化前该频率处的位移(2.1xlO4),更远远小于机器共振时的(1。6x10一),振动量降低了接近1O倍。(2)经过力的优化以后,由于对整体结构不存在激振力,所以一、二、四、五阶振型不会对动态性能产生影响。(3)由于该压片机的实际工作转数在每分钟4O一6O转之间,即工作频率为48 73Hz之间,而优化后在96HZ处振动量较大,远离工作频率范围,所以,机器处于安全良好的工作区域范围,具有良好的动态性能。通过对压片机的模态分析,动力学谐响应分析,得出了压片机在不同工作频率范围下的响应,在此基础上对整体结构进行了力的优化,有效的抑制了共振现象的发生,解决了机器工作时振动和噪音的问题,分析结

摘要 TFT—LCD显示及驱动电路设计由视频解码电路,LCD显示电路,电源控制电路和单片机控制电路四个模块组成。视频源产生模拟视频信号,由TVP5150视频解码把模拟视频信号解码输出数字视频信号,由LCD液晶屏显示。对视频解码和液晶显示器的配置是通过单片机完成的。本设计主要针对高校电视技术实践课程设计,应用于视频解码输出教学,实现信号处理可视模块化教学方案。 关键字 视频解码 LCD显示单片机

毕业论文 目录 第一章概述 (3) 1.1 设计背景 (3) 1.2系统框图 (3) 第二章 TFT--LCD液晶显示技术 (1) 2.1液晶基本性质及显示原理 (1) 2.2 PT035TN01—V6液晶显示屏 (1) 2.2.1 PT035TN01—V6模式选择 (1) 2.2.2 PT035TN01—V6屏的交直流电路设计 (1) 2.2.3 PT035TN01—V6屏的SPI电路设计 (2) 第三章图像解码的电路设计 (4) 3.1视频解码芯片的选取 (4) 3.2 TVP5150视频解码芯片 (5) 3.2.1 TVP5150芯片引脚功能 (5) 3.2.2 TVP5150典型寄存器 (5) 3.3 TVP5150视频解码系统配置 (6) 3.3 TVP5150典型电路 (6) 3.3.1 复位电路 (6) 3.3.2 A/D采样电路 (6) 3.3.3 晶振电路 (6) 3.4 TVP5150的具体配置 (7) 第四章 MCU 控制电路 (9) 4. 1单片机概述 (9) 4.2单片机的总线控制 (9) 4.2.1单片机对液晶屏的控制 (9) 4.2.2单片机对TVP5150的控制 (9) 第五章开关电源设计 (11) 5.1设计要求 (11) 5.1.1 电源芯片的选取 (11) 5.1.2功能分析 (11) 5.2 升压电路 (11) 5.2.1升压原理 (11) 5.2.2 升压电路 (11) 5.2 降压电路 (11) 5.2.1降压原理 (11) 5.2.2降压电路 (11) 第六章软件系统 (12) 6.1软件流程图 (12) 6.1.1 PT035TN01—V6液晶显示屏软件流程图 (12) 6.1.2 TVP5150解码电路程序框图 (13) 6.2 TVP5150 IIC程序见附录一 (13) 第七章系统调试与结果 (14) 7.1 硬件调试 (14) 7.1.1 调试方法 (14) 7.1.2 调试数据 (14) 7.2软件调试 (14) 7.2.1 编译环境 (14) 7.2.2 调试波形 (14) 总结 (15) 谢辞 (16) 参考文献 (17) 附录一 (18)

机械原理课程设计 题目:干粉压片机 学校:洛阳理工学院 院系:机电工程系 专业:计算机辅助设计与制造 班级:z080314 设计者:李腾飞(组长)李铁山杜建伟 指导老师:张旦闻 2010年1月1日星期五

课程设计评语 课程名称:干粉压片机的机构分析与设计 设计题目:干粉压片机 设计成员:李腾飞(组长)李铁山杜建伟 指导教师:张旦闻 指导教师评语: 2010年1月1日星期五

前言 干粉压片机装配精度高,材质优良耐磨损,稳定可靠,被公认为全国受欢迎产品。特别是现在的小型干粉压片机,市场前景很好。很多小型企业不可能花高价去买大型的,而且得不尝试,所以小型压片机更少中小型企业青睐。例如蚊香厂、鱼药饲料厂、消毒剂厂、催化剂厂都相继使用。本机还可改为异形冲模压片。由于该机型相对于其他机型压力较大,压片速度适中,因而受到生产奶片、钙片、工业、电子异形片的厂家欢迎。相信本厂品会给您带来良好的企业效应。 编者:洛阳理工学院第二小组 日期:2010年1月1日星期五

目录 一. 设计题目 (5) 1.工作原理以及工艺过程 (5) 2.原始数据以及设计要求 (5) 二. 设计题目的分析 (5) 1. 总功能分析 (5) 2. 总功能分解 (5) 3. 功能元求解 (6) 4. 运动方案确定 (7) 5. 方案的评价 (9) 6. 运动循环图 (10) 7. 尺度计算 (11) 8.下冲头对心直动滚子推杆盘形凸轮机 (13) 9.下冲头对心直动滚子推杆盘形凸轮机的位移曲线 (13) 三. 干粉压片机各部件名称以及动作说明 (14) 四. 参考书目 (14) 五. 新得体会 (14)

8位移位寄存器的电路设计与版图实现 摘要 电子设计自动化,缩写为EDA,主要是以计算机为主要工具,而Tanner EDA则是一种在计算机windows平台上完成集成电路设计的一种软件,基本包括S-Edit,T-Spice,W-Edit,L-Edit与LVS等子软件,其S-Edit以及L-Edit为常用软件,前者主要实现电路设计,后者主要针对的是已知电路的版图绘制,而T-Spice主要可实现电路图及版图的仿真,可以用Tanner EDA实现电路的设计布局以及版图实现等一系列完整过程。本文用Tanner EDA工具主要设计的是8位移位寄存器,移位寄存器主要是用来实现数据的并行和串行之间的转换以及对数据进行运算或专业处理的工具,主要结构构成是触发器,触发器是具有储存功能的,可以用来储存多进制代码,一般N 位寄存器就是由N个触发器构成,移位寄存器工作原理主要是数据在其脉冲的作用下实现左移或者右移的效果,输入输出的方式表现为串行及并行自由组合,本设计就是在Tanner EDA的软件平台上进行对8位移位寄存器的电路设计仿真,再根据电路图在专门的L-Edit 平台上完成此电路的版图实现,直至完成的结果和预期结果保持一致。 关键词:Tanner EDA;L-Edit;移位寄存器,S-Edit

8 bits shift register circuit design and layout Abstract Electronic design automation,referred to as EDA,it is based on computers as the main tool,and Tanner EDA is a kind of software that complete the integrated circuit design on Windows platforms.Its Sub-Softwares include S-Edit,T-Spice,W-Edit,L-Edit and LVS and so on.S-Edit and L-Edit are commonly used software,S-Edit is primarily designed to achieve circuit,the latter is aimed primarily known circuit layout drawing,T-Spice can achieve schematic and layout simulation.We can achieve layout of the circuit design and a series of complete process layout used Tanner EDA tools.In this paper, Tanner EDA tools are mainly designed an 8-bit shift register.The shift register is mainly used for data conversion between parallel and serial, and the data processing tool operation or professional,its main structure is the trigger composition,flip-flop is a storage function,it can be used to store more hexadecimal code,In general N-bits register is composed of N trigger.Working principle of the shift register data under the action of the pulse, mainly the effect of the shift to the left or right,input and output of the way of serial and parallel free combination.This design is in Tanner on the EDA software platform to 8 bits shift register circuit design and simulation,then according to the circuit diagram on special L - Edit platform to complete the circuit layout implementation,until the finish is consistent with the results and expected results. Keywords:Tanner EDA;L-Edit;Shift register,S-Edit

邮局订阅号:82-946360元/年技术创新 PLDCPLDFPGA应用 《PLC技术应用200例》 您的论文得到两院院士关注 基于CPLD 的多路视频帧切换技术研究 Research of the method of switching multi-channel video signal base on frame using CPLD (中山大学) 黄海路蒋念东 HUANGHai-luJIANGNian-dong 摘要:多路视频监控中常常会用到视频切换,而现行的各种视频切换多为基于播放时间的切换,切换瞬间会有图像损失,这对 视频监控是不利的。基于这种问题,本文设计一个应用在嵌入式系统的基于帧切换的多路视频切换系统,使用复杂可编程逻辑器件(Complex Programmable Logic Device,CPLD)提高电路集成度并简化开发流程。仿真结果显示切换瞬间扰动时间只有一帧图像的十万分之一,结果良好。 关键词:多路视频;视频切换;CPLD;TVP5150;帧切换;嵌入式中图分类号:TN911.73文献标识码:B Abstract:Most of the in existence multi-channel video switching method is base on time.And the picture may be partly broken at the moment of switching.It is a disadvantage in video monitoring.Aim to solute the problem,we design a system that switches mul -ti-channel video signal base on https://www.doczj.com/doc/ba5793899.html,ing complex programmable logic device (CPLD)can upgrade the integration of the circuit and simplify the designing flow.The simulation show a nice effect that the disorder signal just hundred thousandth of a frame in time. Key words:multi-channel video;video switching;CPLD;TVP5150;frame switching;embedded systems 文章编号:1008-0570(2010)09-2-0125-03 1引言 目前我国交通量随着经济的高速发展迅猛增长,同时交通状况也不断恶化,交通事故的频发导致了大量的人员伤亡和经济损失。其中群死群伤的重特大交通事故大多涉及客运车辆和运输车辆。导致事故的主要原因就是超载、超速、疲劳驾驶[1]等。同时,由于治安问题,乘客的生命安全和财产安全时有受到威胁。而对运营车辆进行视频监控不仅可以防患于未然,有效监控和约束司机行为,也能对车上的违法犯罪行为有威慑作用。 虽然基于PC 平台的视频采集卡已有大量成品并已投入市场,但现存的应用在嵌入式系统的视频监控系统多为单路视频监控,要进行多路监控,只能购入多套系统。在一辆运营车辆内安装多套系统,安装布线麻烦,设备占用空间大且成本高。而且如果需求改变则必须更换整套系统,不利于设备的升级。 现有的视频切换技术,多是基于时间的视频切换,即每隔一定的时间间隔切换一路视频信号。这种切换方法控制简单,但缺点也显然易见,切换的瞬间并不一定是视频信号两帧图像的切换时刻。切换更多的是发生在某帧图像的中段,于是切换瞬间的图像质量会相当不可靠,会出现半幅图像、黑屏、花屏等现象。由此造成图像失真,这将不利于监视与取证。 基于以上原因,本文研究设计一个使用CPLD 芯片对多路视频数据进行帧切换的系统,保证多路视频切换瞬间图像的完整性。 2系统基本原理 本系统从摄像机接收模拟视频信号,通过视频信号模数转换芯片(视频AD 芯片)将信号转化为数字信号。以CPLD 对数字信号进行处理,并选择输出,总体结构如图1所示。常见的视频数字信号编码方式有YUV 和RGB 两种,本文采用YUV422编码。在YUV422编码下的数字图像信号中,每帧图像开始时都会处在奇场且垂直同步信号为高电平,因此可利用这个特性准确地判断图像的开始。本系统用CPLD 芯片捕捉各路视频图像数据的开始信号,并根据选择信号判断输出某一路视频图像。 图1系统总体示意图 一般的视频AD 芯片都需要在上电时进行寄存器设置,设置的工作量不大,但每次上电开机时都必须设置一次,因此本文使用低端的单片机对多块视频AD 芯片进行设置,这样既满足需要又可降低成本。 3硬件系统 设计中使用4路模拟视频输入,视频制式可以是PAL(B,D, G,H,I,M,N)、NTSC(M,4.43)或SECAM(B,D,G,K,K1,L)中的 任意一种。通过视频数据模数转换芯片将模拟信号转换为数字信号,然后输入CPLD 芯片进行多路信号的切换,最后通过数据线将被选通的一路视频信号输送出去。 3.1TVP5150:视频AD 转换 本文使用的视频AD 转换芯片是TI(Texas Instruments 德州仪器公司)的TVP5150。该芯片使用1.8V 供电,是超低功耗、支 黄海路:硕士研究生125--

第一章 计算机硬件基本组成:1.运算器(ALU) 2.控制器(CU)3.存储器(M)4.输入设备(IN)5.输出设备(OUT) 1945年冯·诺依曼第一次提出了计算机组成和工作方式的基本思想 程序计数器(PC)控制指令的执行顺序 计算机中,所遇的信息都是用二进制表示的,其最小的单位是位,即一个二进制数。一组二进制数称之为一个字,字中所包含的二进制位数称之为字长。 一个字节由8位二进制数组成。储存单位一般以字节为单位。 一台计算机所固有的基本操作指令的集合成为该计算机的指令系统。 计算机的主频越高,运算速度越快。 复杂指令集计算机(CISC),精简指令计算机(RISC) 微处理器包括算术逻辑部件(ALU)、控制部件(CU)和寄存器组R三个基本部分和内部总线 微机的系统总线分为:1.数据总线(DB)2.地址总线(AB)3.控制总线(CB) 第二章 8086的编程结构包括:1.EU执行部件2.BIU总线借口部件 段寄存器的分类:1.CS 16位代码段寄存器 2.DS 16位数据段寄存器 3.SS 16位堆栈段寄存器 4.ES 16位附加段寄存器 物理地址计算方法:(物理地址是段地址左移四位加偏移地址) 物理地址=段基址×10H+偏移地址 寄存器在指令中的隐含使用 AH&AL=AX(accumulator):累加寄存器,常用于运算;在乘除等指令中指定用来存放操作数,另外,所有的I/O指令都使用这一寄存器与外界设备传送数据. BH&BL=BX(base):基址寄存器,常用于地址索引; CH&CL=CX(count):计数寄存器,常用于计数;常用于保存计算值,如在移位指令,循环(loop)和串处理指令中用作隐含的计数器. DH&DL=DX(data):数据寄存器,常用于数据传递。 他们的特点是,这4个16位的寄存器可以分为高8位: AH, BH, CH, DH.以及低八位:AL,BL,CL,DL。这2组8位寄存器可以分别寻址,并单独使用。