基于82527的CAN总线智能传感器节点设计

摘要:介绍一种以8051微控制器和82527独立CAN总线控制器为核心组成的CAN 总线智能传感器节点的设计方法,并给出其硬件原理图和初始化程序。

关键词:CAN总线 82527 单片机数据采集智能节点

引言

CAN(Controller Area Network,控制局域网)属于工业现场总线,是德国Bosch公司20世纪80年代初作为解决现代汽车中众多的控制与测试仪器间的数据交换而开发的一种通信协议。1993年11月,ISO正式颁布了高速通信控制局域网(CAN)的国际标准(ISO11898)。CAN总线系统中现场数据的采集由传感器完成,目前,带有CAN总线接口的传感器种类还不多,价格也较贵。本文给出一种由8051单片机和82527独立CAN总线控制器为核心构成的智能节点电路,在普通传感器基础上形成可接收8路模拟量输入和智能传感器节点。

1 独立CAN总线控制器82527介绍

82527是Intel公司生产的独立CAN总线控制器,可通过并行总线与Intel 和Motrorola的控制器接口;支持CAN规程2.0B标准,具有接收和发送功能并可完成报文滤波。82527采用CHMOS 5V工艺制造,44脚PLCC封装,使用温度为-44~+125℃,其引脚的排列和定义参见参考文献[1]。

(1)82527的时钟信号

82527的运行由2种时钟控制:系统时钟SCLK和寄存器时钟MCLK。SCLK

由外部晶振获得,MCLK对SCLK分频获得。CAN总线的位定时依据SCLK的频率,而MCLK为寄存器操作提供时钟。SCLK频率可以等于外部晶振XTAL,也可以是其频率的1/2;MCLK的频率可以等于SCLK或是其频率的1/2。系统复位后的默认设置是SCLK=XTAL/2,MCLK=SCLK/2。

(2)82527的工作模式

82527有5种工作模式:Intel方式8位分时复用模式;Intel方式16位分时复用模式;串行接口模式;非Intel方式8位分时复用模式;8位非分时复用模式。本文应用Intel方式8位分时复用模式,此时82527的30和44脚接地。

(3)82527的寄存器结构[2]

82527的寄存器地址为00~FFH.下面根据需要对寄存器给予介绍。

①控制寄存器(00H):

CCE——改变配置允许位,高电平有效。该位有效时允许CPU对配置寄存器1FH、2FH、3FH、4FH、9FH、AFH写操作。

EIE——错误中断允许位,高电平有效。该位一般置1,当总线上产生异常数量的错误时中断CPU。

SIE——状态改变中断允许位,高电平有效。该位一般置0。

IE——中断允许位,高电平有效。

INIT——软件初始化允许位,高电平有效。该位有效时,CAN停止收发报文,TX0和TX1为隐性电平1。在硬件复位和总线关闭时该位被置位。

②CPU接口寄存器(02H):

RSTST——硬件复位状态位。该位由82527写入,为1时硬件复位激活,不允许对82527访问;为0时允许对82527访问。

DSC——SCLK分频位。该位为1,SCLK=XTAL/2;为0,SCLK=XTAL。

DMC——MCLK分频位。该位为1,MCLK=SCLK/2;为0,MCLK=SCLK。

PWD——掉电模式使能位,高电平有效。

SLEEP——睡眠模式使能位,高电平有效。

MUX——低速物理层复用标志位。该位为1,ISO低速物理层激活,

PIN24=VCC/2,PIN11=INT#(#表示取反);该位为0,PIN24=INT#,PIN11=P2.6。

CEN——时钟输出允许位,高电平有效。

③标准全局屏蔽寄存器(06~07H)。该寄存器用于具有标准标识符的报文,或XTD置0的报文寄存器。该方式称为报文接收滤波。当某位为1时,报文标识符的相应位必须匹配;为0时,不必匹配。

④扩展全局屏蔽寄存器(08~0BH)。该寄存器用于扩展报文格式,或XTD 置1的报文寄存器,其作用与③相同。

⑤总线配置寄存器(2FH):

COBY——旁路输入比较器标志位,高电平有效。

POL——极性标志位。为1,如果旁路输入比较器,RX0的输入逻辑1为显性,逻辑0为隐性;为0,则反之。

DCT1——TX1输出切断控制位。为1,TX1输出不被驱动,该模式用于1根总线的情况,2根差分导线短路;为0,TX1输出被驱动。

DCR1——RX1输入切断控制位。为1,RX1与输入比较器的反相端断开,接至VCC/2;为0,RX1接至输入比较器反相端。

DCR0——RX0输入切断控制位。作用与DCR1相同,此时RX0接至比较器同相端。

⑥位定时寄存器0(3FH);

SJW——同步跳转宽度位场,编程值1~3。

BRP——波特率分频位场,编程值0~63。

⑦位定时寄存器1(4FH):

SPL——采样模式标志位。1表示每位采样3次;0表示每位采样1次。

TSEG1——时间段1位场,编程值2~15。

TSEG1——时间段2位场,编程值1~7。

波特率=XTAL/[(DSC+1)*(BRP+1)*(3+TSEG1+TSEG2)]

⑧报文寄存器(把每个寄存器的第1字节地址作为基址BASE)。

◇控制寄存器0,1(BASE+0,BASET+1)

MSGVAL——报文寄存器有效标志位,高电平有效。10置位,01复位。

TXIE——发送中断允许标志位,高电平有效。10置位,01复位。

RXIE——接收中断允许标志位,高电平有效,10置位,01复位。

INTPND——中断申请标志位,高电平有效。10置位,01复位。

RMTPND——远程帧申请标志位,高电平有效。10置位,01复位。

TXRQST——请求发送标志位,高电平有效。10置位,01复位。

MSGLST——报文丢失标志位,只用于接收报文寄存器。10表示未读报文被新报文覆盖,01表示未覆盖。

CPUUPD——CPU更新标志位,只用于发送报文寄存器。10报文不被发送,01报文可发送。

NEWDAT——新数据标志位。10表示向寄存器写入了新数据,01表示无新数据写入。

◇仲裁寄存器0,1,2,3(BASE+2-BASE+5)

存储报文标识符。

7 6 5 4 3 2 1 0

DLC DIR XTD 保留

◇报文配置寄存器(BASE+6)

DLC——数据长度编码,编程值0~8。

DIR——方向标志位。1发送,0接收。

XTD——标准/扩展标识符标志位。1扩展标识符,0标准标识符。

◇数据寄存器(BASE+7-BASE+14)

82527存储报文时,8个数据字节均被写入,未用到的字节数据是随机的。

2 硬件电路设计

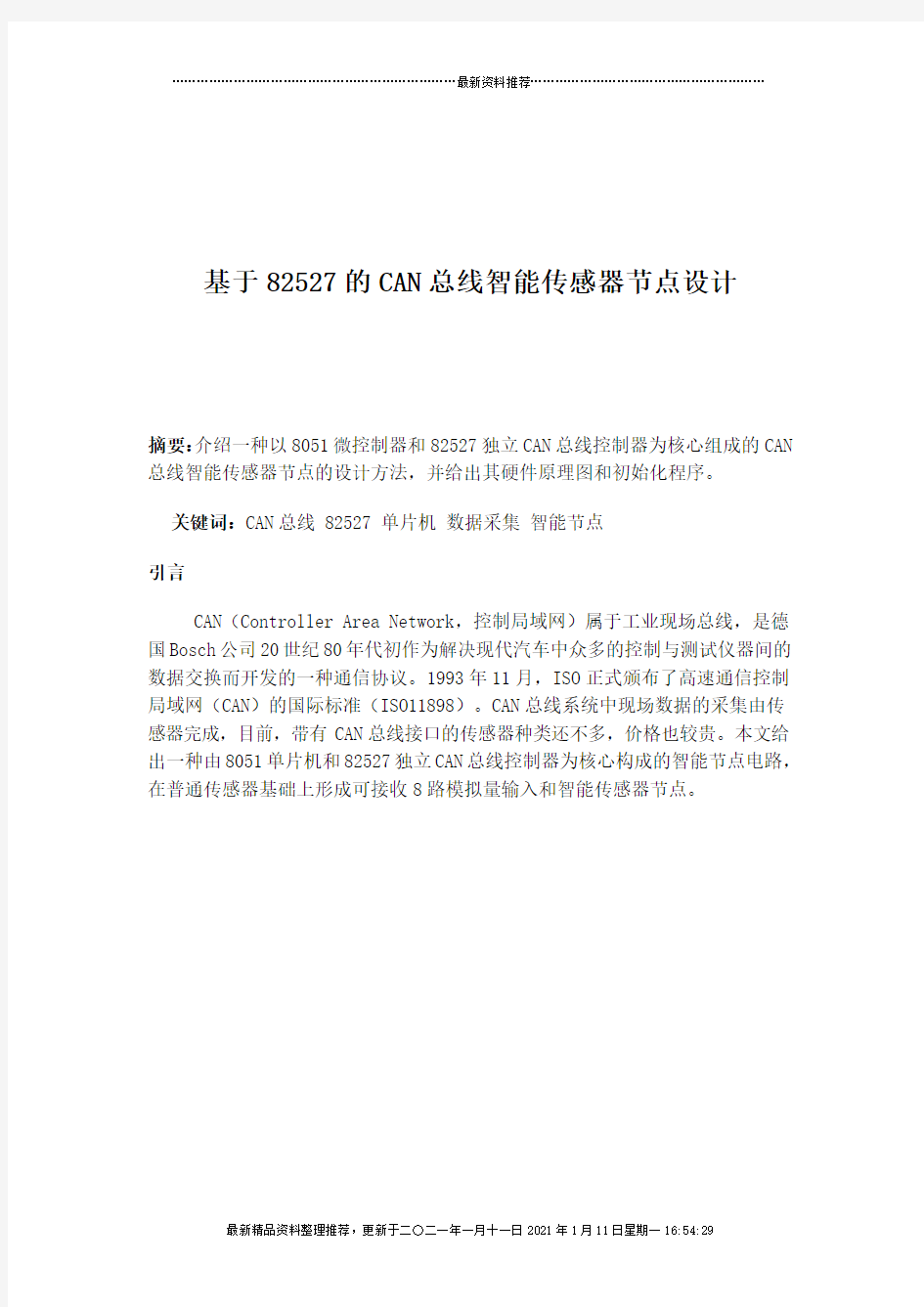

智能节点的电路如图1所示(图中6264略去)。

在硬件设计中,由ADC0809完成对8路模拟置的转换,与8051的信息交换采用查询方式,地址BFF8~BFFFH,其时

钟可由ALE二分频获得;82527完成与CAN总线的信息交换。

本设计中,旁路了输入比较器,与8051的信息交换采用中断

方式,地址7F00~7FFFH,可以用82527的P1口和P2口对开

关量采集或对继电器进行控制。82C250提供82527和物理总

线间的接口,提高接收和发送能力。可根据需要扩展程序存储

器。

3 软件设计

本设计软件采用MCS-51汇编语言编写,程序框图如图2所示。

82527的初始化程序如下:

INT:MOV DPTR,#0FF02H

MOV A,#00H

MOVX @DPTR,A ;SCLK=XTAL

;MCLK=SCLK,CLKOUT无效

MOV DPTR,#0FF00H

MOV A,#41H

MOVX @DPTR,A ;置位CCE,INIT

MOV DPTR,#0FF2FH

MOV A,#48H

MOVX @DPTR,A ;旁路输入比较器设置1位隐性,0为显性,RX1无效MOV DPTR,#0FF3FH;

MOV A,#43H;

MOVX @DPTR,A ;SJW=2,BRP=3

MOV DPTR,#0FF4FH

MOV A,#0EAH

MOVX @DPTR,A ;SPL=1,TSEG1=7,TSEG2=6此时波特率为100Kbps MOV DPTR,#0FF00H;

MOV A,#01H

MOVX @DPTR,A ;禁止对配置寄存器的访问

MOV DPTR,#0FF10H;

MOV A,#55H;

MOVX @DPTR,A;

INC DPTR;

MOVX @DPTR,A;

·

·

MOV DPTR,#0FFF0H;

MOV A,#55H;

MOVX @DPTR,A

INC DPTR;

MOVX @DPTR,A ;报文寄存器控制位初始化

MOV R0,#06H;

MOV DPTR,#0FF06H;

MOV A,#0FFH;

L1:MOVX @DPTR,A ;报文标识符需全部匹配

INC DPTR

DJNZ R0,L1;

MOV DPTR,#0FF16H;

MOV A,#8CH ;报文寄存器1可发送8个字节扩展报文MOVX @DPTR,A;

MOV DPTR,#0FF26H;

MOV A,#84H;

MOVX @DPTR,A ;报文寄存器2可接收8个字节扩展报文MOV DPTR,#0FF00H;

MOV A,#00H;

MOVX @DPTR,A ;初始化结束

Lonworks现场总线由美国Echelon公司于1993年推出,由于其开放的网络操作系统、标准的网络通信协议、丰富的介质接口模板、支持多种介质之间相互通信等特点,在工业控制领域得到了广泛响应。目前已有多种支持Lonworks 技术的芯片,Echelon公司的神经元芯片NeuronC31是一种集3个8位CPU及网络通信协议(LonTalk协议)为一体的芯片。采用该芯片构成的智能节点在Lonworks现场总线控制网络中起着举足轻重的作用,它能使现场设备之间相互通信,快速地交换信息,以满足系统实时监控的要求。但由于3150神经元芯片只提供11个通用I/O口,不能满足采集量和控制量要求较多的现场设备的要求,因此研究和开发基于神经元芯片的多点I/O的智能节点,是一项有意义的工作。

1 NeuronC3150神经元芯片的特点

NeuronC芯片既是Lonworks技术的核心也是智能节点的核心,目前由Toshiba和Motorola两家公司生产,主要包括NeuronC3150和NeuronC3120两种系列。3150芯片中包括E2PROM和RAM存储器,同3120芯片区别在于它无内部ROM,但具有访问外部存储器的接口,寻址空间可达64Kbyte。从这一点来说,3150比3120在节点开发上具有更好的灵活性。3150芯片内部带有3个8位微处理器:一个用于链路层的控制,另一个用于网络层的控制,第三个用于执行用户

的应用程序。该芯片还包含11个I/O口和完整的LonTalk通信协议,它同时具有通信和控制功能。

2 基于神经元芯片智能节点的开发方法

基于神经元芯片开发的智能节点具有结构简单、成本低等优势,其开发方法可分为两种:(1)基于控制模块的硬件设计方法。采用这一方法的优势是可缩短产品的开发周期,因为控制模块通常都集成了神经元芯片、Flash程序存储器、收发器以及RAM等,用户只需设计自己的应用电路即可完成节点开发。(2)基于收发器的硬件电路设计方法。采用这一方法可以降低节点成本,提高节点的市场竞争力,但是这一方法需要在考虑应用电路设计的同时考虑神经元芯片与Flash存储器及RAM的接口电路,这对于电路板的设计加工及生产工艺的要求都较高。

3 智能节点的电路设计

节点采用主、背板结构。主板上集成有控制电路、通信电路和其他附加电路,其结构图如图1。背板设计为两种多点I/O模块(包括多点数字I/O模块和多点模拟I/O模块)。主、背板之间采用统一标准的20针接口。采用主、背板结构设计法,使得此智能节点的应用领域更为广泛,适应性、通用性和功能都大大增强,对于节点应用程序的开发也更为灵活。

3.1 主板电路设计

3.1.1 控制电路

控制电路主要由神经元芯片,主背板接口电路和片外存储器等组成。各元器件功能如下:

(1)神经元芯片采用Toshiba公司生产的3150芯片,它主要用于提供对节点的控制、实施与Lon网的通信、支持对现场信息的输入输出等应用服务。

(2)片外存储器采用Atmel公司生产的AT29C256(FLASH存储器)。

AT29C256共有32K字节的地址空间,其中低16K字节空间用来存放神经元芯片的固件(包括LonTalk协议等)。高16字节空间作为节点应用程序的存储区。采用ISSI公司生产的IS61C256作为神经元芯片的外部RAM.。

(3)主、背板接口电路用于主板与多点I/O模块的电气连接。

3.1.2 通信电路

通信电路的核心——收发器是智能节点与Lon网之间的接口。目前,Echelon公司和其他开发商均提供了用于多种通信介质的收发器模块。本智能节点采用Echelon公司生产的适用于双绞线传输介质的FTT-10A收发器模块。

3.1.3 附加电路

附加电路主要包括晶振电路、复位电路和Service电路等。

晶振电路为3150神经元芯片提供工作时钟。

复位电路用于在智能节点上电时产生复位操作。另外,节点还将一个低压中断设备与3150的Reset管脚相连,构成对神经元芯片的低压保护设计,提高节点的可靠性和稳定性。

Service电路是专为下载应用程序的电路,Service指示灯对诊断神经元芯片固件状态有指示作用。

3.2 I/O扩展电路设计

3150神经元芯片包含11个通用口,用户可根据不同的需求进行灵活配置,以便于同外部设备进行接口。对于输入和输出(I/O)数量需求较大的外围设备,11个I/O口显然不能满足。虽然可以依靠增加节点数量来满足外围要求,但是这样做不仅成本价格高而且增加了安装的工作量,维护也不方便。因此,通过增加外围电路实现I/O扩展,成为多点I/O智能节点开发的重要部分。I/O扩展设计包括多点模拟模块设计和多点数字模块设计。

3.2.1 多点模块模块设计

多点模拟模块主电路图如图2。TLC2543是支持SPI串行总线的11路模拟通道的12位逐次逼近型模/数转换器。CS(Pin 15)片选信号端接IO0;DATA INPUT (Pin 17)为串行数据输入,其中四位串行地址用来选择下一个被转换的模拟通道或测试电压寄存器;DATA OUTPUT(Pin 16)输出模/数转换的结果;CLK是维持模/数转换正常工作的时钟。值得注意的是,时钟信号频率较高,任何一点干扰都可能影响模块的正常工作。在CLK上串联或并联一支电阻可以起到明显的抗干扰效果,保证模/数模块的稳定。(本模块中,CLK接IO8,DATA INPUT接IO9,DATA OUTPUT接IO10)。TLC2543还有一个特点:IO9输入数据的同时,IO10输出的是上一次模/数转换的值,因此在编写NeuronC源程序时要注意模/数转换的时序。选通两支旁路电路:一支47μF电解电容,对低频起滤波作用;另一支为0.1μF,对高频起滤波作用。此模/数模块没有选用电压基准,故在模/数芯片的参考电压边上接了一支0.1μF电容,用以去除高频干扰。

3.2.2 多点数字模块设计

多点数字模块主要包括:输入部分、输出部分、双向I/O三部分。通过扩展,模块具16路数字输入通道、15路数字输出通道和3路双向I/O通道。

(1)输入部分采用两片8选1数据选择器74LS151级联,并将NeuronC3150的IO0~IO3定义为Nibble Output方式,即半字节输出方式;IO4定义为Bit Input方式,即位输入方式。IO0~IO3作为16路输入通道的地址选通信号,与74LS151的地址输入端(E、A、B、C管脚)相连。IO4作为数字信号入口,与74LS151

的输出端连接。(具体电路如图3)下面的NeuronC源程序可完成对16路数字通道的定时扫描,定时时间为1s:

IO_0 output nibble io_mselect://定义半字节输出IO

IO_4 input bit io_tmp; //定义位输入IO

Stimer repeating t_circle=1 ;//定义并初始化定时器

When (timer_expires(t_circle))

{int i ;bit I_num,temp[15];//定义循环变量通道状态数组初始化通道号

for(i=0;i<16;i++)

{io_out(io_mselect,I_num) //写通道号

temp[i]=(io_in(io_tmp)= =ON)?1:0)}} //读通道状态并存入状态数组

(2)输出部分如图4,输出部分由两片8位移位寄存器74LS164和两片74LS373锁存器组成。164的功能是将NeuronC I/O口的15位串行帧输出转化为15路并行信号输出。373锁存器的作用是使164的15路输出在电平转换后加以保持,直到下一次电平转换。为了满足15路并行输出的要求,在时序上需要使两片373严格同步。因此在硬件上增加了非门和RC电路,对两片373的使能信号加以协调。通过实验,证明此电路能够完全满足设计要求。在NeuronC源程序中将IO8、IO9定义为Serial Output方式,即中行输出方式。其中IO8输出时钟信号,IO9输出串行数据。IO7定义为Bit Output方式,即位输出方式,作为164的清零端。

(3)双向I/O部分为了使用户对此智能节点的二次开发更为灵活、方便,我们在多点数字模块上设计了三个双向I/O口(IO5、IO6、IO10)。用户可根据自己需要,利用模块上的拨动开关进行输入、输出切换。

需要注意的是,为了提高智能节点的抗干扰能力,在输入、输出电路中均采用了光电耦合器进行电气隔离。特别在输出端加入了三极管功率放大电路以便驱动外部继电器。

水电厂中的水利机组控制系统中有众多参量需要测量和控制(包括模拟和数字量),如调速器开关、灭磁信号、主阀开关、冷却水泵、励磁投入信号、锁锭控制等。因此,系统对I/O口的需求量较大,传统的智能节点远远不能满足要求。而我们通过对多点I/O智能节点的开发,成功地研制出WSTA2000小型水利机组综合自动化装置。此装置已在水电厂中投入使用,运行情况良好。