数字电子课程设计实验报告

数字钟是采用数字电路实现“时”、“分”、“秒”数字显示的计时装置。钟表的数字化在提高报时精度的同时,也大大扩展了它的功能,诸如定时自动报警、按时自动打铃、时间程序自动控制、定时广播、定时启闭路灯等。因此,研究数字钟及扩大其应用,有着非常现实的意义。

一、设计目的

1)掌握数字钟的设计、组装与调试方法。

2)熟悉集成电路的使用方法。

二、设计任务与要求

1)时钟显示功能,能够以十进制显示“时”、“分”、“秒”。

2)具有校准时、分的功能。

3)整点自动报时,在整点时,便自动发出鸣叫声,时长1s。

三、数字钟的基本原理及电路设计

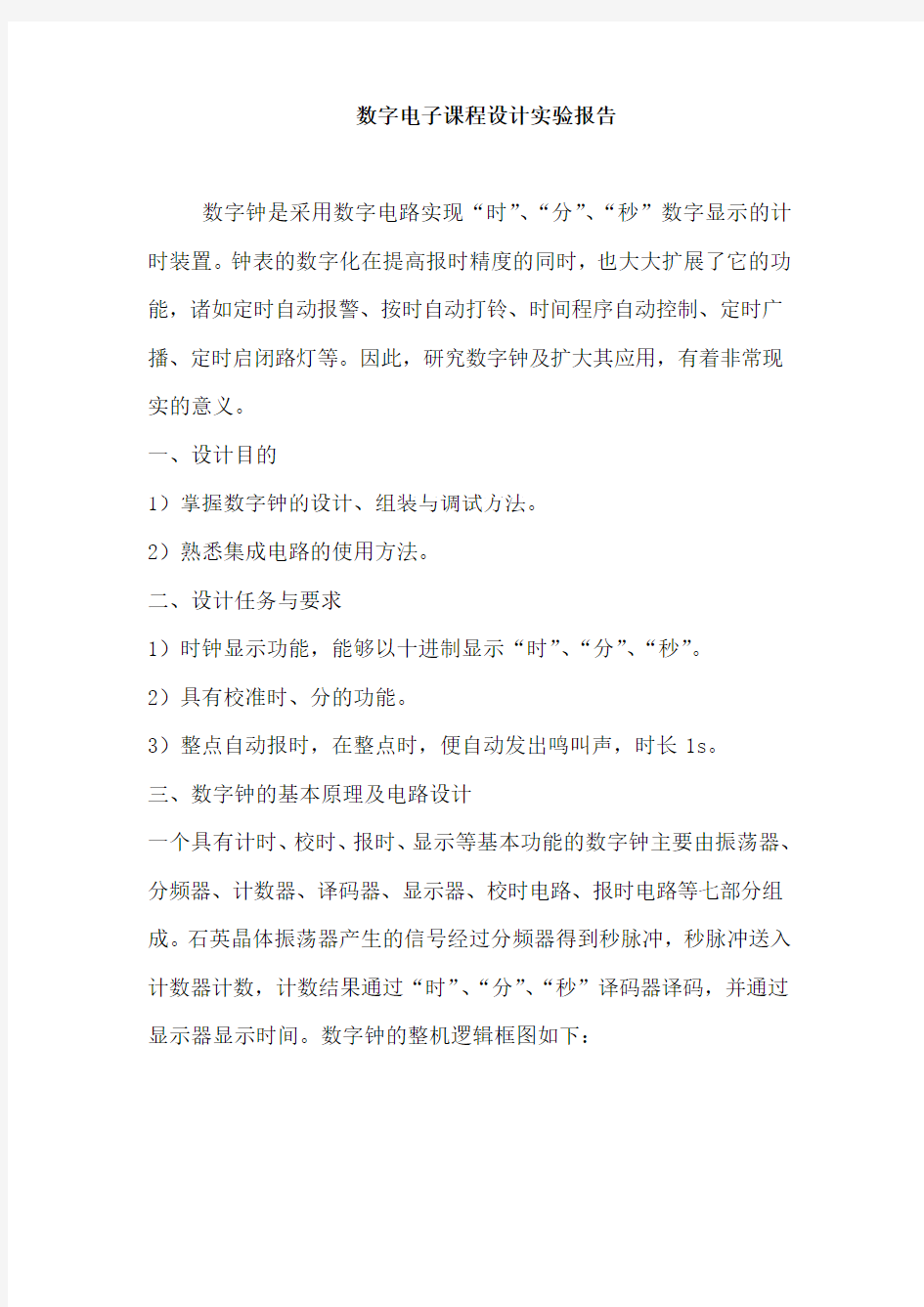

一个具有计时、校时、报时、显示等基本功能的数字钟主要由振荡器、分频器、计数器、译码器、显示器、校时电路、报时电路等七部分组成。石英晶体振荡器产生的信号经过分频器得到秒脉冲,秒脉冲送入计数器计数,计数结果通过“时”、“分”、“秒”译码器译码,并通过显示器显示时间。数字钟的整机逻辑框图如下:

数字钟整机逻辑图

1)振荡器

振荡器可由晶振组成,也可以由555定时器组成。下图是由555定时器构成的1KHZ的自激振荡器,其原理是0.7(2R3+R4+R5)C4=1ms,f=1/t=1KHZ。

下图为555定时器产生频率为1KHZ信号的电路

分频器

计时是1HZ的脉冲才是1S计一次数,所以需要分频才能得到1HZ的脉冲,如下图所示电路,是三个用十进制计数器74LS90串联而成的分频器,分频原理是在74LS90的输出端子中,从低位输入10个脉冲才从高位输出1个脉冲,这样一片74LS90就可以起十分频的作用,三个74LS90串联就构成了千分频的电路,输出的便是1HZ的信号,从而达到目的。

在仿真时,1HZ的频率太慢了,在实际中得到的时间不是1S计数一次,所以仿真都是用函数发生器代替。

计数器

整个计数器电路由秒计数器、分计数器、时计数器串接而成。秒计数器和分计数器各自由计数。

两个十进制计数器可以形成两个六十进制计数器。

六十进制计数器

由两个十进制计数器构成的二十进制计数器的电路图

数字通信原理实验报告 指导老师学生姓名 学号 专业班级宋虹 ************* *********************

实验_ --------------------------------------- 2实验目的 ---------------------------------------- 2实验内容 ---------------------------------------- 2基本原理 ---------------------------------------- 2实验步骤 ---------------------------------------- 9实验结果 ---------------------------------------- 11

实验一数字基带信号 一、实验目的 1、了解单极性码、双极性码、归零码、不归零码等基带信号波形特点。 2、掌握AMI、HDB,码的编码规则。 3、掌握从HDB,码信号中提取位同步信号的方法。 4、掌握集中插入帧同步码时分复用信号的帧结构特点。 5、了解HDB, (AMI)编译码集成电路CD22103o 二、实验内容 1、用示波器观察单极性非归零码(NRZ)、传号交替反转码(AMI)、三阶高密度双极性 码(HDB,)、整流后的AMI码及整流后的HDB,码。 2、用示波器观察从HDB,码中和从AMI码中提取位同步信号的电路中有关波形。 3、用示波器观察HDB,、AMI译码输岀波形。 基本原理 本实验使用数字信源模块和HDBs编译码模块。 1、数字信源 本模块是整个实验系统的发终端,模块内部只使用+5V电压,其原理方框图如图1-1所示,电原理图如图1-3所示(见附录)。本单元产生NRZ信号,信号码速率约为170. 5KB, 帧结构如图1-2所示。帧长为24位,其中首位无泄义,第2位到第8位是帧同步码(7位巴克码1110010),另外16位为2路数据信号,每路8位。此NRZ信号为集中插入帧同步码时分复用信号,实验电路中数据码用红色发光二极管指示,帧同步码及无左义位用绿色发光二极管指示。发光二极管亮状态表示1码,熄状态表示0码。 本模块有以下测试点及输入输岀点: ?CLK 晶振信号测试点 ?BS-0UT 信源位同步信号输岀点/测试点(2个) ?FS 信源帧同步信号输出点/测试点 ?NRZ-OUT(AK)NRZ信号(绝对码)输岀点/测试点(4个) 图1-1中各单元与电路板上元器件对应关系如下:

通信原理实验平台依据国内主流教材内容设计,涵盖数字基带传输、数字调制模拟信号数字化、同步技术、信道编码等主要教学内容,实验平台的技术方案与教材一致,使理论教学与实验教学实现无缝衔接。通过实验既能加深对理论的理解又能用学习理论指导实验,避免互相脱节的麻烦,获得理论与实践的双赢。 本实验平台共由24个实验模块组成,可分为信号源模块、终端编译码模块、线路编译码模块、信道调制解调模块、二次开发模块、各种测量通信接口模块,以及控制显示模块等几大类,各模块功能叙述如下: 1、液晶显示模块 显示实验模块及其工作方式以供选择。 2、键盘控制模块 (1)选择实验模块及其工作方式。 (2)学生可自己编制数字信号输入,进行编码或调制实验。 3、模拟信号源模块 提供同步正弦波、非同步信号(正弦波、三角波、方波)、音乐信号等模拟信号,可通过连 接线发送到各终端编码模块。 4、用户电话接口模块 提供用户电话接口,进行用户摘挂机检测,可发送语音信号,接收语音信号。 5、数字信号源模块 (1)CPLD可编程逻辑器件,编程输出各种数字信号 (2)通过计算机输入数字数据信号 (3)薄膜键盘键入编制数字信号 (4)EPM240芯片,学生二次开发编程输出各种数字信号、控制信号等 6、噪声源模块 提供白噪声信号,可加入到调制信道中模仿信道噪声干扰。 7、抽样定理与PAM实验系统 完成抽样定理的验证实验,及PAM通信系统实验。 注:提供多种频率的方波及窄脉冲信号抽样 8、PCM编译码系统模块 完成PCM的编码、译码实验; 完成两路PCM编码数字信号时分复用/解复用实验。

注:可改变时分复用的时隙位置,时分可复用路数及进行时分数据交换,加深学生对时分复用概念的理解 9、增量调制的编码模块 完成增量调制的编码实验,可进行模块或系统实验。 注:提供了三种编码时钟 10、增量调制的译码模块 完成增量调制的译码实验,可进行独立模块或系统实验。 注:提供了对应的三种译码时钟 11、AMI/HDB3编译码系统模块 完成AMI编译码功能、HDB3编译码功能。 注:提供对全“1”、全“0”、伪随机码、手工编制数字信号等进行编码译码 12、卷积编码实验模块 完成卷积编码实验。 注:通过对地址开关拨动编制数字信号输入,可模拟在信道中插入误码,分析卷积编译码的纠错能力 13、卷积译码实验模块 完成卷积译码实验。 14、VCO数字频率合成器模块 完成对1KHz、2KHz和外加数字信号的倍频输出。 15、频移键控FSK(ASK)调制模块 完成频移键控FSK调制实验, ASK调制实验。 注:①可对方波,伪随机码,计算机数据等信号的调制输出; ②可对已调信号进行放大或衰减输出; ③可在已调信号中加入噪声,模拟信道干扰 ④可完成本实验箱的自环单工通信实验,也可完成两台实验箱间的双工通信实验 16、频移键控FSK(ASK)解调模块 完成频移键控FSK解调实验,ASK解调实验。 17、相移键控BPSK(DPSK)调制模块 完成相移键控BPSK(DPSK)调制实验。 注:①可对方波,伪随机码,及计算机数据等信号进行调制输出;

《电子技术课程设计报告》 教学院:电气与电子信息工程学院 专业班级:xx级电子信息工程(x)班 学号:xxxxxxxxxxxx 学生:坏水 指导教师:xxxxxxxxxxxx 时间:2011.10.10~10.23 地点:电子技术实验室

课程设计成绩评定表

电子技术课程设计任务书 2011~2012学年第一学期 学生:坏水专业班级:xx电信本x班 指导教师:xxxxxxxxx 工作部门:电气与电子信息工程学院 一、课程设计题目:多功能数字钟电路的设计/直流稳压电源的设计 二、课程设计容(含技术指标): ①拟定多功能数字钟和直流稳压电源的组成框图,要现电路的基本功能,使用 的器件少,成本低; ②画出数字钟和直流稳压电源的主体电路逻辑图; ③测试多功能数字钟的逻辑功能,同时满足基本功能与扩展功能的要求; ④设计并安装各单元电路,要求布线整齐、美观,便于级联与调试;

四、基本要求 1.基本功能:要求设计出+5V的直流稳压电源。数字钟要求以数字形式显示时、分、秒的时间。小时计数器的计时要求为“12翻1”,要求具有手动校时功能。 2.扩展功能:定时控制,其时间自定;仿广播电台正点报时,自动报整点时数或触摸报整点时数(主要体现在理论知识上进行电路设计)。 (一)实训题目:直流稳压电源和多功能数字钟。 (二)实训目的: 1、巩固和加深学生对模拟电子技术,数字逻辑电路等课程基本知识的理解,综 合运用课程中所学到的理论知识去独立完成一个实际课题。 2、根据课程需要,通过查阅手册和文献资料,培养学生独立分析和解决实际问 题的能力。 3、通过电路方案的分析、论证和比较,设计计算和选用元气件,通过电路组装, 调试和检测环节,掌握电路的分析方法和设计方法。 4、熟用常用电子元气件的类型和特性,并掌握合理选用原则。 5、掌握电路图、PCB图的设计方法,学会电路的安装与调试。 6、掌握常用仪器、仪表的正确使用方法,学会电路整机指标的测试方法。(三)实训要求

中南大学 数字通信原理实验报告指导老师***** 学生姓名*** 学号*********** 专业班级*****************

目录 实验四 ----------------------------------------2 实验目的 ----------------------------------------2 实验内容 ----------------------------------------2基本原理 ----------------------------------------2实验步骤 ----------------------------------------9 实验结果 ----------------------------------------11

实验四数字解调与眼图 一、实验目的 1. 掌握2DPSK相干解调原理。 2. 掌握2FSK过零检测解调原理。 二、实验内容 1. 用示波器观察2DPSK相干解调器各点波形。 2. 用示波器观察2FSK过零检测解调器各点波形。 3.用示波器观察眼图。 三、基本原理 可用相干解调或差分相干解调法(相位比较法)解调2DPSK信号。在相位比较法中,要求载波频率为码速率的整数倍,当此关系不能满足时只能用相干解调法。本实验系统中,2DPSK载波频率等码速率的13倍,两种解调方法都可用。实际工程中相干解调法用得最多。2FSK信号的解调方法有:包络括检波法、相干解调法、鉴频法、过零检测法等。 图4-1 数字解调方框图 (a)2DPSK相干解调(b)2FSK过零检测解调 本实验采用相干解调法解调2DPSK信号、采用过零检测法解调2FSK信号。2DPSK模块内部使用+5V、+12V和-12V电压,2FSK模块内部仅使用+5V电压。图4-1为两个解调器的原理方框图,其电原理图如图4-2所示(见附录)。

信息科学与工程学院 课程:数字通信原理 题目:通信原理实验报告 专业班级: 学生姓名: 学号:

2017年12月1日

目录 实验一数字基带信号....................................二实验二数字调制......................................十六实验四数字解调与眼图..............................二十三

实验一数字基带信号 一、实验目的 1、了解单极性码、双极性码、归零码、不归零码等基带信号波形特点。 2、掌握AMI、HDB 3 码的编码规则。 3、掌握从HDB 3 码信号中提取位同步信号的方法。 4、掌握集中插入帧同步码时分复用信号的帧结构特点。 5、了解HDB 3 (AMI)编译码集成电路CD22103。 二、实验内容 1、用示波器观察单极性非归零码(NRZ)、传号交替反转码(AMI)、三阶 高密度双极性码(HDB 3)、整流后的AMI码及整流后的HDB 3 码。 2、用示波器观察从HDB 3 码中和从AMI码中提取位同步信号的电路中有关波形。 3、用示波器观察HDB 3 、AMI译码输出波形。 三、基本原理 本实验使用数字信源模块和HDB 3 编译码模块。 1、数字信源 本模块是整个实验系统的发终端,模块内部只使用+5V电压,其原理方框图如图1-1所示,电原理图如图1-3所示(见附录)。本单元产生NRZ信号,信号码速率约为170.5KB,帧结构如图1-2所示。帧长为24位,其中首位无定义,第2位到第8位是帧同步码(7位巴克码1110010),另外16位为2路数据信号,每路8位。此NRZ信号为集中插入帧同步码时分复用信号,实验电路中数据码用红色发光二极管指示,帧同步码及无定义位用绿色发光二极管指示。发光二极管亮状态表示1码,熄状态表示0码。 本模块有以下测试点及输入输出点: ? CLK 晶振信号测试点 ? BS-OUT 信源位同步信号输出点/测试点(2个) ? FS 信源帧同步信号输出点/测试点 ? NRZ-OUT(AK) NRZ信号(绝对码)输出点/测试点(4个) 图1-1中各单元与电路板上元器件对应关系如下: ?晶振CRY:晶体;U1:反相器7404 ?分频器U2:计数器74161;U3:计数器74193;U4:计

专业:电子信息工程班级:电信1305班日期:2015.5.5 第3次实验 姓名:康健组别: 6 指导教师:成绩: 实验课题:EDA多功能数字钟 1、已知条件 Quartus II软件、FPGA实验开发装置。 2、主要技术指标 以数字形式显示时、分、秒的时间;小时计数器为同步24进制;要求手动校时、校分。 3、实验用仪器 PC、FPGA开发板、示波器、稳压电源等 4、电路工作原理 所谓的时钟,其实本质上就是计数器。以开发板上的晶振时钟作为时间基准。 然后通过分频模块(计数器)进行分频,得到1Hz的脉冲信号作为秒的信号脉冲,然后用模60的计数器构成秒的计数单元。每记60下就自动清零且产生进位信号。将这个进位信号作为分的计数器的使能信号,其中,分计数器也是模为60的计数器。这里的计数器都是由模10和模6 组成的BCD码的计数器。个位和十位分别是一个四位的数字。同理,每记满60,分计数器就会产生一个进位信号,这个进位信号作为小时的使能信号。小时的计数器就是模24的BCD计数器。注意,这里的整个电路都是用1HZ的频率作为时间脉冲的,也就是说,这个电路是同步时序的电路。通过使能,来控制各个部分的时序逻辑。将小时和分的使能信号在总是为有效电平和下一级进位信号做选择,就是时钟调时状态和正常计时状态的切换。当在调时状态的时候,时钟每完成一个周期,无论是分钟还是小时,就向前加1,。最后,将分钟和小时通过译码器连接到数码管。将秒直接连接到LED灯,完成整个工程的基本功能(扩展功能见选作的实验报告)。 5、电路设计与调试 1、模10计数器的设计

2、模6计数器的设计 3、模60计数器设计(分、秒计数) 4、模24计数器设计(小时计数)

《数字通信原理与技术》实验报告 学院:江苏城市职业学院 专业:计算机科学与技术 班级: 姓名:___________ 学号: ________

实验一熟悉MATLAB环境 一、实验目的 (1)熟悉MATLAB的主要操作命令。 (2)掌握简单的绘图命令。 (3)用MATLAB编程并学会创建函数。 (4)观察离散系统的频率响应。 二、实验内容 (1)数组的加、减、乘、除和乘方运算。输入A=【1 2 3 4】,B=【3 4 5 6】,求C=A+B,D=A-B,E=A.*B,F=A./B,G=A.^B并用stem语句画出A、B、C、D、E、F、G。 (2)用MATLAB实现下列序列: a)x(n)=0.8n 0≦n≦15 b)x(n)=e(0.2+0.3j) 0≦n≦15 c)x(n)=3cos(0.125πn+0.2π)+0.2sin(0.25πn+0.1π) 0≦n≦15 d) 将c)中的x(n)扩展成以16为周期的函数x16(n)=x(n+16),绘出四个周期。 e) 将c)中的x(n)扩展成以10为周期的函数x10(n)=x(n+10),绘出四个周期。 (3) 绘出下列时间函数图形,对x轴、y轴以及图形上方均须加上适当的标注: a)x (t )=sin(2πt) 0≦n≦10s b) x (t)=cos(100πt)sin(πt) 0≦n≦14s 三、程序和实验结果 (1)实验结果: 1、A=[1,2,3,4] B=[3,4,5,6] C=A+B D=A-B E=A.*B F=A./B G=A.^B A =1 2 3 4 B =3 4 5 6 C =4 6 8 10 D =-2 -2 -2 -2 E =3 8 15 24 F =0.3333 0.5000 0.6000 0.6667 G =1 16 243 4096 >> stem(A) >> stem(B) >> stem(C) >> stem(D) >> stem(E) >> stem(F)

中南大学 数字通信原理 实验报告 课程名称:数字通信原理实验 班级: 学号: 姓名: 指导教师:

实验一数字基带信号 一、实验目的 1、了解单极性码、双极性码、归零码、不归零码等基带信号波形特点。 2、掌握AMI、HDB3码的编码规则。 3、掌握从HDB3码信号中提取位同步信号的方法。 4、掌握集中插入帧同步码时分复用信号的帧结构特点。 5、了解HDB3(AMI)编译码集成电路CD22103。 二、实验内容 1、用示波器观察单极性非归零码(NRZ)、传号交替反转码(AMI)、三阶高密度双极性码(HDB3)、整流后的AMI码及整流后的HDB3码。 2、用示波器观察从HDB3码中和从AMI码中提取位同步信号的电路中有关波形。 3、用示波器观察HDB3、AMI译码输出波形。 三、实验步骤 本实验使用数字信源单元和HDB3编译码单元。 1、熟悉数字信源单元和HDB3编译码单元的工作原理。接好电源线,打开电源开关。 2、用示波器观察数字信源单元上的各种信号波形。 用信源单元的FS作为示波器的外同步信号,示波器探头的地端接在实验板任何位置的GND点均可,进行下列观察: (1)示波器的两个通道探头分别接信源单元的NRZ-OUT和BS-OUT,对照发光二极管的发光状态,判断数字信源单元是否已正常工作(1码对应的发光管亮,0码对应的发光管熄); (2)用开关K1产生代码×1110010(×为任意代码,1110010为7位帧同步码),K2、K3产生任意信息代码,观察本实验给定的集中插入帧同步码时分复用信号帧结构,和NRZ 码特点。 3、用示波器观察HDB3编译单元的各种波形。 仍用信源单元的FS信号作为示波器的外同步信号。 (1)示波器的两个探头CH1和CH2分别接信源单元的NRZ-OUT和HDB3单元的AMI-HDB3,将信源单元的K1、K2、K3每一位都置1,观察全1码对应的AMI码(开关K4置于左方AMI 端)波形和HDB3码(开关K4置于右方HDB3端)波形。再将K1、K2、K3置为全0,观察全0码对应的AMI码和HDB3码。观察时应注意AMI、HDB3码的码元都是占空比为0.5的双极性归零矩形脉冲。编码输出AMI-HDB3比信源输入NRZ-OUT延迟了4个码元。

《多功能数字钟电路的设计、制作》 课程设计报告 班级:(兴) 2008级自动化 姓名:胡荣 学号:2008960623 指导教师:刘勇 2010年11月13日

目录 一、设计目的.................................1 二、设计内容及要求...........................1 三、总设计原理...............................1 四、主要元件及设备...........................2 五、单元电路的设计...........................5 1、数字电子计时器组成原理.................5 2、用74LS160实现12进制计数器..............6 3、校时电路...............................7 4、时基电路设计...........................8 六、设计总电路图.............................8 七、设计结果及其分析.........................8 八、设计过程中的问题及解决方案...............9 九、心得体会.................................9 十、附录.....................................10

多功能数字钟电路设计 一、设计目的 通过课程设计要实现以下两个目标:一、初步掌握电子线路的设计、组装及调试方法。即根据设计要求,查阅文献资料,收集、分析类似电路的性能,并通过组装调试等实践活动,使电路达到性能要求;二、课程设计为后续的毕业设计打好基础。毕业设计是系统的工程设计实践,而课程设计的着眼点是让我们开始从理论学习的轨道上逐渐引向实际方面,运用已学过的分析和设计电路的理论知识,逐步掌握工程设计的步骤和方法,同时,课程设计报告的书写,为今后从事技术工作撰写科技报告和技术资料打下基础。 二、设计内容及要求 1、功能要求: ①基本功能: 以数字形式显示时、分、秒的时间,小时计数器的计时要求为“12翻1”,并要求能手动快校时、快校分或慢校时、慢校分。 ②扩展功能: 定时控制,其时间自定;仿广播电台正点报时—自动报正点时数。 2、设计步骤与要求: ①拟定数字钟电路的组成框图,要求先实现电路的基本功能,后扩展功能,使用的器件少,成本低; ②设计各单元电路,并用Multisim软件仿真; ③在通用电路板上安装电路,只要求显示时分; ④测试数字钟系统的逻辑功能; ⑤写出设计报告。设计报告要求:写出详细地设计过程(含数字钟系统的整机逻辑电路图)、调试步骤、测试结果及心得体会。 三、总设计原理 数字电子钟原理是一个具有计时、校时、报时、显示等基本功能的数字钟主要由振荡器、分频器、计数器、译码器、显示器、校时电路、报时电路等七部分组成。石英晶体振荡器产生的信号经过分频器得到秒脉冲,秒脉冲送入计数器计数,计数结果通过“时”、“分”、“秒”译码器译码,并通过显示器显示时间。 四、主要元件及设备 1、给定的主要器件: 74LS00(4片),74LS160(4片)或74LS161(4片),74LS04(2片),74LS20(2片),74LS48(4片),数码管BS202(4只),555(1片),开关(1个),电阻47k(2个)电容10uF(1个)10nF(1个) 各元件引脚图如下图:

数字通信原理 实验报告 实验一AMI、HDB3编译码实验 学院计算机与电子信息学院 专业班级 姓名学号 指导教师 实验报告评分:_______

实验一 AMI、HDB3编译码实验 一、实验目的 了解由二进制单极性码变换为AMI码HDB3码的编码译码规则,掌握它的工作原理和实验方法。 二、实验内容 1.伪随机码基带信号实验 2.AMI码实验 ① AMI码编码实验 ② AMI码译码实验 ③ AMI码位同步提取实验 3.HDB3编码实验 4.HDB3译码实验 5.HDB3位同步提取实验 6.AMI和HDB3位同步提取比较实验 7.HDB3码频谱测量实验 8.书本上的HDB3码变化和示波器观察的HDB3码变化差异实验 三、基本原理:PCM信号基带传输线路码型 PCM信号在电缆信道中传输时一般采用基带传输方式,尽管是采用基带传输方式,但也不是将PCM编码器输出的单极性码序列直接送入信道传输,因为单极性脉冲序列的功率谱中含有丰富的直流分量和较多的低频分量,不适于直接送人用变压器耦合的电缆信道传输,为了获得优质的传输特性,一般是将单数性脉冲序列进行码型变换,以适应传输信道的特性。 (一)传输码型的选择 在选择传输码型时,要考虑信号的传输信道的特性以及对定时提取的要求等。归结起来,传输码型的选择,要考虑以下几个原则: 1.传输信道低频截止特性的影响 在电缆信道传输时,要求传输码型的频谱中不应含有直流分量,同时低频分量要尽量少。原因是PCM端机,再生中继器与电缆线路相连接时,需要安装变压器,以便实现远端供电(因设置无人站)以及平衡电路与不平衡电路的连接。 图1.1是表示具有远端供电时变压器隔离电源的作用,以保护局内设备。 图1.1变压器的隔离作用 由于变压器的接入,使信道具有低频截止特性,如果信码流中存在直流和低频成分,则

实验1:用 Verilog HDL 程序实现乘法器 1实验要求: (1) 编写乘法器的 Veirlog HDL 程序. (2) 编写配套的测试基准. (3) 通过 QuartusII 编译下载到目标 FPGA器件中进行验证 (4) 注意乘法逻辑电路的设计. 2 试验程序: Module multiplier(input rst,input clk,input [3:0]multiplicand, input [3:0]multiplier,input start_sig,output done_sig,output [7:0]result); reg [3:0]i; reg [7:0]r_result; reg r_done_sig; reg [7:0]intermediate; always @ ( posedge clk or negedge rst ) if( !rst ) begin i<=4'b0; r_result<=8'b0; end else if(start_sig) begin case(i) 0: begin intermediate<={4'b0,multiplicand}; r_result<=8'b0; i<=i+1; end 1,2,3,4: begin if(multiplier[i-1]) begin r_result<=r_result+intermediate; end intermediate<={intermediate[6:0],1'b0}; i<=i+1; end 5: begin r_done_sig<=1'b1;

i<=i+1; end 6: begin r_done_sig<=1'b0; i<=1'b0; end endcase end assign result=r_done_sig?r_result:8'bz; assign done_sig=r_done_sig; endmodule3 测试基准: `timescale 1 ps/ 1 ps module multiplier_simulation(); reg clk; reg rst; reg [3:0]multiplicand; reg [3:0]multiplier; reg start_sig; wire done_sig; wire [7:0]result; /***********************************/ initial begin rst = 0; #10; rst = 1; clk = 1; forever #10 clk = ~clk; end /***********************************/ multiplier U1 ( .clk(clk), .rst(rst), .multiplicand(multiplicand), .multiplier(multiplier), .result(result), .done_sig(done_sig), .start_sig(start_sig) ); reg [3:0]i; always @ ( posedge clk or negedge rst ) if( !rst )

数 字 钟 实 验 报 告 课 程: 专业班级: 学生姓名: 学 号: 2014年 12月 22 日

多功能数字钟设计 一、设计任务 设计一多功能数字钟并进行仿真以及PCB制版。 二、设计要求 基本功能:准确计时,以数字形式显示时、分、秒的时间。 扩展功能:校正时间 PCB制版要求:尽量单面板、尺寸为200mm*150mm、焊孔0.5mm等三、设计方案 数字钟设计方案基本框图如下: 时的设计: 时的计数以24小时为周期,按通常的习惯,24小时计数器的计数序列为00,01,…,22,23,00,…,即当计数到23小时59分59秒时,再来一个秒脉冲,计数器就进到00时00分00秒。这样,可利用反馈置数或反馈清零法进行二十四进制计数。 分、秒的设计: 分和秒计数器都是模M=60的计数器。计数规律为00,01,…,58,59,00,…。它们的个位都是十进制,而十位则是六进制。 译码显示: 将计数器输出的4位二进制代码,译码显示出相应的十进制数状态,可利用译码显示器和数码管实现。 校时电路: 校时可用1s脉冲快速校正,也可手动产生单次脉冲慢校正至时或者分计数器。可设置变量来控制实现校正或正常计数。 四、Multisim仿真与分析

1、设计方案与模块框图 2、各子模块电路设计及原理说明 (1)振荡器 石英晶体振荡器的特点是振荡频率准确、电路结构简单、频率易调整。它还具有压电效应,在晶体某一方向加一电场,则在与此垂直的方向产生机械振动,有了机械振动,就会在相应的垂直面上产生电场,从而机械振动和电场互为因果,这种循环过程一直持续到晶体的机械强度限止时,才达到最后稳定。这用压电谐振的频率即为晶体振荡器的固有频率。 一般来说,振荡器的频率越高,计时精度越高,但耗电量将增大。如果精度要求不高也可以采用由集成电路定时器555与RC组成的多谐振荡器。如图1所示。 图1 ②分频器 由于振荡器产生的频率很高,要得到秒脉冲,需要分屏电路。本实验由集成

AMI、HDB3码实验 1、说明AMI码和HDB3码的特点,及其变换原则。 回答: AMI码的特点:1、无直流成分,低频成分也少,高频成分少,信码能量集中在fB/2处; 2、码型有了一定的检错能力,检出单个误码; 3、当连0数不多时可通过全波整流法提取时钟信息,但是连0数过多时就无法正常地提出时钟信息。 变换规则:二进码序列中“0”仍编为“0”;而二进码序列中的“1”码则交替地变为“+1”码及“-1”码。 HDB3码的特点:1、无直流成分,低频成分也少,高频成分少,信码能量集中在fB/2处; 2、码型有了一定的检错能力,检出单个误码; 3、可通过全波整流法提取时钟信息。 变换规则:(1)二进制信号序列中的“0”码在HDB3码中仍编为“0”码,二进制信号中“1”码,在HDB3码中应交替地成+1和-1码,但序列中出现四个连“0”码时应按特殊规律编码; (2)二进制序列中四个连“0”按以下规则编码:信码中出现四个连“0”码时,要将这四个连“0”码用000V或B00V取代节来代替(B和V也是“1”码,可正、可负)。这两个取代节选取原则是,使任意两个相邻v脉冲间的传号数为奇数时选用000V取代节,偶数时则选用B00V取代节。 2、示波器看到的HDB3变换规则与书本上和老师讲的有什么不同,为什么有这个差别。 回答:示波器上看到的HDB3编码器的输出P22点的波形比书本上的理论上的输出波形要延时5个码位。原因是实验电路中采用了由4个移位寄存器和与非门组成的四连零测试模块去检测二进制码流中是否有四连零,因此输出的HDB3码有5个码位的延时。 3、用滤波法在信码中提取定时信息,对于HDB3码要作哪些变换,电路中如何实现这些变换。 回答:首先,对HDB3码进行全波整流,把双极性的HDB3码变成单极性的归零码,这个在电路上是通过整流二极管实现的;然后,把归零码经晶体管调谐电路进行选频,提取时钟分量;最后,对提取的时钟分量进行整形来产生定时脉冲。 PCM实验思考题参考答案 1.PCM编译码系统由哪些部分构成?各部分的作用是什么? 回答: 其中,低通滤波器:把话音信号带宽限制为3.4KHz,把高于这个频率的信号过滤掉。

基带传输系统实验报告 一、 实验目的 1、 提高独立学习的能力; 2、 培养发现问题、解决问题和分析问题的能力; 3、 学习matlab 的使用; 4、 掌握基带数字传输系统的仿真方法; 5、 熟悉基带传输系统的基本结构; 6、 掌握带限信道的仿真以及性能分析; 7、 通过观察眼图和星座图判断信号的传输质量。 二、 实验原理 在数字通信中,有些场合可以不经载波调制和解调过程而直接传输基带信号,这种直接传输基带信号的系统称为基带传输系统。 基带传输系统方框图如下: 基带脉冲输入 噪声 基带传输系统模型如下: 信道信号 形成器 信道 接收 滤波器 抽样 判决器 同步 提取 基带脉冲

各方框的功能如下: (1)信道信号形成器(发送滤波器):产生适合于信道传输的基带信号波形。因为其输入一般是经过码型编码器产生的传输码,相应的基本波形通常是矩形脉 冲,其频谱很宽,不利于传输。发送滤波器用于压缩输入信号频带,把传输 码变换成适宜于信道传输的基带信号波形。 (2)信道:是基带信号传输的媒介,通常为有限信道,如双绞线、同轴电缆等。信道的传输特性一般不满足无失真传输条件,因此会引起传输波形的失真。另 外信道还会引入噪声n(t),一般认为它是均值为零的高斯白噪声。 (3)接收滤波器:接受信号,尽可能滤除信道噪声和其他干扰,对信道特性进行均衡,使输出的基带波形有利于抽样判决。 (4)抽样判决器:在传输特性不理想及噪声背景下,在规定时刻(由位定时脉冲控制)对接收滤波器的输出波形进行抽样判决,以恢复或再生基带信号。 (5)定时脉冲和同步提取:用来抽样的位定时脉冲依靠同步提取电路从接收信号中提取。 三、实验内容 1采用窗函数法和频率抽样法设计线性相位的升余弦滚讲的基带系统(不调用滤波器设计函数,自己编写程序) 设滤波器长度为N=31,时域抽样频率错误!未找到引用源。o为4 /Ts,滚降系数分别取为0.1、0.5、1, (1)如果采用非匹配滤波器形式设计升余弦滚降的基带系统,计算并画出此发送滤波器的时域波形和频率特性,计算第一零点带宽和第一旁瓣衰减。 (2)如果采用匹配滤波器形式设计升余弦滚降的基带系统,计算并画出此发送滤波器的时域波形和频率特性,计算第一零点带宽和第一旁瓣衰减。 (1)非匹配滤波器 窗函数法: 子函数程序: function[Hf,hn,Hw,w]=umfw(N,Ts,a)

EDAⅡ实验报告 --多功能数字钟 学院专业: 学生学号: 指导老师:蒋立平 交稿时间:2012年3月25日

摘要 本实验借助于quartusⅡ软件设计一个多功能的数字时钟,具有24小时计时、星期显示、保持、清零、校分校时校星期、整点报时等基本功能,并在此基础上添加了闹钟、音乐闹钟、秒表等附加功能。同时,留有万年历的接口可以方便的进行扩展。.利用quartusⅡ进行相应的设计、仿真、调试,最后下载到SmartSOPC实验系统上验证设计的正确性。 关键词:多功能数字时钟,quartusⅡ,计时,星期显示,整点报时,闹钟,秒表 ABSTRACT This experiment is to design a multifunctional digital clock with quartus Ⅱ.The multifunctional digital clock has varities of the functions like 24-hour timer,week,keeping,clearing zero,adjusting time and chime on integral hour .It also include additional functions such as alarm clock,stopwatch and so on.At the sametimes,it can be added calendar.we designed and simulated with quartusⅡ.Finally downloaded it to the experiment platform to test. Key words:multifunctional digital clock,quartusⅡ,time,week,chime on integral hour, alarm clock,stopwatch

交通大学数字电子技术实验报告 数字钟设计 姓名:** 学院:**学院 班级:**22 学号:212******5

一、实验名称 基于Verilog HDL设计的多功能数字钟 二、试验任务及要求 实验要求以Verilog HDL语言为手段,设计多功能数字钟。多功能数字钟应该具有的功能有:显示时—分—秒、整点报时、小时和分钟可调等基本功能。整个钟表的工作应该是在1Hz信号的作用下进行,这样每来一个时钟信号,秒增加1秒,当秒从59秒跳转到00秒时,分钟增加1分,同时当分钟从59分跳转到00分时,小时增加1小时,小时的围为0~23时。 在实验中为了显示与编写方便,该设计采用一个位24位二进制码[23:0]cnt 记录时间,每四位记录一个数,从高到低分别为时针十位、时针个位、分针十位、分针个位、秒针十位、秒针个位。 实验中由于七段码管是扫描的方式显示,所以虽然时钟需要的是1Hz时钟信号,但是扫描需要一个比较高频率的信号,因此为了得到准确的1Hz信号,必须对输入的系统时钟50Mhz进行分频。 关于调整时间功能,该设计采用四个按钮调整对应位的数值,从而调整时间。 三、实验条件 该实验以Verilog HDL语言为手段,以Xilinx ISE Design Suite 13.4_1软件实现源程序的综合与仿真,并用BASYS2开发板作为目标器件。 四、设计过程 1.列写多功能数字钟设计--层次结构图

2.拟定数字钟的组成框图,在Xilinx ISE Design Suite 1 3.4_1软件中,使用Verilog语言输入,采用分层次分模块的方法设计电路; 3.设计各单元电路并进行仿真; 4.对数字钟的整体逻辑电路图,选择器件,分配引脚,进行逻辑综合; 5.下载到Basys2实验平台上,实际测试数字钟的逻辑功能。 五、Verilog代码 module clock(input clk, input en, input key1, input key2, input key3, input key4, output sec, output wire[7:0] seg, output wire[3:0] digit ); wire[3:0] num0,mum1,num2,num3; disp u0(clk,num0,mum1,num2,num3,seg,digit); clk_gen u1(clk,en,key1,key2,key3,key4,sec,num0,mum1,num2,num3); endmodule

4PSK和4ASK的MATLAB仿真 一、实验目的: 学会利用MATLAB软件进行4PSK和4ASK调制的仿真。通过实验提高学生实际动手能力和编程能力,为日后从事通信工作奠定良好的基础。 二、实验内容:利用MATLAB软件编写程序,画出4PSK和4ASK图形,进一步了解4PSK和4ASK调制的原理。 (1)设二进制数字序列为0 1 0 1 1 0 0 0 1 1 0 1 0 0,编程产生4PSK调制信号波形。 (2)设二进制数字序列为1 1 0 0 1 1 0 0 1 0 0 1 1 1,编程产生4ASK调制信号波形。 三、程序和实验结果: (1)4PSK程序 clf clc clear T=1; M=4; fc=1/T; N=500; delta_T=T/(N-1); input=[0 1 0 1 1 0 0 0 1 1 0 1 0 0] input1=reshape(input,2,7) t=0:delta_T:T for i=1:7 hold on if input1([1 2],i)==[0;0] u=cos(2*pi*fc*t);plot(t,u) elseif input1([1 2],i)==[1;0] u=cos(2*pi*fc*t+2*pi/M);plot(t,u) elseif input1([1 2],i)==[1;1] u=cos(2*pi*fc*t+4*pi/M);plot(t,u) elseif input1([1 2],i)==[0;1] u=cos(2*pi*fc*t+6*pi/M);plot(t,u) end t=t+T end grid hold off 实验结果:

Digital Communication Project 姓名:王志卓 学号:514104001502

在PSK调制时,载波的相位随调制信号状态不同而改变。如果两个频率相同的载波同时开始振荡,这两个频率同时达到正最大值,同时达到零值,同时达到负最大值,此时它们就处于―同相‖状态;如果一个达到正最大值时,另一个达到负最大值,则称为―反相‖。把信号振荡一次(一周)作为360度。如果一个波比另一个波相差半个周期,两个波的相位差180度,也就是反相。当传输数字信号时,―1‖码控制发0度相位,―0‖码控制发180度相位。 PSK相移键控调制技术在数据传输中,尤其是在中速和中高速的数传机(2400bit/s~4800bit/s)中得到了广泛的应用。相移键控有很好的抗干扰性,? 在有衰落的信道中也能获得很好的效果。主要讨论二相和四相调相,在实际应用中还有八相及十六相调相。 PSK也可分为二进制PSK(2PSK或BIT/SK)和多进制PSK(MPSK)。在这种调制技术中,载波相位只有0和π两种取值,分别对应于调制信号的―0‖和―1‖。传―1―信号时,发起始相位为π的载波;当传―0‖信号时,发起始相位为0的载波。由―0‖和―1‖表示的二进制调制信号通过电平转换后,变成由―–1‖和―1‖表示的双极性NRZ(不归零)信号,然后与载波相乘,即可形成2PSK信号,在MPSK中,最常用的是四相相移键控,即QPSK (QuadraturePhaseShiftKeying),在卫星信道中传送数字电视信号时采用的就是QPSK调制方式。可以看成是由两个2PSK调制器构成的。输入的串行二进制信息序列经串—并变换后分成两路速率减半的序列,由电平转换器分别产生双极性二电平信号I(t)和Q(t),然后对载波Acos2πfct和Asin2πfct进行调制,相加后即可得到QPSK信号。 PSK信号也可以用矢量图表示,矢量图中通常以零度载波相位作为参考相位。四相相移调制是利用载波的四种不同相位差来表征输入的数字信息,是四进制移相键控。QPSK是在M=4时的调相技术,它规定了四种载波相位,分别为45°,135°,225°,315°。调制器输入的数据是二进制数字序列,为了能和四进制的载波相位配合起来,则需要把二进制数据变换为四进制数据,这就是说需要把二进制数字序列中每两比特分成一组,共有四种组合,即00,01,10,11,其中每一组称为双比特码元。每一个双比特码元是由两位二进制信息比特组成的,它们分别代表四进制四个符号中的一个符号。QPSK中每次调制可传输2

大连理工大学本科实验报告题目:多功能数字钟 课程名称:《数字电路课程设计》 学院(系):电子信息与电气工程学部 专业:自动化 班级:电自0801 学生姓名: 学号:200881142 完成日期:2011年7月20日 成绩: 2011 年7 月20 日

题目:多功能数字钟 1 设计要求 (1)一个具有“时”,“分”,“秒”的十进制数字显示(小时从00~23) 计时器。 (2)具有手动校时,校分的功能。 (3)定时与闹钟功能,能在设定的时间发出闹铃声 (4)能整点报时。要求从59分54秒起报时,每隔2秒发出低音,,连续 3次,在整点要求是高音。 2 设计分析及系统方案设计 系统总体结果 系统设计要求说明: (1)该秒表用模24、模60计数器实现24小时计时 (2)在调节闹钟时不影响数字钟的正常走表; (3)在调节闹钟时要通过数码管显示出; 3系统以及模块硬件电路设计 根据上述给出的系统总体结构框图,给出系统硬件电路设计,并作必要的说明和理论计算。由于“数字电路课程设计”课程采用实验箱完成,没有学时涉及有关FPGA芯片的使用,因此有关FPGA芯片的部分可以用“FPGA最小系统”

模块框代替。其余接口部分(按键,LED以及数码管,各种接口等需要设计电路以及参数)。 下载时选择的开发系统模式以及管脚定义 4 系统的VHDL设计 系统的各个部分如何用VHDL设计出来的应该有说明,包括论述以及真值表或者状态图等。 要求:系统(或顶层文件)结构描述,各个模块(或子程序)的功能描述;1)用原理图实现的,需包含以下内容: (1)系统原理图

(2)主要模块或符号说明; 主要模块:模60计数器,模24计数器, 2)用VHDL语言实现的 (1) 秒计数器(模60计数器) library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; entity m_601 is port(clk: in std_logic; clk_1: out std_logic; --clk_1表进位 qh,ql:out std_logic_vector(3 downto 0) –qh,ql表示十位与个位); end; architecture a of m_601 is signal qqh,qql: std_logic_vector(3 downto 0); signal tmp: std_logic; begin process(clk) begin if clk'event and clk='1' then if qql=9 then qql<="0000"; if qqh=5 then