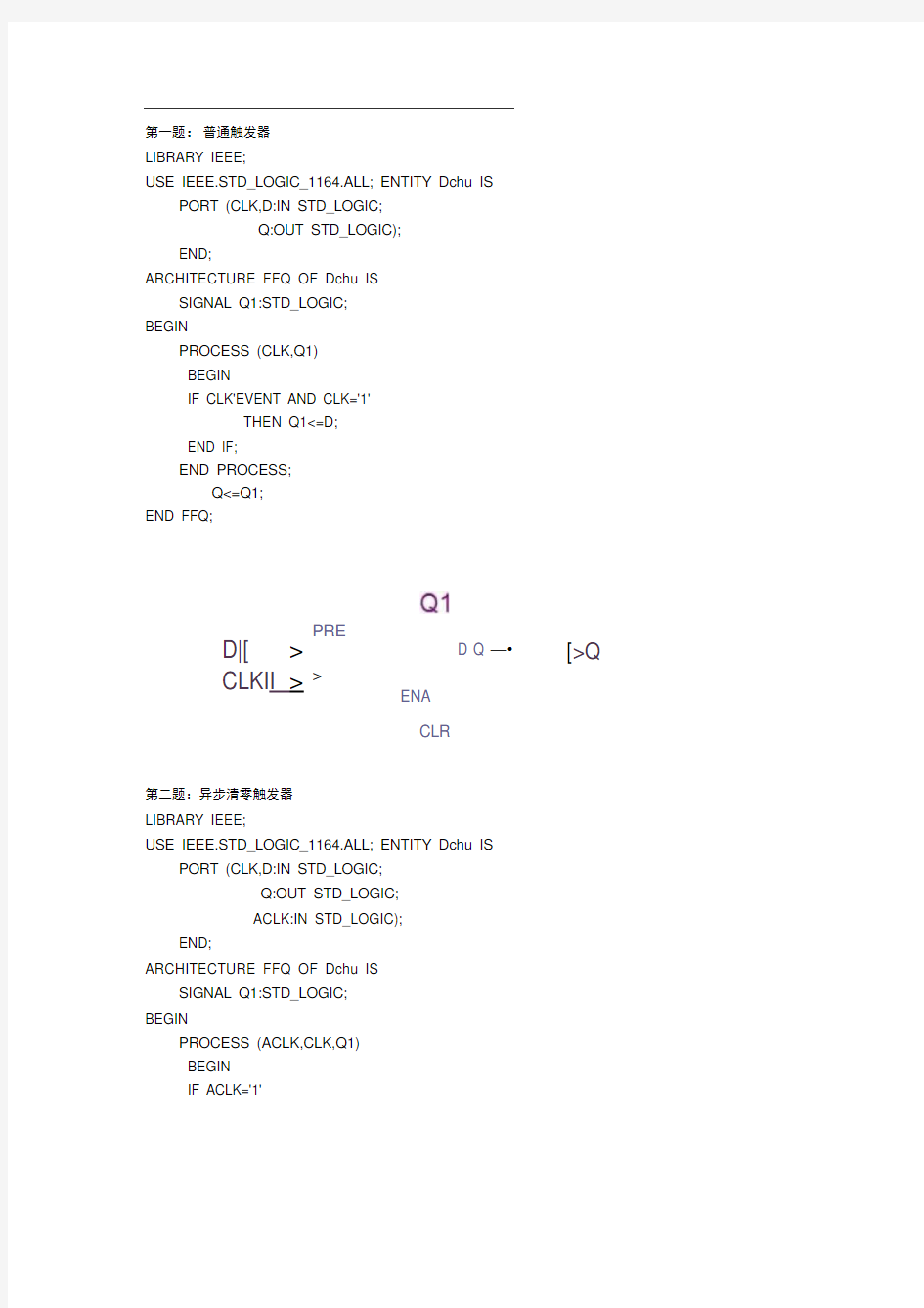

第一题:普通触发器

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL; ENTITY Dchu IS

PORT (CLK,D:IN STD_LOGIC;

Q:OUT STD_LOGIC);

END;

ARCHITECTURE FFQ OF Dchu IS

SIGNAL Q1:STD_LOGIC;

BEGIN

PROCESS (CLK,Q1)

BEGIN

IF CLK'EVENT AND CLK='1'

THEN Q1<=D;

END IF;

END PROCESS;

Q<=Q1;

END FFQ;

PRE

D Q —?

>

ENA

CLR

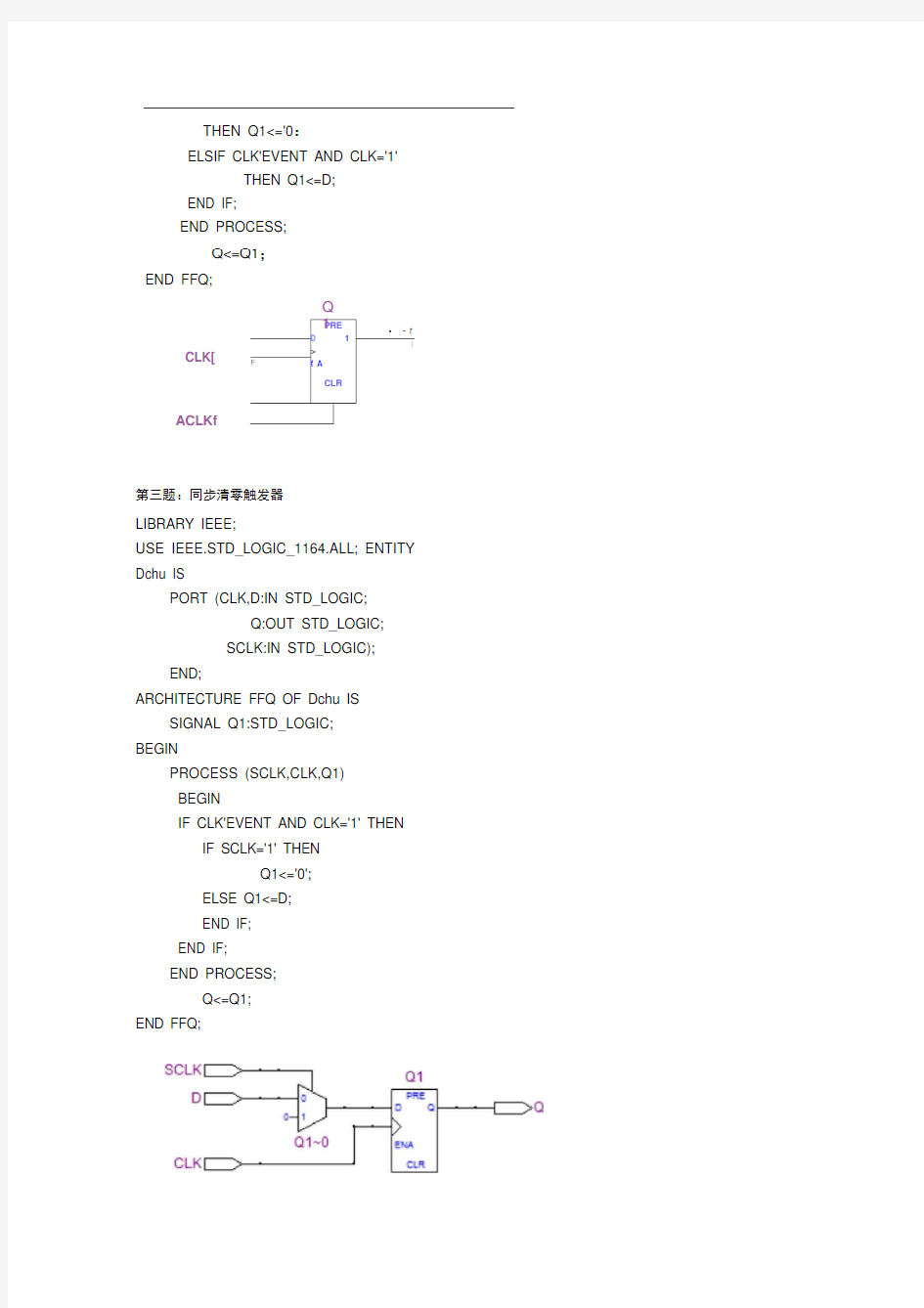

第二题:异步清零触发器

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL; ENTITY Dchu IS

PORT (CLK,D:IN STD_LOGIC;

Q:OUT STD_LOGIC;

ACLK:IN STD_LOGIC);

END;

ARCHITECTURE FFQ OF Dchu IS

SIGNAL Q1:STD_LOGIC;

BEGIN

PROCESS (ACLK,CLK,Q1)

BEGIN

IF ACLK='1'

D|[ >

CLKII >

[>Q

THEN Q1<='0:

ELSIF CLK'EVENT AND CLK='1'

THEN Q1<=D;

END IF;

END PROCESS;

Q<=Q1;

END FFQ;

第三题:同步清零触发器

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL; ENTITY Dchu IS

PORT (CLK,D:IN STD_LOGIC;

Q:OUT STD_LOGIC;

SCLK:IN STD_LOGIC);

END;

ARCHITECTURE FFQ OF Dchu IS

SIGNAL Q1:STD_LOGIC;

BEGIN

PROCESS (SCLK,CLK,Q1)

BEGIN

IF CLK'EVENT AND CLK='1' THEN

IF SCLK='1' THEN

Q1<='0';

ELSE Q1<=D;

END IF;

END IF;

END PROCESS;

Q<=Q1;

END FFQ;

ACLKf PRE D 1 > f A CLR ? - r | F

Q 1 CLK[

第四题:异步置位apre

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL; ENTITY Dchu IS

PORT (

CLK : IN STD_LOGIC;

D : IN STD_LOGIC;

Q :OUT STD_LOGIC;

APRE :IN STD_LOGIC

);

END;

ARCHITECTURE FFQ OF Dchu IS SIGNAL Q1:STD_LOGIC; BEGIN

PROCESS (APRE,CLK,Q1)

BEGIN

IF APRE='1'

THEN Q1<='1';

ELSIF CLK'EVENT AND CLK='1'

THEN Q1<=D;

END IF;

END PROCESS;

Q<=Q1;

END FFQ;

APRE 、??

第五题:同步置位spre

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL; ENTITY Dchu IS

PORT (

CLK : IN STD_LOGIC;

D : IN STD_LOGIC;

Q :OUT STD_LOGIC;

SPRE :IN STD_LOGIC

);

END;

ARCHITECTURE FFQ OF Dchu IS

SIGNAL Q1:STD_LOGIC;

BEGIN

PROCESS (SPRE,CLK,Q1)

BEGIN

IF CLK'EVENT AND CLK='1' THEN IF SPRE='1' THEN

Q1<='1:

ELSE Q1<=D;

END IF;

END IF;

END PROCESS;

Q<=Q1;

END FFQ;

第六题:异步清零,异步置位

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL; ENTITY Dchu IS

PORT (

CLK : IN S TD_LOGIC;

ACLR : IN S TD_LOGIC;

APRE : IN S TD_LOGIC;

D : IN S TD_LOGIC;

Q :OUT STD_LOGIC

);

END;

ARCHITECTURE FFQ OF Dchu IS

SIGNAL Q1:STD_LOGIC;

BEGIN

PROCESS (APRE,ACLR,CLK,Q1)

BEGIN

IF ACLR='1' THEN

Q1<='0';

ELSIF APRE='1'

THEN Q1<='1';

ELSIF CLK'EVENT AND CLK='1'

THEN Q1<=D;

END IF;

END PROCESS;

Q<=Q1; END FFQ;

comb-0

D

>

CLFt

第七题:同步使能

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY Dchu IS

PORT (

CLK : IN STD_LOGIC;

D : IN STD_LOGIC;

Q :OUT STD_LOGIC;

EN : IN STD_LOGIC

);

END;

ARCHITECTURE FFQ OF Dchu IS

SIGNAL Q1:STD_LOGIC;

BEGIN

PROCESS (EN,CLK,Q1)

BEGIN

IF CLK'EVENT AND CLK='1' THEN

IF EN='1' THEN

Q1<=D;

END IF;

END IF;

END PROCESS;

Q<=Q1;

END FFQ;

Q1

pp

OLE

第八题:异步清零,置位,同步使能

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ACLRI------ >

APREI >

DI >

CLKI >

ENTITY Dchu IS

PORT (

END;

ARCHITECTURE FFQ OF Dchu IS

SIGNAL Q1:STD_LOGIC;

BEGIN

PROCESS (APRE,ACLR,EN,CLK,Q1)

BEGIN

IF ACLR='1' THEN

Q1<='0';

ELSIF APRE='1'

THEN Q1<='1';

ELSIF CLK'EVENT AND CLK='1' THEN IF EN='1' THEN

Q1<=D;

END IF;

END IF;

END PROCESS;

Q<=Q1;

END FFQ;

CL% CLK

EN

ACLR

APRE

Q

);

IN STD_LOGIC;

IN STD_LOGIC;

IN STD_LOGIC;

IN STD_LOGIC;

IN STD_LOGIC;

OUT STD LOGIC

CLKI >

camt)*0