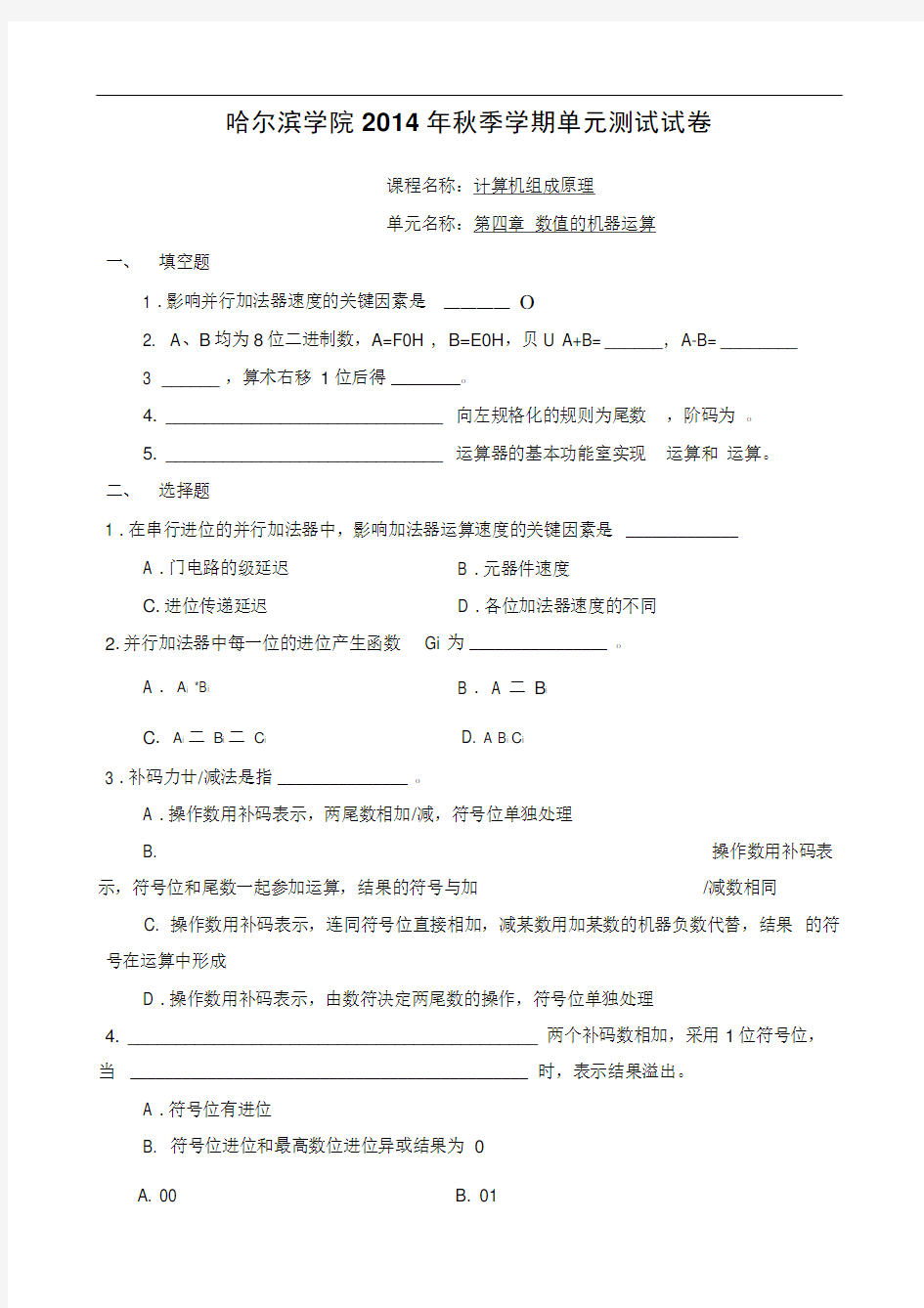

哈尔滨学院2014年秋季学期单元测试试卷

课程名称:计算机组成原理 单元名称:第四章 数值的机器运算

一、 填空题

1 .影响并行加法器速度的关键因素是 ________ O

2. A 、B 均为8位二进制数,A=F0H , B=E0H ,贝U A+B= ______ , A-B= ________ 3 ______ ,算术右移 1位后得 ________ O

4. _____________________________ 向左规格化的规则为尾数 ,阶码为

O

5. _____________________________ 运算器的基本功能室实现 运算和 运算。 二、 选择题

1 .在串行进位的并行加法器中,影响加法器运算速度的关键因素是 _____________

A .门电路的级延迟 C .进位传递延迟

2.并行加法器中每一位的进位产生函数 A . A i *B i

C . A i 二 B i 二 C i

D. A B i C i

3 .补码力廿/减法是指 _______________ O

A .操作数用补码表示,两尾数相加/减,符号位单独处理 B.

操作数用补码表示,符号位和尾数一起参加运算,结果的符号与加

/减数相同

C. 操作数用补码表示,连同符号位直接相加,减某数用加某数的机器负数代替,结果 的符号在运算中形成

D .操作数用补码表示,由数符决定两尾数的操作,符号位单独处理

4. ___________________________________________ 两个补码数相加,采用1位符号位,当 ______________________________________________ 时,表示结果溢出。

A .符号位有进位

B. 符号位进位和最高数位进位异或结果为 0 B .元器件速度

D .各位加法器速度的不同

Gi 为

________________ O

B . A 二 B i

C. 符号位为1

D .符号位进位和最高数位进位异或结果为1

5. ____________________________________________________________ 在双符号位判断溢出的方案中,出现正溢时,双符号位应当为___________________________ O

C. 10

D. 11

6. __________________________________________________ 在定点机中执行算术运算时会产生溢出,其原因是 _____________________________________

8. _________ 。

A. B .

C.

D

9.将用8位二进制补码表示的十进制数-121,扩展成16位二进制补码,结果用十六进制表 示为 ____________ 。

A. 0087H D . FFF9H

B. 18H D. F1H

1位则数值 ,若小数点右移 1位则数

B .扩大一倍,缩小一半 D. 缩小一半,缩小一半

1位符号位,n 位数值位。若采用Booth 补码一位乘法

实现乘法运算,则最多需要做加法运算的次数是 ______________

A. n-1 C. n+1

D. n+2

13 .原码加减交替除法又称为不恢复余数法,因此 __________________

A .不存在恢复余数的操作

B. 当某一步运算不够减时,做恢复余数的操作 C .仅当最后一步余数为负时,做恢复余数的操作 D .当某一步余数为负时,做恢复余数的操作

A .主存容量不够 C .操作数地址过大

7. 当定点运算发生溢出时,应进行

A. 向左规格化

C .发出出错信息 B .操作数过大

D .运算结果无法表示

B. 向右规格化 D .舍入处理

B . FF87H

C . 8079H

10

.已知中补=泅,计算机的机器字长为 8位二进制编码,则[X ]补= _______ A .8CH C. E3H

11 .对于二进制数,若小数点左移 值 _________ 。

A .扩大一倍,扩大一倍

C .缩小一半,扩大一倍

12. X 、丫为定点二进制数,其格式为

14?在加法器、寄存器的基础上增加部分控制电路实现除法时,用

B 寄存器存放

A .被乘数和被除数 B. 被乘数和除数 C. 乘数和被除数 D .乘数和除数

15. ___________________________________________________________ 若浮点数用补码表示,判断运算结果是否是规格化数的方法是 _____________________________

17. 4片 74181ALU 和1片74182CLA 相配合,具有 ______ 传递功能。

A. 串行进位 B .组内并行进位,组间串行进位

C. 组内串行进位,组间并行进位 D .组内、组间

均为并行进位

18. ____________________________________________ 运算器虽由许多部件组成,但核心部件是 ______________________________________________ o

A .算术逻辑运算单元

B .多路开关

C .数据总线

D .累加寄存器

19. ____________________________ 下列叙述中,错误的是 o

A .运算器中通常都有一个状态标志寄存器,为计算机提供判断条件,以实现程序转 移 B. 补码乘法器中,被乘数和乘数的符号都不参加运算 C. 并行加法器中高位的进位依赖于低位

D .在小数除法中,为了避免溢出,要求被除数的绝对值小于除数的绝对值 20. _______________________ 计算机中的累加器 o

A .没有加法器功能,也没有寄存器功能 B. 没有加法器功能,有寄存器功能 C. 有加法器功能,没有寄存器功能 A .阶符与数符相同

C. 数符与尾数最高有效位相同 16. 若浮点数用补码表示,一个数的阶码值为

较小的浮点数的小数点 _______ 。

A. 左移1位

B .阶符与数符相异

D .数符与尾数最高有效位相异

7,另一个数的阶码值为9,则需要将阶码值

B. 右移1位 D.右移2位

21. 一个C语言程序在一台32位机器上运行。程序中定义了3个变量x、y和z,其中x

和z

为int型,y为short型。当x=127、y=-9时,执行赋值语句z=x+y后,x、y和z的值分别是 __

A ? x =0000007FH , y =FFF 9H, z =00000076H

B . x =0000007FH , y =FFF 9H ,z =FFFF 0076H

C. x=0000007FH,y 二FFF7H,z =FFFF 0076H

D . x =0000007FH,y 二FFF 7H , z =00000076H

22. 浮点数加、减运算一般包括对阶、尾数运算、规格化、舍入和判断溢出等步骤。

设浮点数的阶码和尾数均采用补码表示,并且位数分别为5位和7位(均含2位符号位)。若有两个数X =2729/32,丫=:255/8,则用浮点加法计算X Y的最终结果是______________ 。

A. 00111 1100010

B. 00111 0100010

C. 01000 0010001

D.发生溢出

23. 假定有4个整数用8位补码分别表示为 A =FEH、b =F2H、r3 =90H、q =F8H。若

将运算结果存放在一个8位寄存器中,则下列运算会发生溢出的是 _________ 。

A. r1r2

B. r2r3

C. r1r4

D. r2r4

24. 某字长为8位的计算机汇总,已知整型变量x、y的机器数分别为[X]补=10000100,[Y]补=10110000。若整型变量z =2 x y/2,则z的机器数为____________ 。

A. 1 1000000

B. 00100100

C. 1 0101010

D.溢出

25. __ 若x=103,y=~25,则下列表达式采用8位定点补码运算实现时,会发生溢出的是。

A. x y

B. -x y

D. -x - y

C. x - y

三、判断题

1. 进位信号串行传递的加法器称为串行加法器。

2. 进位产生函数为R二A i二B i。

3. 运算器中设置了加法器后就没有必要设置减法器

4?浮点数对阶的原则是大阶向小阶看齐。

5?运算器不仅可以完成数据信息的算逻运算,还可以作为数据信息的传送通路。

6. 80387被称为协处理器,本身不能单独使用

四、简答题

1简述浮点运算中溢出的处理问题。

2?试述先行进位解决的问题及基本思想。

3?串行加法器和并行加法器有何不同?影响并行加法器的关键因素是什么?设低位来的进位信号为C o,请分别按下列两种方式写出C4、C3、C2、C l的逻辑表达式。

(1)串行进位方式

(2)并行进位方式

五、分析题

1某加法器采用组内并行、组间并行的进位链, 达

4位一组,写出进位信号C6的逻辑表式。

2.写出一位2421码加法器的校正函数。

六、计算题

1. 已知X和Y,用变形补码计算X+Y和X-Y,同时指出运算结果是否溢出?

(1) X =空,丫二聖

32 32

(2) X上,丫」

16 16

1

2. 已知[X]补=1.1011000,[Y]补=1.0100110。计算2[X]补[Y]补

3. 已知X =0.10010,Y =-0.10101,

用补码一位乘法计算X Y,要写出详细的运算过程。

X

4. 已知X =0.1000,Y =0.1010,用补码加减交替法求 -^?

5. 已知X -7.25,Y =28.5625,

(1 )将X、丫分别转换成二进制浮点数(阶码占4位,尾数占10位,各包含一位符号

(2)用变形补码,求X -丫 =?

6.有两个浮点数X =210 (0.101),丫 =201 (T.111),设阶符1位,阶码2位,数符1位,尾

数3位,用补码运算规则计算X Y的值。

七、设计题

1利用CLA加法器或BCLA加法器以及CLA电路设计加法器,要求实现如下功能:

(1)构建20位单级先行进位加法器

①使用5个4位的CLAW法器;

②使用4个5位的CLA W法器;

分别画出连接简图(请特别标明进位信号)。比较这两种方法得到的最长进位延迟时间有无区别。

(2)构建20位二级先行进位加法器。

①使用5个4位的BCL加法器和1个5位的CLA电路;

②使用4个5位的BCL加法器和1个4位的CLA电路;

分别画出连接简图(请特别标明进位信号)。比较这两种方法得到的最长进位延迟时间有无区别。

2. 利用74181和74182芯片设计如下3种方案的32位ALU。

(1)行波进位方案;

(2)二级先行进位方案;

(3)三级先行进位方案。

八、综合应用题

假定在一个8位字长的计算机中运行下列类C程序段:

Unsigned int x=134;

Unsigned int y=26;

Int m=x;

Int n=y;

Unsigned int z1=x-y?;

Unsigned int z2=x+y?;