Two or three shunt resistor based current sensing circuit design in 3-phase inverters

- 格式:pdf

- 大小:1.17 MB

- 文档页数:14

Texas Instruments, Inc. C2000 Systems and Applications2012Digital Motor ControlSoftware Library: F2803x DriversContentsINTRODUCTION (3)ADC_ILEG_DRV (4)BLDC_PWM_DRV (6)CAP_EVENT_DRV (11)DATALOG (14)HALL3_DRV (19)PWMDAC_DRV (26)PWMDRV (30)QEP_DRV (33)IntroductionThe digital motor control library is composed of C functions (or macros) developed for C2000 motor control users. These modules are represented as modular blocks in C2000 literature in order to explain system-level block diagrams clearly by means of software modularity. The DMC library modules cover nearly all of the target-independent mathematical macros and target-specific peripheral configuration macros, which are essential for motor control. These modules can be classified as:Transformation and Observer Modules Clarke, Park, Phase Voltage Calculation, Sliding Mode Observer, BEMF Commutation, Direct Flux Estimator, Speed Calculators and Estimators, Position Calculators and Estimators etc.Signal Generators and Control Modules PID, Commutation Trigger Generator, V/f Controller, Impulse Generator, Mod 6 Counter, Slew Rate Controllers, Sawtooth & Ramp generators, Space Vector Generators etc.Peripheral Drivers PWM abstraction for multiple topologies and techniques, ADC Drivers,Hall Sensor Driver, QEP Driver, CAP Driver etc.Real-Time Debugging Modules DLOG module for CCS graph window utility, PWMDAC module for monitoring the control variables through socilloscopeIn the DMC library, each module is separately documented with source code, use, and background technical theory. All DMC modules allow users to quickly build, or customize their own systems. The library supports three principal motor types (induction motor, BLDC and PM motors) but is not limited to these motors.The DMC library components have been used by TI to provide system-level motor control examples. In the motor control code, all DMC library modules are initialized according to the system specific parameters, and the modules are inter-connected to each other. At run-time the modules are called in order. Each motor control system is built using an incremental build approach, which allows some sections of the code to be built at a time, so that the developer can verify each section of the application one step at a time. This is critical in real-time control applications, where so many different variables can affect the system, and where many different motor parameters need to be tuned.Software LibraryADC Driver Description This module allows the user to configure analog-to-digital conversion (ADC) channels. The conversions are triggered on end of conversion (EOC) which is setto 4th conversion by default. In DMC projects, the converted results representload currents and DC-bus voltage but not limited to these.Availability C interface versionModule Properties Type: Target Dependent, Application IndependentTarget Devices: 28x Fixed PointC Version File Names: f2803xileg_vdc.h (for x2803x)IQmath library files for C: N/AC InterfaceC InterfaceModule UsageInstantiationThere is no instantiation for ADC configuration.Initialization// Default ADC initializationint ChSel[16] = Default_ch_sel; int TrigSel[16] = Default_trig_sel;int ACQPS[16] = Default_ACQPS;whereChSel [ ] stores which ADC pin is used for conversion when a Start of Conversion (SOC) trigger is received for the respective channelTrigSel [ ] stores what trigger input starts the conversion of the respective channelACQPS [ ] stores the acquisition window size used for the respective channelInvoking the computation macro ChSel[0]=x; ChSel[1]=y;ChSel[2]=z;Examplemain() { ChSel[1]=1; // ChSelect: ADC A1-> Phase A Current ChSel[2]=9; // ChSelect: ADC B1-> Phase B Current ChSel[3]=3; // ChSelect: ADC A3-> Phase C Current ChSel[7]=10; // ChSelect: ADC B2-> DC Bus Voltage ADC_MACRO_INIT(ChSel,TrigSel,ACQPS) // Call init macro for ADC INIT }void interrupt periodic_interrupt_isr() {clarke1.As = _IQmpy2(_IQ12toIQ(AdcResult.ADCRESULT1)-offsetA); // Phase A curr. clarke1.Bs = _IQmpy2(_IQ12toIQ(AdcResult.ADCRESULT2)-offsetB); // Phase B curr. volt1.DcBusVolt = _IQ12toIQ(AdcResult.ADCRESULT7); // DC Bus voltage meas. }Description This module generates the 6 switching states of a 3-ph power inverter used to drive a 3-ph BLDC motor. These switching states are determined by the inputvariable CmtnPointer. The module also controls the PWM duty cycle bycalculating appropriate values for the compare registers. The duty cycle valuesfor the PWM outputs are determined by the input DutyFunc.Availability C interface versionModule Properties Type: Target Dependent, Application IndependentTarget Devices: 28x Fixed PointIQmath library files for C: IQmathLib.h, IQmath.libC Version File Names: f2803xbldcpwm.h (for x2803x)C InterfaceObject DefinitionThe structure of PWMGEN object is defined by following structure definitiontypedef struct { Uint16 CmtnPointer; // Input: Commutation (or switching) state pointer input (Q0) int16 MfuncPeriod; // Input: Duty ratio of the PWM outputs (Q15)Uint16 PeriodMax; // Parameter: Maximum period (Q0)int16 DutyFunc; // Input: PWM period modulation input (Q15)Uint16 PwmActive; // Parameter: 0 = active low, 1 = active high (0 or 1)} PWMGEN;Special Constants and Data typesPWMGENThe module definition is created as a data type. This makes it convenient to instance an interface to the PWMGEN driver. To create multiple instances of the module simply declare variables oftype PWMGEN.PWMGEN_DEFAULTSStructure symbolic constant to initialize PWMGEN module. This provides the initial values to theThis default definition of the object implements two methods – the initialization and the runtime compute macro for PWMGEN generation. This is implemented by means of a macro pointer, and the initializer sets this to BLDCPWM_INIT_MACRO and BLDCPWM_MACRO macros for x280x.The argument to this macro is the address of the PWMGEN object.Module UsageInstantiationThe following example instances one PWMGEN objectPWMGEN pwm1;InitializationTo Instance pre-initialized objectsInvoking the computation macroBLDCPWM_INIT_MACRO (pwm1);BLDCPWM_MACRO (pwm1);ExampleThe following pseudo code provides the information about the module usage.main(){pwm1.PeriodMax = 7500; // PWM frequency = 20 kHz, clock = 150 MHzBLDCPWM_INIT_MACRO(pwm1); // Call init macro for pwm1 }void interrupt periodic_interrupt_isr(){pwm1.CmtnPointer = (int)(CmtnPointer1); // CmtnPointer1 is in Q0pwm1.DutyFunc = (int)_IQtoIQ15(DutyFunc1); // DutyFunc1 is in GLOBAL_QBLDCPWM_MACRO(pwm1); // Call update macro for pwm1 }Technical BackgroundFigure 1 shows the 3-phase power inverter topology used to drive a 3-phase BLDC motor. In this arrangement, the motor and inverter operation is characterized by a two phases ON operation.This means that two of the three phases are always energized, while the third phase is turned off.This is achieved by controlling the inverter switches in a periodic 6 switching or commutation states. The bold arrows on the wires in Figure 1 indicate the current flowing through two motor stator phases during one of these commutation states. The direction of current flowing into the motor terminal is considered as positive, while the current flowing out of the motor terminal is considered as negative. Therefore, in Figure 1, Ia is positive, Ib is negative and Ic is 0.Figure 1: Three Phase Power Inverter for a BLDC Motor Drive In this control scheme, torque production follows the principle that current should flow in only two of the three phases at a time and that there should be no torque production in the region of Back EMF zero crossings. Figure 2 depicts the phase current and Back EMF waveforms for a BLDC motor during the two phases ON operation. All the 6 switching states of the inverter in Figure 1 are indicated in Figure 2 by S1 through S6. As evident from Figure 2, during each state only 2 of the 6 switches are active, while the remaining 4 switches are turned OFF. Again, between the 2 active switches in each state, the odd numbered switch (Q1or Q3 or Q5) are controlled with PWM signal while the even numbered switch (Q2 or Q4 or Q6) is turned fully ON. This results in motor current flowing through only two of the three phases at a time. For example in state S1, Ia is positive, Ib is negative and Ic is 0. This is achieved by driving Q1 with PWM signals and turning Q4 fully ON. This state occurs when the value in the commutation state pointer variable, CmtnPointer, is 0. Table 1 summarizes the state of the inverter switches.Technical Background and the corresponding values of the related peripheral register, the commutation pointer and the motor phase currents.Figure 2: Phase Current and Back EMF Waveforms in 3-ph BLDC Motor controlTable 1: Commutation States in 3-ph BLDC Motor controlDescription This module provides the instantaneous value of the selected time base (GP Timer) captured on the occurrence of an event. Such events can be anyspecified transition of a signal applied at ECAP input pins of 280x devices.Availability C interface versionModule Properties Type: Target Dependent, Application IndependentTarget Devices: 28x Fixed PointIQmath library files for C: IQmathLib.h, IQmath.libC Version File Names: f2803xcap.h (for x2803x)C InterfaceObject DefinitionThe structure of CAPTURE object is defined by following structure definition for x280x series typedef struct { int32 EventPeriod; // Output: Timer value difference between two edges (Q0)Uint16 CapReturn; // Output: Status of one entry of first event of ECAP pin (Q0)} CAPTURE;Special Constants and Data typesCAPTUREThe module definition is created as a data type. This makes it convenient to instance an interface to the CAPTURE driver. To create multiple instances of the module simply declare variables oftype CAPTURE.CAPTURE_DEFAULTSStructure symbolic constant to initialize CAPTURE module. This provides the initial values to the terminal variables as well as method pointers.This default definition of the object implements two methods – the initialization and the runtime compute macro for CAPTURE generation. This is implemented by means of a macro pointer, and the initializer sets this to CAP_INIT_MACRO and CAP_MACRO macros for x280x. The argument to this macro is the address of the CAPTURE object.Module UsageInstantiationThe following example instances one CAPTURE objectCAPTURE cap1;InitializationTo Instance pre-initialized objectsCAPTURE cap1 = CAPTURE_DEFAULTS;Invoking the computation macroCAP_INIT_MACRO (1); // For cap#1CAP_MACRO (1,cap1);ExampleThe following pseudo code provides the information about the module usage.main(){CAP_INIT_MACRO(1); // Call init macro for cap1}void interrupt periodic_interrupt_isr(){Uint16 CapReturn;Uint32 EventPeriod;CapReturn = CAP_MACRO(1,cap1);// if status==1 then a time stamp was not read,// if status==0 then a time stamp was readif(status==0){EventPeriod=(int32)(cap1.EventPeriod); // Read out new time stamp}}4-Channel Data Logging Utility Module Description This module stores the real-time values of four user selectable software Q15 variables in the data RAM provided on the 28xx DSP. Four variables are selectedby configuring four module inputs, iptr1,iptr2,iptr3 and iptr4, point to the addressof the four variables. The starting addresses of the four RAM locations, where thedata values are stored, are set to DLOG_4CH_buff1, DLOG_4CH_buff2,DLOG_4CH_buff3, and DLOG_4CH_buff4. The DATALOG buffer size,prescalar, and trigger value are also configurable.Availability C interface versionModule Properties Type: Target Dependent, Application IndependentTarget Devices: 28x Fixed PointIQmath library files for C: IQmathLib.h, IQmath.libCcA Version File Names: dlog4chc.asm, dlog4ch.hC InterfaceObject DefinitionThe structure of DLOG_4CH object is defined by following structure definitiontypedef struct { long task; // Variable: Task address pointerint *iptr1; // Input: First input pointer (Q15)int *iptr2; // Input: Second input pointer (Q15)int *iptr3; // Input: Third input pointer (Q15)int *iptr4; // Input: Fourth input pointer (Q15)int trig_value; // Input: Trigger point (Q15)int prescalar; // Parameter: Data log prescaleint skip_cntr; // Variable: Data log skip counterint cntr; // Variable: Data log counterlong write_ptr; // Variable: Graph address pointerint size; // Parameter: Maximum data bufferint (*init)(); // Pointer to init functionint (*update)(); // Pointer to update function} DLOG_4CH;Note: The trigger value is with reference to the input *iptr1. In accordance with this, the input connected to channel 1 should be time varying, and the trigger value should be set up such that input crosses the trigger value.The other channels are captured synchronous to the channel 1. There is no trigger mechanism on channels 2 through 4.Special Constants and Data typesDLOG_4CHThe module definition is created as a data type. This makes it convenient to instance an interface to the DATALOG driver. To create multiple instances of the module simply declare variables oftype DLOG_4CH.DLOG_4CH_handleUser defined Data type of pointer to DATALOG moduleDLOG_4CH_DEFAULTSStructure symbolic constant to initialize DATALOG module. This provides the initial values to the terminal variables as well as method pointers.Methodsint DLOG_4CH_init(DLOG_4CH *);int DLOG_4CH_update(DLOG_4CH *);This default definition of the object implements two methods – the initialization and the runtime update function for DATALOG. This is implemented by means of a function pointer, and the initializer sets this to DLOG_4CH_init and DLOG_4CH_update functions for x281x/x280x. The argument to this function is the address of the DATALOG object.Module UsageInstantiationThe following example instances one DATALOG objectDLOG_4CH dlog1;InitializationTo Instance pre-initialized objectsDLOG_4CH dlog1 = DLOG_4CH_DEFAULTS;Invoking the computation functiondlog1.init(&dlog1);dlog1.update(&dlog1);ExampleThe following pseudo code provides the information about the module usage.main(){dlog1.iptr1 = &Q15_var1; // Pass input to DATALOG moduledlog1.iptr2 = &Q15_var2; // Pass input to DATALOG moduledlog1.iptr3 = &Q15_var3; // Pass input to DATALOG moduledlog1.iptr4 = &Q15_var4; // Pass input to DATALOG module dlog1.trig_value = 0x0; // Pass input to DATALOG moduledlog1.size = 0x400; // Pass input to DATALOG moduledlog1.prescalar = 1; // Pass input to DATALOG moduledlog1.init(dlog1); // Call init function for dlog1}void interrupt periodic_interrupt_isr(){dlog1.update(&dlog1); // Call update function for dlog1 }Technical BackgroundTechnical BackgroundThis software module stores up to four real-time Q15 values of each of the selected input variables in the data RAM as illustrated in the following figures. The starting addresses of four RAM sections, where the data values are stored, are set to DLOG_4CH_buff1, DLOG_4CH_buff2, DLOG_4CH_buff3, and DLOG_4CH_buff4.To show four stored Q15 variables in CCS graphs properly, the properties of two dual timegraphs for these variables should be configured as shown in the following figures. In the software,the default buffer size is 0x400. The sampling rate is usually same as ISR frequency. In this case, it is 20 kHz with the prescalar of 1.DLOG_4CH_buff1 + sizeDLOG_4CH_buff3DLOG_4CH_buff3 + sizeDLOG_4CH_buff4hall signals received on GPIO pins 24, 25, and 26. Edges detected are validatedor debounced, to eliminate false edges often occurring from motor oscillations.The software attempts all (6) possible commutation states to initiate motormovement. Once the motor starts moving, commutation occurs on eachAvailability C interface versionModule Properties Type: Target Dependent, Application IndependentTarget Devices: 28x Fixed PointIQmath library files for C: IQmathLib.h, IQmath.libC Version File Names: f2803xhall3.h (for x2803x)C InterfaceC InterfaceObject DefinitionThe structure of HALL3 object is defined by following structure definitiontypedef struct { Uint16 CmtnTrigHall; // Output: Commutation trigger for Mod6cnt inputUint16 CapCounter; // Variable: Running cnt of detected edges on CAP/GPIO Uint16 DebounceCount; // Variable: Counter/debounce delay current value Uint16 DebounceAmount; // Parameter: Counter delay amount to // validate/debounce GPIO readingsUint16 HallGpio; // Variable: Most recent logic level on CAP/GPIO Uint16 HallGpioBuffer; // Variable: Buffer of last logic level on CAP/GPIO while // being debouncedUint16 HallGpioAccepted; // Variable: Debounced logic level on CAP/GPIOUint16 EdgeDebounced; // Variable: Trigger from Debounce macro to Hall_Drv, // if = 0x7FFF edge is debouncedUint16 HallMap[6]; // Variable: CAP/GPIO logic levels for HallMapPointer = 0-5Uint16 CapFlag; // Variable: CAP flags, indicating which CAP/GPIO detected // the edge// an edge detection of a hall signal.Uint16 HallMapPointer; // Input/Output: During the map created, this variable points// to the current commutation state. After map creation, it // points to the next commutation state.} HALL3;Special Constants and Data typesHALL3The module definition is created as a data type. This makes it convenient to instance an interface to the HALL3 driver. To create multiple instances of the module simply declare variables of type HALL3.HALL3_DEFAULTSStructure symbolic constant to initialize HALL3module. This provides the initial values to theterminal variables as well as method pointers.This default definition of the object implements two methods – the initialization and the runtime compute macro for HALL3. This is implemented by means of a macro pointer, and the initializer sets this to HALL3_INIT_MACRO and HALL3_READ_MACRO macros for x280x. The argument to this macro is the address of the HALL3 object.Module UsageInstantiationThe following example instances one HALL3 objectHALL3 hall;InitializationTo Instance pre-initialized objectsHALL3 hall = HALL3_DEFAULTS;Invoking the computation macroHALL3_INIT_MACRO (hall);HALL3_READ_MACRO (hall);ExampleThe following pseudo code provides the information about the module usage.main(){HALL3_INIT_MACRO (hall); // Call init macro for hall3}void interrupt periodic_interrupt_isr(){HALL3_READ_MACRO (hall); // Call the hall3 read macro}Software Flowcharts2-Channel PWM DAC Driver Description This module converts any s/w variables into the PWM signals in EPWMxA/B for 2803x. Thus, it can be used to view the signal, represented by the variable, at theoutputs of the PWMxA, PWMxB, pins through the external low-pass filters.Availability C interface versionModule Properties Type: Target Dependent, Application IndependentTarget Devices: 28x Fixed PointIQmath library files for C: IQmathLib.h, IQmath.libC Version File Names: f2803xpwmdac.h (for x2803x)C InterfaceObject DefinitionThe structure of PWMDAC object is defined by following structure definitiontypedef struct {_iq MfuncC1; // Input: PWM 1 Duty cycle ratio (Q24)_iq MfuncC2; // Input: PWM 2 Duty cycle ratio (Q24)Uint16 PeriodMax; // Parameter: PWMDAC half period in number of clocks (Q0)Uint16 HalfPerMax; // Parameter: Half of PeriodMax} PWMDAC;Special Constants and Data typesPWMDACThe module definition is created as a data type. This makes it convenient to instance an interface to the PWMDAC driver. To create multiple instances of the module simply declare variables oftype PWMDAC.PWMDAC_DEFAULTSStructure symbolic constant to initialize PWMDAC module. This provides the initial values to the terminal variables as well as method pointers.This default definition of the object implements two methods – the initialization and the runtime compute macro for PWMDAC generation. This is implemented by means of a macro pointer, and the initializer sets this to PWMDAC_INIT_MACRO and PWMDAC_MACRO macros for x280x.The argument to this macro is the address of the PWMDAC object.Module UsageInstantiationThe following example instances one PWMDAC objectPWMDAC pwmdac1;InitializationTo Instance pre-initialized objectsPWMDAC pwmdac1 = PWMDAC_DEFAULTS;Invoking the computation macroPWMDAC_INIT_MACRO(pwmdac1);PWMDAC_MACRO(pwmdac1);ExampleThe following pseudo code provides the information about the module usage.main(){pwmdac1.PeriodMax=500; // @60Mhz clock freq, PWM freq = 60kHzPWMDAC_INIT_MACRO (6, pwmdac1) // PWM 6A,6B}void interrupt periodic_interrupt_isr(){pwmdac1.MfuncC1 = variable1; // variable1 is in GLOBAL_Qpwmdac1.MfuncC2 = variable2; // variable2 is in GLOBAL_QPWMDAC_MACRO (6,pwmdac1) // update macro for pwmdac1 for PWM ch #6}Technical BackgroundTechnical BackgroundThe external low-pass filters are necessary to view the actual signal waveforms as seen in Figure1. The (1st-order) RC low-pass filter can be simply used for filter out the high frequency component embedded in the actual low frequency signals. To select R and C values, its time constant can be expressed in term of cut-off frequency (f c ) as follow: cf 21RC π==τ (1)Figure 1: External RC low-lass filter connecting to PWMx pin in x280x DSPPWM Driver Description This module uses the duty ratio information and calculates the compare values for generating PWM outputs. The compare values are used in the full compareEPWM unit in 280x. This also allows PWM period modulation.Availability C interface versionModule Properties Type: Target Dependent, Application IndependentTarget Devices: 28x Fixed PointIQmath library files for C: IQmathLib.h, IQmath.libC Version File Names: f2803xpwm.h (for x2803x)C InterfaceC InterfaceObject DefinitionThe structure of PWMGEN object is defined by following structure definitiontypedef struct { Uint16 PeriodMax; // Parameter: PWM Half-Period in CPU clock cycles (Q0) Uint16 HalfPerMax; // Parameter: Half of PeriodMax (Q0)Uint16 Deadband; // Parameter: PWM deadband in CPU clock cycles (Q0)_iq MfuncC1; // Input: PWM 1 Duty cycle ratio (Q24)_iq MfuncC2; // Input: PWM 2 Duty cycle ratio (Q24)_iq MfuncC3; // Input: PWM 3 Duty cycle ratio (Q24)} PWMGEN;Special Constants and Data typesPWMGENThe module definition is created as a data type. This makes it convenient to instance an interface to the PWMGEN driver. To create multiple instances of the module simply declare variables oftype PWMGEN.PWMGEN_DEFAULTSStructure symbolic constant to initialize PWMGEN module. This provides the initial values to the terminal variables as well as method pointers.C InterfaceThis default definition of the object implements two methods – the initialization and the runtime compute macro for PWMGEN generation. This is implemented by means of a pointer, and the initializer sets this to PWM_INIT_MACRO and PWM_MACRO macros for x280x. The argument to this macro is the address of the PWMGEN object.Module UsageInstantiationThe following example instances one PWMGEN objectPWMGEN pwm1;InitializationTo Instance pre-initialized objectPWMGEN pwm1 = PWMGEN_DEFAULTS;Invoking the computation macroPWM_INIT_MACRO (pwm1);PWM_MACRO (pwm1);ExampleThe following pseudo code provides the information about the module usage.main(){pwm1.PeriodMax = 3000; // PWM frequency = 10 kHz, clock = 60 MHzpwm1.HalfPerMax = pwm1.PeriodMax/2;PWM_INIT_MACRO (pwm1); // Call init macro for pwm1}void interrupt periodic_interrupt_isr(){pwm1.MfuncC1 = svgen_dq1.Ta; // svgen_dq1.Ta is in GLOBAL_Qpwm1.MfuncC2 = svgen_dq1.Tb; // svgen_dq1.Tb is in GLOBAL_Qpwm1.MfuncC3 = svgen_dq1.Tc; // svgen_dq1.Tc is in GLOBAL_QPWM_MACRO (1,2,3,pwm1); // Call update macro for pwm1 for PWM ch #1,2,3 }Quadrature Encoder Pulse Driver Description This module determines the rotor position and generates a direction (of rotation) signal from the shaft position encoder pulses.Availability C interface versionModule Properties Type: Target Dependent, Application IndependentTarget Devices: 28x Fixed PointIQmath library files for C: IQmathLib.h, IQmath.libC Version File Names: f2803xqep.h (for x2803x)C InterfaceObject DefinitionThe structure of QEP object is defined by following structure definitiontypedef struct { int32 ElecTheta; // Output: Motor Electrical angle (Q24)int32 MechTheta; // Output: Motor Mechanical Angle (Q24)Uint16 DirectionQep; // Output: Motor rotation direction (Q0)Uint16 QepPeriod; // Output: Capture period of QEP signal (Q0)Uint32 QepCountIndex; // Variable: Encoder counter index (Q0)int32 RawTheta; // Variable: Raw angle from EQEP position counter (Q0) Uint32 MechScaler; // Parameter: 0.9999/total count (Q30)Uint16 LineEncoder; // Parameter: Number of line encoder (Q0)Uint16 PolePairs; // Parameter: Number of pole pairs (Q0)int32 CalibratedAngle; // Parameter: Raw offset between encoder and ph-a (Q0) Uint16 IndexSyncFlag; // Output: Index sync status (Q0)} QEP;Special Constants and Data typesQEPThe module definition is created as a data type. This makes it convenient to instance an interface to the QEP driver. To create multiple instances of the module simply declare variables of typeQEP.QEP_DEFAULTSStructure symbolic constant to initialize QEP module. This provides the initial values to theterminal variables as well as method pointers.This default definition of the object implements three methods – the initialization, the runtime compute, and interrupt macros for QEP generation. This is implemented by means of a macro pointer, and the initializer sets this to QEP_INIT_MACRO, and QEP_MACRO macros for x280x.The argument to this macro is the address of the QEP object.Module UsageInstantiationThe following example instances one QEP objectQEP qep1;InitializationTo Instance pre-initialized objectsQEP qep1 = QEP_DEFAULTS;Invoking the computation macroQEP_INIT_MACRO (1, qep1);QEP_MACRO (1, qep1);The index event handler resets the QEP counter, and synchronizes the software/hardware counters to the index pulse. Also it sets the QEP IndexSyncFlag variable to reflect that an index sync has occurred.The index handler is invoked in an interrupt service routine. Of course the system framework must ensure that the index signal is connected to the correct pin and the appropriate interrupt is enabled and so on.ExampleThe following pseudo code provides the information about the module usage.main(){QEP_INIT_MACRO(1,qep1); // Call init macro for qep1}void interrupt periodic_interrupt_isr(){QEP_MACRO(1,qep1); // Call compute macro for qep1}Technical BackgroundFigure 1. Speed sensor diskFigure 1 shows a typical speed sensor disk mounted on a motor shaft for motor speed, position and direction sensing applications. When the motor rotates, the sensor generates two quadrature pulses and one index pulse. These signals are shown in Figure 2 as QEP_A, QEP_B and QEP_index.Figure 2. Quadrature encoder pulses, decoded timer clock and direction signal.QEP_AQEP_BQEP CLK (H/W) DIR (H/W)1000 QEP pulses= 4000 counter “ticks,” per 360°12。

a r X i v :c o n d -m a t /9703188v 1 [c o n d -m a t .d i s -n n ] 20 M a r 1997Sparse random matrix configurations for two or three interactingelectrons in a random potential Shi-Jie Xiong 1,2and S.N.Evangelou 1,31Foundation for Research and Technology,Institute for Electronic Structure and Lasers,Heraklion,P.O.Box 1527,71110Heraklion,Crete,Greece 2Department of Physics,Nanjing University,Nanjing 210008,China 3Department of Physics,University of Ioannina,Ioannina 45110,Greece Abstract We investigate the random matrix configurations for two or three interacting electrons in one-dimensional disordered systems.In a suitable non-interacting localized electron basis we obtain a sparse random matrix with very long tails which is different from a superimposed random band matrix usually thought to be valid.The number of non-zero off-diagonal matrix elements is shown to decay very weakly from the matrix diagonal and the non-zero matrix elements are distributed according to a Lorentzian around zero with also very weakly decaying parameters.The corresponding random matrix for three interacting electrons is similar but even more sparse.PACS numbers:72.15.Rn,71.30.+h,74.25.FyThere is a great current interest in the localization weakening effect due to the interaction of two electrons in one-dimensional(1D)disordered systems[1,2,3,4,5, 6,7,8,9,10].Shepelyansky[1]mapped this problem onto a class of random banded matrices with stronglyfluctuating diagonal elements,being the eigenenergies of the non-interacting problem,and independent Gaussian random off-diagonal matrix el-ements of zero average and typical strength Ustates with a considerable enhancementξ∼U2ξ21of the localization length 2Lalong the center of mass coordinate is predicted due to coherent propagation of the electronic pair.It was also shown that the interaction has no effect for the majority of other states with the two particles localized in isolated spatial positions which do not allow overlapping.This conclusion was confirmed and extended to higher di-mensions via Thouless block scaling picture by Imry[2].The subsequent numerical studies[3,4,5,6,7,8,9,10]verified the main qualitative results concerning the presence of Shepelyansky states,mostly by supressing single particle transport via efficient Green function or bag model methods which examine pair propagation[8]. The deviations from the predicted behavior of the two-particle localization lengthξfound were usually attributed to the oversimplified statistical assumptions concerning the band random matrix model of the original Shepelyansky construction.However,there is an ongoing debate whether coherent pair propagation actu-ally exists for two interacting electrons in infinite disordered systems[11,12],which began by a recent transfer matrix study where no propagation enhancement is found at E=0for an infinite chain[11].Moreover,it was pointed out that the reduction to a SBRM relies on questionable assumptions regarding chaoticity of the non–interacting electron localized states withinξ1,so that the relevant matrix model could be prob-ably different[13,14].Although the reported absence of propagation enhancement [11]can be critisized,since the transfer matrix method may not measure the actual pair localization length,it is correct that the fraction of the Shepelyansky states will eventually shrink to zero when the system size increases,although not affecting their physical significance.A different localization length enhancement for theses states, of the formξ∼U2ξ1+γ1with a U–dependent exponentγ<1,was also proposed on the basis of numerical data by a reduction mechanism to another appropriate random matrix model[13].It must be mentioned that the Shepelyansky states are expected to exist as long as the interaction is not too large,since it isfirmly established[10,13] that in the strong interaction limit U→∞no coherent propagation enhancement is possible with these states decoupled from the main band withξ≈ξ1.It is worthwhile to check the validity of the mapping to a SBRM which al-lowed most of the previous results concerning the Shepelyansky states to be derived. The fact that a mapping to SBRM neglects phase correlations of the one particle localized states was also emphasised for a few known examples in another recent study[14],where it lead to a non–justified propagation enhancement.In order to shed light on the appropriate random matrix description for the problem of two in-teracting electrons in a random potential we examine explicitly the structure of the two and three-electron Hamiltonian matrices by a direct numerical analysis.The corresponding Anderson-Hubbard Hamiltonian[15,16]can be written asH=Nn=1 σ(c†n+1,σc n,σ+H.c.)+N n=1 σǫn c†n,σc n,σ+Nn=1 σ=σ′Uc†n,σ′c n,σ′c†n,σc n,σ,(1)where c†n,σand c n,σare the creation and destruction operators for the electron at site n and with spinσ,ǫn is energy level at site n which is a random variable uniformlydistributed in the range[−W/2,W/2]as for the Anderson model and U is the strength of the interaction between the electrons.A non–interacting disordered system of N atoms with U=0in Eq.(1)has N linearly independent one–electron localized wave functionsψi with corresponding eigenvalues E i,i=1,2,3,...,N.These exponentially localized wave functions are of the approximate formψi(n)∼1ξ1exp −|n−n i|W2whereE is the single particle energy,although for some special E the prefactor is different. In order to examine the few–body problem in the presence of disorder we have ob-tained numerically all the localized statesψi and arranged them so that if i<j the coordinate n i for the localization center ofψi is smaller than the corresponding center n j of the wave functionψj.This is a natural kind of arrangement which quarantees the largest overlapping of the wave functions to occur when their indices have the smallest difference.Firstly,we consider two electrons with opposite spins and use the N2products of the two one-electron wave functionsΨ(2)m=ψiψj,i,j=1,2,..,N,(3) as convenient basis states for the two interacting electrons.We do not consider the spin configuration of the two-electron wave function as suggested in Ref.[1].The index m is also arranged in such a way so that states with the smallest difference of their indices have the strongest coupling.One can calculate the matrix elements of the U–dependent Hubbard interaction term of Eq.(1)in the obtained new basis setviaH m,m′=U nψi(n)ψj(n)ψi′(n)ψj′(n).(4) In the original SBRM construction the matrix element H m,m′was shown to vanish unless all four relevant wave functions were overlapping.Then eachψi(n)was assumed completely random withinξ1by taking the approximate states of Eq.(2)with a random phase factorθi(n),so that one immediately obtains the estimate Uh2 +a3a2We have also investigated the random matrix structure for the corresponding three electron problem.In order to simplify the calculations we have restricted our consideration to three electrons where two of them have spin up and one spin down. For a chain of N–sites in the adopted three–electron basis there are N2(N−1)/2 linearly independent states whose wave functions can be written asΨ(3)m=ψi,↑ψj,↑ψk,↓,i=j.(6) We again sort these3-particle states in such a way so that those with the smallest difference in their indices have the strongest possible coupling.In Fig.5we display the obtained distributions for the diagonal and the off-diagonal matrix elements.For the diagonal elements the distribution is more sharp when compared to the two-electron case,reflecting a smearing effect in the total energyfluctuations due to the increase in the number of particles.Wefind that the off-diagonal matrix elements obey the general principles of the two–electron problem but the matrix structure is comparatively even more sparse in this case.In summary,we have studied the random matrix configurations for two or three interacting electrons in a disordered chain.We made a basis set arrangement which consists of non-interacting particle wave function products of orbitals so that the off-diagonal matrix elements due to the interaction occur successively only for states having closely spaced indices.Although this is the most favourable basis set for obtaining a SBRM a very sparse random matrix structure is shown to emerge from our data instead,having no well–defined band region with Gaussian matrix elements.We thinkfinding another basis set consistent with a band random matrix structure is not easy and the few-body problem can be studied via extremely sparse random matrix configurations.It must be pointed out that the obtained sparse matrix is not incompatible with states having enhanced localization length along the centerof mass coordinate,since they can be shown by methods which do not rely on the specific matrix mapping[8,17].AcknowledgmentsThis work was supported in part by aΠENE∆Research Grant of the Greek Secretariat of Science and Technology,from EU contract CHRX-CT93-0136and a TMR network.We also thank F.von Oppen for an e-mail correspondance.References[1]D.L.Shepelyansky,Phys.Rev.Lett.73,2607(1994).[2]Y.Imry,Europhys.Lett.30,405(1995).[3]K.Frahm,A.Muller-Groeling,J.-L.Pichard,and D.Weinmann,Europhys.Lett.31,169(1995).[4]M.E.Raikh,L.I.Glazman,and L.E.Zhukov,Phys.Rev.Lett.77,1354(1996).[5]Yan V.Fyodorov and A.D.Mirlin,Phys.Rev.B52,R11580(1995).[6]D.Weinmann,A.Muller-Groeling,J.-L.Pichard and K.Frahm,Phys.Rev.Lett.75,1598(1995).[7]P.Jacquod and D.L.Shepelyansky,Phys.Rev.Lett.75,3501(1995).[8]F.von Oppen,T.Wetting,and J.Muller,Phys.Rev.Lett.76,491(1996).[9]K.Frahm,A.Muller-Groeling and J.-L.Pichard,Phys.Rev.Lett.76,1509(1996).[10]S.N.Evangelou,S.J.Xiong and E.N.Economou,Phys.Rev.B54,8469(1996).[11]R.A.Romer and M.Shreiber,Phys.Rev.Lett.78,515(1997).[12]K.Frahm,A.Muller-Groeling,J.-L.Pichard,and D.Weinmann,comment incond-mat/9702084and R.A.Romer and M.Shreiber reply in cond-mat/9702246.[13]I.V.Ponomarev and P.G.Silvestrof,cond-mat/9610202[14]T.Vojta,R.A.Romer and M.Shreiber,cond-mat/9702241.[15]P.W.Anderson,Phys.Rev.115,2(1959).[16]J.Hubbard,Proc.R.Soc.London Ser.A276,238(1963);277,237(1964).[17]F.von Oppen and T.Wetting,Europhys.Lett.32,741(1996).Figure CaptionsFig. 1.The distribution of the matrix elements for the two-electron Hamiltonian with disorder W=3,interaction strength U=1and chain size N=100.(a)The diagonal matrix elements.(b)Thefirst off-diagonal matrix elenents(continuous line) and thefitting curve from Eq.(5)(broken line).Fig.2.The same as Fig.1but for W=6and interaction strength U=4.Fig.3.The fourfitting parameters a1,a2,a3,a4of Eq.(5)for the distribution of the off-diagonal matrix elements corresponding to Fig.1as a function of the distance from the main matrix diagonal,with chain size N=100,disorder W=3and interaction strength U=1.Fig. 4.The same as Fig.3but for W=6and interaction strength U=4 corresponding to Fig.2.Fig. 5.The distribution of the matrix elements for the three-electron Hamiltonian with disorder W=6,interaction strength U=4and chain size N=100.(a) The distribution of the diagonal matrix elements.(b)The distribution of thefirst off-diagonal matrix elenents.–0.004–0.00200.0020.004Off-diagonal elements0.20.40.6N u m b e rFig. 1(b)W=3 U=10.050.10.150.2Diagonal elements50100150N u m b e rFig. 1(a)W=3 U=1–0.004–0.00200.0020.004Off-diagonal elements0.20.40.60.8N u m b e rFig. 2(b)W=6 U=4–0.20.20.40.60.8Diagonal elements050100150N u m b e rFig. 2(a)W=6 U=4050000100000150000200000250000300000-5510152025N u m b e rDiagonal elementsFig. 5(a)050000100000150000200000250000300000-1.5-1-0.500.51 1.5N u m b e rOff-diagonal elementsFig. 5(b)。

The Model 2000 6½-Digit Multimeter is part of Keithley’s family of high perfor-mance DMMs. Based on the same high speed, low noise A/D converter technology as the Model 2001 and 2002, the 2000 is a fast, accurate, and highly stable instrument that’s as easy to operate as it is to afford. It combines broad measurement ranges with superior accuracy specifications — DC voltage from 100nV to 1kV (with 0.002% 90-day basic accuracy) and DC resistance from 100µW to 100M W (with 0.008% 90-day basic accuracy). Optional switch cards enable multiplexing up to 20 different input signals for multipoint measurement applications.High ThroughputThe 2000 offers exceptional measurement speed at any reso l ution. At 6½digits, it delivers 50 triggered rdgs/s over the IEEE-488 bus. At 4½ digits, it can read up to 2000 rdgs/s into its internal 1024 reading buf f er, making it an excellent choice for applications where throughput is c ritical.For benchtop or stand-alone applications, the 2000 has a front panel design that’s simple to understand and easy to use. The 2000 has 13 built-inmeasurement functions, including DCV, ACV, DCI, ACI, 2W W , 4W W , temper a ture, frequency, period, dB, dBm, continuity mea s ure m ent, and diode testing. A built-in RS-232 inter f ace conn ects to a notebook or full-sized PC’s serial port to take, store, process, and dis p lay meas u re m ents auto matically.Key Features• 13 built-in measurement functions • 2000 readings/second at 4½ digits• Optional scanner cards for multipoint measurements • GPIB and RS-232 interfaces • Fluke 8840/42 command setA Tektronix CompanyOrdering Information20006½-Digit DMM2000/2000-SCAN6½-Digit DMM/Scanner CombinationAccessories SuppliedInstruction Manual and Model 1751 Safety Test LeadsAccessories Available2000-SCAN 10-channel, General-Purpose Scanner Card 2001-SCAN10-channel Scanner Card with two high-speed c hannels2001-TCSCAN9-channel, Thermocouple Scanner C ard with built-in cold junctionCABLES/ADAPTERS 7007-1 Shielded IEEE-488 Cable, 1m (3.3 ft)7007-2 Shielded IEEE-488 Cable, 2m (6.6 ft)7009-5 RS-232 Cable RACK MOUNT KITS 4288-1 Single Fixed Rack Mount Kit 4288-2 Dual Fixed Rack Mount KitGPIB INTERFACESKPCI-488LPA IEEE-488 Interface/Controller for the PCI Bus KUSB-488B IEEE-488 USB-to-GPIB Interface AdapterServices Available2000-SCAN-3Y-EW1-year factory warranty extended to 3 years from date of shipment 2000-3Y-EW1-year factory warranty extended to 3 years from date of shipment 2001-TCSCAN-3Y-EW1-year factory warranty extended to 3 years from date of shipment C/2000-3Y-ISO3 (ISO-17025 accredited) calibrations within 3 years of purchas for Models 2000, 2000-SCAN*C/2001-3Y-ISO3 (ISO-17025 accredited) calibrations within 3 years of purchase for Model 2001-TCSCAN**Not available in all countriesSCANNER OPTION 2000-SCANGENERAL: 10 channels of 2-pole relay input. All channels configurable to 4-pole.CAPABILITIES: Multiplex one of ten 2-pole or one of five 4-pole signals into DMM.INPUTSMaximum Signal Level:DC Signals: 110V DC, 1A switched, 30VA maximum (resistive load).AC Signals: 125V AC rms or 175V AC peak, 100kHz maximum, 1A switched, 62.5VA maxi-mum (resistive load).Contact Life: >105 operations at maximum signal level; >108 operations cold switch i ng.Contact Resistance: <1W at end of contact life.Actuation Time: 2.5ms maximum on/off.Contact Potential: <±500nV typical per contact, 1µV max. <±500nV typical per contact pair, 1µV max.Connector Type: Screw terminal, #22 AWG wire size.Isolation Between Any Two Terminals: >109W , <75pF.Isolation Between Any Terminal and Earth: >109W , <mon Mode Voltage: 350V peak between any terminal and earth.Maximum Voltage Between Any Two Terminals: 200V peak.Maximum Voltage Between Any Terminal and Model 2001 Input LO: 200V peak.ENVIRONMENTAL: Meets all Model 2000 environmental specifications.DIMENSIONS, WEIGHT: 21mm high × 72mm wide × 221mm deep (0.83 in. × 2.83 in. × 8.7 in.). Adds 0.4kg (10 oz.).Scanner Configuration for Models 2000-SCAN and 2001-SCANOptional Multiplexer CardsCreating a self-contained multipoint measurement solution is as simple as plugging a scanner card into the option slot on the 2000’s back panel. This ap p roach eliminates the complexities of triggering, timing, and processing issues and helps reduce test time significantly. For applications involving more than 10 measurement points, the 2000 is com p atible with Keithley’s switch matrices and cards.Model 2000-SCAN Scanner Card • Ten analog input channels (2-pole)• Configurable as 4-pole, 5-channelModel 2001-SCAN Scanner Card • Ten analog input channels• Two channels of 2-pole, high-speed, solid-state switching Model 2001-TCSCAN Thermocouple Scanner Card • Nine analog input channels• Built-in temperature reference for thermo c ouple cold-junction compensationDC OPERATING CHARACTERISTICS 2Function Digits Readings/s PLCs 8 DCV (all ranges),6½ 3, 4510 DCI (all ranges), and6½ 3, 7301 Ohms (<10M range)6½ 3, 55015½ 3, 52700.15½ 55000.15½ 510000.044½ 520000.01 DC SYSTEM SPEEDS 2, 6RANGE CHANGE 3: 50/s.FUNCTION CHANGE 3: 45/s.AUTORANGE TIME 3, 10: <30ms.ASCII READINGS TO RS-232 (19.2K BAUD): 55/s.MAX. INTERNAL TRIGGER RATE: 2000/s.MAX. EXTERNAL TRIGGER RATE: 400/s.DC GENERALLINEARITY OF 10VDC RANGE: ±(1ppm of reading + 2ppm of range).DCV, W, TEMPERATURE, CONTINUITY, DIODE TEST INPUT PROTECTION: 1000V, all ranges. MAXIMUM 4W W LEAD RESISTANCE: 10% of range per lead for 100W and 1k W ranges; 1k W per lead for all other ranges.DC CURRENT INPUT PROTECTION: 3A, 250V fuse.SHUNT RESISTOR: 0.1W for 3A, 1A, and 100mA ranges. 10W for 10mA range. CONTINUITY THRESHOLD: Adjustable 1W to 1000W.AUTOZERO OFF ERROR: Add ±(2ppm of range error + 5µV) for <10 minutes and ±1°C change.OVERRANGE: 120% of range except on 1000V, 3A, and diode.SPEED AND NOISE REJECTIONRate Readings/s DigitsRMS Noise 10VRange NMRR 12CMRR 13 10 PLC56½< 1.5 µV60 dB140 dBDC NOTES1. Add the following to “ppm of range” uncertainty:1V and 100V, 2ppm; 100mV, 15ppm; 100W, 15ppm;1k W–<1M W, 2ppm; 10mA and 1A, 10ppm; 100mA, 40ppm.2. Speeds are for 60Hz operation using factory default operating conditions (*RST). Autorange off, Displayoff, Trigger delay = 0.3. Speeds include measurement and binary data transfer out the GPIB.4. Auto zero off.5. Sample count = 1024, auto zero off.6. Auto zero off, NPLC = 0.01.7. Ohms = 24 readings/second.8. 1 PLC = 16.67ms @ 60Hz, 20ms @ 50Hz/400Hz. The frequency is automatically determined at power up.9. For signal levels >500V, add 0.02ppm/V uncertainty for the portion exceeding 500V.10. Add 120ms for ohms.11. Must have 10% matching of lead resistance in Input HI and LO.12. For line frequency ±0.1%.13. For 1k W unbalance in LO lead.14. Relative to calibration accuracy.15. Specifications are for 4-wire ohms. For 2-wire ohms, add 1W additional uncertainty.16. For rear inputs, add the following to temperature coefficient “ppm of reading” uncertainty 10M W 95ppm,100M W 900ppm. Operating environment specified for 0° to 50°C and 50% RH at 35°C.DC CharacteristicsConditions:MED (1 PLC)1 or SLOW (10 PLC)or MED (1 PLC) with filter of 10Accuracy: ±(ppm of reading + ppm of range) (ppm = parts per million)(e.g., 10ppm = 0.001%)Function Range ResolutionTest Currentor BurdenVoltage (±5%)InputResistanceTemperatureCoefficient0°–18°C and 28°–50°C24 Hour 1423°C ± 1°90 Day23°C ± 5°1 Year23°C ± 5°Voltage100.0000mV 0.1µV> 10 G W30 + 3040 + 3550 + 35 2 + 610.00000V10µV 7µA20 + 630 + 740 + 78 + 1HIGH CREST FACTOR ADDITIONAL ERROR ±(% of reading) 7CREST FACTOR: 1–2 2–3 3–4 4–5ADDITIONAL ERROR: 0.05 0.15 0.30 0.40AC OPERATING CHARACTERISTICS 2FunctionDigits Readings/s Rate Bandwidth ACV (all ranges), and 6½ 32s/reading SLOW 3 Hz–300 kHz ACI (all ranges)6½ 3 1.4MED 30 Hz–300 kHz 6½ 4 4.8MED 30 Hz–300 kHz 6½32.2FAST 300 Hz–300 kHz 6½ 435FAST300 Hz–300 kHzADDITIONAL LOW FREQUENCY ERRORS ±(% of reading)SlowMed Fast 20 Hz –30 Hz 00.3—AC SYSTEM SPEEDS 2, 5FUNCTION/RANGE CHANGE 6: 4/s.AUTORANGE TIME: <3s.ASCII READINGS TO RS-232 (19.2K BAUD) 4: 50/s.MAX. INTERNAL TRIGGER RATE 4: 300/s.MAX. EXTERNAL TRIGGER RATE 4: 300/s.AC GENERALINPUT IMPEDANCE: 1M W ±2% paralleled by <100pF.ACV INPUT PROTECTION: 1000Vp.MAXIMUM DCV: 400V on any ACV range.ACI INPUT PROTECTION: 3A, 250V fuse.BURDEN VOLTAGE: 1A Range: <0.3V rms. 3A Range: <1V rms.SHUNT RESISTOR: 0.1W on all ACI ranges.AC CMRR: >70dB with 1k W in LO lead.MAXIMUM CREST FACTOR: 5 at full scale.VOLT HERTZ PRODUCT: ≤8 × 107 V·Hz.OVERRANGE: 120% of range except on 750V and 3A ranges.AC NOTES1. Specifications are for SLOW rate and sinewave inputs >5% of range.2. Speeds are for 60Hz operation using factory default operating conditions (*RST). Auto zero off, Auto range off, Display off, includes measurement and binary data transfer out the GPIB.3. 0.01% of step settling error. Trigger delay = 400ms.4. Trigger delay = 0.5. DETector:BANDwidth 300, NPLC = 0.01.6. Maximum useful limit with trigger delay = 175ms.7. Applies to non-sinewaves >5Hz and <500Hz (guaranteed by design for crest factors >4.3).8. Applies to 0°–18°C and 28°–50°C.9. For signal levels >2,2A, add additional 0.4% to “of reading” uncertainty.10. Typical uncertainties. Typical represents two sigma or 95% of manufactured units measure <0.35% of reading and three sigma or 99.7% measure <1.06% of reading.True RMS AC Voltage and Current CharacteristicsAccuracy 1: ±(% of reading + % of range), 23°C ±5 °CVoltage Range Resolution Calibration Cycle3 Hz–10 Hz 1010 Hz–20 kHz20 kHz–50 kHz50 kHz–100 kHz100 kHz–300 kHz100.0000mV 0.1µV 1.000000V 1.0µV 90 Days0.35 + 0.030.05 + 0.030.11 + 0.050.60 + 0.084 + 0.510.00000V 10µV 100.0000V 100µV 1 Year0.35 + 0.030.06 + 0.030.12 + 0.050.60 + 0.084 + 0.5750.000V1mVTemperature Coefficient/°C 80.035 + 0.0030.005 + 0.0030.006 + 0.0050.01 + 0.0060.03 + 0.01Current Range ResolutionCalibration Cycle 3 Hz–10 Hz 10 Hz–3 kHz 3 kHz–5 kHz 1.000000A 1µA 90 Day/1 Year 0.30 + 0.040.10 + 0.040.14 + 0.043.00000 A910µA90 Day/1 Year 0.35 + 0.060.15 + 0.060.18 + 0.06Temperature Coefficient/°C 80.035 + 0.0060.015 + 0.0060.015 + 0.006Triggering and MemoryREADING HOLD SENSITIVITY: 0.01%, 0.1%, 1%, or 10% of reading.TRIGGER DELAY: 0 to 99 hrs (1ms step size).EXTERNAL TRIGGER LATENCY: 200µs + <300µs jitter with autozero off, trigger delay = 0.MEMORY: 1024 readings.Math FunctionsRel, Min/Max/Average/StdDev (of stored reading), dB, dBm, Limit Test, %, and mX+b with user defined units displayed. DBM REFERENCE RESISTANCES: 1 to 9999W in 1W increments.Standard Programming LanguagesSCPI (Standard Commands for Programmable Instruments)Keithley 196/199Fluke 8840A, Fluke 8842ARemote InterfaceGPIB (IEEE-488.1, IEEE-488.2) and RS-232C.Frequency and Period Characteristics 1, 2ACV Range FrequencyRangePeriodRange Gate TimeResolution±(ppm ofreading)Accuracy90 Day/1 Year±(% of reading)100 mV to 750 V 3 Hz to500 kHz333 ms to2 µs 1 s (SLOW)0.30.01FREQUENCY NOTES1. Specifications are for square wave inputs only. Input signal must be >10% of ACV range. If input is <20mV on the 100mV range, then frequency must be >10Hz.2. 20% overrange on all ranges except 750V range.Temperature CharacteristicsThermocouple 2, 3, 4Accuracy 190 Day/1 Year (23°C ± 5°C)Type Range ResolutionRelative toReference Junction Using 2001-TCSCAN 5J–200 to +760°C0.001°C±0.5°C±0.65°CK–200 to +1372°C0.001°C±0.5°C±0.70°CT–200 to +400°C0.001°C±0.5°C±0.68°C TEMPERATURE NOTES1. For temperatures <–100°C, add ±0.1°C and >900°C add ±0.3°C.2. Temperature can be displayed in °C, K or °F.3. Accuracy based on ITS-904. Exclusive of thermocouple error.5. Specifications apply to channels 2–6. Add 0.06°C/channel from channel 6.General InformationPOWER SUPPLY: 100V / 120V / 220V / 240V.LINE FREQUENCY: 50Hz to 60Hz and 400Hz, automatically sensed at power-up.POWER CONSUMPTION: 22VA.VOLT HERTZ PRODUCT:≤8 × 107V·Hz.OPERATING ENVIRONMENT: Specified for 0°C to 50°C. Specified to 80% R.H. at 35°C and at an altitude of up to 2000m. STORAGE ENVIRONMENT: –40°C to 70°C.SAFETY: Conforms to European Union Low Voltage Directive.EMC: Conforms to European Union EMC Directive.WARMUP: 1 hour to rated accuracy.VIBRATION: MIL-PRF-2800F Class 3 Random.DIMENSIONS:Rack Mounting: 89mm high × 213mm wide × 370mm deep (3.5 in × 8.38 in × 14.56 in).Bench Configuration (with handle and feet): 104mm high × 238mm wide × 370mm deep (4.13 in × 9.38 in × 14.56 in). NET WEIGHT: 2.9kg (6.3 lbs).SHIPPING WEIGHT: 5kg (11 lbs).Contact Information:Australia* 1 800 709 465Austria 00800 2255 4835Balkans, Israel, South Africa and other ISE Countries +41 52 675 3777Belgium* 00800 2255 4835Brazil +55 (11) 3759 7627Canada 180****9200Central East Europe / Baltics +41 52 675 3777Central Europe / Greece +41 52 675 3777Denmark +45 80 88 1401Finland +41 52 675 3777France* 00800 2255 4835Germany* 00800 2255 4835Hong Kong 400 820 5835India 000 800 650 1835Indonesia 007 803 601 5249Italy 00800 2255 4835Japan 81 (3) 6714 3010Luxembourg +41 52 675 3777Malaysia 180****5835Mexico, Central/South America and Caribbean 52 (55) 56 04 50 90Middle East, Asia, and North Africa +41 52 675 3777The Netherlands* 00800 2255 4835New Zealand 0800 800 238Norway 800 16098People’s Republic of China 400 820 5835Philippines 1 800 1601 0077Poland +41 52 675 3777Portugal 80 08 12370Republic of Korea +82 2 6917 5000Russia / CIS +7 (495) 6647564Singapore 800 6011 473South Africa +41 52 675 3777Spain* 00800 2255 4835Sweden* 00800 2255 4835Switzerland* 00800 2255 4835Taiwan 886 (2) 2656 6688Thailand 1 800 011 931United Kingdom / Ireland* 00800 2255 4835USA 180****9200Vietnam 12060128* European toll-free number. If notaccessible, call: +41 52 675 3777Find more valuable resources at /KEITHLEYCopyright © Tektronix. All rights reserved. Tektronix products are covered by U.S. and foreign patents, issued and pending. Information in this publication supersedes thatin all previously published material. Specification and price change privileges reserved. TEKTRONIX and TEK are registered trademarks of Tektronix, Inc. All other trade namesreferenced are the service marks, trademarks or registered trademarks of their respective companies.。

英语四级长篇阅读匹配试题及答案英语四级长篇阅读匹配试题及答案 1There are three kinds of goals: short-term,medium-range and long-term goals. Short-range goals are those that usually deal with current activities,which we can apply on a daily basis.Such goals can be achieved in a week or less,or two weeks,or possible months.It should be remembered that just as a building is no stronger than its foundation ,out long-term goals cannot amount to very munch without the achievement of solid short-term goals.Upon completing our short-term goals,we should date the occasion and then add new short-term goals that will build on those that have been completed. The intermediate goals bukld on the foundation of the short-range goals.They might deal with just one term of school or the entire school year,or they could even extend for several years.Any time you move a step at a time,you should never allow yourself to become discouraged or overwhelmed. As you complete each step,you will enforce the belief in your ability to grow adn succeed.And as your list of completion dates grow,your motivation and desire will increase.Long-range goals may be related to our dreams of the future. They might cover five years or more. Life is not a static thing.We should never allow a long-term goal to limit us or our course of action. 1.Our long-term goals mean a lot______.A.if we complete our short-range goalsB.if we cannot reach solid short-term goalsC.if we write down the datesD.if we put forward some plans2.New short-term goals are bulid upon______.A.two yearsB.long-term goalsC.current activitiesD.the goals that have been completed3.When we complete each step of our goals ,______.A.we will win final successB.we are overwhelmedC.we should build up confidence of successD.we should strong desire for setting new goals 4.Once our goals are drawn up,_______.A.we should stick to them until we complete themB.we may change our goals as we have new ideas and opportunitiesC.we had better wait for the exciting news of successD.we have made great decision5.It is implied but not stated in the passage that ______.A.those who habe long-term goals will succeedB.writing down the dates may discourage youC.the goal is only a guide for us to reach our desinationD.every should have a goal答案:adcbc英语四级长篇阅读匹配试题及答案 2If the population of the earth goes on increasing at its present rate, there will eventually not be enough resources left to sustain life on the planet.By the middle of the 21st century,if present trends continue, we will have used up all the oil that drives our cars,for example.Even if scientists develop new ways of feeding the human race,the crowded conditions on earth will make it necessary for lus to look for open space somewhere else. But none of the other planets in our solar system are capable of supporting life at present. One possible solution to the problem, however,has recently been suggested by American scientist, Professor Carl Sagan. Sagan believes that before the earths resources are compleetely exhausted it will be possible to change the atmophere of Venus and so create a new world almost as large as earth itself. The difficult is that Venus is much hotter than the earth and there is only a tiny amount of water there. Sagan proposes that algae organisms that can live in extremely hot or cold atmospheres and at the same time produce oxygen,should be bred in condition similar to those on Venus.As soon as this has been done, the algae will be placed in small rockets. Spaceship will then fly to Venus and fire the rockets into the atmosphere .In a fairly short time, the alge will break down the carbon dioxide into oxygen andcarbon. When the algae have done theri work, the atmosphere will become cooler,but befor man can set foot on Venus it will be neccessary for the oxygen to produce rain. The surface of the planet will still be too hot for man to land on it but the rain will eventually fall and in a few years something like earth will be reproduced on Venus. -1.Inte long run, the most insoluble problem caused by population growth on earth will probably be the lack of ______.a.foodb.oilc.spaced.resources2.Carl Sagan believes that Venus might be colonized from earth because _____ a.it might be possible to change its atmosphere b.its atmosphere is the same as the earthsc.there is a good supply of water on Venusd.the days on Venus are long enough3.On Venus there is a lot of ________.a.waterb.carbon dioxidec.carbon monoxided.oxygen4.Algae are plants that can____.a.live in very hot temperaturesb.live in very cold temperaturesc.manufacture oxygend.all of the above5. Man can land on Venus only when_______. a.the algae have done their work -b.the atmosphere becomes coolerc.thereis oxygend.it rains there答案:cabdd英语四级长篇阅读匹配试题及答案 3Like a needle climbing up a bathroom scale, the number keeps rising. In 1991, 15% of Americans were obese(肥胖的); by 1999, that proportion had grown to 27%. Youngsters, who should have age and activity on their side, are growing larger as well: 19% of Americans under 17 are obese. Waistbands have been popping in other western countries too, as physical activity has declined and diets have expanded. By and large, people in the rich world seem to have lost the fight against flab(松弛).Meanwhile, poorer nations have enjoyed some success in their battles against malnutrition and famine. But, according to research presented at the annual meeting of the American Association for the Advancement of Science, it is more a case of being out of the frying pan and into the fire. The most striking example actually in the poor world comes from the Pacific islands, home of the world’s most obese communities. In 1966, 14% of the men on this island were obese while 100% of men under the age of 30 in 1996 were obese.This increase in weight has been uneven as well as fast. As a result, undernourished and over-nourished people frequently live cheek by jowl(面颊). The mix can even occur within a single household. A study of families in Indonesia found that nearly 10% contained both the hungry and the fat. This is a mysterious phenomenon, but might have something to do with people of different ages being given different amounts of food to eat.The prospect of heading off these problems is bleak. In many affected countries there are cultural factorsto contend with, such as an emphasis on eating large meals together, or on food as a form. ofhospitality.Moreover, there is a good measure of disbelief on the part of policymakers that such a problem Could existin their countries. Add to that reluctance on the part of governments to spend resources on promoting dietand exercise while starvation is still a real threat, and the result is a recipe for inaction. Unless something is done soon, it might not be possible to turn the clock back.英语四级阅读模拟试题:Choose correct answers to the question:1.The first sentence of the passage most probably implies that ______.A.many Americans are obsessed with the rising temperature in their bathroomB.more people are overweighed in the United StatesC.people are doing more physical exercises with the help of scalesD.youngsters become taller and healthier thanks to more activities2.As physical exercise declines and diet expands, ______.A.other western countries has been defeated by fatB.obesity has become an epidemic(流行病)of the rich worldC.waistbands begin to be popular in other western countriesD.western countries can no longer fight against obesity3.Which is NOT the point of the example of the Pacific Islands?A.The poor community has shaken off poverty and people are well-fed now.B.Obesity is becoming a problem in the developing world too.C.Excessive weight increase will cause no less harm than the food shortage.D.The problem of overweight emerges very fast.4.Of tackling obesity in the poor world, we can learn from the passage that____A.the matter is so complex as to go beyond our capacityB.no matter what we do, the prospect will always be bleakC.it is starvation, the real threat, that needs to be solvedD.we should take immediate actions before it becomes incurable5.What is the main idea of this passage?A.Obesity is now a global problem that needs tackling.B.The weights increase fast throughout the whole world.C.Obesity and starvation are two main problems in the poor world.D.Obesity has shifted from the rich world to the poor world.英语四级阅读参考答案1.[B] 推理判断题。

September 2008 Rev 31/7TN0063Technical noteOverview of the STM32F103xxACIM and PMSM motor control software libraries release 2.0IntroductionThe purpose of this technical note is to provide an overview of the main features and performance metrics of the STM32F103xx motor control firmware libraries release 2.0.For the complete documentation, please refer to the two following user manuals:■UM0483: STM32F103xx AC induction motor IFOC software library V2.0■UM0492: STM32F103xx permanent-magnet synchronous motor FOC software library V2.0These documents are available for free upon request to your nearest STMicroelectronics sales office or distributor. For a complete list of ST offices and distributors, refer to the ST website .New features in this motor control firmware library package release 2.0■patented single, common DC link shunt-resistor current-sampling method ■optimized IPMSM (internal permanent-magnet synchronous motor) maximum-torque-per-ampere strategy ■redesigned closed-loop flux weakening algorithm for PMSMs ■optional rotor prepositioning before each motor startup in the PMSM sensorless mode ■optional feed-forward current regulation for PMSM ■more robust hall-sensor module for PMSM ■redesigned PID regulation module ■maximum-modulation-index configuration tool for the single-shunt and three-shunt current-sampling methods ■supports all members of the STM32F103xx performance line family ■workspaces for IAR EWARM 5.20, KEIL RVMDK 3.22, Green Hills MULTI 5.03■Companion parameter file generation tool for PMSM (FOCGUI)1 Presentation of the STM32F103xx AC inductionmotor IFOC software library V2.0The UM0483 user manual describes the AC induction motor IFOC software library, anindirect field oriented control (IFOC) firmware library for 3-phase induction motorsdeveloped for the STM32F103xx microcontrollers.These 32-bit, ARM Cortex™-M3 cored ST microcontrollers (STM32F103xx) come with a setof peripherals which makes it suitable for performing both permanent magnet and ACinduction motors FOC. In particular, this manual describes the STM32F103xx softwarelibrary developed to control AC induction motors equipped with an encoder ortachogenerator, in both torque and speed control modes. The control of a permanentmagnet (PM) motor in sinewave mode with encoder/hall sensors or sensorless is describedin the UM0492 user manual.The AC IM IFOC software library is made of several C modules and is fitted out with IAREWARM 5.20, KEIL RealView MDK 3.22a and Green Hills MULTI 5.03 workspaces. It isused to quickly evaluate both the MCU and the available tools. In addition, when usedtogether with the STM32F103xx motor control starter kit (STM3210B-MCKIT) and an ACinduction motor, a motor can be made to run in a very short time. It also eliminates the needfor time-consuming development of IFOC and speed regulation algorithms by providingready-to-use functions that let the user concentrate on the application layer.A prerequisite for using this library is basic knowledge of C programming, AC motor drivesand power inverter hardware. In-depth know-how of STM32F103xx functions is onlyrequired for customizing existing modules and for adding new ones for a completeapplication development.Figure2 shows the architecture of the firmware. It uses the STM32F103xx standard libraryextensively but it also acts directly on hardware peripherals when optimizations in terms ofexecution speed or code size are required.2/7AC IM IFOC software library V2.0 features (CPU running at72MHz)●Supported speed feedback:–Tachogenerator–Quadrature incremental encoder●Current sampling method:– 2 isolated current sensors (ICS)– 3 shunt resistors placed on the bottom of the three inverter legs–single, common DC link shunt resistor●DAC functionality for tracing the most important software variables●Current regulation for torque and flux control:–PID sampling frequency adjustable up to the PWM frequency●Speed control mode for speed regulation●Torque control mode for torque regulation●Field weakening●16-bit space vector PWM generation frequencies:–PWM frequency can be easily adjusted–Centered PWM pattern type–11 bits resolution at 17.6 kHz●Free C source code and spreadsheet for look-up table generation●CPU load below 21% (IFOC algorithm refresh frequency 10 kHz)●Code size 11.5 KB (three shunt resistors for current reading, tachogenerator for speedfeedback) + 12.6 KB for LCD/joystick managementNote:These figures are for information only; this software library may be subject to changes depending on the final application and peripheral resources. Note that it was built usingrobustness-oriented structures, thus preventing the speed or code size from being fullyoptimized.Related documentsAvailable on :●STM32F103xx datasheet●‘ARM®-based 32-bit MCU STM32F101xx and STM32F103xx, firmware library’ usermanual●‘STM32F103xx Flash programming’ manualAvailable on :●Cortex-M3 T echnical Reference Manual3/72 Presentation of the STM32F103xx permanent-magnetsynchronous motor FOC software library V2.0The UM0492 user manual describes the permanent magnet synchronous motor (PMSM)FOC software library, a field oriented control (FOC) firmware library for 3-phase permanent-magnet motors developed for the STM32F103xx microcontrollers.These 32-bit, ARM Cortex™-M3 cored ST microcontrollers (STM32F103xx) come with a setof peripherals that makes it suitable for performing both permanent-magnet and ACinduction motor FOC. In particular, this manual describes the STM32F103xx software librarydeveloped to control sine-wave driven permanent-magnet motors in both torque and speedcontrol mode. These motors may be equipped with an encoder, with three Hall sensors orthey may be sensorless. The control of an AC induction motor equipped with encoder ortacho generator is described in the UM0483 user manual.The PMSM FOC library is made of several C modules, and is fitted out with IAR EWARM5.20, KEIL RealView MDK 3.22a and Green Hills MULTI 5.03 workspaces. It is used toquickly evaluate both the MCU and the available tools. In addition, when used together withthe STM32F103xx motor control starter kit (STM3210B-MCKIT) and PM motor, a motor canbe made to run in a very short time. It also eliminates the need for time-consumingdevelopment of FOC and speed regulation algorithms by providing ready-to-use functionsthat let the user concentrate on the application layer. Moreover, it is possible to get rid of anyspeed sensor thanks to the sensorless algorithm for rotor position reconstruction.A prerequisite for using this library is basic knowledge of C programming, PM motor drivesand power inverter hardware. In-depth know-how of STM32F103xx functions is onlyrequired for customizing existing modules and for adding new ones for a completeapplication development.Users are assisted in customizing their PMSM application firmware by a parameter filegeneration tool (FOCGUI) which, starting from the system parameters, automaticallygenerates all that is needed by the motor control firmware library to quickly run the motor,saving time and easing the development phase. This tool can be downloaded from:/mcu/.Figure2 shows the architecture of the firmware. It uses the STM32F103xx standard libraryextensively but it also acts directly on hardware peripherals when optimizations in terms ofexecution speed or code size are required.4/7PMSM FOC software library V2.0 features (CPU running at 72MHz)●Supported speed feedbacks:–Sensorless–60° or 120° displaced Hall sensors–Quadrature incremental encoder●Current-sampling method:– 2 isolated current sensors (ICS)–single, common DC link shunt resistor– 3 shunt resistors placed on the bottom of the three inverter lags●optimized IPMSM & SM-PMSM drive●field weakening●feed-forward, high-performance current regulation●DAC functionality for tracing the most important software variables●Brake resistor management●Speed control mode for speed regulation●Torque control mode for torque regulation●16-bit space vector–PWM frequency can be easily adjusted–Centered PWM pattern type–11-bit resolution at 17.6 kHz●Rules for the “a priori” determination of all the parameters necessary for firmwarecustomization●CPU load below 22% in the 3-shunt/sensorless configuration (10 kHz FOC samplingrate)●Code size in 3-shunt/sensorless configuration is about 12.5 Kbytes plus 11.5 Kbytes forLCD/joystick management5/7Revision history TN00636/73 Revision historyTable 1.Document revision history DateRevision Changes 31-Jan-20081Initial release.04-Sep-20082Motor control firmware library package upgraded (release 2.0).New features in this motor control firmware library package release2.0 added.AC IM IFOC software library V2.0 features (CPU running at 72MHz)updated to UM0483 rev. 2.PMSM FOC software library V2.0 features (CPU running at 72MHz)updated to UM0492 rev. 2.16-Sep-20083Library release number corrected in Section 2.TN0063Please Read Carefully:Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries (“ST”) reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.All ST products are sold pursuant to ST’s terms and conditions of sale.Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.UNLESS OTHERWISE SET FORTH IN ST’S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXP RESS OR IMP LIED WARRANTY WITH RESP ECT TO THE USE AND/OR SALE OF ST P RODUCTS INCLUDING WITHOUT LIMITATION IMP LIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. UNLESS EXP RESSLY AP P ROVED IN WRITING BY AN AUTHORIZED ST REP RESENTATIVE, ST P RODUCTS ARE NOT RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY, DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER’S OWN RISK.Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.ST and the ST logo are trademarks or registered trademarks of ST in various countries.Information in this document supersedes and replaces all information previously supplied.The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.© 2008 STMicroelectronics - All rights reservedSTMicroelectronics group of companiesAustralia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America7/7。

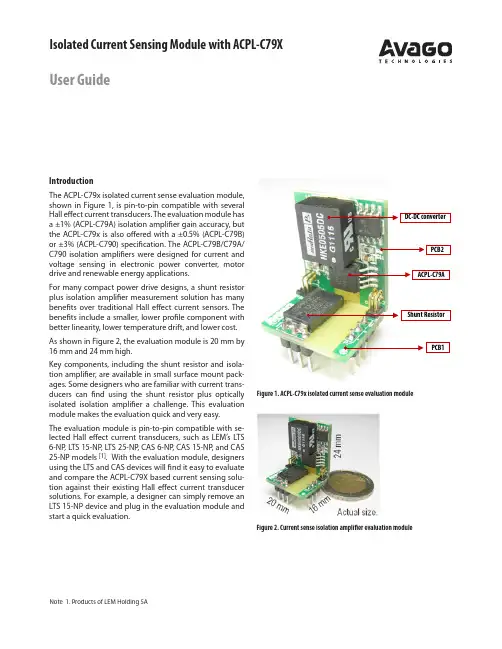

Isolated Current Sensing Module with ACPL-C79X User GuideIntroductionThe ACPL-C79x isolated current sense evaluation module, shown in Figure 1, is pin-to-pin compatible with several Hall effect current transducers. The evaluation module has a ±1% (ACPL-C79A) isolation amplifier gain accuracy, but the ACPL-C79x is also offered with a ±0.5% (ACPL-C79B) or ±3% (ACPL-C790) specification. The ACPL-C79B/C79A/ C790 isolation amplifiers were designed for current and voltage sensing in electronic power converter, motor drive and renewable energy applications.For many compact power drive designs, a shunt resistor plus isolation amplifier measurement solution has many benefits over traditional H all effect current sensors. The benefits include a smaller, lower profile component with better linearity, lower temperature drift, and lower cost. As shown in Figure 2, the evaluation module is 20 mm by 16 mm and 24 mm high.Key components, including the shunt resistor and isola-tion amplifier, are available in small surface mount pack-ages. Some designers who are familiar with current trans-ducers can find using the shunt resistor plus optically isolated isolation amplifier a challenge. This evaluation module makes the evaluation quick and very easy.The evaluation module is pin-to-pin compatible with se-lected H all effect current transducers, such as LEM’s LTS 6-NP, LTS 15-NP, LTS 25-NP, CAS 6-NP, CAS 15-NP, and CAS 25-NP models [1]. With the evaluation module, designers using the LTS and CAS devices will find it easy to evaluate and compare the ACPL-C79X based current sensing solu-tion against their existing H all effect current transducer solutions. For example, a designer can simply remove an LTS 15-NP device and plug in the evaluation module andstart a quick evaluation.Figure 1. ACPL-C79x isolated current sense evaluation moduleFigure 2. Current sense isolation amplifier evaluation moduleNote 1. Products of LEM Holding SAFor product information and a complete list of distributors, please go to our web site: Avago, Avago Technologies, and the A logo are trademarks of Avago Technologies in the United States and other countries.Data subject to change. Copyright © 2005-2012 Avago Technologies. All rights reserved. AV02-3742EN - August 7, 2012Figure 3. The Evaluation module schematicSchematicThe evaluation module circuit schematic is show in Figure 3. The evaluation module is made from two printed circuit boards (PCBs): PCB1 and PCB2. PCB1 has the shunt resis-tor and two header connectors to form a current path; a third header connector is used as an interface. PCB2 has an ACPL-C79A isolation amplifier (±1% gain accuracy) and an isolated DC-DC converter. The two PCBs are assembled with header connectors P4 and P5.AC or DC current through shunt resistor R1 results in a voltage that is proportional to current. This voltage is fil-tered by the anti-aliasing filter formed by R2, R3 and C1 and then sensed by the differential input ACPL-C79A. A differential output voltage that is proportional to the in-put voltage is created on the other side of the optical iso-lation barrier.Following the isolation amplifier, an OPA237 configured as a difference amplifier converts the differential signal to a single-ended output. This stage can be configured to further amplify the signal, if required, and form a low-pass filter to limit the bandwidth.In the evaluation module, the difference amplifier is de-signed for a gain of 1 with a low-pass filter corner frequen-cy of 234 kHz. Resistors R6 and R7 can be selected for a different gain. The bandwidth can be reduced by adding capacitors to the positions of C6 and C8.With the ACPL-C79A gain of 8.2, the overall transfer func-tion is:Vout = I × R1 × 8.2 + Vref .The output signal, Vout, is then connected to the next stage, such as a signal processor, through the P7 header connector, pin 3.Shunt Resistor and Current RangeThe shunt resistor in this module is fixed at 10 milliohm. The appropriate current measurement range is about 15 A RMS . This is calculated from the nominal input range of ±200 mV of the ACPL-C79A. The ACPL-C79x specifies a full scale input range of ±300 mV, which allows accurate overload current detection of up to 21 A PEAK . Because the evaluation module does not provide good heat dissipa-tion for the shunt resistor due to small PCB size, limit cur-rent to 10 A RMS during evaluation or for a quick functional check at 15 A RMS . For a detailed performance evaluation, a PCB with proper layout for the shunt resistor and other components is recommended.Power SuppliesThe evaluation module works on a single 5 V supply, which can be the same power supply for the signal pro-cessor and controller device connected through pin 1 and 2 of P7.The isolated DC-DC converter (U1 in Figure 3) is included in the evaluation module to power up the signal input side of the ACPL C79A; this makes the evaluation an easy plug-and-play operation. However, to make an ACPL C79A based solution cost effective in mass production, the 5 V supply would usually be supplied by a floating power sup-ply, which in many applications could be the same supply that is used to drive the high-side power transistor. A sim-ple three-terminal voltage regulator will provide a stable voltage. Another method is to add an additional winding to an existing transformer to produce a 5 V supply.Note *: Dotted lines denote header pin connections.。