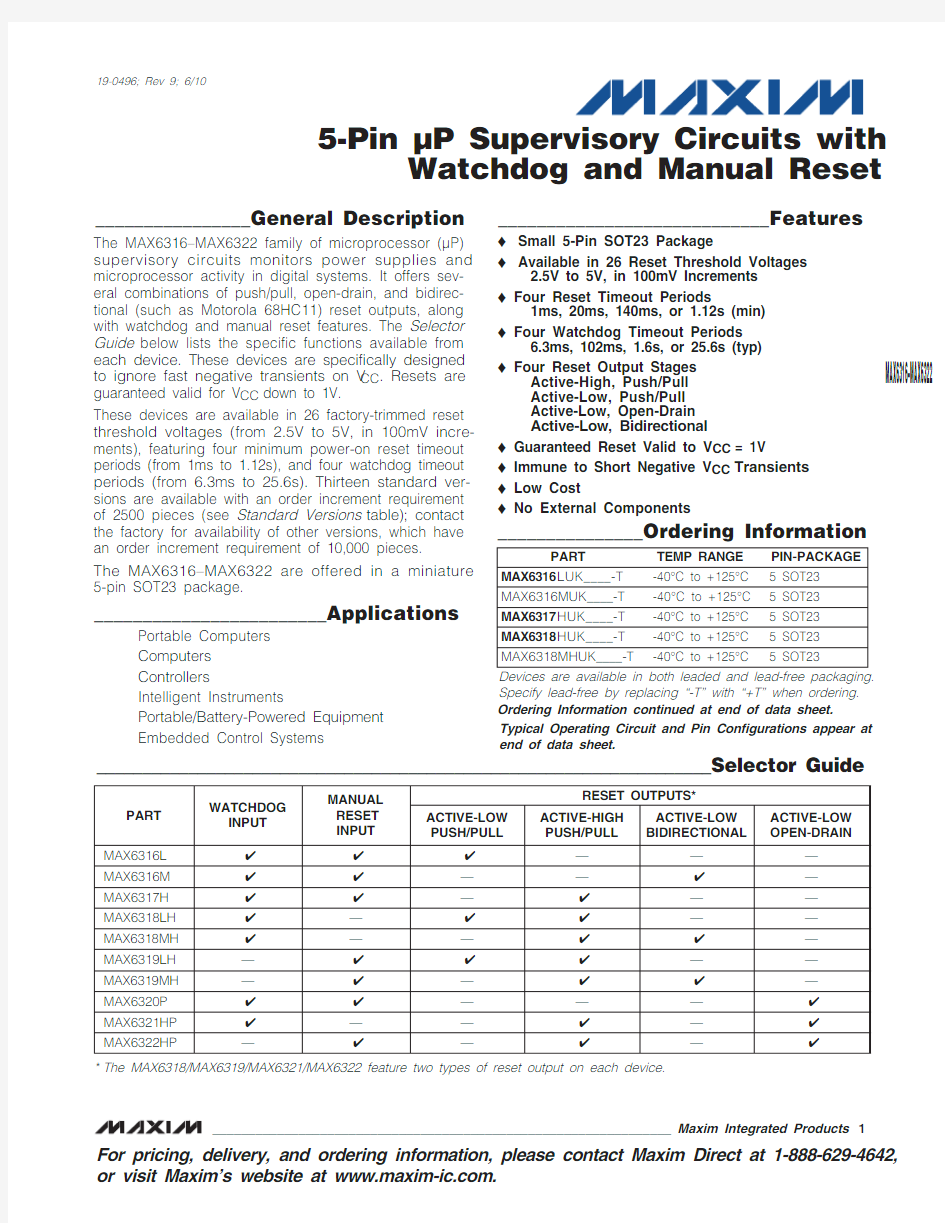

___________________________________________________________________Selector Guide

________________General Description

The MAX6316–MAX6322 family of microprocessor (μP)supervisory circuits monitors power supplies and microprocessor activity in digital systems. It offers sev-eral combinations of push/pull, open-drain, and bidirec-tional (such as Motorola 68HC11) reset outputs, along with watchdog and manual reset features. The Selector Guide below lists the specific functions available from each device. These devices are specifically designed to ignore fast negative transients on V CC . Resets are guaranteed valid for V CC down to 1V.

These devices are available in 26 factory-trimmed reset threshold voltages (from 2.5V to 5V, in 100mV incre-ments), featuring four minimum power-on reset timeout periods (from 1ms to 1.12s), and four watchdog timeout periods (from 6.3ms to 25.6s). Thirteen standard ver-sions are available with an order increment requirement of 2500 pieces (see Standard Versions table); contact the factory for availability of other versions, which have an order increment requirement of 10,000 pieces.

The MAX6316–MAX6322 are offered in a miniature 5-pin SOT23 package.

________________________Applications

Portable Computers Computers Controllers

Intelligent Instruments

Portable/Battery-Powered Equipment Embedded Control Systems

____________________________Features

?Small 5-Pin SOT23 Package

?Available in 26 Reset Threshold Voltages

2.5V to 5V, in 100mV Increments ?Four Reset Timeout Periods

1ms, 20ms, 140ms, or 1.12s (min)?Four Watchdog Timeout Periods

6.3ms, 102ms, 1.6s, or 25.6s (typ) ?Four Reset Output Stages

Active-High, Push/Pull Active-Low, Push/Pull Active-Low, Open-Drain Active-Low, Bidirectional

?Guaranteed Reset Valid to V CC = 1V

?Immune to Short Negative V CC Transients ?Low Cost

?No External Components

MAX6316–MAX6322

5-Pin μP Supervisory Circuits with

Watchdog and Manual Reset

________________________________________________________________Maxim Integrated Products 1

19-0496; Rev 9; 6/10

_______________Ordering Information

Ordering Information continued at end of data sheet.

*The MAX6318/MAX6319/MAX6321/MAX6322 feature two types of reset output on each device.

Typical Operating Circuit and Pin Configurations appear at end of data sheet.

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642,or visit Maxim’s website at https://www.doczj.com/doc/b94915196.html,.

Specify lead-free by replacing “-T” with “+T” when ordering.

ELECTRICAL CHARACTERISTICS

(V

= 2.5V to 5.5V, T = -40°C to +125°C, unless otherwise noted. Typical values are at T = +25°C.) (Note 1)

M A X 6316–M A X 6322

5-Pin μP Supervisory Circuits with Watchdog and Manual Reset 2

_______________________________________________________________________________________

ABSOLUTE MAXIMUM RATINGS

Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Voltage (with respect to GND)

V CC ......................................................................-0.3V to +6V RESET (MAX6320/MAX6321/MAX6322 only)...... -0.3V to +6V All Other Pins.........................................-0.3V to (V CC + 0.3V)Input/Output Current, All Pins.............................................20mA Continuous Power Dissipation (T A = +70°C)

S OT23 (derate 7.1mW/°C above +70°C)..................571mW

Operating Temperature Range..........................-40°C to +125°C Junction Temperature......................................................+150°C Storage Temperature Range..............................-65°C to +160°C Lead Temperature (soldering, 10s).................................+300°C Soldering Temperature (reflow)

Leaded Package.........................................................+240°C Lead-Free Package.....................................................+260°C

available in 100mV increments from 2.5V to 5V (see Table 1 at end of data sheet).

Note 3:Guaranteed by design.

MAX6316–MAX6322

5-Pin μP Supervisory Circuits with

Watchdog and Manual Reset

_______________________________________________________________________________________

3

Note 5:Measured from RESET V OL to (0.8 x V CC ), R LOAD = ∞.

Note 6:WDI is internally serviced within the watchdog period if WDI is left unconnected.

Note 7:

The WDI input current is specified as the average input current when the WDI input is driven high or low. The WDI input is designed for a three-stated-output device with a 10μA maximum leakage current and capable of driving a maximum capac-itive load of 200pF. The three-state device must be able to source and sink at least 200μA when active.

ELECTRICAL CHARACTERISTICS (continued)

M A X 6316–M A X 6322

5-Pin μP Supervisory Circuits with Watchdog and Manual Reset 4_______________________________________________________________________________________

__________________________________________Typical Operating Characteristics

(T A = +25°C, unless otherwise noted.)

021*********-40

20

-20

40

60

80

100MAX6316/MAX6317/MAX6318/MAX6320/MAX6321

SUPPLY CURRENT vs. TEMPERATURE

TEMPERATURE (°C)S U P P L Y C U R R E N T (μA )

302010504090

807060100-40-20020406080100

V CC FALLING TO RESET PROPAGATION

DELAY vs. TEMPERATURE

TEMPERATURE (°C)R E S E T P R O P A G A T I O N D E L A Y (μs )

140

180160240220200300280260320

-40020-20406080100

MAX6316/MAX6317/MAX6319/MAX6320/MAX6322

MANUAL RESET TO RESET

PROPAGATION DELAY vs. TEMPERATURE

TEMPERATURE (°C)

P R O P A G A T I O N D E L A Y (n s )

0.95

0.980.970.961.000.991.041.031.021.011.05-40

-20

20

40

60

80

100

NORMALIZED RESET TIMEOUT PERIOD vs. TEMPERATURE

M A X 6316t o c 04

TEMPERATURE (°C)

N O R M A L I Z E D R E S E T T I M E O U T P E R I O D

0.95

0.980.970.961.000.991.041.031.021.011.05

-40

-20

20

40

60

80

100

MAX6316/MAX6317/MAX6318/MAX6320/MAX6321

NORMALIZED WATCHDOG TIMEOUT

PERIOD vs. TEMPERATURE

M A X 6316t o c 05

TEMPERATURE (°C)

N O R M A L I Z E D W A T C H D O G T I M E O U T P E R I O D

80

010

100

1000MAXIMUM V CC TRANSIENT DURATION vs. RESET THRESHOLD OVERDRIVE

2010

RESET THRESHOLD OVERDRIVE (mV) V RST - V CC

T R A N S I E N T D U R A T I O N (μs )

3050604070

200ns/div

MAX6316M/6318MH/6319MH

BIDIRECTIONAL

PULLUP CHARACTERISTICS

MAX6316–MAX6322

5-Pin μP Supervisory Circuits with

Watchdog and Manual Reset

_______________________________________________________________________________________5

______________________________________________________________Pin Description

M A X 6316–M A X 6322

5-Pin μP Supervisory Circuits with Watchdog and Manual Reset 6

_______________________________________________________________________________________

_______________Detailed Description

A microprocessor’s (μP) reset input starts or restarts the μP in a known state. The reset output of the MAX6316–MAX6322 μP supervisory circuits interfaces with the reset input of the μP, preventing code-execution errors during power-up, power-down, and brownout condi-tions (see the Typical Operating Circuit ). The MAX6316/MAX6317/MAX6318/MAX6320/MAX6321 are also capa-ble of asserting a reset should the μP become stuck in an infinite loop.

Reset Output

The MAX6316L/MAX6318LH/MAX6319LH feature an active-low reset output, while the MAX6317H/MAX6318_H/MAX6319_H/MAX6321HP/MAX6322HP feature an active-high reset output. RESET is guaran-teed to be a logic low and RESET is guaranteed to be a logic high for V CC down to 1V.

The MAX6316–MAX6322 assert reset when V CC is below the reset threshold (V RST ), when MR is pulled low (MAX6316_/MAX6317H/MAX6319_H/MAX6320P/MAX6322HP only), or if the WDI pin is not serviced within

the watchdog timeout period (t WD ). Reset remains assert-ed for the specified reset active timeout period (t RP ) after V CC rises above the reset threshold, after MR transitions low to high, or after the watchdog timer asserts the reset (MAX6316_/MAX6317H/MAX6318_H/MAX6320P/MAX6321HP). After the reset active timeout period (t RP )expires, the reset output deasserts, and the watchdog timer restarts from zero (Figure 2).

Figure 1. Functional Diagram

Figure 2. Reset Timing Diagram

MAX6316–MAX6322

5-Pin μP Supervisory Circuits with

Watchdog and Manual Reset

_______________________________________________________________________________________

7

Bidirectional R E S E T Output

The MAX6316M/MAX6318MH/MAX6319MH are designed to interface with μPs that have bidirectional reset pins,such as the Motorola 68HC11. Like an open-drain output,these devices allow the μP or other devices to pull the bidirectional reset (RESET ) low and assert a reset condi-tion. However, unlike a standard open-drain output, it includes the commonly specified 4.7k Ωpullup resistor with a P-channel active pullup in parallel.

This configuration allows the MAX6316M/MAX6318MH/MAX6319MH to solve a problem associated with μPs that have bidirectional reset pins in systems where sev-eral devices connect to RESET (Figure 3). These μPs can often determine if a reset was asserted by an exter-nal device (i.e., the supervisor IC) or by the μP itself (due to a watchdog fault, clock error, or other source),and then jump to a vector appropriate for the source of the reset. However, if the μP does assert reset, it does not retain the information, but must determine the cause after the reset has occurred.

The following procedure describes how this is done in the Motorola 68HC11. In all cases of reset, the μP pulls RESET low for about four external-clock cycles. It then releases RESET , waits for two external-clock cycles,then checks RESET ’s state. If RESET is still low, the μP concludes that the source of the reset was external and, when RESET eventually reaches the high state, it jumps to the normal reset vector. In this case, stored-state information is erased and processing begins from

scratch. If, on the other hand, RESET is high after a delay of two external-clock cycles, the processor knows that it caused the reset itself and can jump to a different vector and use stored-state information to determine what caused the reset.

A problem occurs with faster μPs; two external-clock cycles are only 500ns at 4MHz. When there are several devices on the reset line, and only a passive pullup resis-tor is used, the input capacitance and stray capacitance can prevent RESET from reaching the logic high state (0.8?V CC ) in the time allowed. If this happens, all resets will be interpreted as external. The μP output stage is guaran-teed to sink 1.6mA, so the rise time can not be reduced considerably by decreasing the 4.7k Ωinternal pullup resistance. See Bidirectional Pullup Characteristics in the Typical Operating Characteristics .

The MAX6316M/MAX6318MH/MAX6319MH overcome this problem with an active pullup FET in parallel with the 4.7k Ωresistor (Figures 4 and 5). The pullup transistor holds RESET high until the μP reset I/O or the supervisory circuit itself forces the line low. Once RESET goes below V PTH , a comparator sets the transition edge flip-flop, indi-cating that the next transition for RESET will be low to high. When RESET is released, the 4.7k Ωresistor pulls RESET up toward V CC . Once RESET rises above V PTH but is below (0.85 x V CC ), the active P-channel pullup turns on. Once RESET rises above (0.85 x V CC ) or the 2μs one-shot times out, the active pullup turns off. The parallel combination of the 4.7k Ωpullup and the

Figure 3. MAX6316M/MAX6318MH/MAX6319MH Supports Additional Devices on the Reset Bus

M A X 6316–M A X 6322

5-Pin μP Supervisory Circuits with Watchdog and Manual Reset 8_______________________________________________________________________________________

Figure 4. MAX6316/MAX6318MH/MAX6319MH Bidirectional Reset Output Functional Diagram

MAX6316–MAX6322

5-Pin μP Supervisory Circuits with

Watchdog and Manual Reset

_______________________________________________________________________________________9

P-channel transistor on-resistance quickly charges stray capacitance on the reset line, allowing RESET to transition from low to high within the required two elec-tronic-clock cycles, even with several devices on the reset line. This process occurs regardless of whether the reset was caused by V CC dipping below the reset threshold, the watchdog timing out, MR being asserted,or the μP or other device asserting RESET . The parts do not require an external pullup. To minimize supply cur-rent consumption, the internal 4.7k Ωpullup resistor dis-connects from the supply whenever the MAX6316M/MAX6318MH/MAX6319MH assert reset.

Open-Drain R E S E T Output

The MAX6320P/MAX6321HP/MAX6322HP have an active-low, open-drain reset output. This output struc-ture will sink current when RESET is asserted. Connect a pullup resistor from RESET to any supply voltage up to 6V (Figure 6). Select a resistor value large enough to

register a logic low (see Electrical Characteristics ), and small enough to register a logic high while supplying all input current and leakage paths connected to the RESET line. A 10k Ωpullup is sufficient in most applications.

Manual-Reset Input

The MAX6316_/MAX6317H/MAX6319_H/MAX6320P/MAX6322HP feature a manual reset input. A logic low on MR asserts a reset. After MR transitions low to high, reset remains asserted for the duration of the reset timeout peri-od (t RP ). The MR input is connected to V CC through an internal 52k Ωpullup resistor and therefore can be left unconnected when not in use. MR can be driven with TTL-logic levels in 5V systems, with CMOS-logic levels in 3V systems, or with open-drain or open-collector output devices. A normally-open momentary switch from MR to ground can also be used; it requires no external debouncing circuitry. MR is designed to reject fast, negative-going transients (typically 100ns pulses). A 0.1μF capacitor from MR to ground provides additional noise immunity.

The MR input pin is equipped with internal ESD-protection circuitry that may become forward biased. Should MR be driven by voltages higher than V CC , excessive current would be drawn, which would damage the part. For example, assume that MR is driven by a +5V supply other than V CC . If V CC drops lower than +4.7V, MR ’s absolute maximum rating is violated [-0.3V to (V CC + 0.3V)], and undesirable current flows through the ESD structure from MR to V CC . To avoid this, use the same supply for MR as the supply monitored by V CC . This guarantees that the voltage at MR will never exceed V CC .

Watchdog Input

The MAX6316_/MAX6317H/MAX6318_H/MAX6320P/MAX6321HP feature a watchdog circuit that monitors the μP’s activity. If the μP does not toggle the watchdog input (WDI) within the watchdog timeout period (t WD ),reset asserts. The internal watchdog timer is cleared by reset or by a transition at WDI (which can detect pulses as short as 50ns). The watchdog timer remains cleared while reset is asserted. Once reset is released, the timer begins counting again (Figure 7).

The WDI input is designed for a three-stated output device with a 10μA maximum leakage current and the capability of driving a maximum capacitive load of 200pF.The three-state device must be able to source and sink at least 200μA when active. Disable the watchdog function by leaving WDI unconnected or by three-stating the driver connected to WDI. When the watchdog timer is left open circuited, the timer is cleared internally at intervals equal to 7/8 of the watchdog period.

Figure 6. MAX6320P/MAX6321HP/MAX6322HP Open-Drain RESET Output Allows Use with Multiple Supplies

Figure 5. Bidirectional RESET Timing Diagram

M A X 6316–M A X 6322

5-Pin μP Supervisory Circuits with Watchdog and Manual Reset 10

______________________________________________________________________________________

Applications Information

Watchdog Input Current

The WDI input is internally driven through a buffer and series resistor from the watchdog counter. For minimum watchdog input current (minimum overall power con-sumption), leave WDI low for the majority of the watch-dog timeout period. When high, WDI can draw as much as 160μA. Pulsing WDI high at a low duty cycle will reduce the effect of the large input current. When WDI is left unconnected, the watchdog timer is serviced within the watchdog timeout period by a low-high-low pulse from the counter chain.

Negative-Going V CC Transients

These supervisors are immune to short-duration, nega-tive-going V CC transients (glitches), which usually do not require the entire system to shut down. Typically,200ns large-amplitude pulses (from ground to V CC ) on the supply will not cause a reset. Lower amplitude puls-es result in greater immunity. Typically, a V CC transient that goes 100mV under the reset threshold and lasts less than 4μs will not trigger a reset. An optional 0.1μF bypass capacitor mounted close to V CC provides addi-tional transient immunity.

Ensuring Valid Reset Outputs

Down to V CC = 0

The MAX6316_/MAX6317H/MAX6318_H/MAX6319_H/MAX6321HP/MAX6322HP are guaranteed to operate properly down to V CC = 1V. In applications that require valid reset levels down to V CC = 0, a pulldown resistor to active-low outputs (push/pull and bidirectional only,Figure 8) and a pullup resistor to active-high outputs (push/pull only, Figure 9) will ensure that the reset line

is valid while the reset output can no longer sink or

source current. This scheme does not work with the open-drain outputs of the MAX6320/MAX6321/MAX6322.The resistor value used is not critical, but it must be large enough not to load the reset output when V CC is above the reset threshold. For most applications,100k Ωis adequate.

Watchdog Software Considerations

(MAX6316/MAX6317/MAX6318/

MAX6320/MAX6321)

One way to help the watchdog timer monitor software execution more closely is to set and reset the watchdog input at different points in the program, rather than pulsing the watchdog input high-low-high or low-high-low. This technique avoids a stuck loop, in which the watchdog timer would continue to be reset inside the loop, keeping the watchdog from timing out.

Figure 7. Watchdog Timing Relationship

Figure 9. Ensuring RESET Valid to V CC = 0 on Active-High Push/Pull Outputs

Figure 8. Ensuring RESET Valid to V CC = 0 on Active-Low Push/Pull and Bidirectional Outputs

MAX6316–MAX6322

5-Pin μP Supervisory Circuits with

Watchdog and Manual Reset

______________________________________________________________________________________11

Figure 10 shows an example of a flow diagram where the I/O driving the watchdog input is set high at the beginning of the program, set low at the end of every subroutine or loop, then set high again when the pro-gram returns to the beginning. If the program should hang in any subroutine, the problem would be quickly corrected, since the I/O is continually set low and the watchdog timer is allowed to time out, causing a reset or interrupt to be issued. As described in the Watchdog Input Current section, this scheme results in higher time average WDI current than does leaving WDI low for the majority of the timeout period and periodically pulsing it low-high-low.

Figure 10. Watchdog Flow Diagram

__________________Pin Configurations

Typical Operating Circuit

M A X 6316–M A X 6322

5-Pin μP Supervisory Circuits with Watchdog and Manual Reset

MAX6316–MAX6322

__Ordering Information (continued)

Note:These devices are available with factory-set V CC reset

thresholds from 2.5V to 5V, in 0.1V increments. Insert the

desired nominal reset threshold (25 to 50, from Table 1) into the

blanks following the letters UK. All devices offer factory-pro-

grammed reset timeout periods. Insert the letter corresponding

to the desired reset timeout period (A, B, C, or D from Table 3)

into the blank following the reset threshold suffix. Parts that offer

a watchdog feature (see Selector Guide) are factory-trimmed to

one of four watchdog timeout periods. Insert the letter corre-

sponding to the desired watchdog timeout period (W, X, Y, or Z

from Table 3) into the blank following the reset timeout suffix.

5-Pin μP Supervisory Circuits with

Watchdog and Manual Reset ______________________________________________________________________________________13

TRANSISTOR COUNT: 191

SUBSTRATE IS INTERNALLY CONNECTED TO V+

Chip Information

dard versions only. The required order increment for nonstandard versions is 10,000 pieces. Contact factory for availability.

Devices are available in both leaded and lead-free packaging.

Specify lead-free by replacing “-T” with “+T” when ordering.

/V denotes an automotive qualified part.

Package Information

For the latest package outline information and land patterns,

go to https://www.doczj.com/doc/b94915196.html,/packages. Note that a “+”, “#”, or

“-” in the package code indicates RoHS status only. Package

drawings may show a different suffix character, but the drawing

pertains to the package regardless of RoHS status.

M A X 6316–M A X 6322

5-Pin μP Supervisory Circuits with Watchdog and Manual Reset Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

14____________________Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600?2010 Maxim Integrated Products

Maxim is a registered trademark of Maxim Integrated Products, Inc.

复位/上电(外部)复位/低电压检测和复位/看门狗定时器复位 复位电路产生一个一定宽度的复位脉冲信号去复位整个电路,使其工作在预设的状态,保证电路从一个预先已知的状态开始工作。SH66/67/69xxx系列单片机复位功能包括上电(外部)复位、低电压复位、看门狗定时器复位等。 1.上电复位 ( Power On Reset,POR )及外部复位 内建的上电复位电路配合外接的上电复位辅助电路,在上电时产生复位脉冲信号复位整个电路,保证电路从一个预先已知的预设状态开始工作。 SH66/67/69xxx系列单片机内建了稳定的上电复位电路,在复位输入端外接的复位辅助电路配合下,单片机具有稳定可靠上电复位性能。同时,复位输入端也作为外部复位的输入端,输入外部复位信号复位整个电路。中颖的SH66/67/69xxx 系列单片机普遍采用低电平有效的复位方式。按应用场合和对上电复位可靠性要求不同,复位外部电路可采用不同的方式。 简易型RC复位电路 最简单的上电复位电路即是用RC充放电电路所构成(如图1-1),应用于干扰较小的环境。复位时间长短由电阻R和电容C的值决定。复位时间的长短,一般考虑为当系统电源稳定进入单片机工作范围时,才可结束复位。当单片机断电时,C上的电荷应尽快完全放电,以保证下次复位的成功。R和C建议数值为47k.和0.1μF。复位电路的布线很重要,一般要求复位电容C与单片机的Reset 和VSS引脚的布线最短。 R C 图1-1 简易型RC复位电路 改良型RC复位电路 为了让上电复位更加稳定,在简易型RC复位电路的基础上,可以在电阻位置并联一个二极管构成改良型RC复位电路(如图1-2)。复位时间长短仍由R 和C的值决定。当单片机断电时,附加的二极管D可使电容C上的电荷快速完全放电,以保证下次复位的成功。

TMS320F2812 Watchdog范例程序 FILE: Example_28xWatchdog.c // // TITLE: DSP28 Watchdog interrupt test program. // // ASSUMPTIONS: // // This program requires the DSP28 header files. To compile the // program as is, it should reside in the DSP28/examples/watchdog // sub-directory. // // As supplied, this project is configured for "boot to H0" operation. // // DESCRIPTION: // This program exercises the watchdog on the F2812/F2810 parts. // // First the watchdog is connected to the WAKEINT interrupt of the // PIE block. The code is then put into an infinite loop. // // The user can select to feed the watchdog key register or not // by commenting one line of code in the infinite loop. // // If the watchdog key register is fed by the KickDog function // then the WAKEINT interrupt is not taken. If the key register // is not fed by the KickDog function then WAKEINT will be taken. // // Watch Variables: // LoopCount for the number of times through the infinite loop // WakeCount for the number of times through WAKEINT // //########################################################################### // // Ver | dd mmm yyyy | Who | Description of changes // =====|=============|======|=============================================== // 0.57| 29 May 2002 | L.H. | Initial Release //########################################################################### // Step 0. Include required header files // DSP28_Device.h: device specific definitions #include statements for // all of the peripheral .h definition files. // DSP28_Example.h is specific for the given example. #include "DSP28_Device.h"

看门狗攻略《看门狗》流程攻略图文详解小编今天为大家带来的是看门狗全流程攻略,为大家详细讲解《看门狗》全部剧情流程,希望这个看门狗攻略大家能喜欢。 第一章-01.8局下半 注:第一节名为“8局下半”,这是棒球的术语,棒球比赛共有9局,分上半和下半。 那么去到8局下半,亦即是比赛进入了白热化的阶段。 另外首先本节内容是在正在举行棒球比赛的场馆中举行,也有一定相关星。 剧情:艾登与他的师傅戴米安内应外合,艾登负责潜入到海洛特酒店的大厅(艾登与一名装束密实的黑人女子发生碰撞),艾登马上开始骇入,两人过了片刻便盗取了大厅所有人的银行账户存款。 可是艾登发现了此网路亦有另一伙人骇入,可是戴米安却不以为然,仍希望通过一己之力揪出竞争对手,可是被人对方骇入了艾登与戴米安的系统,艾登只好马上脱离。 反侦察戴米安与艾登的神秘人致电给一名叫作莫里斯的收尾者,让他去收拾艾登及其妻女。 剧情:(11嗰月之后)艾登找到了莫里斯,艾登已经将他打得眼肿鼻青,但此人矢口否认与艾登家人被害有关,随后艾登便拿出了莫里斯与神秘人的对话录音。 总算,莫里斯是承认了自己有参与袭击,但是他没有意识到要袭击小孩(导致艾登的侄女 去世),他就没有痛下杀手(起码心里没有这种想法),他告诉艾登,操纵此事件的幕后集团相当庞大,一旦他泄露,肯定人间蒸发。

step1.既然莫里斯不肯说出实情,就拿出手枪要吓唬他一下,此时手枪并没有子弹(被约尔迪给拿走了弹夹),对准莫里斯然后按RT键。 step2.眼见被耍,莫里斯马上捡起地上的球棒往艾登袭击,此时按B键使用伸缩棍予以还击,将其打晕。

step3.既然莫里斯如此守口如瓶,那么就走到75周年锦旗旁的货物架前,按X键骇入莫里斯的收集。 剧情:听完莫里斯手机中的录音后,离开更衣室,去到走廊上会被莫里斯的几嗰手下给逮住,幸好约尔迪出手相助。 约尔迪才离开艾登2分钟,艾登就因为急于盘问莫里斯就冲动行事,约尔迪之前离开就是去打电话报警,因为他知道艾登莽撞,所以喊来警察,然后将现场伪装成是帮派狗咬狗的情节,那么黑道就不容易会追查到艾登他们。 step4.两人决定分头逃跑,因为艾登与莫里斯的仇口太深,所以就让约尔迪带着昏睡的莫里斯离开。

瑞士EM6323复位+看门狗芯片 描述 EM6323/24是低功耗,高精密复位IC 具有手动复位和看门狗输入。他们有 不同的阈值电压和几个超时复位期间 (TPOR)和看门狗超时周期为最大(TWD) 在应用程序的灵活性。EM6323具有手动复位(MR 内部上拉)和一个看门狗输入引脚。EM6324具有 只有一个看门狗输入引脚(WDI)。看门狗功能 被禁用或三态驱动器驱动世界发展指标“ 让世界发展指标“无关。这是有用的,当MCU 睡眠模式。 小型SOT23-5L封装以及超低电源电流 3.8μAEM6323和EM6324的理想选择 便携式和电池供电设备。 特点 !超低电源电流3.8μA(VDD = 3.3V) !工作温度范围:-40°C至+125°C的 !复位门限精度±1.5% !11复位阈值电压VTH,4.63V,4.4V,3.08V, 2.93V,2.63V,2.2V,1.8V,1.66V,1.57V,1.38V,1.31V !200ms的复位超时周期(1.6ms,25ms的,1600ms之间 请求) ! 1.6s的看门狗超时周期(6.2ms,102ms,25.6s 请求) !3重置输出选项: 低电平复位推,拉 低电平复位漏极开路 高电平复位推- 拉 !在睡眠模式下的单片机检测 复位阈值电压: 看门狗输入。世界发展指标“必须与CMOS输出驱动。如果单片机的I / O在高阻抗条件下,电路将检测到这种情况,作为微控制器在休眠模式,并防止 其看门狗超时 阈值电压 复位输出 一个微处理器(μP)复位输入开始在微处理器 已知状态。EM6323/24微处理器监控电路 断言复位,以防止代码执行错误,在 上电,掉电和欠压条件。复位 保证是低的VDD下降至0.9V的逻辑。

看门狗电路设计 在工业现场运行的单片机应用系统,由于坏境恶劣,常有强磁场、电源尖峰、电火花等外界干扰,这些干扰可能造成仪表中单片机的程序运行出现“跑飞”现象,引起程序混乱,输出或显示不正确,甚至“死机”。系统无法继续正常的运行,处在一种瘫痪状态,它的硬件电路并没有损坏,只是内部程序运行出现了错误,这时,即使干扰消失,系统也不会恢复正常,这就需要采取一些措施来保障系统失控后能自动恢复正常,“程序运行几天来视系统”(Watchdog看门狗)就是常用的一种抗干扰措施,用以保证系统因干扰失控后能自动复位。为了提高仪表可靠性及抗干扰能力,通常在智能仪表中采用“看门狗”技术。 看门狗电路它实质上是一个可由CPU复位的定时器,它的定时时间是固定不变的,一旦定时时间到,电路就产生复位信号或中断信号。当程序正常运行时,在小于定时时间隔内,单片机输出一信号刷新定时器,定时器处于不断的重新定时过程,因此看门狗电路就不会产生复位信号或中断信号,反之,当程序因出现干扰而“跑飞”时,单片机不能刷新定时器,产生复位信号或产生中断信号使单片机复位或中断,在中断程序中使其返回到起始程序,恢复正常。 它的工作原理如同图3-4所示的两个计时周期不同的定时器T1和T2是两个时钟源相同的定时器,设T1=1.0s,T2=1.1s,而用T1定时器的溢出脉冲P1同时对T1和T2定时器清零,只要T1定时器工作正常,则定时器T2永远不可能计时溢出。当T1定时器不在计时,定时器T2则会计时溢出,并产生溢出脉冲P2。一旦产生溢出脉冲P2,则表明T1出了故障。这里的T2即是看门狗。利用溢出脉冲P2并进行巧妙的程序设计,可以检测系统的出错,而后使“飞掉”的程序重新恢复运行。 图3-4 看门狗工作原理示意图 看门狗电路的应用,使单片机可以在无人关态下实现连续工作。看门狗芯片和单片机的一个I/O引脚相连,该I/O引脚通过程序控制它定时地往看门狗的这

看门狗分硬件看门狗和软件看门狗。硬件看门狗是利用一个定时器电路,其定时输出连接到电路的复位端,程序在一定时间范围内对定时器清零(俗称“喂狗”),因此程序正常工作时,定时器总不能溢出,也就不能产生复位信号。如果程序出现故障,不在定时周期内复位看门狗,就使得看门狗定时器溢出产生复位信号并重启系统。软件看门狗原理上一样,只是将硬件电路上的定时器用处理器的内部定时器代替,这样可以简化硬件电路设计,但在可靠性方面不如硬件定时器,比如系统内部定时器自身发生故障就无法检测到。当然也有通过双定时器相互监视,这不仅加大系统开销,也不能解决全部问题,比如中断系统故障导致定时器中断失效。 看门狗本身不是用来解决系统出现的问题,在调试过程中发现的故障应该要查改设计本身的错误。加入看门狗目的是对一些程序潜在错误和恶劣环境干扰等因素导致系统死机而在无人干预情况下自动恢复系统正常工作状态。看门狗也不能完全避免故障造成的损失,毕竟从发现故障到系统复位恢复正常这段时间内怠工。同时一些系统也需要复位前保护现场数据,重启后恢复现场数据,这可能也需要一笔软硬件的开销。 图1:(a) 多任务系统看门狗示意图;(b) 相应的看门狗复位逻辑图。 在单任务系统中看门狗工作原理如上所述,容易实现。在多任务系统中情况稍为复杂。假如每个任务都像单任务系统那么做,如图1(a)所示,只要有一个任务正常工作并定期“喂狗”,看门狗定时器就不会溢出。除非所有的任务都故障,才能使得看门狗定时器溢出而复位,如图1(b)。 而往往我们需要的是只要有一个任务故障,系统就要求复位。或者选择几个关键的任务接受监视,只要一个任务出问题系统就要求复位,如图2(a)所示,相应的看门狗复位逻辑如图2(b)所示。 在多任务系统中通过创建一个监视任务TaskMonitor,它的优先级高于被监视的任务群Task1、Task2...Taskn。TaskMonitor在Task1~Taskn正常工作情况下,一定时间内对硬件看门狗定时器清零。如果被监视任务群有一个Task_x出现故障,TaskMonitor就不对看门狗定时器清零,也就达到被监视任务出现故障时系统自动重启的目的。另外任务TaskMonitor自身出故障时,也不能及时对看门狗定时器清零,看门狗也能自动复位重启。

看门狗定时器用来防止程序因供电电源、空间电磁干扰或其它原因引起的强烈干扰噪声而跑飞的事故。程序中设置看门狗清零指令 WDTCTL=WDTPW+WDTCNTCL,当程序跑飞不能及时清零看门狗,导致看门狗溢出复位,这样程序可以恢复正常运行状态。 一、WDT寄存器包括WDTCNT和WDTCTL,两个寄存器在上电和系统复位内容全部清零 1.记数单元WDTCNT:WDTCNT是16位增记数器,由MSP430选定的时钟电路产生的固定周期脉冲信号对记数器进行加法记数。WDTCNT不能直接软件存取,必须通过看门狗定时器的控制寄存器WDTCTL来控制。 2.控制寄存器WDTCTL:WDTCTL由两部分组成,高8位用作口令,即5AH(头文件中定义为WDTPW),低8位是对WDT操作的控制命令。写入WDT控制命令时先写入口令WD TPW,口令写错将导致系统复位。读WDTCTL时不需口令,低字节WDTCTL的值,高字节读出始终为69H。 bit 15-8 7 6 5 4 3 2 1 0 口令HOLD NMIES NMI TMSE L CNTCL SSEL IS1 IS0 IS1 SI0 选择看门狗定时器的定时输出,T为WDTCNT的输入时钟源周期。 TMSEL W DT工作模式选择 0 0 T*2的15次 方 0 看门狗模式 0 1 T*2的13次

方 1 定时器模式 1 0 T*2的9次 方 NMI 选择RST/NMI 引脚功能 1 1 T*2的6次 方 RST/NMI为复位端 SSEL 选择WDTCNT的时钟 源 1 RST/NMI为非屏蔽中断输入 0 SMCL K 1 ACLK NMIES 选择NMI中断的边沿触发方 式 HOLD 停止看门狗定时器工作 0 上升沿触发NMI中 断 0 看门狗功能激活 1 下降沿触发NMI中 断 1 时钟禁止输入,记数停止

看门狗电路。在单片机中,为了能使得程序能够正常的运行。设定的及时根据程序所返回的值检测程序运行情况的定时电路。 在主程序中设定一定的值,把这个值在看门狗定时电路数值益处之前定时赋给看门狗赋给定时电路,让看门狗定时器复位。主程序的赋值周期要小于看门狗定时电路的运行周期。 看门狗 百科名片 单片机"看门狗" 在由单片机构成的微型计算机系统中,由于单片机的工作常常会受到来自外界电磁场的干扰,造成程序的跑飞,而陷入死循环,程序的正常运行被打断,由单片机控制的系统无法继续工作,会造成整个系统的陷入停滞状态,发生不可预料的后果,所以出于对单片机运行状态进行实时监测的考虑,便产生了一种专门用于监测单片机程序运行状态的芯片,俗称"看门狗"(watchdog) 目录[隐藏] 应用 基本原理 看门狗使用注意 看门狗运用 设计思路 [编辑本段]应用 看门狗电路的应用,使单片机可以在无人状态下实现连续工作,其工作原理是:看门狗芯片和单片机的一个I/O引脚相连,该I/O引脚通过程序控制它定时地往看门狗的这个引脚上送入高电平(或低电平),这一程序语句是分散地放在单片机其他控制语句中间的,一旦单片机由于干扰造成程序跑飞后而陷入某一程序段进入死循环状态时,写看门狗引脚的程序便不能被执行,这个时候,看门狗电路就会由于得不到单片机送来的信号,便在它和单片机复位引脚相连的引脚上送出一个复位信号,使单片机发生复位,

即程序从程序存储器的起始位置开始执行,这样便实现了单片机的自动复位。 [编辑本段]基本原理 看门狗,又叫watchdog timer,是一个定时器电路, 一般有一个输入,叫喂狗(kicking the dog or service the dog),一个输出到MCU的RST端,MCU正常工作的时候,每隔一端时间输出一个信号到喂狗端,给WDT 清零,如果超过规定的时间不喂狗,(一般在程序跑飞时),WDT 定时超过,就会给出一个复位信号到MCU,使MCU复位. 防止MCU死机. 看门狗的作用就是防止程序发生死循环,或者说程序跑飞。工作原理:在系统运行以后也就启动了看门狗的计数器,看门狗就开始自动计数,如果到了一定的时间还不去清看门狗,那么看门狗计数器就会溢出从而引起看门狗中断,造成系统复位。所以在使用有看门狗的芯片时要注意清看门狗。硬件看门狗是利用了一个定时器,来监控主程序的运行,也就是说在主程序的运行过程中,我们要在定时时间到之前对定时器进行复位如果出现死循环,或者说PC指针不能回来。那么定时时间到后就会使单片机复位。常用的WDT芯片如MAX813 ,5045, IMP 813等,价格4~10元不等. 软件看门狗技术的原理和这差不多,只不过是用软件的方法实现,我们还是以51系列来讲,我们知道在51单片机中有两个定时器,我们就可以用这两个定时器来对主程序的运行进行监控。我们可以对T0设定一定的定时时间,当产生定时中断的时候对一个变量进行赋值,而这个变量在主程序运行的开始已经有了一个初值,在这里我们要设定的定时值要小于主程序的运行时间,这样在主程序的尾部对变量的值进行判断,如果值发生了预期的变化,就说明T0中断正常,如果没有发生变化则使程序复位。对于T1我们用来监控主程序的运行,我们给T1设定一定的定时时间,在主程序中对其进行复位,如果不能在一定的时间里对其进行复位,T1 的定时中断就会使单片机复位。在这里T1的定时时间要设的大于主程序的运行时间,给主程序留有一定的的裕量。而T1的中断正常与否我们再由T0定时中断子程序来监视。这样就够成了一个循环,T0监视T1,T1监视主程序,主程序又来监视T0,从而保证系统的稳定运行。51 系列有专门的看门狗定时器,对系统频率进行分频计数,定时器溢出时,将引起复位.看门狗可设定溢出率,也可单独用来作为定时器使用。凌阳61的看门狗比较单一,一个是时间单一,第二是功能在实际的使用中只需在循环当中加入清狗的指令就OK了。AVR系列中,avr-libc 提供三个API 支持对器件内部Watchdog 的操作,它们分别是:wdt_reset() // Watchdog 复位wdt_enable(timeout) // Watchdog 使能wdt_disable() // Watchdog 禁止C8051Fxxx单片机内部也有一个21位的使用系统时钟的定时器,该定时器检测对其控制寄存器的两次特定写操作的时间间隔。如果这个时间间隔超过了编程的极限值,将产生一个WDT复位。-------------------------------------------------------------------------------- [编辑本段]看门狗使用注意

MAX813L芯片中文资料(看门狗及复位专用芯片) 1 MAX813L芯片及其工作原理 1.1 MAX813L芯片特点 · 加电、掉电以及供电电压下降情况下的复位输出,复位脉冲宽度典型值为200 ms。 · 独立的看门狗输出,如果看门狗输入在1.6 s未被触发,其输出将变为高电平。 · 1.25 V门限值检测器,用于电源故障报警、电池低电压检测或+5 V 以外的电源*。 · 门限电压为4.65V · 低电平有效的手动复位输入。 · 8引脚DIP封装。 1.2 MAX813L的引脚及功能 1.2.1 MAX813L芯片引脚排列见图1—1 1.2.2 引脚功能及工作原理说明

(1)手动复位输入端() 当该端输入低电平保持140 ms以上,MAX813L就输出复位信号.该输入端的最小输入脉宽要求可以有效地消除开关的抖动。与 TTL/CMOS兼容。 (2)工作电源端(VCC):接+5V电源。 (3)电源接地端(GND):接0 V参考电平。 (4)电源故障输入端(PFI) 当该端输入电压低于1.25 V时,5号引脚输出端的信号由高电平变为低电平。 (5)电源故障输出端() 电源正常时,保持高电平,电源电压变低或掉电时,输出由高电平变为低电平。 (6)看门狗信号输入端(WDI) 程序正常运行时,必须在小于1.6 s的时间间隔向该输入端发送一个脉冲信号,以清除芯片部的看门狗定时器。若超过1.6 s该输入端收不到脉冲信号,则部定时器溢出,8号引脚由高电平变为低电平。 (7)复位信号输出端(RST) 上电时,自动产生200 ms的复位脉冲;手动复位端输入低电平时,该端也产生复位信号输出。

STM32窗口看门狗程序 窗口看门狗(WWDG)通常被用来监测由外部干扰或不可预见的逻辑条件造成的应用程序背离正常的运行序列而产生的软件故障。除非递减计数器的值在T6位(WWDG->;CR的第六位)变成0前被刷新,看门狗电路在达到预置的时间周期时,会产生一个MCU复位。在递减计数器达到窗口配置寄存器(WWDG->;CFR)数值之前,如果7位的递减计数器数值(在控制寄存器中)被刷新,那么也将产生一个MCU复位。这表明递减计数器需要在一个有限的时间窗口中被刷新。

图 3.6.1.1中,T[6:0]就是WWDG_CR的低七位,W[6:0]即是WWDG->;CFR的低七位。T[6:0]就是窗口看门狗的计数器,而W[6:0]则是窗口看门狗的上窗口,下窗口值是固定的(0X40)。当窗口看门狗的计数器在上窗口值之外被刷新,或者低于下窗口值都会产生复位。 上窗口值(W[6:0])是由用户自己设定的,根据实际要求来设计窗口值,但是一定要确保窗口值大于0X40,否则窗口就不存在了。 窗口看门狗的超时公式如下: Twwdg=(4096×2^WDGTB×(T[5:0]+1)) /Fpclk1; 其中: Twwdg:WWDG超时时间(单位为ms) Fpclk1:APB1的时钟频率(单位为Khz) WDGTB:WWDG的预分频系数 T[5:0]:窗口看门狗的计数器低6位 窗口看门狗寄存器介绍:

如何使用窗口看门狗: 1)使能WWDG时钟 2)设置WWDG_CFR和WWDG_CR两个寄存器 在时钟使能完后,我们设置WWDG的CFR和CR两个寄存器,对WWDG进行配置。包括使能窗口看门狗、开启中断、设置计数器的初始值、设置窗口值并设置分频数WDGTB 3)开启WWDG中断并分组 4)编写中断服务函数 软件例程: //---------------------------wdg.c----------------------- #include "wdg.h" #include "led.h" u8 wwdg_cnt=0x7f; //窗口看门狗计数器初值 void wwdg_init(u8 tr,u8 wr,u8 fprer) { RCC->;APB1ENR|=1;CFR|=fprer;CFR|=1;CFR&=0xff80; //窗口值清零 WWDG->;CFR|=wr; //设定窗口值 WWDG->;CR|=(wwdg_cnt|1;CR|=(cnt&0x7f); //喂狗值 } void WWDG_IRQHandler(void)

《看门狗》第四章:目标四:第福特的处境流程攻略 《看门狗》第四章目标四怎么过?今天小编给大家带来《看门狗》第四章:目标四:第福特的处境流程攻略,希望对大家有所帮助! 第四章:目标四:第福特的处境 1.先到剧场的右侧利用监控器骇入,打开左侧的铁门;铁门在有门卫的门旁边,被墙挡住视线的。 2.剧场里扫描会找到三个被第福特洗掉了信息的人(显示大师第福特之类的),全部找到后利用监控器侵入第福特的机器。 3.通过障碍物的攀爬和楼梯到达顶楼,全歼第福特的收尾人。 4.从大楼一侧的集装箱跳回地面,驱车追赶第福特。接下来的追逐战,玩家只能依靠自己的技术和耐心,别无他法。当玩家与第福特距离在80M以内的时候,玩家会从第福特身上下载数据,需要下载到100%才可完成任务。如果玩家能够撞到第福特把他卡住就可以获得大量数据,但是不可以杀掉第福特。 玩家需要注意第福特的行车轨迹,他一般都是有路口就右转的,有右撇子倾向。 5.至于最后的撂倒第福特,也许是一个隐藏任务,第福特会消失的很快,如果能在第福

特消失之前逮住他或许有额外奖励,但是被他跑了也不回影响剧情。 侠盗猎车5PC版太平洋银行最终任务攻略GTA5太平洋银 行最终任务技巧分析 在碰到大批强打的悍匪之后,基本没有写太平洋银行最终任务的这个窍门的,特此说一下。 做最后的任务骑摩托车硬抗警察真的是一件很蠢的事情,特别是你还背着钱钱,不小心的话小则丢命大则丢钱! 一个很简单的小窍门,买拉古纳斯大道4号公寓,去搜一下这个房产,就在摩托车存放点的隔壁,只要靠墙就能爬上花坛翻过去,很方便。做任务前记得把你保命的骷髅马或者叛乱分子扔这个车库里,银行脱出后跑到摩托车点,注意要上一下摩托车! 然后走到紧邻房产的墙角爬上花坛穿越过去,房主进房子后其余队员在门口等邀请,进入后一起去车库,开启你心爱的防弹骷髅马,上路不要走山路走海边的公路,走海边的公路!(应该都是知道的gps的首选路线都是拦截重重这个道理的吧?!)唱着歌听着子弹打在车上啪啪啪的声音就把钱赚回家了。 另外注意,到了上船点一定要全队速度快!一个人拖拉就能害死一组人!必要时开车冲进水抢时间吧,反正有保险的说!

S3C2410接口之看门狗控制器原理与编程 1.看门狗:是一种电路,具有监视并恢复程序正常运行的功能,从而达到增强系统的稳定性。它本质上是一种定时器电路 2.稳定性和定时器之间有什么样的关系呢? 3.看门狗增强系统稳定性的基本原理:设一系统程序完整运行一周期的时间是Tp,看狗的定时周期为Ti,要求Ti>Tp。在程序运行一周期后,修改定时器的计数值,只要程序正常运行,定时器就不会溢出。若由于干扰等原因使系统不能在Tp 时刻修改定时器的计数值,定时器将在Ti 时刻溢出,引发系统复位,使系统得以重新运行,从而起到监控作用。 s3c2410的看门狗控制器 S3C2410 的看门狗定时器有两个功能: (1)定时器功能:可以作为常规定时器使用,它是一个十六位的定时器,并且可以产生中断,中断名为INT_WDT,中断号是0x09。 (2)复位功能:作为看门狗定时器使用,当时钟计数减为0(超时)时,它将产生一个128个时钟周期的复位信号。 S3C2410 ARM9的看门狗主要由五部分构成:时钟、看门狗计时器、看门狗数据寄存器、复位信号发生器、控制逻辑等。 S3C2410 ARM9的看门狗工作原理: PCLK 经过预分频、再分频,使得到达看门狗的频率能够没有那么高,这样看门狗才处理得了。 ?S3C2410 看门狗定时时间 预分频器为8位,其值为:0---255 再分频器可选择值为:16、32、64、128 输入到计数器的时钟周期为: T_wtd=1/[PCLK/(Prescaler+1)/Division_factor] 看门狗的定时周期为: T=WTDAT(看门狗的计数器的初值)×T_wtd

【经验分享】KE KEA看门狗不复位的几点说明 最近发现有些网友在使用KE,KEA系列的看门狗时,发现配置后,看门狗不能正常复位,或者是设置的复位时间不对等问题。而且这些网友基本上使用官方例程添加看门狗代码,或者是自己使用CW新建一个工程遇到这样的问题。所以,为了方便后来者,在这里总结下大家遇到问题的原因以及相关的解决方法。 下面来具体讲解遇到问题的原因以及解决方法: 1,主程序配置看门狗不复位 谈到这点,首先需要认真的阅读下KE,KEA系列的相关用户手册的WDOG章节以及第三章中关于WDOG的讲解,在关于WDOG的寄存器中,有些是复位后只写一次的,写第二次无效,比如WDOG_CS1,WDOG_CS2中的window 使能,分频使能,时钟源选择等。这里,需要注意,WDOG_CS1[EN]是看门狗的使能位,默认是使能的,上电后一旦禁止,后续第二次开启是无效的。 而我们官方例程中,为了防止看门狗上电复位,在代码启动时,就会做一个看门狗关闭的动作,所以后续如果需要使用看门狗,就要先把启动代码中的看门狗禁止代码屏蔽,从而使能看门狗。 很多网友在主程序中配置相应的看门狗使能代码,发现程序不能实现看门狗复位的原因正是因为没有屏蔽掉启动代码中的看门狗禁止程序。下面以 KEXX_DRIVERS_V1.2.1_DEVD 为例,讲解下在IAR, KEIL, CW中的启动代码看门狗屏蔽情况。 (1)IAR启动代码

从上图中可以看到,IAR启动先进入start函数,进入cpu文件夹中start.c文件,发现,start函数的第一句就是:WDOG_DisableWDOGEnableUpdate(); 即关闭看门狗。如果实际使用想实现具体的看门狗配置,可以直接在这个地方配置看门狗并及时喂狗,防止在程序没有进入到main程序就mcu看门狗复位。 这里给出一个看门狗配置的例子: 从上图中,可以看到KEIL的启动代码,进入main之前首先进入到SystemInit函数中,在CPU文件夹的Start.c中可以找到SystemInit函数,这个函数里面统一是关于关闭看门狗的代码,如果是KEIL工程,那么就需要在这个地方屏蔽掉关闭看门狗的代码,可以加上自己的看门狗初始化代码,例子见(1)。 (3)CW启动代码

在该电路中SPC3的复位电路与89C52的复位电路应相互独立,这样在单片机复位时SPC3仍能够正常通信。由MAX705组成的看门狗复位电路可以保证单片机系统在程序“跑飞”时能够可靠复位,MAX705的复位脉冲输出有正脉冲和负脉冲两种方式,当复位脉冲为负脉冲时,需要外接反相器后再连接到单片机的复位端,具体连接如图4。 图4 看门狗电路 在正常情况下,P1.x引脚不超过1.6s就向WDI端发出“喂狗”信号,程序陷入死循环后,“喂狗”信号无法发出,当死循环运行时间超过1.6s时,MAX705的看门狗输出将变低并触发,复位信号从端输出。 1看门狗 看门狗实际上是一个计数器,它需要在一定的看门狗延时周期内被清零,如果没有清零动作,看门狗电路将产生一个复位信号以使系统重新启动或建立一个非屏蔽中断(NMI)并执行故障恢复子程序。大多数看门狗电路是沿触发,这样,无论是上升沿还是下降沿触发看门狗的输入端(WDI)通常都能够清计数器。WDI引脚一般连接在处理器的一个I/0口,这条口线可由软件触发。图1所示是微处理器通过在WDl脚发送脉冲清除看门狗定时器以防止复位的连接方式,实际上,清看门狗计数器的命令必须在主程序内。如果看门狗没有被清零,复位后软件将从地址为0000(启动程序)的子程序处开始运行。计算主程序的运行时间往往很困难,因为在此期间可能需要多次调用子程序,这与系统输入有关。因此,设计人员常常选择看门狗延时周期远远高于测试到的或计算出的循环时间。图2所示是正常工作情况下(看门狗在延时周期内被请零)的看门狗信号和复位信号。图3所示为看门狗计数器溢出时引发一次复位的时序示意图。工业标准的看门狗电路延时周期一般在l00ms~2s范围内,当然,也有些可调节或定制的看门狗电路能够覆盖更宽的延时范围(30ms至几分钟)。如果主程序的执行时间对于看门狗电路而言过长,设计人员可以在主程序的不同部位多次执行看门狗触发命令,也可以选用看门狗延时周期更长的器件。

705系列复位电路 #概述 GC705/706/707/708/813L是一组CMOS微处理器监控电路,可用来监控微处理器系统供电异常、电池故障和工作状态。和采用分立元件及多片IC组合成电路相比,明显减小了系统电路的复杂性和元器件的数量,并提高了系统的可靠性和精度。 GC705/706/813L具备以下四项基本功能: 1)电源开机,关机及电源供电不足时给出复位输出。 2)内含独立的看门狗电路输出。如看门狗电路输入在1.6秒内未得到翻转信号,看门狗电路输出端将变成低电平。 3)内含门限1.25V的检测器,用于掉电报警,电池欠电监测和监测加错电源的状况(以+5V为准)。 4)手动复位时,给出确定脉宽的负向复位脉冲 GC707/708和GC705/706基本功能一致,区别只在于GC705/706芯片中的第8脚正脉冲的复位(RESET)输出取消了,换成了看门狗定时器,原第6脚空脚被用做看门狗电路的输入端。GC813L则除了第7脚输出正脉冲的RESET外,其它功能和GC705/706完全一样。这几种电路的管脚功能定义和差异详见管脚定义图和管脚说明附表。 #应用范围 计算机,微处理器和微控制器系统;嵌入式控制器系统;智能仪器仪表;通信系统;工业自动化系统;电池供电手持设备等等。

# 电气参数 除非特殊说明,Vcc = 4.75V~ 5.5V (GC705/GC707/GC813), Vcc =4.5V~5.5V (GC706/GC708),T A = T MIN to T MAX 参数 符号 测试条件 最小值典型值 最大值 单位 GC705、706、707、708 1.0 5.5 电源电压范围 Vcc GC813 1.1 5.5 V GC705、706、813 150 350 电源电流 Icc GC707、708 50 350 uA GC705、707、813 4.50 4.65 4.75 GC706、708 4.25 4.40 4.50 复位门限 V RT GC706T 3.00 3.08 3.15 V 复位门限迴差 40 mV 复位脉冲宽度 t RS 140 200 280 ms I SOURSE =800uA VCC-1.5 I SINK = 3.2mA 0.4 GC705~708,VCC=1V ,I SINK = 50uA 0.3 GC707\708,I SOURCE =800uA VCC-1.5 GC707\708,I SINK = 1.2mA 0.4 复位输出电压 GC813,I SOURCE =4uA,V CC = 1.1V 0.8 V 看门狗计时长度 t WD GC705\706\813 1.00 1.60 2.25 秒 WDI 脉冲宽度 t WP VIL =0.4V ,VIH =(VCC)(0.8) 50 ns 下限 0.8 WDI 输入阈值 上限 GC705\706\813 V CC =5V 3.5 V GC705\706\813,WDI =VCC 50 150 WDI 输入电流 GC705\706\813,WDI =0V -150 -50 uA GC705\706\813,I SOURCE =800uA VCC-1.5 WDI 输出电压 GC705\706\813,I SINK =1.2mA 0.4 V MR 上拉电流 MR =0V 100 250 600 uA MR 脉冲宽度 t MR 150 ns 下限 0.8 MR 输入阈值 上限 2.0 V MR 到RESET 的 延迟 t MD 250 ns PFI 输入阈值 VCC =5V V PFI 输入电流 -25 25 nA I SOURCE =800uA VCC-1.5 PFO 输出电压 I SINK =3.2mA 0.4 V

C51单片机看门狗电路及 程序设计案 院系:信息工程学院 年级:2010级 电子一班禹豪 电子一班训虎 电子二班邓启新 一、引言 在由单片机构成的微型计算机系统中,程序的正常运行常常会因为来自外界的电磁场干扰等原因而被打断,从而造成程序的跑飞,而陷入死循环。由此导致单片机控制的系统无法继续工作,造成整个系统的陷入停滞状态,发生不可预料的后果,所以出于对单片机运行状态进行实时监测的考虑,便产生了一种专门用于监测单片机程序运行状态的芯片或程序,俗称"看门狗"(watchdog) (1)看门狗电路基本原理 看门狗电路的应用,使单片机可以在无人状态下实现连续工作,其工作原理是:看门狗芯片和单片机的一个I/O引脚相连**,该I/O引脚通过程序控制它定时地往看门狗的这个引脚上送入高电平(或低电平),这一程序语句是分散地放在单片机其他控制语句中间的,一旦单片机由于干扰造成程序跑飞后而陷入某一程序段进入死循环状态时,写看门狗引脚的程序便不能被执行,这个时候,看门狗电路就会由于得不到单片机送来的信号,便在它和单片机复位引脚相连的引脚上送出一个复位信号,使单片机发生复位,即程序从程序存储器的起始位置开始执行,这样便实现了单片机的自动复位。 *此处设计原理实际上为下文中硬件看门狗设计思路。

(2)看门狗电路一般设计式 “看门狗”电路一般分为硬件看门狗与软件看门狗两种设计式。 硬件看门狗是利用了一个定时器,来监控主程序的运行,也就是说在主程序的运行过程中,我们要在定时时间到之前对定时器进行复位。如果出现死循环,或者说PC指针不能回来,那么定时时间到后就会使单片机复位。常用的WDT芯片如MAX813,5045,IMP 813等,价格4~10元不等. 软件看门狗技术的原理和硬件看门狗类似,只不过是用软件的法实现(即利用单片机部定时器资源,通过编程模拟硬件看门狗工作式),以51系列为例:因在51单片机中有两个定时器,在利用部定时器资源来对主程序的运行进行监控时。可以对T1(或T0)设定一定的定时时间(设定的定时值要小于主程序的运行时间),当产生定时中断的时候对一个变量进行赋值(此变量在主程序运行的开始已有一个初值)。当主程序运行至最后时对此变量的值进行判断,如果值发生了预期的变化,就说明T0中断正常,如果没有发生变化则使程序复位。 考虑到设计要求,本设计采用软件看门狗设计思路。 二、看门狗电路整体设计思路 根据设计要求,本设计利用C51单片机部自带的定时器1进行编程,并配合少量电路实现“看门狗“电路功能。整个设计分为软件部分与硬件部分,如下: (1)软件部分设计原理: 软件设计分为三部分:“看门狗“定时器设置程序、溢出中断服务程序和喂狗代码。 1.1设计思路: 1)在主程序开头,“看门狗“定时器设置程序设置定时器1计时50ms。 2)当定时达50ms时,定时器1产生溢出中断,溢出中断服务程序开始工作,将看门狗标志num加1。当num的值等于100时,说明看门狗定时器已经计时5s,此时,单片机I/O端口P1.0输出高电平,对程序进行复位。 3)在此过程中,喂狗代码将被穿插于程序中循环体末尾。当循环体结束时,喂狗代码执行,关闭定时器1、清空num并重新初始化定时器设置。若循环体进入死循环,喂狗代码无法执行,num将一直累加至100,此时程序复位。 注:喂狗代码放置位置可根据num预计数值进行调整:当num门限值较小,即看门狗计数时间较短时,喂狗代码可放于程序中各循环体之后或均匀分布于整个主程序中。当num门限值较大,即看门狗计数时间较长时,喂狗代码可放于程序主循环体末尾。但是需注意看门狗计数时间必须长于正常工作时间,以免非正常复位。 1.2软件设计流程图:

附录一、 驱动程序:at91sam9g20核心板的看门狗驱动 看门狗的驱动一般来说比较简单,只要做寄存器的设置实现开启、关闭、喂狗功能。本项目中我们使用的是at91sam920处理器,带有看门狗定时器。这个看门狗的驱动却比较复杂,应用层想用它的话,将涉及到boot引导设置,uboot配置及驱动,改写驱动程序。下面将逐步说明。 1、boot引导(bootstrap-v1.15) 由于该看门狗的MR寄存器只能写一次(Only a processor reset resets it.),而默认情况下看门狗在boot引导程序中被关闭了,所以在boot引导程序中我们要开启看门狗。在board/at91sam9g20ek/at91sam9g20ek.c文件的硬件初始化函数hw_init中注释掉下面的配置即可开启看门狗: /* writel(AT91C_WDTC_WDDIS, AT91C_BASE_WDTC + WDTC_WDMR); */ 为了功能设置:我们配置如下: writel(AT91C_WDTC_WDV | AT91C_WDTC_WDD | AT91C_WDTC_WDRSTEN | AT91C_WDTC_WDFIEN, AT91C_BASE_WDTC + WDTC_WDMR); 2、uboot配置及驱动(uboot-v1.3.4): 默认情况下,看门狗在uboot中没有配置,需要手动添加配置,在文件include/configs/at91sam9g20ek.h中添加如下配置 #define CONFIG_HW_WA TCHDOG 1 #define CONFIG_AT91SAM9_WA TCHDOG 1 此时编译uboot,会提示你找不到hw_watchdog_reset复位函数,这是因为虽然我们配置看门狗,但看门狗的uboot驱动并不存在,下面就来添加uboot下的看门狗驱动。 1)添加include/asm-arm/arch-at91sam9/at91_wdt.h,内容如下 /* * [origin: Linux kernel arch/arm/mach-at91/include/mach/at91_wdt.h] * * Copyright (C) 2008 Jean-Christophe PLAGNIOL-VILLARD