基于SPI串行总线协议的大容量flash存储器

在MEMS姿态测量系统中的具体应用

摘要:基于MEMS传感器的姿态测量系统以其实时性好、使用方便、成本低廉、体积小等优点而得到了广泛的应用,姿态测量信息除实时处理外,许多场合需要将大量信息保存以备专门的计算仿真。本文主要介绍了大容量存储器AT45DB321D在姿态测量系统中的应用,描述了其主要功能、工作原理、操作指令、读写时序及在姿态测量系统中的硬件连接,重点介绍了软件操作中的模拟SPI和操作指令传输的具体实现两个重难点问题。

关键词:AT45DB321D;姿态测量系统;SPI;操作指令

Abstract: The MEMS attitude measurement system Based on MEMS sensor has been widely used with its properties of real-time, easy to use, low cost, small volume etc. Mostly, the attitude information is not only used for the real-time processing, but also stored for special simulation and calculation. This paper mainly introduces application of AT45DB321 in the attitude system, and describes the main functions, working theory, operation instruction ,read-write schedule and the hardware design in the attitude measurement system. This paper particularly presents the realization of the analog SPI and operation instruction transportation in software program.

Key words: AT45DB321;attitude measurement system; SPI; operation instruction 利用MEMS加速度计、陀螺仪、磁强计等惯性器件研制的微型姿态测量系统,具有体积小、价格低、功耗低、抗冲击力强等优点,广泛应用于现代武器制导系统、人体姿态测量系统、无人机飞行控制等方面。姿态测量系统信息储存的需要使得大容量的存储设备变得必要。AT45DB321D是ATMEL公司生产的串行接口的可编程闪速存储器,它采用SPI串行模式可与任何单片机或微机进行通信,几乎无需外接元器件。该芯片具备操作方便、数据存储量大、安全性好、封装尺寸小、集成度高、功耗低等优点。

1.芯片介绍

1.1 AT45DB321D特点:

(1)单电源2.7~3.6V供电,串行接口结构,最大时钟频率66MHZ,兼容SPI(串行外围接口)模式0和模式3。

(2)页编程操作:主存8192 页(512/528 字节/页),共计32M存储容量,可进行页擦除、块擦除、扇区擦除、片擦除。

(3)两个静态数据缓存器(512/528字节)。允许编程时接收数据,支持整片芯片连续读。(4)具有硬件数据保护端和软件数据保护模式,对需要重点保存的代码和数据有锁存区。(5)低功耗:读状态典型电流值7 毫安,待机状态典型电流值25 微安,休眠状态典型电流值5微安。

(6)128字节的安全保护寄存器,支持至少100000次的擦写,数据可保持20年。

1.2 AT45DB321D 引脚配置及内部结构。

SI 15

6

7

8

432VCC

GND SO SCK

目前AT 45DB321D 主要有四种封装形式:MLF 、SOIC 、CARD 、TSOP 。不同的封装形式取决于应用场合的不同,器件的基本功能是一致的。我们所用的存储芯片封装形式为SOIC (如图1所示),各管脚的功能配置如表1所示。

表1 管脚功能配置表

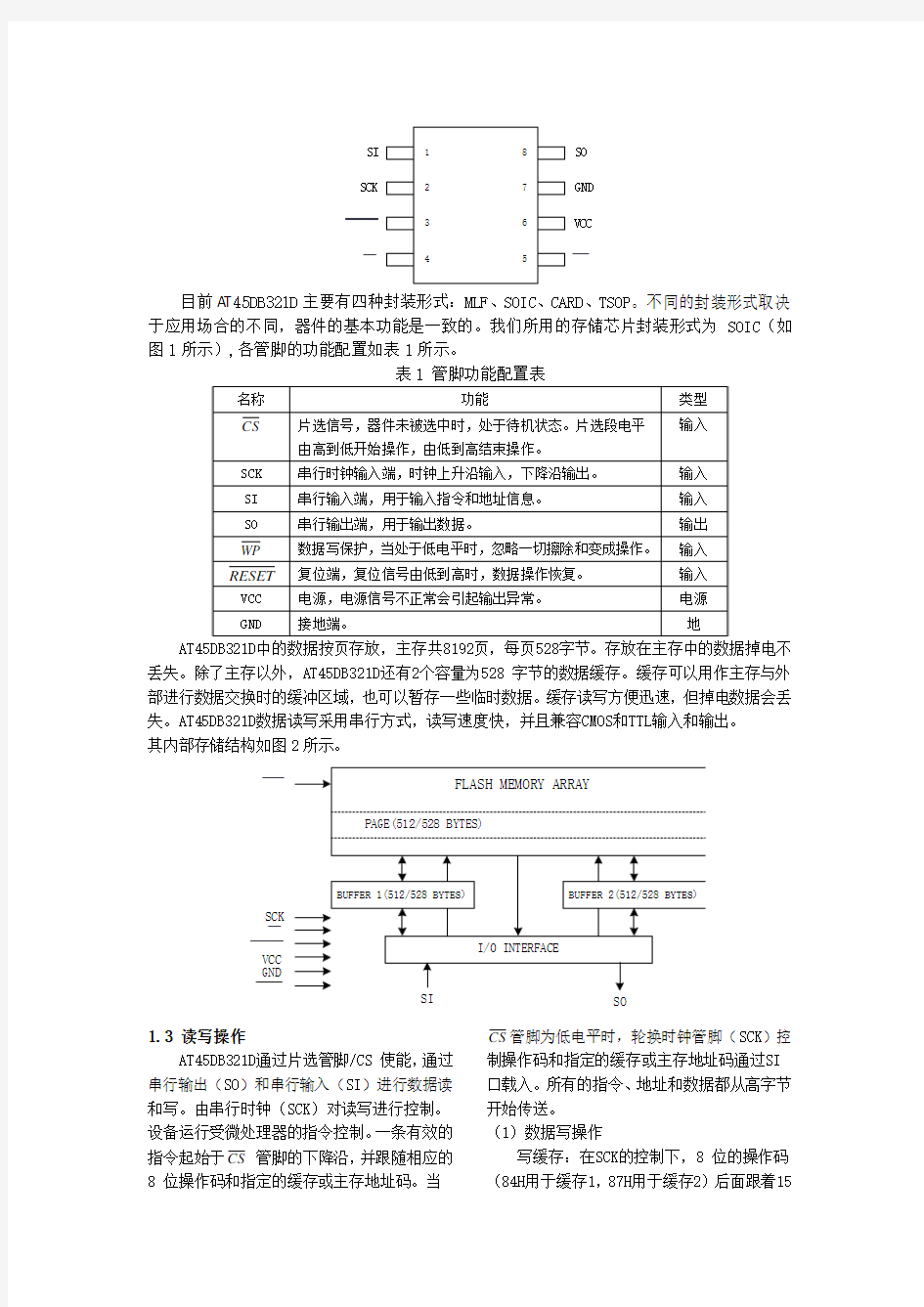

AT45DB321D 中的数据按页存放,主存共8192页,每页528字节。存放在主存中的数据掉电不丢失。除了主存以外,AT45DB321D 还有2个容量为528 字节的数据缓存。缓存可以用作主存与外部进行数据交换时的缓冲区域,也可以暂存一些临时数据。缓存读写方便迅速,但掉电数据会丢失。AT45DB321D 数据读写采用串行方式,读写速度快,并且兼容CMOS 和TTL 输入和输出。 其内部存储结构如图2所示。

VCC GND

SO

SCK

1.3 读写操作

AT45DB321D 通过片选管脚/CS 使能,通过串行输出(SO )和串行输入(SI )进行数据读和写。由串行时钟(SCK )对读写进行控制。设备运行受微处理器的指令控制。一条有效的指令起始于CS 管脚的下降沿,并跟随相应的8 位操作码和指定的缓存或主存地址码。当

CS 管脚为低电平时,轮换时钟管脚(SCK )控

制操作码和指定的缓存或主存地址码通过SI 口载入。所有的指令、地址和数据都从高字节开始传送。 (1)数据写操作

写缓存:在SCK 的控制下,8 位的操作码(84H 用于缓存1,87H 用于缓存2)后面跟着15

位任意码和9位地址码(BFA8-BFA0),它们都由SI载入,其中9位地址码指定了缓存中被写

的首字节,数据紧随着地址码输入。上一

个由低到高的电平跳变将结束写缓存操作。

带有内置擦除的缓存至主存页的传送:8 位的操作码(83H用于缓存1,86H用于缓存2)后跟有2位保留位,13 位指定要写入的主存页的地址码(A21-A9)和9位任意码,在轮换时

钟SCK 的控制下从SI 载入。当CS上检测到一个由低到高的电平跳变时,器件将首先擦除被选中的主存页,然后将储存在缓存中的数据写入该页。擦除和写入的过程都是自动进行的。在这个时间里,状态寄存器将指示状态忙。(2)数据读操作

读缓存:通过不同的操作码可选择读取2 个缓存中的其中一个(操作码54H用作读缓存1,而操作码56H用作读缓存2)。为了实现读缓存的操作,在8位操作码后必须跟有14位任意码、10位地址码和8位任意码。其中9位地址码(BFA8-BFA0)被用作指定要读取的首字节。

在轮换时钟SCK 的控制下,从SI 载入操作码、地址码、任意码。当载入结束后,在SCK 轮换时钟的控制下,缓存中的数据就可以从SO读出。当读到缓存的末尾时,设备将继续从缓存的开始重读。在这整个过程中CS必须保持低电平。读缓存结束后,CS上一个从低到高的电平跳

变将终止读操作。

主存页到缓存的传送:一页数据可以从主存传至缓存1或缓存2。8位操作码(53H用于缓存1,55H用于缓存2)后跟有2位保留位,13

位用于指定目的页的地址位(A21-A9)和9位

任意码。在轮换时钟SCK的控制下从SI 载入。在这一过程中CS管脚必须保持低电位。当载入结束后,在CS上检测到一个由低到高的电

平跳变后,主存页中的数据开始传送至缓存。在数据传送的过程中,状态寄存器将指示状态忙。

2.在姿态测量系统中的应用

2.1 系统框图设计

MEMS产品因其体积小、价格低、功耗低,被称为是传统的惯性测量组合的一次重大的革命,越来越多地应用于姿态测量应用中。随着MEMS技术的迅速发展MEMS姿态测量系统各方面性能如精度、鲁棒性、动态响应等都得到了巨大的提高[2],在各行各业中都得到了应用。在本系统中,加速度计、磁强计、陀螺仪的信号被采集到微处理器C8051F411中,通过数传模块将数据送到上位机进行数据融合姿态解算,同时将数据存储到AT45DB321D中,一方面进行数据对比验证,另一方面完成数据保存功能可以应用于下一步的仿真计算。存储器在整个系统中的连接如示意框图2中微存储器所示。

输入信息

数据处理数据应用

2.2 C8051F411与AT45DB321的接口电路硬件设计

AT45DB321D存储器数据存储量大、外部电路简单,几乎可以与任何类型的单片机接口, 无论单片机是否有SPI接口。如果单片机有SPI接口,存储器读/写程序则相对简单。如没有SPI接口,则可以用软件仿真SPI接口与存储器通信。在本系统中,系统数传模块需要SPI接口,所以本存储模块使用软件仿真的SPI接口。图4为AT45DB321D 芯片在姿态测量系统中应用部分的电路图,SO、SI、SCK、CS、WP、RESET分别与微处理器的通用I/O 相连, SPI协议软件模拟的实现在3.2中详细叙述。

3.软件设计

3.1软件读写设计

AT45DB321D 与C8051F411之间的数据传输包括读和写两种操作,对AT45DB161D 的写有两种方式。一种是直接写指令,通过C8051F411的模拟SPI移位寄存器直接往AT45DB321D 的指定页的指定地址写数据,这个指令必须提供指定页的指定地址。所以在这种方式下,要想存储一段连续的数据,必须用一个循环来实现,执行时间较长。另一种方式是通过缓存间接写FLASH。先把

C8051F411中的数据依次通过移位寄存器存到缓存1,在写完缓存后一次写到FLASH 中去。读操作也分为两种方式,直接从FLASH中给定的起始页连续读到C8051F411中,也可以通过页地址单页间接读取。本系统中所用的写操作和读操作均采用间接方式。程序设计流程图分别如图6 、图7 所示。

3.2模拟SPI总线设计

典型的SP I接口共有4种操作模式,分别为0、1、2和3。SPI操作模式决定了设备接收和发送数据时的时钟相位和极性,即决定了时钟信号的上升沿和下降沿与数据流动方向之间的关系。DataFlash系列存储器仅支持使用得最为广泛的SPI模式0和3。在这两种模式下, SCK 信号的上升沿触发数据输入,下降沿触发数据输出,如图3所示。二者的区别仅是SCK信号的起始电平不同。在本系统中采用SPI模式0来实现C8051F411与Flash之间的通信。因本系统中SPI协议已经使用,故采用软件模拟SPI协议来实现数据的存储。如下的C程序就是模拟SPI

协议的程序实现,用数据移位操作实现移位寄存器,同时设定时钟上升沿输入数据,下降沿

输出数据。其中Out_Byte函数实现一个字节的移位操作,Out_Word函数实现两个字节的移位操作。

方式0

方式1

方式2

方式3

(1)void Out_Byte(unsigned char Byte)

{unsigned char TempCyc,Out_SI;

for(TempCyc=0;TempCyc<8;TempCyc++)

{ SCK=0;delay(20);Out_SI = Byte & 0x80;

if(Out_SI==0){ MOSI=0; }

else {MOSI=1;}

Byte = Byte<<1; delay(20); SCK=1;delay(20);}}

(2)void Out_Word(unsigned int Word)

{unsigned char TempCyc;unsigned int Out_SI;

for(TempCyc=0;TempCyc<16;TempCyc++)

{SCK=0; delay(20); Out_SI = Word & 0x8000;

if(Out_SI==0){ MOSI=0;}

else{MOSI=1;}

Word = Word<<1; delay(20); SCK=1; delay(20);}}

3.3程序指令设计

CMD8 bits8 bits8 bits……

SI(INPUT)

MSB XX XXXXX XXXXXXXXX XXXX XXXX

Don’t

Care Bits(A21-A9)

Byte/Buffer

Address(A8-A0)

LSB

AT45DB321D的数据命令格式的实现是首先在SPI总线上传输8位操作码后,后边是包括13位页地址和9位缓存器地址或指定页起始地址。因我们给出的页面地址和起始地址都是2字节的int数据类型,存储器并不识别。所以我们需要进行一个移位操作,使得我们传输的页面地址和起始地址是存储器识别的地址码。本文采用将13位有效位的页面地址左移1位实现存储器识别的页面地址,将9位有效位的起始地址右移8位余下的最高字节加到左移后的页面地址后面,同时低字节的8位地址保持,将经过移位操作的总过22位地址传输给存储器,进行相关指令操作。经仿真验证本方法切实可行。具体的C程序实现如下所示。

Out_Address_1=(Page_Address<<1)|(Start_Address>>8);

Out_Address_0=(Start_Address&0x00ff);

Out_Word(Out_Address_1);

Out_Byte(Out_Address_0);

4.结束语

本文仅仅介绍了大容量FLASH 存储器AT45DB321在姿态测量系统中的应用部分,包括硬件接口设计和软件编程部分,重点对模拟SPI协议和数据操作指令进行了介绍。AT45DB321D

存取速度快、可靠性高, 简单的串行接口方便了硬件电路设计, 增加了系统的可靠性,使用时需注意: 1、芯片存取速度可达66MHz, 需采用运行速度较快的单片机与之接口, 否则不能发挥它的速度优势; 2、AT系列Flash芯片的兼容性好,产品设计尽量采用卡片式封装, 可方便实现容量升级换代及维护。相信该系列芯片在计算机外部设备、通讯设备、自动化控制和各种消费品等产品中会有越来越广泛的应用。

参考文献

(1)朱荣,周兆英.基于MEMS的姿态测量系统.测控技术:2002年第21卷第10期.

(2)陈新隽,刘晓平.多MEMS传感器的嵌入式姿态测量系统设计.2011年机械电子学学术会议论文集.2011.9.

(3)C8051F411 datasheet,Silicon labs,2007.

(4)AT45DB321D Dataflash datasheet, Atmel Corporation,2007.

(5)胡智华.大容量SPIDataFlash与DSP的接口设计与应用.空间电子技术.2006,4.

(6)黄秋, 丁卫撑. SPI 接口的FLASH ROM与C8051F340 的接口设计. 《自动化技术与应用》2010 年第29 卷第4 期.

(7)扶小飞,郑善贤. 一种Flash 文件系统的设计和实现. 《微计算机信息》(嵌入式与SOC)2010 年第26 卷第2-2 期.

实验一存储器实验 1.FPGA中LPM_ROM定制与读出实验 一.实验目的 1、掌握FPGA中lpm_ROM的设置,作为只读存储器ROM的工作特性与配置方法。 2、用文本编辑器编辑mif文件配置ROM,学习将程序代码以mif格式文件加载于 lpm_ROM中; 3、在初始化存储器编辑窗口编辑mif文件配置ROM; 4、验证FPGA中mega_lpm_ROM的功能。 二.实验原理 ALTERA的FPGA中有许多可调用的LPM (Library Parameterized Modules)参数化的模块库,可构成如lpm_rom、lpm_ram_io、lpm_fifo、lpm_ram_dq的存储器结构。CPU 中的重要部件,如RAM、ROM可直接调用她们构成,因此在FPGA中利用嵌入式阵列块EAB 可以构成各种结构的存储器,lpm_ROM就是其中的一种。lpm_ROM有5组信号:地址信号address[ ]、数据信号q[ ]、时钟信号inclock、outclock、允许信号memenable,其参数都就是可以设定的。由于ROM就是只读存储器,所以它的数据口就是单向的输出端口,ROM中的数据就是在对FPGA现场配置时,通过配置文件一起写入存储单元的。图3-1-1中的lpm_ROM有3组信号:inclk——输入时钟脉冲;q[23、、0]——lpm_ROM的24位数据输出端;a[5、、0]——lpm_ROM的6位读出地址。 实验中主要应掌握以下三方面的内容: ⑴ lpm_ROM的参数设置; ⑵ lpm_ROM中数据的写入,即LPM_FILE初始化文件的编写; ⑶lpm_ROM的实际应用,在GW48_CP+实验台上的调试方法。 三.实验步骤 (1)用图形编辑,进入mega_lpm元件库,调用lpm_rom元件,设置地址总线宽度address[] 与数据总线宽度q[],分别为6位与24位,并添加输入输出引脚,如图3-1-1设置与连接。 (2)设置图3-1-1为工程。 (3)在设置lpm_rom数据参数选择项lpm_file的对应窗口中(图3-1-2),用键盘输入 lpm_ROM配置文件的路径(rom_a、mif),然后设置在系统ROM/RAM读写允许,以便能

NOR Flash 存储器测试方法介绍 一、NOR FLASH简介 NOR FLASH 是很常见的一种存储芯片,数据掉电不会丢失。NOR FLASH支持Execute ON Chip,即程序可以直接在FLASH片内执行。这点和NAND FLASH不一样。因此,在嵌入是系统中,NOR FLASH很适合作为启动程序的存储介质。 NOR FLASH的读取和RAM很类似,但不可以直接进行写操作。对NOR FLASH的写操作需要遵循特定的命令序列,最终由芯片内部的控制单元完成写操作。从支持的最小访问单元来看,NOR FLASH一般分为8 位的和16位的(当然,也有很多NOR FLASH芯片同时支持8位模式和是16 位模式,具体的工作模式通过特定的管脚进行选择) 。对8位的NOR FLASH芯片,或是工作在8-BIT模式的芯片来说,一个地址对应一个BYTE(8-BIT)的数据。 在对FLASH进行写操作的时候,每个BIT可以通过编程由1变为0,但不可以有0修改为1。为了保证写操作的正确性,在执行写操作前,都要执行擦除操作。擦除操作会把FLASH 的一个SECTOR,一个BANK或是整片FLASH 的值全修改为0xFF。这样,写操作就可以正确完成了。 1. 8-BIT的NOR FLASH 例如一块8-BIT的NOR FLASH,假设容量为4个BYTE。那芯片应该有8个数据信号D7-D0 和2个地址信号,A1-A0。地址0x0对应第0个BYTE,地址0x1对应于第1BYTE,地址0x2对应于第2个BYTE,而地址0x3则对应于第3 个BYTE 2. 16-BIT的NOR FLASH 对16位的NOR FLASH芯片,或是工作在16-BIT模式的芯片来说,一个地址对应于一个HALF-WORD(16-BIT)的数据。例如,一块16-BIT的NOR FLASH,假设其容量为4个BYTE。那芯片应该有16 个数据信号线D15-D0 和1个地址信号A0。地址0x0对应于芯片内部的第0个HALF-WORD,地址0x1对应于芯片内部的第1个HALF-WORD。 3. NOR Flash结构 FLASH一般都分为很多个SECTOR,每个SECTOR包括一定数量的存储单元。对有些大容量的FLASH,还分为不同的BANK,每个BANK包括一定数目的SECTOR。FLASH的擦除操作一般都是以SECTOR,BANK或是整片FLASH为单位的。

基于March C-算法的单片机存储器测试 作者:于文考高成张栋 来源:《现代电子技术》2010年第06期 摘要:为了保证单片机系统的可靠性,对单片机内嵌存储器的测试显得尤为重要。根据MCS-51系列单片机系统内嵌存储器的结构特点和故障模型,研究了测试算法的选择、数据背景的产生等问题,首次提出将March C-算法用于单片机内嵌存储器的用户级测试程序编写。该测试程序对SAF,TF,AF,CF的故障覆盖率可达到100%,并且能够检测部分NPSF故障,具有较高的故障覆盖率,适合于对用户级MCS-51系列单片机存储器的测试。 关键词:单片机;March C-算法;存储器测试;故障覆盖率 中图分类号:TP333文献标识码:B 文章编号:1004-373X(2010)06-019-03 Test of Single Chip Microcomputer′s Memory Based on March C- Algorithm YU Wenkao,GAO Cheng,ZHANG Dong (Beihang University,Beijing,100191,China) Abstract:In order to ensure thereliability of single chip microcomputer system,test of the single chip microcomputer embedded memory is particularly important.In accordance with characteristics and fault model of MCS-51 embedded memory,selection of the test algorithm and the data background are researched,and the test program which based on March C- algorithm for MCS-51 single chip microcomputer embedded memory for the first time in user-level is presented.The test program can reach all of the SAF,TF,AF,CF failure and some of NPSF failure,has a high fault coverage,suitable for test of MCS-51 single chip microcomputer embedded memory in user-level. Keywords:single chip microcomputer;March C- algorithm;memory test;fault coverage 0 引言 存储器是单片机系统中的重要组成部分,其功能的正确性直接影响到单片机的可靠性。因此,为了保证单片机系统的可靠性,对单片机内嵌存储器的功能测试尤为重要。针对单片机内嵌存储器的结构特点,在详细分析嵌入式存储器故障模型的基础上,合理选择测试算法和数据背景,采用面向位与面向字节相结合的March C-算法,实现了基于March C-算法的单片机内嵌存储器测试。 1 存储器的故障模型

第13章Flash存储器 Flash存储器具有电可擦除、无需后备电源来保护数据、可在线编程、存储密度高、低功耗、成本较低等特点,这使得Flash存储器在嵌入式系统中的使用迅速增长。 本章主要以HC08系列中的GP32为例阐述Flash存储器的在线编程方法,也简要阐述了HCS08系列中GB60的在线编程方法。本章首先概述了Flash存储器的基本特点,并介绍其编程模式,随后给出M68HC908GP32的Flash存储器编程的基本操作及汇编语言和C语言的在线编程实例。最后讨论MC9S08GB60的Flash存储器编程方法。 Flash存储器编程方法有写入器模式与在线模式两种,本章讨论的是在线模式。有的芯片内部ROM中,包含了Flash擦除与写入子程序,在本章的进一步讨论中给出了调用方法,使Flash编程相对方便。有的芯片内部ROM中没有固化Flash擦除与写入子程序,只能自己编写Flash擦除与写入子程序。而编写Flash擦除与写入子程序需要较严格的规范,所以这是比较细致的工作,读者应仔细分析本章的例程,并参照例程编程。掌握了GP32芯片的Flash编程方法后,可以把此方法应用于整个系列的Flash编程。Flash在线编程对初学者有一定难度,希望通过实例分析学习。本章给出Flash在线编程的C语言实例,对于训练C语言与汇编联合编程技巧很有帮助。 13.1 Flash存储器概述与编程模式 理想的存储器应该具备存取速度快、不易失、存储密度高(单位体积存储容量大)、价格低等特点,但一般的存储器只具有这些特点中的一个或几个。近几年Flash存储器(有的译为:闪速存储器或快擦型存储器)技术趋于成熟,它结合了OTP存储器的成本优势和EEPROM的可再编程性能,是目前比较理想的存储器。Flash存储器具有电可擦除、无需后备电源来保护数据、可在线编程、存储密度高、低功耗、成本较低等特点。这些特点使得Flash存储器在嵌入式系统中获得广泛使用。从软件角度来看,Flash和EEPROM技术十分相似,主要的差别是Flash存储器一次只能擦除一个扇区,而不是EEPROM存储器的1个字节1个字节地擦除,典型的扇区大小是128B~16KB。尽管如此,因为Flash存储器的总体性价比,它还是比EEPROM更加流行,并且迅速取代了很多ROM器件。 嵌入式系统中使用Flash存储器有两种形式:一种是嵌入式处理器上集成了Flash,另一种是片外扩展Flash。 目前,许多MCU内部都集成了Flash存储器。Freescale公司在Flash存储器技术相当成熟的时候,在HC08系列单片机内集成了Flash存储器。该系列内部的Flash存储器不但可用编程器对其编程,而且可以由内部程序在线写入(编程),给嵌入式系统设计与编程提供了方便。存储器是MCU的重要组成部分,存储器技术的发展对MCU的发展起到了极大的推动作用。对于Freescale公司新推出的HCS08系列MCU采用第三

本技术公开了一种存储器测试方法,包括以下步骤:激活操作系统,令系统进入存储器测试的保护模式;在存储器中创建一地址转换页表;判断待测存储器的物理地址空间是否超过 4GB;若是,激活地址转换页表,将系统给定的32位线性地址转换为与存储器的实际物理地址相对应,并在系统中央处理器的控制下,依照地址转换页表查询和访问存储器的实际物理地址,且执行存储器检测算法进行存储器测试;若不是,则在系统中央处理器的控制下,直接访问与系统的32位线性地址相对应的存储器的实际物理地址,并执行存储器检测算法进行存储器测试。采用本技术可以访问和测试4GB以上存储器地址空间的问题及缺陷,从而在提 高了存储器测试范围的同时节约了测试成本。

技术要求 1、一种存储器测试方法,应用于使用英特尔中央处理器的计算机服务器 系统或个人微电脑系统中的存储器检测过程,其特征在于,该方法包括以下步骤: 激活操作系统,并令系统进入存储器测试的保护模式; 在存储器中创建一地址转换页表结构,用以在后续步骤中将系统给定的 32位线性地址转换成具有4GB以上物理地址空间的存储器的物理地址; 判断所测试的存储器的物理地址空间是否超过4GB; 如超过4GB,则激活所述地址转换页表结构,将系统给定的32位线性地 址转换为与所述存储器的实际物理地址相对应,并在系统中央处理器的控制下,依据该地址转换页表查询和访问所述存储器的实际物理地址,且执行存储器检测算法对该存储器进行测试,并且在完成对所述存储器的实际物理地址的访问及存储器测试后,关闭该地址转换页表结构;以及 如未超过4GB,则不激活所述地址转换页表结构,而在所述系统中央处理 器的控制下,直接访问与系统给定的32位线性地址相对应的所述存储器的实际物理地址,并执行存储器检测算法对该存储器进行测试。 2、根据权利要求1所述的方法,其特征在于,所述地址转换页表结构是 基于Intel公司提供的物理地址扩展/页扩展技术而构建的。 3、根据权利要求2所述的方法,其特征在于,进一步包括如下步骤: 在存储器的控制缓存器CR3中装载一具有两级页表结构的页映像表; 在存储器的控制缓存器CR4中设定所述线性地址第5位支持所述物理地址 扩展功能,并设定该线性地址第4位的偏移大小;以及

嵌入式资源免费分享区 https://www.doczj.com/doc/b94185112.html,

一片Norflash上建立bootrom和TFFS文件系统

开发环境:2410+AM29LV160DB(前 0.5m 存放 bootrom,后 1.5m 建立 TFFS) NorFLash 挂接 bank0 由网络上 sst39vf160 源代码修改而来 主要修改了文件名、命令字序列、加入屏蔽中断、mmu 映射,其他部分改动很少 ①关键问题描述与解决措施 问题描述:在 wshell 中调用 tffsDevFormat -> tffsDevFormat Identify AM29LV160 media.0x2249 shine**********identify ok shine**********lv160MTDErase routine(进入擦除命令后停止) shine**********ret is 100000,call by lv160MTDMap0(此处是我在 map 函数中 增加的打印) Exception number 12: Task: 0x33e18b98 (t17) Instruction prefetch abort Program Counter: 0x200000 Status Register: 0x20000097 value = 0 = 0x0 结果系统进入异常 解 决措施:需要在擦除和写操作中屏蔽中断,因为 Flash 在擦除、写和读 ID 状态时,不能正常读取 Flash 中数据。而 VxWorks 的异常入口位于 Flash 存储 器的开始处,异常发生时不能得到正常的入口指令,会导致系统跑飞。解决这个 问题的最好方法是添加第 2 片 Flash 存储器, 专门用于文件系 统。 (摘自 Amine 的 44B0 调试笔记) ②在 lv160mtd.c 中(把文件名 sst39vf160 改为 lv160mtd.c) 增加如下头文件 # include "intLib.h" /* include intLock() and intUnlock() */ 屏蔽中断函数使用示例: 代码: int Eint_lock_key; int_lock_key = intLock (); /* disable interrupts*/ intUnlock (int_lock_key); /* restore interrupt enable setting*/ 代码:

flash存储原理 一、半导体存储设备的原理 目前市面上出现了大量的便携式存储设备,这些设备大部分是以半导体芯片为存储介质的。采用半导体存储介质,可以把体积变的很小,便于携带;与硬盘之类的存储设备不同,它没有机械结构,所以也不怕碰撞;没有机械噪声;与其它存储设备相比,耗电量很小;读写速度也非常快。半导体存储设备的主要缺点就是价格和容量。 现在的半导体存储设备普遍采用了一种叫做“FLASH MEMORY”的技术。从字面上可理解为闪速存储器,它的擦写速度快是相对于EPROM而言的。FLASH MEMORY是一种非易失型存储器,因为掉电后,芯片内的数据不会丢失,所以很适合用来作电脑的外部存储设备。它采用电擦写方式、可10万次重复擦写、擦写速度快、耗电量小。 1.NOR型FLASH芯片 我们知道三极管具备导通和不导通两种状态,这两种状态可以用来表示数据0和数据1,因此利用三极管作为存储单元的三极管阵列就可作为存储设备。FLASH 技术是采用特殊的浮栅场效应管作为存储单元。这种场效应管的结构与普通场管有很大区别。它具有两个栅极,一个如普通场管栅极一样,用导线引出,称为“选择栅”;另一个则处于二氧化硅的包围之中不与任何部分相连,这个不与任何部分相连的栅极称为“浮栅”。通常情况下,浮栅不带电荷,则场效应管处于不导通状态,场效应管的漏极电平为高,则表示数据1。编程时,场效应管的漏极和选择栅都加上较高的编程电压,源极则接地。这样大量电子从源极流向漏极,形成相当大的电流,产生大量热电子,并从衬底的二氧化硅层俘获电子,由于电子的密度大,有的电子就到达了衬底与浮栅之间的二氧化硅层,这时由于选择栅加有高电压,在电场作用下,这些电子又通过二氧化硅层到达浮栅,并在浮栅上形成电子团。浮栅上的电子团即使在掉电的情况下,仍然会存留在浮栅上,所以信息能够长期保存(通常来说,这个时间可达10年。由于浮栅为负,所以选择栅为正,在存储器电路中,源极接地,所以相当于场效应管导通,漏极电平为低,即数据0被写入。擦除时,源极加上较高的编程电压,选择栅接地,漏极开

实验一存储器实验 1.FPGA中LPM_ROM定制与读出实验 一.实验目的 1、掌握FPGA中lpm_ROM的设置,作为只读存储器ROM的工作特性和配置方法。 2、用文本编辑器编辑mif文件配置ROM,学习将程序代码以mif格式文件加载于 lpm_ROM中; 3、在初始化存储器编辑窗口编辑mif文件配置ROM; 4、验证FPGA中mega_lpm_ROM的功能。 二.实验原理 ALTERA的FPGA中有许多可调用的LPM (Library Parameterized Modules)参数化的模块库,可构成如lpm_rom、lpm_ram_io、lpm_fifo、lpm_ram_dq的存储器结构。CPU中的重要部件,如RAM、ROM可直接调用他们构成,因此在FPGA中利用嵌入式阵列块EAB可以构成各种结构的存储器,lpm_ROM是其中的一种。 lpm_ROM有5组信号:地址信号address[ ]、数据信号q[ ]、时钟信号inclock、outclock、允许信号memenable,其参数都是可以设定的。由于ROM是只读存储器,所以它的数据口是单向的输出端口,ROM中的数据是在对FPGA现场配置时,通过配置文件一起写入存储单元的。图3-1-1中的lpm_ROM有3组信号:inclk——输入时钟脉冲;q[23..0]——lpm_ROM的24位数据输出端;a[5..0]——lpm_ROM的6位读出地址。 实验中主要应掌握以下三方面的内容: ⑴lpm_ROM的参数设置; ⑵lpm_ROM中数据的写入,即LPM_FILE初始化文件的编写;

⑶lpm_ROM的实际应用,在GW48_CP+实验台上的调试方法。 三.实验步骤 (1)用图形编辑,进入mega_lpm元件库,调用lpm_rom元件,设置地址总线宽度address[]和数据总线宽度q[],分别为6位和24位,并添加输入输出引脚,如图3-1-1设置和连接。 (2)设置图3-1-1为工程。 (3)在设置lpm_rom数据参数选择项lpm_file的对应窗口中(图3-1-2),用键盘输入lpm_ROM配置文件的路径(rom_a.mif),然后设置在系统ROM/RAM读写允许,以便能对FPGA中的ROM在系统读写。 (4) 用初始化存储器编辑窗口编辑lpm_ROM配置文件(文件名.mif)。这里预先给出后 面将要用到的微程序文件:rom_a.mif 。rom_a.mif中的数据是微指令码(图3-1-3)。 (5)全程编译。 (6)下载SOF文件至FPGA,改变lpm_ROM的地址a[5..0],外加读脉冲,通过实验台上的数码管比较读出的数据是否与初始化数据(rom_a.mif中的数据)一致。 注:下载sof示例文件至实验台上的FPGA,选择实验电路模式仍为NO.0,24位数据输出由数码8至数码3显示,6位地址由键2、键1输入,键1负责低4位,地址锁存时钟CLK由键8控制,每一次上升沿,将地址锁入,数码管8/7/6/5/4/3将显示ROM 中输出的数据。发光管8至1显示输入的6位地址值。

NAND与NOR FLASH的原理与异同! 一、存储数据的原理 两种闪存都是用三端器件作为存储单元,分别为源极、漏极和栅极,与场效应管的工作原理相同,主要是利用电场的效应来控制源极与漏极之间的通断,栅极的电流消耗极小,不同的是场效应管为单栅极结构,而FLASH为双栅极结构,在栅极与硅衬底之间增加了一个浮置栅极。[attach]158 [/attach] 浮置栅极是由氮化物夹在两层二氧化硅材料之间构成的,中间的氮化物就是可以存储电荷的电荷势阱。上下两层氧化物的厚度大于50埃,以避免发生击穿。 二、浮栅的重放电 向数据单元内写入数据的过程就是向电荷势阱注入电荷的过程,写入数据有两种技术,热电子注入(hot electron injection)和F-N隧道效应(Fowler Nordheim tunneling),前一种是通过源极给浮栅充电,后一种是通过硅基层给浮栅充电。NOR型FLASH通过热电子注入方式给浮栅充电,而NAND则通过 F-N隧道效应给浮栅充电。 在写入新数据之前,必须先将原来的数据擦除,这点跟硬盘不同,也就是将浮栅的电荷放掉,两种FLASH都是通过F-N隧道效应放电。 三、0和1 这方面两种FLASH一样,向浮栅中注入电荷表示写入了'0',没有注入电荷表示'1',所以对FLASH清除数据是写1的,这与硬盘正好相反; 对于浮栅中有电荷的单元来说,由于浮栅的感应作用,在源极和漏极之间将形成带正电的空间电荷区,这时无论控制极上有没有施加偏置电压,晶体管都将处于导通状态。而对于浮栅中没有电荷的晶体管来说只有当控制极上施加有适当的偏置电压,在硅基层上感应出电荷,源极和漏极才能导通,也就是说在没有给控制极施加偏置电压时,晶体管是截止的。如果晶体管的源极接地而漏极接位线,在无偏置电压的情况下,检测晶体管的导通状态就可以获得存储单元中的数据,如果位线上的电平为低,说明晶体管处于导通状态,读取的数据为0,如果位线上为高电平,则说明晶体管处于截止状态,读取的数据为1。由于控制栅极在读取数据的过程中施加的电压较小或根本不施加电压,不足以改变浮置栅极中原有的电荷量,所以读取操作不会改变FLASH中原有的数据。 四、连接和编址方式 两种FLASH具有相同的存储单元,工作原理也一样,为了缩短存取时间并不是对每个单元进行单独的存取操作,而是对一定数量的存取单元进行集体操作, NAND型FLASH各存储单元之间是串联的,而NOR型FLASH各单元之间是并联的;为了对全部的存储单元有效管理,必须对存储单元进行统一编址。 NAND的全部存储单元分为若干个块,每个块又分为若干个页,每个页是512byte,就是512个8位数,就是说每个页有512条位线,每条位线下有8个存储单元;那么每页存储的数据正好跟硬盘的一个扇区存储的数据相同,这是设计时为了方便与磁盘进行数据交换而特意安排的,那么块就类似硬盘的簇;容量不同,块的数量不同,组成块的页的数量也不同。在读取数据时,当字线和位线锁定某个晶体管时,该晶体管的控制极不加偏置电压,其它的7个都加上偏置电压而导通,如果这个晶体管的浮栅中有电荷就会导通使位线为低电平,读出的数就是0,反之就是1。 NOR的每个存储单元以并联的方式连接到位线,方便对每一位进行随机存取;具有专用的地址线,可以实现一次性的直接寻址;缩短了FLASH对处理器指令的执行时间。 五、性能

龙源期刊网 https://www.doczj.com/doc/b94185112.html, 存储器测试算法及诊断覆盖率研究 作者:陈金鸿谢亚莲 来源:《企业技术开发·下旬刊》2014年第04期 摘要:随着微电子技术的快速进步,半导体集成电路高速发展,新的存储器测试技术也 不断更新。文章描述了存储器的经典测试算法运算过程,并分析了其原理。在研究经典测试算法的基础上,吸收经典算法的思想,比较各种不同算法的优缺点,改进测试算法,以便在实际检测中能够减少测试所需要的时间,提高故障诊断覆盖率,达到比较满意的测试效果。 关键词:存储器;测试算法;诊断覆盖率 中图分类号:TP333.8 文献标识码:A 文章编号:1006-8937(2014)12-0009-02 存储器测试技术是一直不断更新的技术,随着存储器在市场上的需求日益增加,每一种新存储器技术的出现都会引起广泛的关注,往往新技术的出现都对实际测试工作造成巨大的改变。而面对越来越大的存储器市场,生产商对于存储器功能安全越来越重视,寻找高效的测试算法一直是存储器测试过程中需要解决的问题。 1 存储器测试算法 对于存储器的测试,目前有许多种测试算法,有使用时间长久的经典算法,也有近些年运用广泛的新型算法,它们都各有特点。 现主要的算法有MSCAN算法(全“0”全“1”算法)、Checkerboard算法(棋盘法)、Gallop算法(奔跳法)、March算法等。一种实用有效的测试算法,能够花费较少的时间和操作程序,更全面的检测出存储器故障。 1.1 MSCAN算法(全“0”全“1”算法) 对所有单元写“1”,再读取所有单元,进行对比。对所有单元写“0”,再读取所有单元,进行对比。算法表达式:{■(w0);■(r0);■(w1);■(r1)}。算法的执行方式可以如下: ①从检测起始点,沿着地址递增的方向将所有存储单元写“0”;②从检测起始点,沿着地址递增的方向读出所有存储单元的值“0”;③从检测起始点,沿着地址递增的方向将所有存储单元写“1”;④从检测起始点,按照地址递增的方向读出所有储存单元的值“1”。 可编程为: For I=1 to n;Do

湘潭大学论文 题目:关于Flash存储器的技术和发展 学院:材料与光电物理学院 专业:微电子学 学号:2010700518 姓名:李翼缚 完成日期:2014.2.24

目录 1引言 (4) 2Flash 存储器的基本工作原理 (4) 3 Flash存储器的编程机制 (5) 3.1 沟道热电子注入(CHE) (5) 3.2 F-N隧穿效应(F-NTunneling) (6) 4 Flash存储器的单元结构 (6) 5 Flash存储器的可靠性 (7) 5.1 CHE编程条件下的可靠性机制 (8) 5.2 隧道氧化层高场应力下的可靠性机制 (8) 6 Flash存储器的发展现状和未来趋势 (9) 参考文献: (10)

关于Flash存储器的技术和发展 摘要:Flash 存储器是在20世纪80年代末逐渐发展起来的一种新型半导体不挥发性存储器,它具有结构简单、高密度、低成本、高可靠性和在系统的电可擦除性等优点, 是当今半导体存储器市场中发展最为迅速的一种存储器。文章对F lash 存储器的发展历史和工作机理、单元结构与阵列结构、可靠性、世界发展的现状和未来趋势等进行了深入的探讨。 关键词:半导体存储器;不挥发性存储器; Flash存储器; ETOX结构 About Flash Memory Technology and Its Development Abstract: As a new non -volatile semiconductor memory introduced by Masuoka in 1984, flash memory has a number of advantages, such as simple structure, high integration density, low cost, and high reliability, and it is widely used in mobile phone, digital camer a, PCBIOS, DVD player, and soon. Its evolution, programming mechanism, cell structure, array structure, reliability are described, and its developing trend in the future is dis cussed. Key words: Semico nduct or memory; Flash memor y; Non-volatile memory ; ETOX

浅谈NorFlash的原理及其应用 NOR Flash NOR Flash是现在市场上两种主要的非易失闪存技术之一。Intel 于1988年首先开发出NOR Flash 技术,彻底改变了原先由EPROM(Erasable Programmable Read-Only-Memory电可编程序只读存储器)和EEPROM(电可擦只读存储器Electrically Erasable Programmable Read - Only Memory)一统天下的局面。紧接着,1989年,东芝公司发表了NAND Flash 结构,强调降低每比特的成本,有更高的性能,并且像磁盘一样可以通过接口轻松升级。NOR Flash 的特点是芯片内执行(XIP ,eXecute In Place),这样应用程序可以直接在Flash闪存内运行,不必再把代码读到系统RAM中。NOR 的传输效率很高,在1~4MB的小容量时具有很高的成本效益,但是很低的写入和擦除速度大大影响到它的性能。NAND的结构能提供极高的单元密度,可以达到高存储密度,并且写入和擦除的速度也很快。应用NAND的困难在于Flash的管理需要特殊的系统接口。性能比较 flash闪存是非易失存储器,可以对称为块的存储器单元块进行擦写和再编程。任何flash 器件的写入操作只能在空或已擦除的单元内进行,所以大多数情况下,在进行写入操作之前必须先执行擦除。NAND器件执行擦除操作是十分简单的,而NOR则要求在进行擦除前先要将目标块内所有的位都写为0。由于擦除NOR器件时是以64~128KB的块进行的,执行一个写入/擦除操作的时间为5s,与此相反,擦除NAND器件是以8~32KB的块进行的,执行相同的操作最多只需要4ms。执行擦除时块尺寸的不同进一步拉大了NOR和NAND之间的性能差距,统计表明,对于给定的一套写入操作(尤其是更新小文件时),更多的擦除操作必须在基于NOR的单元中进行。这样,当选择存储解决方案时,设计师必须权衡以下的各项因素。 l 、NOR的读速度比NAND稍快一些。 2、NAND的写入速度比NOR快很多。 3 、NAND的4ms擦除速度远比NOR的5s快。 4 、大多数写入操作需要先进行擦除操作。 5 、NAND的擦除单元更小,相应的擦除电路更少。此外,NAND 的实际应用方式要比NOR复杂的多。NOR可以直接使用,并可在上面直接运行代码;而NAND需要I/O接口,因此使用时需要驱动程序。不过当今流行的操作系统对NAND结构的Flash都有支持。此外,Linux内核也提供了对NAND结构的Flash的支持。详解 NOR

Vol.45No.4 740 计算机与数字工程 Computer /Digital Engineering总第330期 2017年第4期存储器测试图形算法概述$ 罗晶杨士宁石雪梅 (航天科工防御技术研究试验中心北京100854) 摘要存储器的高集成度化、高速化,为存储器测试带来了极大挑战。论文介绍了存储器测试图形的原理和发展,基于传统的存储器测试图形,综合描述了目前国内外几种较为新颖的且可用于实际工业生产的存储器测试图形改进算法。 关键词存储器测试;测试图形&改进的齐步算法 中图分类号TP391 DO# 10.3969/j.issn1672-9722. 2017. 04.031 Summary of Test Pattern Algorithm for Memory LUO Jing YANG Shining SHI Xuemei (Institute201 of the Second Academy of China Aerospace Science/Industry Corp,Beijing100854) Abstract tt brings big challenge to the testing of semiconductor memory with the development of its high integration and speed.The principle and development of test pattern for memory are introduced.Ameliorated test pattern for memory used in industry manufacture based on traditional test pattern for memory is described synthetically at present. Key Words memory test,test pattern,improved march pattern algorithm Class Number TP391 1引言 随着集成电路制造工艺的不断进步,半导体芯 片的发展趋于高密度、高速度、高复杂度,给测试带 来了极大的挑战[1]。存储器是集成电路产品中的 一个主要门类,主要用来存放数据、指令、程序等信 息。存储器的测试一方面可用于判断产品质量是 否合格,另一方面通过测试获得一些数据用于改进 工艺[2]。 目前存储器的基本测试方法已经比较成熟,主 要有存储器直接存取测试、存储器的宏测试、存储 器内建自测试三种,各有利弊。存储器直接存取测 试是利用自动测试设备来进行测试,自动测试设备 的性能和测试成本使得直接存取测试方式对大容 量的存储器并不合适。存储器的宏测试将存储器 作为一个宏模块,利用电路内部的扫描路径生成宏 模块的测试向量,再通过自动测试设备在电路外部施加测试矢量,对于较大的存储器,宏测试向量的 数据量较大,测试需要较长时间。存储器内建自测 试是在存储器外围产生一整套控制电路,实现芯片 内置存储器测试模式的自动产生及测试结果的自 动判别,这种方法增加芯片的面积,但是具有自动化程度 、量 、、等优势(]。 对于存储器来说,最主要的测试是读写逻辑功 能测试,以检测存储单元的故障,包括由于坏的金 属连接、坏的元件、芯片逻辑错误等原因引起的功 能故障。这些故障通常被简化为几个较为成熟的 故障模型,通过不同的测试图形算法来检测故障。 本文以存储器的测试图形为切入点,先简单介 绍存储器简化的故障模型,然后介绍常用的存储器 测试图形算法以及一些新近提出的改进存储器测 试图形算法,对其进行比较,并对将来存储器测试 图形的发展进行预期。 收稿日期:2016年10月8日,修回日期:2016年11月25日 作者简介:罗晶,女,硕士,助理工程师,研究方向:元器件测试。杨士宁,男,硕士,工程师,研究方向:元器件测试。石雪梅,女,硕士,工程师,研究方向:元器件测试。

STM32学习笔记-Flash做为存储器储存数据 说到STM32的FLSAH,我们的第一反应是用来装程序的,实际上,STM32的片内FLASH不仅用来装程序,还用来装芯片配置、芯片ID、自举程序等等。当然, FLASH 还可以用来装数据。 自己收集了一些资料,现将这些资料总结了一下,不想看的可以直接调到后面看怎么操作就可以了。 FLASH分类 根据用途,STM32片内的FLASH分成两部分:主存储块、信息块。主存储块用于存储程序,我们写的程序一般存储在这里。信息块又分成两部分:系统存储器、选项字节。系统存储器存储用于存放在系统存储器自举模式下的启动程序(BootLoader),当使用ISP方式加载程序时,就是由这个程序执行。这个区域由芯片厂写入BootLoader,然后锁死,用户是无法改变这个区域的。选项字节存储芯片的配置信息及对主存储块的保护信息。 FLASH的页面 STM32的FLASH主存储块按页组织,有的产品每页1KB,有的产品每页2KB。页面典型的用途就是用于按页擦除FLASH。从这点来看,页面有点像通用FLASH 的扇区。 STM32产品的分类 STM32根据FLASH主存储块容量、页面的不同,系统存储器的不同,分为小容量、中容量、大容量、互联型,共四类产品。 小容量产品主存储块1-32KB,每页1KB。系统存储器2KB。 中容量产品主存储块64-128KB,每页1KB。系统存储器2KB。 大容量产品主存储块256KB以上,每页2KB。系统存储器2KB。 互联型产品主存储块256KB以上,每页2KB。系统存储器18KB。 对于具体一个产品属于哪类,可以查数据手册,或根据以下简单的规则进行区分: STM32F101xx、STM32F102xx 、STM32F103xx产品,根据其主存储块容量,一定是小容量、中容量、大容量产品中的一种,STM32F105xx、STM32F107xx是互联型产品。 互联型产品与其它三类的不同之处就是BootLoader的不同,小中大容量产品的BootLoader只有2KB,只能通过USART1进行ISP,而互联型产品的BootLoader有18KB,能通过USAT1、4、CAN等多种方式进行ISP。小空量产品、中容量产品的BootLoader与大容量产品相同。 关于ISP与IAP ISP(In System Programming)在系统编程,是指直接在目标电路板上对芯片进行编程,一般需要一个自举程序(BootLoader)来执行。ISP也有叫ICP (In Circuit Programming)、在电路编程、在线编程。 IAP(In Application Programming)在应用中编程,是指最终产品出厂后,由最终用户在使用中对用

RAM / ROM 存储器 ROM和RAM指的都是半导体存储器,ROM是Read Only Memory的缩写,RAM是Random Access Memory的缩写。ROM在系统停止供电的时候仍然可以保持数据,而RAM通常都是在掉电之后就丢失数据,典型的RAM就是计算机的内存。 RAM 有两大类: 1) 静态RAM(Static RAM / SRAM),SRAM速度非常快,是目前读写最快的存储设备了,但是它也非常昂贵,所以只在要求很苛刻的地方使用,譬如CPU的一级缓冲,二级缓冲。 2) 动态RAM(Dynamic RAM / DRAM),DRAM保留数据的时间很短,速度也比SRAM慢,不过它还是比任何的ROM都要快,但从价格上来说DRA M相比SRAM要便宜很多,计算机内存就是DRAM的。 DRAM分为很多种,常见的主要有FPRAM / FastPage、EDORAM、SD RAM、DDR RAM、RDRAM、SGRAM以及WRAM等,这里介绍其中的一种DDR RAM。 DDR RAM(Double-Date-Rate RAM)也称作DDR SDRAM,这种改进型的RAM和SDRAM是基本一样的,不同之处在于它可以在一个时钟读写两次数据,这样就使得数据传输速度加倍了。 这是目前电脑中用得最多的内存,而且它有着成本优势,事实上击败了Int el的另外一种内存标准~Rambus DRAM。 在很多高端的显卡上,也配备了高速DDR RAM来提高带宽,这可以大幅度提高3D加速卡的像素渲染能力。 ROM也有很多种: 1) PROM(可编程ROM),是一次性的,也就是软件灌入后,就无法修改了,这种是早期的产品,现在已经不可能使用了; 2) EPROM (可擦除可编程ROM),是通过紫外光的照射擦出原先的程序,是一种通用的存储器。 3) EEPROM,是通过电子擦除,价格很高,写入时间很长,写入很慢。 举个例子,手机软件一般放在EEPROM中,我们打电话,有些最后拨打的号码,暂时是存在SRAM中的,不是马上写入通话记录(通话记录保存在EEP ROM中),因为当时有很重要工作(通话)要做,如果写入,漫长的等待是让用户忍无可忍的。 内存工作原理 内存是用来存放当前正在使用的(即执行中)的数据和程序,我们平常所提到的计算机的内存指的是动态内存(即DRAM)。 动态内存中所谓的“动态”,指的是当我们将数据写入DRAM后,经过一段时间,数据会丢失,因此需要一个额外设电路进行内存刷新操作。 具体的工作过程是这样的: 一个DRAM的存储单元存储的是0还是1取决于电容是否有电荷,有电荷代表1,无电荷代表0。 但时间一长,代表1的电容会放电,代表0的电容会吸收电荷,这就是数据丢失的原因。 刷新操作定期对电容进行检查,若电量大于满电量的1/2,则认为其代表1,并把电容充满电;若电量小于1/2,则认为其代表0,并把电容放电,藉此

网络存储测试方案 一.目前主流网络存储设备厂商及其主要产品的特点及主要性能指标主流厂商: EMC,IBM,HDS,Netapp等。 EMC 目前EMC产品存储方面主要涵盖:NAS、SAN、云计算等方面。主要产品有: EMC Atmos 集全球规模的存储能力与云体系结构的优势于一身,提供能够满足企业和服务提供商需求的解决方案。 EMC isilon 针对大数据的强大横向扩展NAS 解决方案,不管规模如何,其安装、管理和扩展都很简单。 EMC Symmetrix 10K/20K/40K 这系列三个产品从经济性到高性能均覆盖到,其中 10K:最经济划算的多控制器阵列,专门针对高性能和高效率而设计,适合在虚拟环境中整合应用程序。 20K:专门针对高要求虚拟数据中心环境的性能、整合和自动化需求而打造。 40K:专为混合云环境打造,提供了业界最高级别的整合、性能和可扩展性。 EMC VNX 高性能统一存储,具有无与伦比的简洁性和高效性,针对虚拟应用程序而优化。 IBM IBM TotalStorage DS8870 提供高达 3 倍的性能提升,以实现更快的事务处理速度和实时分析 凭借与IBM 企业级服务器集成的完全硬件冗余的先进业务持续性解决方案,提供卓越的系统可用性 凭借 5 代IBM? System Storage? Easy Tier? 功能和其他先进的自我调整功能,优化性能和成本目标 扩展至高达 1 TB 的系统缓存和高达 2 PB 的容量 通过出色的可扩展性、自我优化、驱动器分层和对广泛工作负载的支持实现整合 IBM XIV 存储系统 针对极致的易用性和运营敏捷性设计的久经考验的创新性高端磁盘存储系统热点、始终如一的高性能,以及通过网格架构实现的大规模并行处理 适用于优化的云与虚拟环境的虚拟化存储资源 通过完全冗余、自我修复和无与伦比的重建速度实现的极高可靠性与可用性