介绍一款基于MPC8548的数据处理板

- 格式:pdf

- 大小:4.12 MB

- 文档页数:9

飞思卡尔双核处理器MPC8572开发参考平台为帮助⽹络设备⼚商简化系统设计和构建智能应⽤⽹络,MICETEK推出基于MPC8572的开发板。

这套开发系统由MPC8572处理器卡(MPC8572PC)和Type-N载板(PQCBN)组成,使开发⼈员能快速⽅便搭建硬件平台,⼤⼤缩短开发周期,加快产品上市。

开发⼈员可以直接迅速得在此平台上进⾏软件设计和调试。

Type-N载板是⼀个MPC85XX系列处理器卡的通⽤I/O 平台。

它提供了千兆以太⽹接⼝,PCI插槽,PCI-Express插槽和串⼝等,⽤于⾼端⽹络通信应⽤,例如企业⽹络,电信传输和交换,3G⽆线架构,存贮和⾼端影像等市场。

我们同时提供Linux BSP给开发⼈员,包括U-BOOT,Linux kernel和⼀些底层接⼝驱动,另外还提供载板设计⽂件和处理器卡原理图(PDF⽂档)。

下图为MT8572-N实物照⽚。

MPC8572系列处理器能够提供⾼达1.2GHz到1.5GHz的设计时钟速率,采⽤了两个强⼤的e500处理器内核,通过增强型外围设备和⾼速互连技术,对处理器性能和I/O系统吞吐量进⾏平衡。

MPC8572基于飞思卡尔90nm规格的绝缘体硅芯⽚(SOI)铜连接制程技术,能够实现更⾼的性能和更低的功耗。

MPC8572在处理器性能⽅⾯有了极⼤的提⾼,并且代表了PowerQUICC 系列主流嵌⼊式处理器在不断创新过程中的最⾼⽔平。

通过⽆损化集成,MPC8572平台构建在⾼性能的嵌⼊式Power Architecture技术之上,加⼊了更多新的⾼级特性,增强了深度数据报检测、分类管理和安全加速等功能。

开发板主要性能:CPU: MPC8572 双e500内核,每个核主频最⾼可达1.333GHz;性能:6897 MIPS@1500 MHzMemory:— 512Mbytes DDR2 at 533MHz SDRAM— 8MBytes NOR flash memory at 16-bit port size— 32MBytes NAND flash memory in 8-bit mode接⼝:— 四个千兆以太⽹接⼝— 三个PCI 插槽— ⼀个PCI Express插槽— ⼀个RS-232 串⼝MPC8572处理器卡总体情况:— COP接⼝— 5V风扇连接器— 由载板提供的3.3V 和 5V 电源— 灵活的POR配置,由不同的拨码开关设置— 10层PCB布线— 尺⼨:147mm x 70.9mmType-N载板总体情况:— 由4pin连接器提供的12 V 和5 V 电源— 6层PCB布线— 尺⼨:220mm x 148mm这套开发系统由MPC8541E处理器卡(MPC8541EPC)和Type-N载板(PQCBN)组成,使开发⼈员能快速⽅便搭建硬件平台,⼤⼤缩短开发周期,加快产品上市。

2008年第 4 期 声学与电子工程 总第 92 期40PowerPC平台引导加载程序的移植张 磊(第七一五研究所,杭州,310012)摘要引导加载程序(Boot Loader)是嵌入式系统软件开发的第一个环节,它把嵌入式操作系统和硬件平台衔接在一起,对于嵌入式系统的后续开发起到十分重要的作用。

U-Boot是目前比较流行且功能强大的Boot Loader,支持种类繁多的体系结构,尤其对PowerPC提供了完善的支持。

MPC8548E是基于E500v2内核,并提供多种接口控制器的处理器。

详细介绍了在基于MPC8548 CPU 的SBC8548E开发板上Boot Loader的移植过程。

关键词引导加载;程序设计;程序移植引导加载程序(Boot Loader)是用来启动设备以及执行内核加载的系统软件组件,配置Boot Loader是所有嵌入式操作系统的一项必要工作。

Linux内核有许多Boot Loader可用,不同架构之间的Boot Loader的质和量也有很大的差异。

Das U-Boot(一般称为U-Boot)被认为是功能最多、最具有弹性以及开发最积极的开放源码Boot Loader。

而基于E500内核的PowerPC芯片是Freescale公司未来高端通信领域的发展方向。

因此研究分析基于E500内核的U-Boot对于深入理解PowerPC架构以及开发后续嵌入式操作系统Linux具有积极的意义。

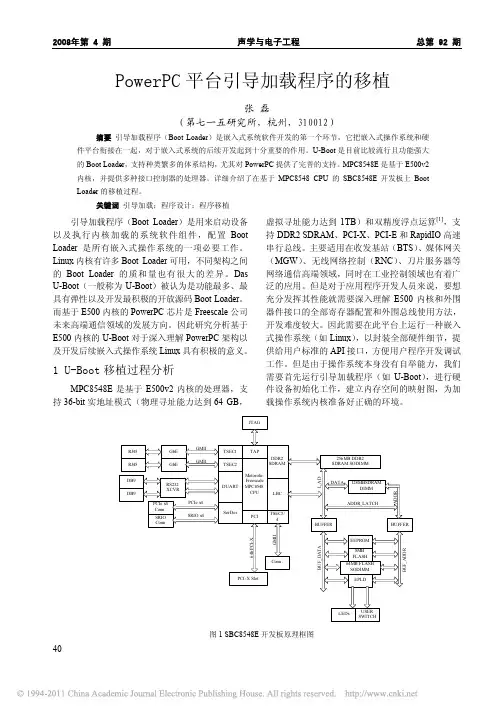

1 U-Boot移植过程分析MPC8548E是基于E500v2内核的处理器,支持36-bit实地址模式(物理寻址能力达到64 GB,虚拟寻址能力达到1TB)和双精度浮点运算[1],支持DDR2 SDRAM、PCI-X、PCI-E和RapidIO高速串行总线。

主要适用在收发基站(BTS)、媒体网关(MGW)、无线网络控制(RNC)、刀片服务器等网络通信高端领域,同时在工业控制领域也有着广泛的应用。

但是对于应用程序开发人员来说,要想充分发挥其性能就需要深入理解E500内核和外围器件接口的全部寄存器配置和外围总线使用方法,开发难度较大。

整个系统的硬件具高成熟度、高稳定度、高安全性、高集成度特性。

板集成度很高,采用14层的PCB。

PCB使用等级为FR-阻燃材料制成。

为确保系统的稳定性,选用芯片都采用业界成熟稳定的芯片,主芯片信息介绍如下:CPU芯片采用飞思卡尔公司的MPC 8548,MPC8548它基于Freescale(飞思卡尔)的PowerPC架构的PowerQuicc III处理器,同时兼容MPC8548E,MPC8547E、PC8545E、MPC8543E系列处理器,其强大的处理能力特别适合于高速低时延的处理。

基本特性如下:(1)处理器:Freescale PowerQuiccIII MPC8548E、MPC8547E、MPC8545E、MPC8543E系列处理器,最高频率1.5GHz(2)内存:最高2GByte DDR2 SDRAM(3)Flash:最高512KByte + 64MByte*2 + 1GByte。

支持从表贴大Flash直接启动以支持抗震指标基带芯片采用德州仪器(TI)的TMS320TCI6487,6487是并行频率高达3.6 GHz 的三核数字信号处理器,它完美结合了功能强大的软件库,全面优异的性能足以满足TD-SCDMA/TD-LTE 等复杂基带算法要求。

基本特性如下:(1)TCI6487 包括三个运行频率均为1.2 GHz 的DSP 内核。

(2)每个内核都拥有自己专用的1 Mb L2、32k L1 数据以及程序高速缓存,从而不仅可最大限度地减少片外存储器存取,还能实现高效率的软件架构。

(3)TI 简单易用的高效率编译器工具可显著节约开发与测试最新软件特性所需的时间。

(4)TCI6487 包含额外的高性能加速器和外设接口,并为蜂窝式基础局端产品进行了优化。

TI DSP 高度的灵活性与优异的简单易用性非常适用于多标准设计,也能作为多种目标设计的核心技术。

(5)除LTE 软件库之外,TI 还针对WiMAX 和WCDMA 提供了优化库,可进一步支持多标准开发。

CPCI总线主控板的设计实现【摘要】本文介绍了一种CPCI总线主控板的设计实现,该主控板采用飞思卡尔半导体公司的RISC微处理器MPC8548E,结合FW21154BE PCI-to-PCI 桥接芯片、DDRII、千兆网PHY和CPLD控制电路等其他电路。

主控板提供多种标准接口,移植VxWorks操作系统,性能稳定可靠。

【关键词】CPCI总线主控板;MPC8548E;VxWorks0.引言MPC8548E型CPCI总线主控板的主要功能是完成对信号处理机的网络和串口等系统信息控制、交换、信号处理板的软件加载等。

它采用的Compact PCI(简称CPCI)总线,该总线具有高带宽、高性能、高可靠性、即插即用、价格低廉等诸多优点,在板极实现上使用飞思卡尔半导体公司的RISC 微处理器MPC8548E。

MPC8548E 是飞思卡尔新一代的PowerQUICC III处理器,应用先进的90纳米绝缘硅(SoI)铜连线工艺,基于e500PowerPC 系统级芯片平台,结构简单,将CPU和桥接功能合为一体,具有千兆级网络功能,是最为苛刻的高速连接应用的理想选择。

1.主控板硬件设计1.1 CPCI总线主控板结构特性基于CPCI总线的MPC8548E型主控板的原理框图如图1所示,主要有以下几方面特性:(1)CPU是MPC8548E,主频可配,最高可达1.2GHz。

(2)512MB DDR2 SDRAM,频率为533MHz。

(3)48MB 的Flash,32KB的nvSRAM。

(4)一个32-bits的PCI总线,总线时钟33MHz,提供系统扩展。

(5)3个10/100/1000Mbsp以太网口。

(6)四个背板引出的RS232/RS422串口,一个RS232微型串口及16-bits 的TTL通用口。

(7)四个通道的DMA控制器。

(8)标准CPCI总线、标准6U尺寸。

(9)工作环境温度:-40℃-+80℃。

(10)功耗:CPU工作频率533MHz,整板功耗约11W。

基于MPC8548E的嵌入式数据处理系统设计

纪雄飞

【期刊名称】《现代导航》

【年(卷),期】2012(003)005

【摘要】提出了一种基于PowerPC的嵌入式数据处理系统设计方案,该方案以MPC8548E处理器为核心,详细阐述了系统的硬件设计和软件设计流程.

【总页数】6页(P373-378)

【作者】纪雄飞

【作者单位】中国电子科技集团公司第二十研究所,西安710068

【正文语种】中文

【中图分类】TP273

【相关文献】

1.基于嵌入式及触摸技术的核谱数据处理系统设计 [J], 杨忠;魏涛

2.基于MPC8548E的嵌入式实时系统自举优化设计 [J], 孙亮;杨斌;钟瑜

3.基于MPC8548E的通用嵌入式计算机平台系统软件研究和实现 [J], 李文光

4.基于MPC8548E的通用嵌入式计算机平台系统软件研究和实现 [J], 庞春辉

5.基于嵌入式的电脑横机数据处理系统设计 [J], 项贤军;马东玲

因版权原因,仅展示原文概要,查看原文内容请购买。

PowerPC处理器MPC8548E的DDR2接口实现

苏鹏;卞春江;张磊

【期刊名称】《微计算机信息》

【年(卷),期】2010(026)035

【摘要】本论文研究了DDR2的特性和M PC8548 E处理器的相关资料,给出了MPC8548E DDR2接口的硬件电路设计,并且通过实例讨论了在U-Boat下对MPC8548 E相关寄存器的配置,给出了试验结果.

【总页数】3页(P174-176)

【作者】苏鹏;卞春江;张磊

【作者单位】100190,北京,中国科学院空间科学与应用研究中心;100190,北京,中国科学院研究生院;100190,北京,中国科学院空间科学与应用研究中心;100190,北京,中国科学院空间科学与应用研究中心

【正文语种】中文

【中图分类】TN368

【相关文献】

1.基于FPGA的嵌入式处理器与PC/104总线接口实现 [J], 韩鸿凌

2.基于FPGA的嵌入式处理器与PC/104总线接口实现 [J], 韩鸿凌

3.基于POWERPC的ARINC429总线接口实现 [J], 李兴旺;颜国正;沈勇

4.Tundra向市场投放第一款用于PowerPC的DDR2内存支持的主桥 [J],

5.PMC—Sierra新推1.8GHz主频双CPU核64位MIPS—Powered多处理器——第三代多处理器RM11200增加了新CPU核心、PCI Express和DDR2 [J],

因版权原因,仅展示原文概要,查看原文内容请购买。

DDR2 SDRAM介绍及其基于MPC8548 CPU的硬件设计2009-02-26 01:35:44 文章出处:与非网DDR2 SDRAM芯片提供一个ODT引脚来控制开或关芯片内部的终结电阻。

在只有一个DDR2 SDRAM芯片作为存储器控制器的负载的情况下,写操作时,由于DDR2 SDRAM作为接收端,所以ODT引脚为高电平以打开芯片内部终结电阻DDR2 SDRAM引入的新技术DDR2(Double Data Rate 2,两倍数据速率,版本2) SDRAM,是由JEDEC标准组织开发的基于DDR SDRAM的升级存储技术。

相对于DDR SDRAM,虽然其仍然保持了一个时钟周期完成两次数据传输的特性,但DDR2 SDRAM在数据传输率、延时、功耗等方面都有了显著提高,而这些性能的提高,主要来源于以下技术的提升:ODT,Post CAS,4n数据预取,封装等。

ODTODT(On-Die Termination),即芯片内部匹配终结。

在DDR SDRAM应用中,需要通过大量的外部电阻上拉到VTT电平(1.25V)以实现信号匹配,以16位芯片为例,以下信号需要通过这种方式进行匹配:CK,CK#,DQ[15:0],LDQS,UDQS, ADDR[10:0],RAS#,CAS#,WE#,即一片芯片需要34个外部上拉电阻,极大的占用了宝贵的PCB面积。

同时,由于DQ[15:0],LDQS,UDQS等信号是双向信号,即读和写时,对匹配电阻的位置有不同要求,因此在电阻布局时很难在两个方向上同时实现最佳的信号完整性。

在DDR2 SDRAM中,采用ODT技术将许多外部的匹配电阻移到芯片内部从而节省了大量的PCB板上面积。

另外,ODT技术允许存储控制器(如下文的MPC8548 CPU)通过配置DDR2 SDRAM的内部寄存器以及控制ODT信号,来实现对匹配电阻的值及其开关状态进行控制,从而可以实现读,写操作时最佳的信号完整性。

基于MPC8548E的嵌入式数据处理系统设计纪雄飞【摘要】提出了一种基于PowerPC的嵌入式数据处理系统设计方案,该方案以MPC8548E处理器为核心,详细阐述了系统的硬件设计和软件设计流程.【期刊名称】《现代导航》【年(卷),期】2012(003)005【总页数】6页(P373-378)【关键词】PowerPC;MPC8548E;VxWorks;BSP【作者】纪雄飞【作者单位】中国电子科技集团公司第二十研究所,西安710068【正文语种】中文【中图分类】TP273随着科学技术的发展,嵌入式处理器在通信设备、消费电子、军用电子等领域有了广泛的应用,而且对处理器的处理速度、功耗及工作温度都有了更加严格的要求,尤其在军用电子方面的应用。

MPC8548E是 Freescale公司开发的新一代PowerQUICC III™系列的高性能处理器。

它基于90纳米(nm)的绝缘硅(SOI)铜互连工艺技术,内部工作频率可达1.5GHz,一级缓存有指令缓存和数据缓存各32KB,集成DDR2存储器控制器,支持PCI-E接口、Rapid IO接口,提供4个以太网控制器(TSEC)。

MPC8548E集成有高性能的e500内核,该内核采用超标量体系结构,在1.5GHz的工作频率时(-40~85℃的温度范围),处理速度可达3065MIPS。

MPC8548E 同时集成了丰富的外设接口,其强大的功能以及宽温、低功耗的特点为数据处理系统的设计提供了保证。

1 系统设计本处理系统采用PowerPC芯片作为核心处理器,用于完成多任务的数据处理功能;FPGA作为逻辑构建单元完成接口转换、时序控制等功能;DSP完成浮点运算、数据融合任务;话音电路部分完成话音信号的D/A、A/D变换。

系统具有丰富的外部接口,包括有高速LVDS接口,10M、100M、1000M自适应以太网接口,RS422串口,RS232串口等。

系统的构成框图如图 2所示。

2 硬件设计2.1 PowerPC设计PowerPC选用Freescale公司的MPC8548E处理器,最大主频1.5GHz(实际降频工作于1GHz)。

基于ADuC848嵌入式系统的实验和课程设计指导书(内部使用)主编银翔刘任斌汤春龙主审黎福海彭楚武二○一二年二月目录第一章硬件系统介绍 (5)1.1板上资源分布 (5)1.2单片机ADuC848 (6)1.2.1 ADuC848的简要介绍(针对本设计所选择的型号) (6)1.2.2 单片机引脚分布 (6)1.3 电源模块 (8)1.4 模数/数模转换 (9)1.4.1 模数转换 (9)1.4.2 数模转换 (9)1.5 RS232串口 (10)1.6 PS/2接口和红外接收 (11)1.7 显示模块 (11)1.7.1 LCD显示 (11)1.7.2 数码管 (12)1.7.3 8路LED (13)1.8 蜂鸣器和红外发送 (14)1.9 SPI接口、步进电机控制 (15)1.10 按键输入 (15)1.11 IIC总线(RTC时钟和EEPROM) (16)1.12 复位与下载 (17)第二章基础实验 (18)汇编实验 (18)实验一I/O 口控制实验 (18)实验二定时器、中断实验 (20)实验三数码显示实验 (24)实验四蜂鸣器驱动实验 (29)实验五128×64 点阵型液晶显示实验 (32)实验六1602字符显示实验 (44)实验七矩阵键盘实验 (53)实验八D/A转换实验 (56)实验九步进电机控制实验 (60)C语言实验 (63)实验一端口输出操作 (63)实验二定时器及定时器中断 (66)实验三数码管显示 (69)实验四矩阵式键盘识别 (73)实验五蜂鸣器驱动实验 (77)实验六1602字符显示实验 (82)实验七128×64 点阵型液晶显示实验 (85)实验九步进电机控制实验 (102)第三章系统设计方法及设计课题 (108)3.1 单片机应用系统的设计过程 (108)3.1.1 方案论证和硬件系统设计 (108)3.1.2 系统软件设计 (109)3.1.3 系统仿真调试设计 (109)3.2 设计课题 (110)3.2.1 多功能定时装置 (110)3.2.2 程控多波形信号发生器 (111)3.2.3 LCD汉字计时报讯屏 (111)3.2.4 简易多功能计数器 (112)3.2.5 LCD字符显示屏 (112)3.2.6 抢答器 (113)3.2.7 秒表 (113)3.2.8 数字密码锁 (113)3.2.9 简易电子琴 (114)3.2.10 LCD显示的交通信号灯 (114)3.2.11步进电机控制器 (114)3.2.12 A/D,D/A转换板 (115)3.2.13 电子计算器 (115)3.2.14 可编程微波炉控制系统 (115)3.2.15 简易超市收银机 (116)3.2.16 全自动洗衣机控制器 (117)3.2.17 多功能走马灯 (117)3.2.18 仿手机键盘 (118)3.2.19 仿电梯控制 (118)3.2.20 仿汽车自动报站器 (118)3.2.21 电机调速器 (119)3.2.22 电压监视仪 (119)3.2.23 自定义课题 (119)3.3 评分标准和注意事项 (120)3.3.1 选择课题 (120)3.3.2 评分标准 (120)3.3.3 实验室设备使用及安全和赔偿条例 (120)第四章Keil uVision4的使用 (122)4.1 前言 (122)4.2 新建工程 (122)4.3 工程设置 (125)4.4 编译连接、下载和调试程序 (128)4.4.1 编译程序 (128)4.4.3 在线调试程序 (130)4.4.4 软件仿真调试程序 (133)第五章PROTEUS的使用 (134)5.1 前言 (134)5.2 操作步骤 (134)5.2.1 进入系统 (134)5.2.2 界面简介 (134)5.2.3 操作步骤 (137)5.3 Proteus与KeiI的结合 (141)附录一课程设计报告参考模板 (142)附录二开发板硬件图 (144)第一章硬件系统介绍本单片机学习板集成多个基础硬件资源模块,各个资源模块可以相互组合使该板实现不同的功能。

基于POWER PC的数据处理系统设计吴杰【摘要】数据处理系统适合于车载、机载等恶劣环境下,运行多任务实时操作系统,完成信息层数据运算,以及高性能图形显示等多种应用.本文对于相关数据处理系统设计具有参考意义.【期刊名称】《科技视界》【年(卷),期】2018(000)008【总页数】4页(P4-7)【关键词】POWERPC;数据处理【作者】吴杰【作者单位】中国电子科技集团公司第二十研究所,陕西西安 710068【正文语种】中文【中图分类】TP274.2随着嵌入式系统的广泛应用,数据处理系统的扩展性和通用型越来越受到大家的关注。

本文中的数据处理板核心处理芯片采用基于POWER PC架构的MPC8548芯片,具有处理速度快,通用接口丰富、工作温度范围大的特点;软件部分选用多任务实时操作系统VxWorks,可以同时完成数据运算、高性能图形显示等多种工作,支持透明的底层硬件操作,实现软件编写与硬件设计分离,简化了底层软件设计,有很好的的扩展性和移植性。

1 系统设计本设计中采用POWER PC作为核心处理芯片,实现多任务并行数据处理功能;CPU主控MPC8548为整个模块数据处理中枢,处理外围各种芯片采集的数据,并将必要的数据保存到非易失存储器。

系统将高性能 MPC8548与嵌入式显示芯片SM722集成在一起,CPU通过PCI总线传输数据到显卡,提供用户交互界面;FPGA通过构建寄存器和双口RAM实现接口通信和时序控制等功能;DSP完成浮点运算和数据处理的功能;话音电路完成话音编解码和数模转换功能。

系统提供丰富的外部接口,包括串口(RS2232和 RS422)、以太网接口、USB接口、LVDS 总线接口以及VGA接口。

系统设计框架如图1所示。

2 硬件设计2.1 主控芯片设计本设计的POWER PC芯片选用Freescale公司的MPC8548处理器,该芯片是一款高性能、低功耗的32位RISC处理器。

最高主频超过800MHz,具有很强的定点和浮点计算能力。

DAM6000系列DAM6000系列能够通过多通道I/O模块进行数据采集和过程控制,为工业应用提供了灵活的数据采集和控制应用方案。

此产品系统由两部分组成:基座(主单元)和I/O模块。

主单元部分分为两个类别:DAM6600系列ARM7分布式RS-485/以太网数据采集及控制系统和DAM6800系列ARM9分布式RS-485/以太网数据采集及控制系统。

DAM6600系列ARM7分布式RS-485/以太网数据采集及控制系统同时支持工业以太网总线和RS-485总线,通过以太网总线可以10M/100Mbps的通讯速度对现场信号进行监控,而通过RS-485总线与主机相连,波特率可达115200bps。

DAM6800系列ARM9分布式RS-485/以太网数据采集及控制系统,可以通过EVC或VS编程语言对其进行编程和独立控制,同时可通过以太网串口和主机间进行数据通信。

DAM6000系列主模块选型表系统 DAM6600DAM6800 备注CPU LPC2292(ARM7)AT91SAM9261(ARM9)SRAM 16KB(片上)+1MB(外置)160KBDRAM —— 64MBFlash ROM 256KB 32KBFlash Memory 256MB(Nand)+2MB(Nor)256MB(Nand)+4MBEEPROM 256B Real-timeClockYes Yes Watchdog Yes YesTimerCOM1 RS485 RS485COM2(programing)RS232(3线) RS232(3线)COM3 RS232(5线)/RS485RS232(5线)/RS485COM4 RS232(5线)/RS485RS232(5线)/RS485CAN 2路——USB ——2路(键盘/鼠标/U盘/USB无线网卡)VGA —— 1xVGA(800x480Resolution)I/O slots 4/8 4/8Power consumption 2.5W(不包括I/O模块)4W(不包括I/O模块)IsolationCommunicatio n 2500Vdc 2500Vdc COM1 onlyCommunicationNetwork Ethernet(RJ-45) Ethernet(RJ-45) Speed 10/100Mbps 10/100Mbps Max Distance 150m 150mMax Nodes 32 32Protocol Modbus/RTUModbus/TCP Modbus/RTU Modbus/TCPRemote I/O Modbus Device Modbus DevicePower RequirementsPowerRequirements+12V ~ +36Vdc +12V ~ +36VdcEnvironmentOperatingTemperature-10 ~ +70℃-10 ~ +70℃StorageTemperature-25 ~ +85℃-25 ~ +85℃Humidity 5 ~ 95% 5 ~ 95%DimensionsDimensions 355 x 110x75mm355 x 110 x75mmDAM66008槽ARM7分布式RS-485/以太网数据采集及控制系统特点1、采用ARM7处理器。

MPC8548的动态降功耗设计

邱凯强;王树争

【期刊名称】《信息技术与信息化》

【年(卷),期】2022()2

【摘要】高性能CPU作为机载计算机数据处理模块的核心组件,其在恶劣环境下的性能将直接影响机载计算机的可靠性。

针对高性能CPU在恶劣环境下由于功耗过高而导致无法正常工作的问题,以MPC8548芯片为研究对象,提出一种基于MPC8548芯片的动态降功耗的方法。

方法通过控制内核频率和平台频率来降低功耗,并设计大量恶劣环境实验以验证该方法的可行性。

结果表明,方法有效地解决了MPC8548芯片功耗过高的问题,保证了其在恶劣环境下正常工作的能力。

在未来的嵌入式系统设计中可以通过使用该方式实现MPC8548的功耗控制。

【总页数】4页(P136-139)

【作者】邱凯强;王树争

【作者单位】航空工业西安航空计算技术研究所

【正文语种】中文

【中图分类】TP3

【相关文献】

1.Actel:ProASIC3L动态功耗降40%

2.一种基于PowerPC8640的动态降功耗方法研究设计

3.基于MPC8548的嵌入式设备的光通信接口设计与实现

4.应用于低功

耗嵌入式处理器的功耗动态管理策略设计5.一种基于国产处理器的动态降功耗方法研究设计

因版权原因,仅展示原文概要,查看原文内容请购买。