慢速充电时钟芯片DS1302

一、特性

1、实时时钟,可对秒、分、时、日、周、月以及带闰年补偿的年进行计数,有效期2100年。

2、用于高速数据暂存的31×8 RAM

3、最少引脚数的串行I/O

4、2.0-5.5V满度工作范围

5、2.5V时耗电小于300nA

6、用于时钟或RAM数据读/写的单字节或多字节(脉冲方式)数据传送

7、8引脚DIP或可选的用于表面安装的8引脚SOIC封装

8、简单的3线接口

9、TTL兼容(VCC=5V)

10、可选的工业温度范围-40℃至+85℃

11、与DS1202兼容

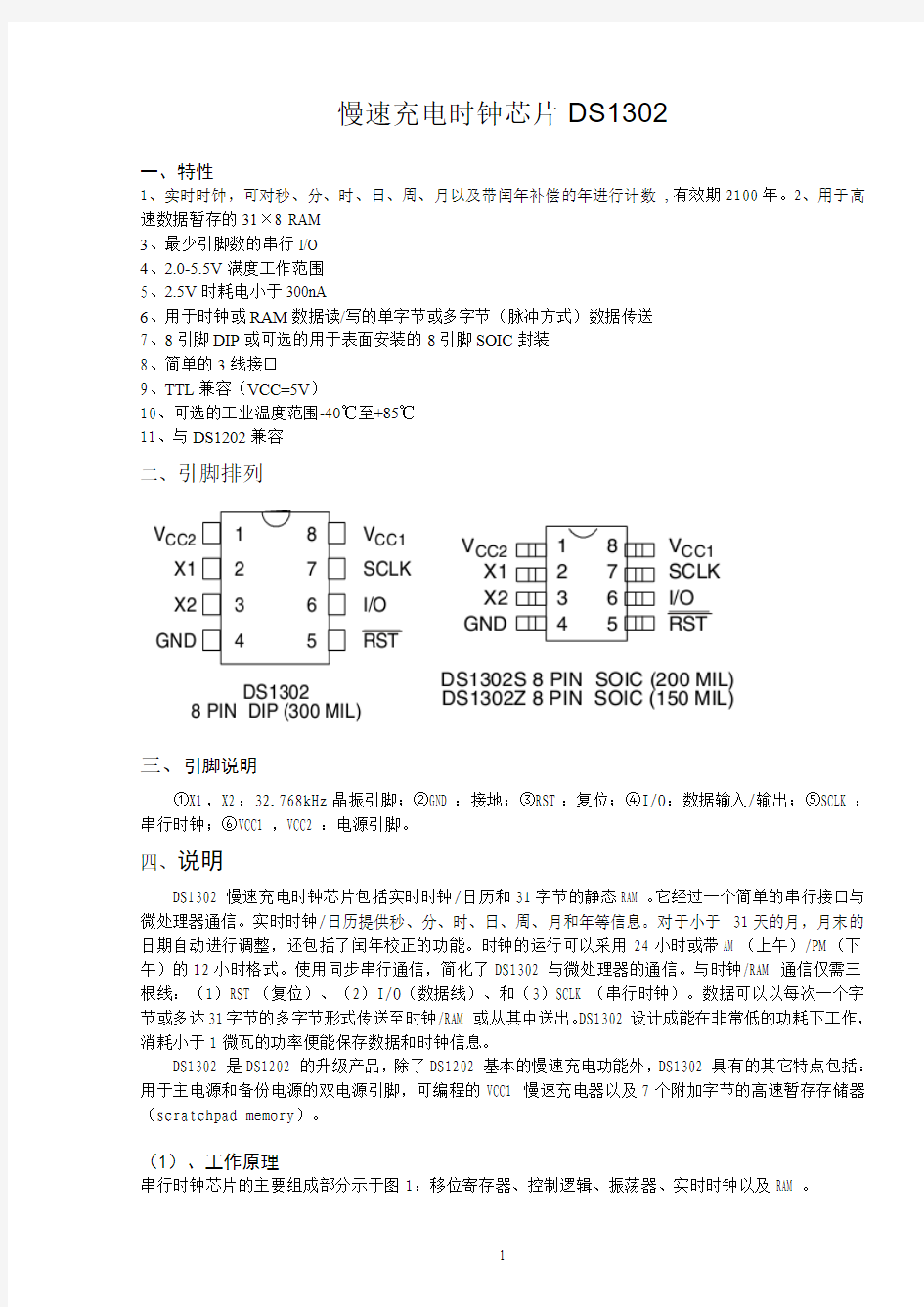

二、引脚排列

三、引脚说明

①X1,X2:32.768kHz晶振引脚;②GND:接地;③RST:复位;④I/O:数据输入/输出;⑤SCLK:串行时钟;⑥VCC1,VCC2:电源引脚。

四、说明

DS1302慢速充电时钟芯片包括实时时钟/日历和31字节的静态RAM。它经过一个简单的串行接口与微处理器通信。实时时钟/日历提供秒、分、时、日、周、月和年等信息。对于小于31天的月,月末的日期自动进行调整,还包括了闰年校正的功能。时钟的运行可以采用24小时或带AM(上午)/PM(下午)的12小时格式。使用同步串行通信,简化了DS1302与微处理器的通信。与时钟/RAM通信仅需三根线:(1)RST(复位)、(2)I/O(数据线)、和(3)SCLK(串行时钟)。数据可以以每次一个字节或多达31字节的多字节形式传送至时钟/RAM或从其中送出。DS1302设计成能在非常低的功耗下工作,消耗小于1微瓦的功率便能保存数据和时钟信息。

DS1302是DS1202的升级产品,除了DS1202基本的慢速充电功能外,DS1302具有的其它特点包括:用于主电源和备份电源的双电源引脚,可编程的VCC1慢速充电器以及7个附加字节的高速暂存存储器(scratchpad memory)。

(1)、工作原理

串行时钟芯片的主要组成部分示于图1:移位寄存器、控制逻辑、振荡器、实时时钟以及RAM。

(2)、信号说明

①VCC1:VCC1在单电源与电池供电的系统中提供低电源并提供低功率的电池备份。通过连接这个引脚对系统实时充电。

②VCC2:VCC2在双电源系统中提供主电源,在这种运用方式中VCC1连接到备份电源,以便在没有主电源的情况下能保存时间信息以及数据。

③DS1302由VCC1或VCC2两者中较大者供电。当VCC2大于VCC1+0.2V时,VCC2给DS1302供电。当VCC2小于VCC1时,DS1302由VCC1供电。

④时钟(串行时钟输入) -时钟用于同步数据移动的串行接口。

⑤I/O(数据输入/输出)-对I/O引脚是双向数据引脚的3线接口。

⑥复位(复位) -复位信号必须在高电平读取或写入。

⑦X1,X2:连接为一个标准的32.768 kHz的石英晶体。所选用晶振规定的负载电容量应当为6pF。(3)、命令字节

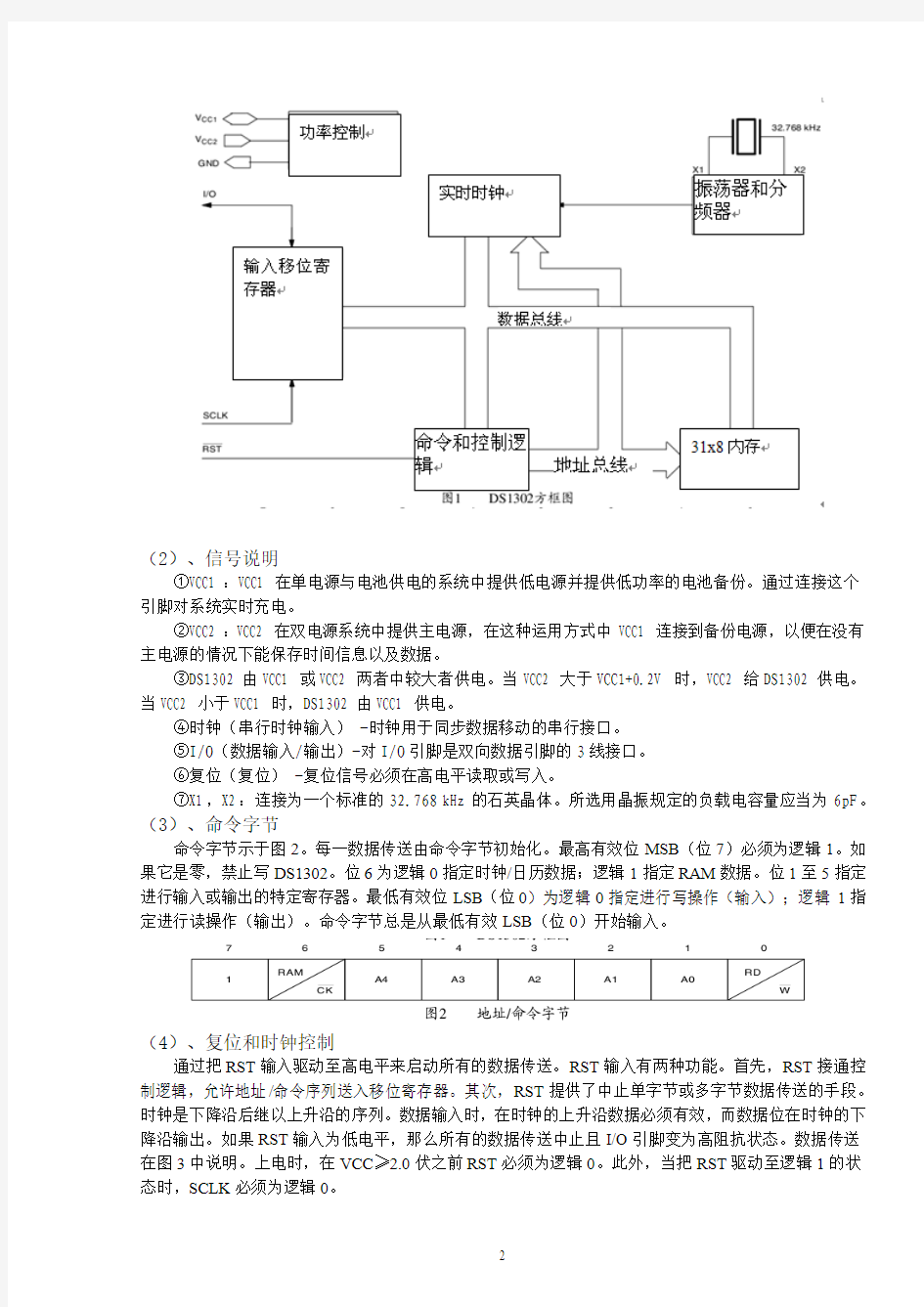

命令字节示于图2。每一数据传送由命令字节初始化。最高有效位MSB(位7)必须为逻辑1。如果它是零,禁止写DS1302。位6为逻辑0指定时钟/日历数据;逻辑1指定RAM数据。位1至5指定进行输入或输出的特定寄存器。最低有效位LSB(位0)为逻辑0指定进行写操作(输入);逻辑1指定进行读操作(输出)。命令字节总是从最低有效LSB(位0)开始输入。

(4)、复位和时钟控制

通过把RST输入驱动至高电平来启动所有的数据传送。RST输入有两种功能。首先,RST接通控制逻辑,允许地址/命令序列送入移位寄存器。其次,RST提供了中止单字节或多字节数据传送的手段。时钟是下降沿后继以上升沿的序列。数据输入时,在时钟的上升沿数据必须有效,而数据位在时钟的下降沿输出。如果RST输入为低电平,那么所有的数据传送中止且I/O引脚变为高阻抗状态。数据传送在图3中说明。上电时,在VCC≥2.0伏之前RST必须为逻辑0。此外,当把RST驱动至逻辑1的状态时,SCLK必须为逻辑0。

图3数据传输概要

(5)数据输入

跟随在输入写命令字节的8个SCLK周期之后,在下8个SCLK周期的上升沿输入数据字节。如果有额外的SCLK周期,它们将被忽略。数据从位0开始输入。

(6)数据输出

跟随在输入读命令字节的8个SCLK周期之后,在下8个SCLK周期的下降沿输出数据字节。注意,被传送的第一个数据位发生在写命令字节的最后一位之后的第一个下降沿。只要RST保持为高电平,如果有额外的SCLK周期,它们将重新发送数据字节。这一操作使之具有连续的多字节方式的读能力。另外,在SCLK的每一上升沿,I/O引脚为三态。数据从位0开始输出。

(7)、多字节方式

通过对地址31(十进制)寻址(地址/命令位1至5=逻辑1),可以把时钟/日历或RAM寄存器规定为多字节(burst)方式。如前所述,位6规定时钟或RAM而位0规定读或写。在时钟/日历寄存器中的地址9至31或RAM寄存器中的地址31不能存储数据。在多字节方式中读或写从地址0的位0开始。与使用DS1202时一样,当以多字节方式写时钟寄存器时,必须按数据传送的次序写最先8个寄存器。但是,当以多字节方式写RAM时,为了传送数据不必写所有31个字节。不管是否写了全部31个字节,所写的每一个字节都将传送至RAM。

(8)、时钟/日历

如图4所示,时钟/日历包含在7个写/读寄存器内。包含在时钟/日历寄存器内的数据是二——十进制(BCD)码。

(9)、时钟暂停

秒寄存器的位7定义为时钟暂停位。当此位设置为逻辑1时,时钟振荡器停止,DS1302被置入低功率的备份方式,其电源消耗小于100毫微安(nanoamp)。当把此位写成逻辑0时,时钟将启动。(10)、AM-PM/12-24方式

小时寄存器的位7定义为12或24小时方式选择位。当它为高电平时,选择12小时方式。在12小时方式下,位5是AM/PM位,此位为逻辑高电平表示PM。在24小时方式下,位5是第2个10小时位(20-23时)。

(11)、写保护寄存器

写保护寄存器的位7是写保护位。开始7位(位0-6)置为零,在读操作时总是读出零。在对时钟或RAM进行写操作之前,位7必须为零。当它为高电平时,写保护位防止对任何其它寄存器进行写操作。

(12)、慢速充电(Trickle charge)寄存器

这个寄存器控制DS1302的慢速充电特性。图5的简化电路表示慢速充电器的基本组成。慢速充电选择(TCS)位(位4-7)控制慢速充电器的选择。为了防止偶然的因素使之工作,只有1010模式才能使慢速充电器工作,所有其它的模式将禁止慢速充电器。DS1302上电时,慢速充电器被禁止。二极管选择(DS)位(位2-3)选择是一个二极管还是两个二极管连接在VCC2与VCC1之间。如果DS为01,那么选择一个二极管;如果DS为10,则选择两个二极管。如果DS为00或11,那么充电器被禁止,与TCS无关。RS位(位0-1)选择连接在VCC2与VCC1之间的电阻。电阻选择(RS)位选择的电阻如下:

如果RS为00,充电器被禁止,与TCS无关。

二极管和电阻的选择由用户根据电池或超容量电容充电所需的最大电流决定。最大充电电流可以如下列所说明的那样进行计算。假定5V系统电源加到VCC2而超容量电容接至VCC1。再假设慢速充电器工作时在VCC2和VCC1之间接有一个二极管和电阻R1。因而最大电流可计算如下:

Imax=(5.0V-二极管压降)/R1

~(5.0V-0.7V)/2kΩ

~2.2mA

显而易见,当超容量电容充电时,VCC2和VCC1之间的电压减少,因而充电电流将会减小。(13)、时钟/日历多字节(Burst)方式

时钟/日历命令字节可规定多字节工作方式。在此方式下,最先8个时钟/日历寄存器可以从地址0的第0位开始连续地读或写(见图4)。当指定写时钟/日历的多字节方式时,如果写保护位设置为高电平,那么没有数据会传送到8个时钟/日历寄存器(包括控制寄存器)的任一个。在多字节方式下,慢速充电器是不可访问的。

(14)、RAM

静态RAM是RAM地址空间中顺序寻址的31×8字节。

(15)、RAM多字节方式

RAM命令字节可规定多字节工作方式。在此方式下,可以从地址0的第0位开始顺序读或写31 RAM 寄存器(见图4)。

(16)、寄存器概要

寄存器数据格式概要示于图4。

(17)、晶振选择

32.768kHz的晶振(诸如Daiwa公司的DT26S、Seiko公司的DS-VT-200或其他类似产品)可通过引脚2和3(X1,X2)直接连接至DS1302。所选用晶振规定的负载电容量(CL)应当为6pF。晶振可从Dallas半导体公司订购。订购器件号是DS9032。

五、极限参数*

任何引脚相对于地的电压–0.5V至+7.0V

运用温度0℃至70℃

贮存温度–55℃至+125℃

焊接温度260℃,10秒

* 强度超出所列的极限参数可能导致器件的永久性损坏。这些仅仅是极限参数,并不意味着在极限条件下或在任何其它超出推荐工作条件所示参数的情况下器件能有效地工作。延长在极限参数条件下的工作时间会影响器件的可靠性。

六、推荐的直流运用条件

七、直流电特性

八、电容

(T A=25℃)

九、交流电特性

(除非另有说明,0℃至70℃;V CC=2.0V至5.5V)

十、时序图

十一、注意:

1. 所有电压以地为参考点。

2. 对于电容性负载,提供电流1mAVCC=5V和0.4mA、VCC=2.5V、VOH=VCC条件下规定逻辑1的电压。

3. 对于电容性负载,在吸收电流4mA、VCC=5V和1.5mA、VCC=2.5V、VOL=地的条件下规定逻辑0的电压。

4. 在I/O开路、RST设置为逻辑0、时钟暂停标志=0(允许振荡器工作)条件下规定ICC1T和ICC2T。

5. 在I/O引脚开路、RST设置为高电平、VCC=5V时SCLK=2MHz;VCC=2.5V时SCLK= 500kHz以及时钟暂停标志=0(允许振荡器工作)的条件下规定ICC1A和ICC2A。

6. RST、SCLK和I/O均接有40kΩ下拉电阻至地。

7. 在VIH=2.0V或VIL=0.8V以及最大为10ms上升和下降时间条件下测量。

8. 在VOH=2.4V或VOL=0.4V条件下测量。

9. 负载电容=50pF。

10. 在RST、I/O和SCLK开路条件下规定ICC1S和ICC2S。时钟暂停标志必须设置为逻辑1(禁止振荡器工作)。

11. 当VCC2>VCC1+0.2V时,VCC=VCC2;当VCC1>VCC2时,VCC=VCC1。

12. VCC2=0伏。

13. VCC1=0伏。

14. 典型值为25℃时的数值。

DS1302 Trickle Charge Timekeeping Chip

一、FEATURES

1、Real time clock counts seconds, minutes hours, date of the month, month, day of the week, and year with leap year compensation valid up to 2100.

2、31 x 8 RAM for scratchpad data storage.

3、Serial I/O for minimum pin count.

4、2.0–5.5V full operation.

5、Uses less than 300 nA at 2.0V.

6、Single–byte or multiple–byte (burst mode) data transfer for read or write of clock or RAM data.

7、8–pin DIP or optional 8–pin SOICs for surface mount.

8、Simple 3–wire interface.

9、TTL–compatible (VCC = 5V).

10、Optional industrial temperature range –40°C to +85°C.

11、DS1202 compatible.

二、PIN ASSIGNMENT

三、PIN DESCRIPTION

①X1, X2:32.768 kHz Crystal Pins;②GND:Ground;③RST:Reset;④I/O:Data Input/Output;

⑤SCLK:Serial Clock;⑥VCC1, VCC2:Power Supply Pins

四、DESCRIPTION

The DS1302 Trickle Charge Timekeeping Chip contains a real time clock/calendar and 31 bytes of static RAM. It communicates with a microprocessor via a simple serial interface. The real time clock/calendar provides seconds, minutes, hours, day, date, month, and year information. The end of the month date is automatically adjusted for months with less than 31 days, including corrections for leap year. The clock operates in either the 24–hour or 12–hour format with an AM/PM indicator. Interfacing the DS1302 with a microprocessor is simplified by using synchronous serial communication. Only three wires are required to communicate with the clock/RAM: (1) RST(Reset), (2) I/O (Data line), and (3) SCLK (Serial clock). Data can be transferred to and from the clock/RAM 1 byte at a time or in a burst of up to 31 bytes. The DS1302 is designed to operate on very low power and retain data and clock information on less than 1 microwatt.

The DS1302 is the successor to the DS1202. In addition to the basic timekeeping functions of the DS1202, the DS1302 has the additional features of dual power pins for primary and back–up power supplies, programmable trickle charger for VCC1, and seven additional bytes of scratchpad memory.

(1)、OPERATION

The main elements of the Serial Timekeeper are shown in Figure 1: shift register, control logic, oscillator,real time clock, and RAM.

DS1302 BLOCK DIAGRAM Figure 1

(2)、SIGNAL DESCRIPTIONS

①VCC1:VCC1 provides low power operation in single supply and battery operated systems as well as low power battery backup. In systems using the trickle charger, the rechargeable energy source is connected to this pin.

②VCC2 :Vcc2 is the primary power supply pin in a dual supply configuration. VCC1 is connected to a backup source to maintain the time and date in the absence of primary power.

③The DS1302 will operate from the larger of VCC1 or VCC2. When VCC2 is greater than VCC1 + 0.2V, VCC2 will power the DS1302. When VCC2 is less than VCC1, VCC1 will power the DS1302.

④SCLK (Serial Clock Input) – SCLK is used to synchronize data movement on the serial interface.

⑤I/O (Data Input/Output) – The I/O pin is the bi-directional data pin for the 3-wire interface.

⑥RST (Reset) – The reset signal must be asserted high during a read or a write.

⑦X1, X2 :Connections for a standard 32.768 kHz quartz crystal. The internal oscillator is designed for operation with a crystal having a specified load capacitance of 6 pF.

(3)、COMMAND BYTE

The command byte is shown in Figure 2. Each data transfer is initiated by a command byte. The MSB (Bit 7) must be a logic 1. If it is 0, writes to the DS1302 will be disabled. Bit 6 specifies clock/calendar data if logic 0 or RAM data if logic 1. Bits 1 through 5 specify the designated registers to be input or output, and the LSB (bit 0) specifies a write operation (input) if logic 0 or read operation (output) if logic 1. The command byte is always input starting with the LSB (bit 0).

ADDRESS/COMMAND BYTE Figure 2

(4)、RESET AND CLOCK CONTROL

All data transfers are initiated by driving the RST input high. The RST input serves two functions. First, RST turns on the control logic which allows access to the shift register for the address/command sequence. Second, the RST signal provides a method of terminating either single byte or multiple byte data transfer. A clock cycle is a sequence of a falling edge followed by a rising edge. For data inputs, data must be valid during the rising edge of the clock and data bits are output on the falling edge of clock. If the RST input is low all data transfer terminates and the I/O pin goes to a high impedance state. Data transfer is illustrated in Figure 3. At power–up, RST must be a logic 0 until V CC> 2.0 volts. Also SCLK must be at a logic 0 when RST is driven to a logic 1 state.

DATA TRANSFER SUMMARY Figure 3

(5)、DATA INPUT

Following the eight SCLK cycles that input a write command byte, a data byte is input on the rising edge of the next eight SCLK cycles. Additional SCLK cycles are ignored should they inadvertently occur. Data is input starting with bit 0.

(6)、DATA OUTPUT

Following the eight SCLK cycles that input a read command byte, a data byte is output on the falling edge of the next eight SCLK cycles. Note that the first data bit to be transmitted occurs on the first falling edge after the last bit of the command byte is written. Additional SCLK cycles retransmit the data bytes should they inadvertently occur so long as RST remains high. This operation permits continuous burst mode read capability. Also, the I/O pin is tri–stated upon each rising edge of SCLK. Data is output starting with bit 0.

(7)、BURST MODE

Burst mode may be specified for either the clock/calendar or the RAM registers by addressing location 31 decimal (address/command bits 1 through 5 = logic 1). As before, bit 6 specifies clock or RAM and bit 0 specifies read or write. There is no data storage capacity at locations 9 through 31 in the Clock/Calendar Registers or location 31 in the RAM registers. Reads or writes in burst mode start with bit 0 of address 0.When writing to the clock registers in

the burst mode, the first eight registers must be written in order for the data to be transferred. However, when writing to RAM in burst mode it is not necessary to write all 31 bytes for the data to transfer. Each byte that is written to will be transferred to RAM regardless of whether all 31 bytes are written or not.

(8)、CLOCK/CALENDAR

The clock/calendar is contained in seven write/read registers as shown in Figure 4. Data contained in the clock/ calendar registers is in binary coded decimal format (BCD). REGISTER ADDRESS/DEFINITION Figure 4:

(9)、CLOCK HALT FLAG

Bit 7 of the seconds register is defined as the clock halt flag. When this bit is set to logic 1, the clock oscillator is stopped and the DS1302 is placed into a low–power standby mode with a current drain of less than 100 nanoamps. When this bit is written to logic 0, the clock will start. The initial power on state is not defined.

(10)、AM-PM/12-24 MODE

Bit 7 of the hours register is defined as the 12– or 24–hour mode select bit. When high, the 12–hour mode is selected. In the 12–hour mode, bit 5 is the AM/PM bit with logic high being PM. In the 24–hour mode, bit 5 is the second 10-hour bit (20 – 23 hours).

(11)、WRITE PROTECT BIT

Bit 7 of the control register is the write-protect bit. The first seven bits (bits 0 –6) are forced to 0 and will always read a 0 when read. Before any write operation to the clock or RAM, bit 7 must be 0. When high, the write protect bit prevents a write operation to any other register. The initial power on state is not defined. Therefore the WP bit should be cleared before attempting to write to the device.

(12)、TRICKLE CHARGE REGISTER

This register controls the trickle charge characteristics of the DS1302. The simplified schematic of Figure 5 shows the basic components of the trickle charger. The trickle charge select (TCS) bits (bits 4 -7) control the selection of the trickle charger. In order to prevent accidental enabling, only a pattern of 1010 will enable the trickle charger. All other patterns will disable the trickle charger. The DS1302 powers up with the trickle charger disabled. The diode select (DS) bits (bits 2 – 3) select whether one diode or two diodes are connected between V CC2 and V CC1. If DS is 01, one diode is selected or if DS is 10, two diodes are selected. If DS is 00 or 11, the trickle charger is disabled independently of TCS. The RS bits (bits 0 -1) select the resistor that is connected between V CC2 and V CC1. The resistor selected by the resistor select (RS) bits is as follows.

If RS is 00, the trickle charger is disabled independently of TCS.

Diode and resistor selection is determined by the user according to the maximum current desired for battery or super cap charging. The maximum charging current can be calculated as illustrated in the following example. Assume that a system power supply of 5 volt is applied to V CC2 and a super cap is connected to V CC1. Also assume that the trickle charger has been enabled with one diode and resistor R1 between V CC2 and V CC1. The maximum current I max would therefore be calculated as follows:

I max = (5.0V – diode drop) / R1

~ (5.0V – 0.7V) / 2 k?

~ 2.2 Ma

Obviously, as the super cap charges, the voltage drop between V CC2 and V CC1 will decrease and thereforethe charge current will decrease.

(13)、CLOCK/CALENDAR BURST MODE

The clock/calendar command byte specifies burst mode operation. In this mode the first eight clock/calendar registers can be consecutively read or written (see Figure 4) starting with bit 0 of address 0. If the write protect bit is set high when a write clock/calendar burst mode is specified, no data transfer will occur to any of the eight clock/calendar registers (this includes the control register). The trickle charger is not accessible in burst mode. At the beginning of a clock burst read, the current time is transferred to a second set of registers. The time information is read from these secondary registers, while the clock may continue to run. This eliminates the need to re-read the registers in case of an update of the main registers during a read.

(14)、RAM

The static RAM is 31 x 8 bytes addressed consecutively in the RAM address space. (15)、RAM BURST MODE

The RAM command byte specifies burst mode operation. In this mode, the 31 RAM registers can be consecutively read or written (see Figure 4) starting with bit 0 of address 0.

(16)、REGISTER SUMMARY

A register data format summary is shown in Figure 4.

(17)、CRYSTAL SELECTION

A 32.768 kHz crystal can be directly connected to the DS1302 via X1 and X2. The crystal selected for use should have a specified load capacitance (CL) of 6 pF. For more information on crystal selection and crys tal layout consideration, please consult Application Note 58, “Crystal Considerations with Dallas Real Time Clocks."

五、ABSOLUTE MAXIMUM RATINGS*

Voltage on Any Pin Relative to Ground –0.5V to +7.0V

Operating Temperature 0°C to 70°C or - 40?C to +85?C for industrial Storage Temperature –55°C to +125°C

Soldering Temperature 260°C for 10 seconds (DIP)

*This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operation sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods of time may affect reliability.

六、RECOMMENDED DC OPERATING CONDITIONS

七、DC ELECTRICAL CHARACTERISTICS

八、CAPACITANCE

(t A= 25oC)

九、AC ELECTRICAL CHARACTERISTICS

十、TIMING DIAGRAM: READ DATA TRANSFER Figure 5

TIMING DIAGRAM: WRITE DATA TRANSFER Figure 6

十一、NOTES:

1.All voltages are referenced to ground.

2.Logic one voltages are specified at a source current of 1 mA at V CC=5V and 0.4 mA at

V CC=2.0V,V OH=V CC for capacitive loads.

3.Logic zero voltages are specified at a sink current of 4 mA at V CC=5V and 1.5 mA at

V CC=2.0V,V OL=GND for capacitive loads.

4.I CC1T and I CC2T are specified with I/O open, RST set to a logic “0”, and clock halt flag=0 (oscillator enabled).

5.I CC1A and I CC2A are specified with the I/O pin open, RST high, SCLK=2 MHz at

V CC=5V;SCLK=500 kHz, V CC=2.0V and clock halt flag=0 (oscillator enabled).

6.RST, SCLK, and I/O all have 40 k? pull–down resistors to ground.

7.Measured at V IH=2.0V or V IL=0.8V and 10 ns maximum rise and fall time.

8.Measured at V OH=2.4V or V OL=0.4V.

9.Load capacitance = 50 pF.

10.I CC1S and I CC2S are specified with RST, I/O, and SCLK open. The clock halt flag must be set to logic one (oscillator disabled).

11.V CC=V CC2, when V CC2>V CC1 +0.2V; V CC=V CC1, when V CC1>V CC2.

12.V CC2=0V.

13.V CC1=0V.

14. Typical values are at 25°C.

DS1302时钟芯片读写详解 2008-09-26 13:07 /*DS1302读写程序(C51)*/ sbit DS13CLK =P1^5; /*DS1302的SCLK脚脉冲*/ sbit DS13IO =P1^6; /*DS1302的IO脚数据*/ sbit DS13CS =P1^7; /*DS1302的RST脚片选*/ /*向DS1302写一个字节*/ void _wds13byte(uchar _code) { uchar i; DS13CLK =0; DS13CLK =0; for(i=0;i<8;i++) { if(_code&0x01) DS13IO =1; else DS13IO =0; DS13CLK =1; DS13CLK =1; DS13CLK =0; DS13CLK =0; _code =_code >> 1; } } /*从DS1302读一个字节*/ uchar _rds13byte(void) { uchar i,_code; _code=0; DS13CLK =0; DS13CLK =0; DS13IO =1; for(i=0;i<8;i++) { _code =_code >>1; if(DS13IO) _code =_code|0x80; DS13CLK =1; DS13CLK =1; DS13CLK =0; DS13CLK =0; } return _code; } /*读功能_code读功能命令*/ uchar readds1302(uchar _code)

{ DS13CS =0; /*关闭DS1302*/ DS13CLK =0; DS13CLK =0; DS13CS =1; /*使能DS1302*/ _wds13byte(_code); /*读代码*/ _code=_rds13byte(); /*返回读取数字*/ DS13CLK =1; DS13CS =0; /*关闭DS1302*/ return _code; } /*写功能fp写的地址,_code写的内容*/ void writeds1302(uchar fp,uchar _code) { DS13CS =0; /*关闭DS1302*/ DS13CLK =0; DS13CLK =0; DS13CS =1; /*使能DS1302*/ _wds13byte(fp); /*写控制命令*/ _wds13byte(_code); /*写入数据*/ DS13CLK=1; DS13CS =0; /*关闭DS1302*/ } /*******DS1302设置快速充电***************/ void ds13_charg(void) { writeds1302(0x8e,0x00); /*解除写保护*/ writeds1302(0x90,0xa5); /*单二极管2K电阻充电*/ writeds1302(0x8e,0x80); /*置位写保护*/ } ;;;DS1302读写程序(汇编);;; ;******************************************************************* **/ T_CLK Bit P1.5 ;实时时钟时钟线引脚 T_IO Bit P1.6 ;实时时钟数据线引脚 T_RST Bit P1.7 ;实时时钟复位线引脚 ;********************************************************** ;子程序名:Set1302 ;功能:设置DS1302 初始时间,并启动计时。 ;说明: ;调用:RTInputByte ;入口参数:初始时间在:Second,Minute,Hour,Day,Month,Week.YearL(地址连续) ;出口参数:无 ;影响资源:A B R0 R1 R4 R7

单片机玩到此时,很想玩TFT真彩屏,但如果不玩一玩汉显字符液晶屏,就总觉得少了些什么,说实话,我对时钟制作并不很感兴趣,因为家里走针的、蹦字的计时器、定时器大小有七八个,还不算手机和电脑的时钟,而要想玩汉显屏,则做时钟算是最合适的了,也难怪杜洋老师会在这上下功夫,毕竟没有那家公司会让咱初学者去搞工控或商品。前些时,在网上淘了一只LCD-12864模块,已经点亮并通过了简单的测试,准备做杜洋的时钟,准备技术资料时,在网上找到了一篇关于时钟芯片DS1302的应用文章,觉得不错,转帖于此以资共享。 时钟芯片DS1302可靠起振的方法 作者:不详出处:不详 DS1302是Dallas公司生产的一种实时时钟芯片。它通过串行方式与单片机进行数据传送,能够向单片机提供包括秒、分、时、日、月、年等在内的实时时间信息,并可对月末日期、闰年天数自动进行调整;它还拥有用于主电源和备份电源的双电源引脚,在主电源关闭的情况下,也能保持时钟的连续运行。另外,它还能提供31字节的用于高速数据暂存的RAM。鉴于上述特点,DS1302已在许多单片机系统中得到应用,为系统提供所需的实时时钟信息。 一、 DS1302的主要特性 1. 引脚排列 图1 DS1302引脚排列图(见附图) DS1302的引脚排列如图1所示,各引脚的功能如下: X1,X2——32768Hz晶振引脚端; RST——复位端; I/O——数据输入/输出端; SCLK——串行时钟端; GND——地; VCC2,VCC1——主电源与后备电源引脚端。 2. 主要功能: DS1302时钟芯片内主要包括移位寄存器、控制逻辑电路、振荡器、实时时钟电路以及用于高速暂存的31字节RAM。DS1302与单片机系统的数据传送依靠RST,I/O,SCLK三根端线即可完成。其工作过程可概括为:首先系统RST引脚驱动至高电平,然后在作用于SCLK时钟脉冲的作用下,通过I/O引脚向DS1302输入地址/命令字节,随后再在SCLK时钟脉冲的配合下,从I/O引脚写入或读出相应的数据字节。因此,其与单片机之间的数据传送是十分容易实现的。 二、时钟的产生及存在的问题 (1) 在实际使用中,我们发现DS1302的工作情况不够稳定,主要表现在实时时间的传送有时会出现误差,有时甚至整个芯片停止工作。我们对DS1302的工作电路进行了分析,其与单片机系统的连接如图2所示。从图中可以看出,DS1302的外部电路十分简单,惟一外接的元件是32768Hz 的晶振。通过实验我们发现:当外接晶振电路振荡时,DS1302计时正确;当外接晶振电路停振时,DS1302计时停止。因此,我们认为32768Hz晶振是造成DS1302工作不稳定的主要原因。 图2 DS1302与单片机系统的连接图(见附图) (2) DS1302时钟的产生基于外接的晶体振荡器,振荡器的频率为32768Hz。该晶振通过引脚X1、X2直接连接至DS1302,即DS1302是依靠外部晶振与其内部的电容配合来产生时钟脉冲的。

DS1302 时钟芯片的原理与应用 1 写保护寄存器操作 当写保护寄存器的最高位为0 时,允许数据写入寄存器,写保护寄存器可以通过命令字节8E 8F 来规定禁止写入/读出。写保护位不能在多字节传送模式下写入Write_Enable: MOV Command,#8Eh ;命令字节为8E MOV ByteCnt,#1 ;单字节传送模式 MOV R0,#XmtDat 数据地址覆给R0 MOV XmtDat,#00h 数据内容为0 写入允许 ACALL Send_Byte 调用写入数据子程序 RET 返回调用本子程序处 当写保护寄存器的最高位为1 时禁止数据写入寄存器 Write_Disable: MOV Command,#8Eh ;命令字节为8E MOV ByteCnt,#1 ;单字节传送模式 MOV R0,#XmtDat 数据地址覆给R0 MOV XmtDat,#80h 数据内容为80h 禁止写入 ACALL Send_Byte 调用写入数据子程序 RET 返回调用本子程序处 以上程序调用了基本数据发送(Send_Byte)模块及一些内存单元定义, 其源程序清单在附录中给出下面 的程序亦使用了这个模块 2 时钟停止位操作 当把秒寄存器的第7 位时钟停止位设置为0 时起动时钟开始 Osc_Enable: MOV Command,#80h ; 命令字节为80 MOV ByteCnt,#1 ; 单字节传送模式 MOV R0,#XmtDat 数据地址覆给R0 MOV XmtDat,#00h 数据内容为0 振荡器工作允许 ACALL Send_Byte 调用写入数据子程序 RET 返回调用本子程序处 当把秒寄存器的第7 位时钟停止位设置为1 时,时钟振荡器停止DS1320 进入低功耗方式 Osc_Disable: MOV Command,#80h ;命令字节为80 MOV ByteCnt,#1 ;单字节传送模式 MOV R0,#XmtDat 数据地址覆给R0 MOV XmtDat,#80h 数据内容为80h 振荡器停止 ACALL Send_Byte 调用写入数据子程序 RET 返回调用本子程序处 3. 多字节传送方式

单片机原理课程设计 课题名称:基于DS1302的数码管显示数字钟 专业班级:电子信息工程 学生学号: 学生姓名: 指导教师: 设计时间:2010年6月21日--2010年6月25日

目录 摘要........................................................................................................................................................................ 1 设计任务和要求............................................................................................................................................ 2 方案论证........................................................................................................................................................ 3 系统硬件设计................................................................................................................................................ 3.1 系统总原理图 ................................................................................................................................ 3.2 元器件清单...................................................................................................................................... 3.3 PCB板图....................................................................................................................................... 3.4 Proteus仿真图 ............................................................................................................................... 3.5 分电路图及原理说明................................................................................................................... 3.5.1 主控部分(单片机MCS-51).............................................................................. 3.5.2 计时部分(实时时钟芯片DS1302).................................................................. 3.5.3 显示部分(共阳极数码管)................................................................................ 3.5.4 调时部分(按键)................................................................................................ 4系统软件设计................................................................................................................................................ 4.1 程序流程图..................................................................................................................................... 4.2 程序源代码........................................................................................................................................ 5心得体会........................................................................................................................................................ 6参考文献........................................................................................................................................................ 7结束语............................................................................................................................................................

目录 摘要 一、引言 (1) 二、基于单片机的电子时钟硬件选择分析 (2) 2.1主要IC芯片选择 (2) 2.1.1微处理器选择 (2) 2.1.2 DS1302简介 (4) 2.1.3 DS1302引脚说明 (4) 2.2电子时钟硬件电路设计 (5) 2.2.1时钟电路设计 (6) 2.2.2整点报时功能 (7) 三、Protel软件画原理图 (8) 3.1系统工作流程图 (8) 3.2原理图 (9) 四、proteus软件仿真及调试 (9) 4.1电路板的仿真 (9) 4.2软件调试 (9) 五、源程序 (10) 六、课设心得 (13) 七、参考文献 (13)

基于单片机电子时钟设计 摘要 电子时钟主要是利用电子技术将时钟电子化、数字化,拥有时钟精确、体积小、界面友好、可扩展性能强等特点,被广泛应用于生活和工作当中。另外,在生活和工农业生产中,也常常需要温度,这就需要电子时钟具有多功能性。 本设计主要为实现一款可正常显示时钟/日历、带有定时闹铃的多功能电子时钟。 本文对当前电子钟开发手段进行了比较和分析,最终确定了采用单片机技术实现多功能电子时钟。本设计应用AT89C52芯片作为核心,6位LED数码管显示,使用DS1302实时时钟日历芯片完成时钟/日历的基本功能。这种实现方法的优点是电路简单,性能可靠,实时性好,时间精确,操作简单,编程容易。 该电子时钟可以应用于一般的生活和工作中,也可通过改装,提高性能,增加新功能,从而给人们的生活和工作带来更多的方便。 关键词:电子时钟;多功能;AT89C52;时钟日历芯片

一、引言 时间是人类生活必不可少的重要元素,如果没有时间的概念,社会将不会有所发展和进步。从古代的水漏、十二天干地支,到后来的机械钟表以及当今的石英钟,都充分显现出了时间的重要,同时也代表着科技的进步。致力于计时器的研究和充分发挥时钟的作用,将有着重要的意义。 1.1 多功能电子时钟研究的背景和意义 20世纪末,电子技术获得了飞速的发展。在其推动下,现代电子产品几乎渗透到了社会的各个领域,有力的推动和提高了社会生产力的发展与信息化程度,同时也使现代电子产品性能进一步提升,产品更新换代的节奏也越来越快。 时间对人们来说总是那么宝贵,工作的忙碌性和繁杂容易使人忘记当前的时间。然而遇到重大事情的时候,一旦忘记时间,就会给自己或他人造成很大麻烦。平时我们要求上班准时,约会或召开会议必然要提及时间;火车要准点到达,航班要准点起飞;工业生产中,很多环节都需要用时间来确定工序替换时刻。所以说能随时准确的知道时间并利用时间,是我们生活和工作中必不可少的[1]。 电子钟是采用电子电路实现对时、分、秒进行数字显示的计时装臵,广泛应用于个人家庭,车站,码头办公室等公共场所,成为人们日常生活中不可少的必需品。由于数字集成电路的发展和石英晶体振荡器的广泛应用,使得数字钟的精度,远远超过老式钟表,钟表的数字化给人们生产生活带来了极大的方便,而且大大地扩展了钟表原先的报时功能。诸如定时自动报警、0按时自动打铃、定时广播、自动起闭路灯、定时开关烘箱、通断动力设备、甚至各种定时电气的自动启用等,所有这些,都是以钟表数字化为基础的。因此,研究数字钟及扩大其应用,有着非常现实的意义。

DS1302 DS1302是美国DALLAS公司推出的一种高性能、低功耗的实时时钟芯片,附加31字节静态RAM,采用SPI三线接口与CPU进行同步通信,并可采用突发方式一次传送多个字节的时钟信号和RAM数据。实时时钟可提供秒、分、时、日、星期、月和年,一个月小与31天时可以自动调整,且具有闰年补偿功能。工作电压宽达2.5~5.5V。采用双电源供电(主电源和备用电源),可设置备用电源充电方式,提供了对后背电源进行涓细电流充电的能力。 下面是标准的接线电路图:

DS1302有关日历、时间的寄存器共有12个,其中有7个寄存器(读时81h~8Dh,写时80h~8Ch)是存放秒、分,小时、日、月、年、周数据的,存放的数据格式为BCD码形式 它的部时间寄存器如下: 将初始设置的时间、日期数据写入这几个寄存器,然后再不断地读取这几个寄存器来获取实时时间和日期。这几个寄存器的说明如下: 1、秒寄存器(81h、80h)的位7定义为时钟暂停标志(CH)。当初始上电时该位置为1,时钟振荡器停止,DS1302处于低功耗状态;只有将秒寄存器的该位置改写为0时,时钟才能开始运行。 2、控制寄存器(8Fh、8Eh)的位7是写保护位(WP),其它7位均置为0。在任何的对时钟和RAM的写操作之前,WP位必须为0。当WP位为1时,写保护位防止对任一寄存器的写操作。也就是说在电路上电的初始态WP是1,这时是不能改写上面任何一个时间寄存器的,只有首先将WP改写为0,才能进行其它寄存器的写操作。 3、控制寄存器(8Fh、8Eh)的位7是写保护位(WP),其它7位均置为0。在任何的对时钟和RAM的写操作之前,WP位必须为0。当WP位为1时,写保护位防止对任一寄存器的写操作。也就是说在电路上电的初始态WP是1,这时是不能改写上面任何一个时间寄存器的,只有首先将WP改写为0,才能进行其它寄存器的写操作。 下面来说说如果对DS1302进行读写: 上面的电路图可以看出,除了电源和接地,DS1302只有三根线和单片机连接,SCLK、I/O 和RST(有的也写成CE),先看时序图:

学习情境2-可调式数字钟 之基于DS1302与数码管设计的可调数字钟 ☆点名,复习 1、定时器的工作方式有哪些?如何对定时器进行初始化。 2、数码管动态显示技术的原理? ☆新课讲授 2.2 基于DS1302与数码管设计的可调数字钟 前面我们用定时器产生1秒的时间,从而也设计出了可以调节数字钟,但用这种方法设计出来的电子钟不够准确。这节课我们用美国DALLAS公司推出的一种高性能、低功耗、带RAM的实时时钟电路DS1302 ,它可以对年、月、日、周日、时、分、秒进行计时,具有闰年补偿功能。同时,我们还是用数码管作为显示时间的硬件。 2.2.1 DS1302芯片技术资料 DS1302 是美国DALLAS公司推出的一种高性能、低功耗、带RAM的实时时钟电路,它可以对年、月、日、周日、时、分、秒进行计时,具有闰年补偿功能,工作电压为2.5V~5.5V。采用三线接口与CPU进行同步通信,并可采用突发方式一次传送多个字节的时钟信号或RAM 数据。DS1302内部有一个31×8的用于临时性存放数据的RAM寄存器。DS1302是DS1202的升级产品,与DS1202兼容,但增加了主电源/后背电源双电源引脚,同时提供了对后背电源进行涓细电流充电的能力。DS1302的外部引脚分配如图1所示及内部结构如图2所示。DS1302用于数据记录,特别是对某些具有特殊意义的数据点的记录上,能实现数据与出现该数据的时间同时记录,因此广泛应用于测量系统中。 图 1 DS1302引脚 图2 DS1302内部结构 1、引脚功能及结构

DS1302的引脚排列,其中Vcc1为后备电源,VCC2为主电源。在主电源关闭的情况下,也能保持时钟的连续运行。DS1302由Vcc1或Vcc2两者中的较大者供电。当Vcc2大于Vcc1+0.2V时,Vcc2给DS1302供电。当Vcc2小于Vcc1时,DS1302由Vcc1供电。X1和X2是振荡源,外接32.768kHz晶振。RST是复位/片选线,通过把RST输入驱动置高电平来启动所有的数据传送。RST输入有两种功能:首先,RST接通控制逻辑,允许地址/命令序列送入移位寄存器;其次,RST提供终止单字节或多字节数据的传送手段。当RST为高电平时,所有的数据传送被初始化,允许对DS1302进行操作。如果在传送过程中RST置为低电平,则会终止此次数据传送,I/O引脚变为高阻态。上电运行时,在Vcc≥2.5V之前,RST必须保持低电平。只有在SCLK为低电平时,才能将RST置为高电平。I/O为串行数据输入输出端(双向),SCLK 始终是输入端。 2 、DS1302的寄存器和控制命令 对DS1302的操作就是对其内部寄存器的操作,DS1302内部共有12个寄存器,其中有7个寄存器与日历、时钟相关,存放的数据位为BCD码形式。 小时寄存器(85h、84h)的位7用于定义DS1302是运行于12小时模式还是24小时模式。当为高时,选择12小时模式。在12小时模式时,位5是,当为1时,表示PM,当为0时,表示AM。在24小时模式时,位5是第二个10小时位。 秒寄存器(81h、80h)的位7定义为时钟暂停标志(CH)。当该位置为1时,时钟振荡器停止,DS1302处于低功耗状态;当该位置为0时,时钟开始运行。 控制寄存器(8Fh、8Eh)的位7是写保护位(WP),其它7位均置为0。在任何的对时钟和RAM的写操作之前,WP位必须为0。当WP位为1时,写保护位防止对任一寄存器的写操作。 日历、时间寄存器及控制字如表1所示: 此外,DS1302还有年份寄存器、控制寄存器、充电寄存器、时钟突发寄存器及与RAM相关的寄存器等。时钟突发寄存器可一次性顺序读写除充电寄存器以外的寄存器。DS1302内部的RAM分为两类,一类是单个RAM单元,共31个,每个单元为一个8位的字节,其命令控制字为COH~FDH,其中奇数为读操作,偶数为写操作;再一类为突发方式下的RAM,此方式下可一次性读写所有的RAM的31个字节,命令控制字为FEH(写)、FFH(读)。

实时时钟芯片DS1302的结构,工作原理及应用(含源程序) 1.ds1302实时时钟简介 现在流行的串行时钟电路很多,如DS1302、DS1307、PCF8485等。这些电路的接口简单、价格低廉、使用方便,被广泛地采用。本文介绍的实时时钟电路DS1302是DALLAS公司的一种具有涓细电流充电能力的电路,主要特点是采用串行数据传输,可为掉电保护电源提供可编程的充电功能,并且可以关闭充电功能。采用普通32.768kHz晶振。 2 DS1302的结构及工作原理 DS1302是美国DALLAS公司推出的一种高性能、低功耗、带RAM的实时时钟电路,它可以对年、月、日、周日、时、分、秒进行计时,具有闰年补偿功能,工作电压为2.5V~5.5V。采用三线接口与CPU进行同步通信,并可采用突发方式一次传送多个字节的时钟信号或RAM数据。DS1302内部有一个31×8的用于临时性存放数据的RAM寄存器。DS1302是DS1202的升级产品,与DS1202兼容,但增加了主电源/后背电源双电源引脚,同时提供了对后背电源进行涓细电流充电的能力。 2.1 引脚功能及结构 图1示出DS1302的引脚排列,其中Vcc1为后备电源,VCC2为主电源。在主电源关闭的情况下,也能保持时钟的连续运行。DS1302由Vcc1或Vcc2两者中的较大者供电。当Vcc2大于Vcc1+0.2V时,Vcc2给DS1302供电。当Vcc2小于Vcc1时,DS1302由Vcc1供电。X1和X2是振荡源,外接32.768kHz晶振。RST是复位/片选线,通过把RST输入驱动置高电平来启动所有的数据传送。RST输入有两种功能:首先,RST接通控制逻辑,允许地址/命令序列送入移位寄存器;其次,RST提供终止单字节或多字节数据的传送手段。当RST 为高电平时,所有的数据传送被初始化,允许对DS1302进行操作。如果在传送过程中RST 置为低电平,则会终止此次数据传送,I/O引脚变为高阻态。上电运行时,在Vcc≥2.5V之前,RST必须保持低电平。只有在SCLK为低电平时,才能将RST置为高电平。I/O为串行数据输入输出端(双向),后面有详细说明。SCLK始终是输入端。 2.2 DS1302的控制字节

关于实时时钟模块DS1302的介绍 DS1302是由美国DALLAS公司推出的具有涓细电流充电能力的低功耗实时时钟芯片。它可以对年、月、日、周、时、分、秒进行计时,且具有闰年补偿等多种功能。DS1302工作原理DS1302 工作电压为2.0V~5.5V。采用三线接口与CPU进行同步通信,并可采用突发方式一次传送多个字节的时钟信号或RAM数据。DS1302内部有一个318的用于临时性存放数据的RAM寄存器。DS1302是DS1202的升级产品,与DS1202兼容,但增加了主电源/后备电源双电源引脚,同时提供了对后备电源进行涓细电流充电的能力。DS1302主要性能指标DS1302实时时钟芯片广泛应用于电话、传真、便携式仪器等产品领域,他的主要性能指标如下: 1、DS1302是一个实时时钟芯片,可以提供秒、分、小时、日期、月、年等信息,并且还有软年自动调整的能力,可以通过配置AM/PM来决定采用24小时格式还是12小时格式。 2、拥有31字节数据存储RAM。 3、串行I/O通信方式,相对并行来说比较节省IO口的使用。 4、DS1302的工作电压比较宽,大概是2.0V~5.5V都可以正常工作。采用双电源供电,当主电源比备用电源高0.2V时,由主电源供电,否则采用备用电源,一般是一个纽扣电池。 5、DS1302这种时钟芯片功耗一般都很低,它在工作电压2.0V的时候,工作电流小于300nA。 6、DS1302共有8个引脚,有两种封装形式,一种是DIP-8封装,芯片宽度(不含引脚)是300mil,一种是SOP-8封装,有两种宽度,一种是150mil,一种是208mil。 DS1302引脚及定义这是单字节写入的时序图,可见,先拉高使能端,进行使能选择,然后在时钟上升沿写入一个字节。 DS1302在进行读写操作时最少读写两个字节,第一个是控制字节,就是一个命令,说明是读还是写操作,第二个时需要读写的数据。 对于单字节写,只有在SCLK为低电平时才能将CE 置高电平,所以刚开始将SCLK 置低,CE置高,然后把需要写入的字节送入IO口,然后跳变SCLK,在SCLK下降沿时,

早就已经不在学校了,可是前几天突然有老童学问我有没有保存这方面的资料,赶紧翻了一下我的电脑,呵呵,还是找到了一些资料,顺便共享出来,有需要的同学们拿走后留个言吧——可以的话。最后感谢无名的原作者。 DS1302的特点 DS1302是美国DALLAS公司推出的一种高性能、低功耗的实时时钟芯片,附加31字节静态RAM,采用SPI三线接口与CPU进行同步通信,并可采用突发方式一次传送多个字节的时钟信号和RAM数据。实时时钟可提供秒、分、时、日、星期、月和年,一个月小与31天时可以自动调整,且具有闰年补偿功能。工作电压宽达2.5~5.5V。采用双电源供电(主电源和备用电源),可设置备用电源充电方式,提供了对后背电源进行涓细电流充电的能力。DS1302的外部引脚分配如图1所示。DS1302用于数据记录,特别是对某些具有特殊意义的数据点的记录上,能实现数据与出现该数据的时间同时记录,因此广泛应用于测量系统中。 各引脚的功能 Vcc1:主电源;Vcc2:备份电源。当Vcc2>Vcc1+0.2V时,由Vcc2向DS1302供电,当Vcc2< Vcc1时,由Vcc1向DS1302供电。SCLK:串行时钟,输入;I/O:三线接口时的双向数据线;CE:输入信号,在读、写数据期间,必须为高。该引脚有两个功能:第一,CE开始控制字访问移位寄存器的控制逻辑;其次,CE提供结束单字节或多字节数据传输的方法。 DS1302的几组寄存器以及有关RAM的地址

(1)DS1302有关日历、时间的寄存器 DS1302有关日历、时间的寄存器共有12个,其中有7个寄存器(读时81h~8Dh,写时80h~8Ch),存放的数据格式为BCD码形式,如图3所示。 (2)小时寄存器(85h、84h)的位7用于定义DS1302是运行于12小时模式还是24小时模式。当为高时,选择12小时模式。在12小时模式时,位5是,当为1时,表示PM。在24小时模式时、位5是第二个10小时位。 (3)秒寄存器(81h、80h)的位7定义为时钟暂停标志(CH)。当该位置为1时,时钟振荡器止,DS1302处于低功耗状态;当该位置为0时,时钟开始运行。(4)控制寄存器(8Fh、8Eh)的位7是写保护位(WP),其它7位均置为0。在任何的对时钟和RAM的写操作之前,WP位必须为0。当WP位为1时,写保护位防止对任一寄存器的写操作。 (5)DS1302中附加31字节静态RAM的地址如图4所示。 (6)DS1302的工作模式寄存器 所谓突发模式是指一次传送多个字节的时钟信号和RAM数据。突发模式寄存器如图5所示

#include

代码: //1为功能键,2为增加时间键,3为减少时间键#include

for(i=0;i<8;i++) { io=date&0x01; sclk=1;sclk=0; date=date>>1; } } uchar read() //读一个字节 { uchar shuju,i; for(i=0;i<8;i++) { shuju=shuju>>1; sclk=0; if(io) shuju=shuju|0x80; sclk=1; } return shuju; } void writebyte(uchar add,date) //写时间的一个单位(分/秒/时/年/月/日/周){ rst=0;sclk=0;rst=1; write(0x8e); write(0x00);

随着人们生活水平的提高和生活节奏的加快,对时间的要求越来越高,精准数字计时的消费需求也是越来越多。 二十一世纪的今天,最具代表性的计时产品就是电子万年历,它是近代世界钟表业界的第三次革命。第一次是摆和摆轮游丝的发明,相对稳定的机械振荡频率源使钟表的走时差从分级缩小到秒级,代表性的产品就是带有摆或摆轮游丝的机械钟或表。第二次革命是石英晶体振荡器的应用,发明了走时精度更高的石英电子钟表,使钟表的走时月差从分级缩小到秒级。第三次革命就是单片机数码计时技术的应用(电子万年历),使计时产品的走时日差从分级缩小到1/600万秒,从原有传统指针计时的方式发展为人们日常更为熟悉的夜光数字显示方式,直观明了,并增加了全自动日期、星期、温度以及其他日常附属信息的显示功能,它更符合消费者的生活需求!因此,电子万年历的出现带来了钟表计时业界跨跃性的进步…… 我国生产的电子万年历有很多种,总体上来说以研究多功能电子万年历为主,使万年历除了原有的显示时间,日期等基本功能外,还具有闹铃,报警等功能。商家生产的电子万年历更从质量,价格,实用上考虑,不断的改进电子万年历的设计,使其更加的具有市场。 本设计为软件,硬件相结合的一组设计。在软件设计过程中,应对硬件部分有相关了解,这样有助于对设计题目的更深了解,有助于软件设计。基本的要了解一些主要器件的基本功能和作用。 除了采用集成化的时钟芯片外,还有采用MCU的方案,利用AT89系列单片微机制成万年历电路,采用软件和硬件结合的方法,控制LED数码管输出,分别用来显示年、月、日、时、分、秒,其最大特点是:硬件电路简单,安装方便易于实现,软件设计独特,可靠。AT89C51是由ATMEL 公司推出的一种小型单片机。95年出现在中国市场。其主要特点为采用Flash存贮器技术,降低了制造成本,其软件、硬件与MCS-51完全兼容,可以很快被中国广大用户接受。 本文介绍了基于AT89C51单片机设计的电子万年历。 首先我们在绪论中简单介绍了单片机的发展与其在中低端领域中的优

DS1302 时钟芯片的程序 /********************************************************************* 公司名称: 模块名称:DS1302.c 功能:实时时钟模块时钟芯片型号:DS1302 说明: 程序设计:zhaojunjie 设计时间:2002.03.02 版本号: 20020302 *********************************************************************/ #include sbit T_CLK = P2^3; /*实时时钟时钟线引脚 */ sbit T_IO = P1^4; /*实时时钟数据线引脚 */ sbit T_RST = P1^5; /*实时时钟复位线引脚 */ sbit ACC0 = ACC^0; sbit ACC7 = ACC^7; void RTInputByte(uchar); /* 输入 1Byte */ uchar RTOutputByte(void); /* 输出?1Byte */ void W1302(uchar, uchar); uchar R1302(uchar); void Set1302(uchar *); /* 设置时间 */ void Bcd2asc(uchar,uchar *); void Get1302(uchar curtime[]); /* 读取1302当前时间 */ /******************************************************************** 函数名:RTInputByte() 功能:实时时钟写入一字节 说明:往DS1302写入1Byte数据 (内部函数) 入口参数:d 写入的数据 返回值:无 设计:zhaojunjie 日期:2002-03-19 修改:日期: ***********************************************************************/

#ifndef __DS1302_H__ #define __DS1302_H__ #define uchar unsigned char #define uint unsigned int #include

#include "ds1302.h" /************************************************************** 函數名稱:DS1302_Write_Byte(uchar Date) 函數功能:单字节写 輸入參數:写的字节 輸出參數:无 備注: **************************************************************/ void DS1302_Write_Byte(uchar Date) { uchar i; for(i = 0;i < 8;i++) { if(Date & 0x01) IO = 1; else IO = 0; SCLK = 1; Date = Date >> 1; SCLK = 0; } } /************************************************************** 函數名稱:uchar DS1302_Read_Byte() 函數功能:单字节读 輸入參數:无 輸出參數:读出的数据 備注: **************************************************************/ uchar DS1302_Read_Byte() {

美国DALLAS公司推出的具有涓细电流充电能力的低功耗实时时钟电路DS1302的结构、工作原理及其在实时显示时间中的应用。它可以对年、月、日、周日、时、分、秒进行 DS1302的引脚排列,其中Vcc1为后备电源,VCC2为主电源。在主电源关闭的情况下,也能保持时钟的连续运行。DS1302由Vcc1或Vcc2两者中的较大者供电。当Vcc2大于Vcc1+0.2V 时,Vcc2给DS1302供电。当Vcc2小于Vcc1时,DS1302由Vcc1供电。 X1和X2是振荡源,外接32.768kHz晶振。RST是复位/片选线,通过把RST输入驱动置高电平来启动所有的数据传送。RST输入有两种功能:首先,RST接通控制逻辑,允许地址/命令序列送入移位寄存器;其次,RST提供终止单字节或多字节数据的传送手段。当RST为高电平时,所有的数据传送被初始化,允许对DS1302进行操作。如果在传送过程中RST置为低电平,则会终止此次数据传送,I/O引脚变为高阻态。上电运行时,在Vcc≥2.5V之前,RST 必须保持低电平。只有在SCLK为低电平时,才能将RST置为高电平。 I/O为串行数据输入输出端(双向),后面有详细说明。 控制字节的最高有效位(位7)必须是逻辑1,如果它为0,则不能把数据写入DS1302中,位6如果为0,则表示存取日历时钟数据,为1表示存取RAM数据;位5至位1指示操作单元的地址;最低有效位(位0)如为0表示要进行写操作,为1表示进行读操作,控制字节总是从最低位开始输出。 在控制指令字输入后的下一个SCLK时钟的上升沿时,数据被写入DS1302,数据输入从低位即位0开始。同样,在紧跟8位的控制指令字后的下一个SCLK脉冲的下降沿读出DS1302 DS1302有12个寄存器,其中有7个寄存器与日历、时钟相关,存放的数据位为BCD码形式此外,DS1302 还有年份寄存器、控制寄存器、充电寄存器、时钟突发寄存器及与RAM相关的寄存器等。时钟突发寄存器可一次性顺序读写除充电寄存器外的所有寄存器内容。 DS1302与RAM相关的寄存器分为两类:一类是单个RAM单元,共31个,每个单元组态为一个8位的字节,其命令控制字为C0H~FDH,其中奇数为读操作,偶数为写操作;另一类为突发方式下的RAM寄存器,此方式下可一次性读写所有的RAM的31个字节,命令控制字为FEH(写)、FFH(读)。 为了实现系统报警计时等功能,此设计采用了DS302实时时钟芯片。DS1302 是美国DALLAS公司推出的一种高性能、低功耗、带RAM的实时时钟电路,它可以对年、月、日、