MOS 管二级效应研究

MOS 管的二级效应主要有三种:背栅效应、沟道长度调制效应、亚阈值效应。

一.背栅效应:

在很多情况下,源极和衬底的电位并不相同。对NMOS 管而言,衬底通常接电路的最低电位,有V BS ≤0;对PMOS 管而言,衬底通常接电路的最高电位,有V BS

≥0。这时,MOS 管的阈值电压将随其源极和衬底之间电位的不同而发生变化。这一效应称为“背栅效应”。 以NMOS 管为例,当NMOS 管V BS <0时,阈值电压的变化规律。随着V GS

上升,栅极吸引衬底内部的电子向衬底表面运动,并在衬底表面产生了耗尽层。当V GS 上升到一定的电压

——阈值电压时,栅极下的衬底表面发生反型,NMOS 管在源漏之间开始导电。阈值电压的大小和耗尽层的电荷量有关,耗尽层的电荷量越多,NMOS 管的开启就越困难,阈值电压——也就是开启NMOS 需要的电压就越高。当V BS

<0时,栅极和衬底之间的电位差加大,耗尽层的厚度也变大,耗尽层内的电荷量增加,所以造成阈值电压变大。随着V BS

变小,阈值电压上升,在V GS 和V DS

不变的情况下,漏极电流变小。因而衬底和栅极的作用类似,也能控制漏极电流的变化。所以我们称它为“背栅”作用。

在电路设计上可采取一些措施来减弱或消除衬偏效应,例如把源极和衬底短接起来,当然可以消除衬偏效应的影响,但是这需要电路和器件结构以及制造工艺的支持,并不是在任何情况下都能够做得到的。例如,对于p 阱CMOS 器件,其中的n-MOSFET 可以进行源-衬底短接,而其中的p-MOSFET 则否;对于n 阱CMOS 器件,其中的p-MOSFET 可以进行源-衬底短接,而其中的n-MOSFET 则否。

另外可以改进电路结构来减弱衬偏效应。例如,对于CMOS 中的负载管,若采用有源负载来代替之,即可降低衬偏调制效应的影响(因为当衬偏效应使负载管的沟道电阻增大时,有源负载即提高负载管的VGS 来使得负载管的导电能力增强)。

二.沟道长度调制效应:

MOS 晶体管中,栅下沟道预夹断后、若继续增大Vds ,夹断点会略向源极方向移动。导致夹断点到源极之间的沟道长度略有减小,有效沟道电阻也就略有减小,从而使更多电子自源极漂移到夹断点,导致在耗尽区漂移电子增多,使Id 增大,这种效应称为沟道长度调制效应。

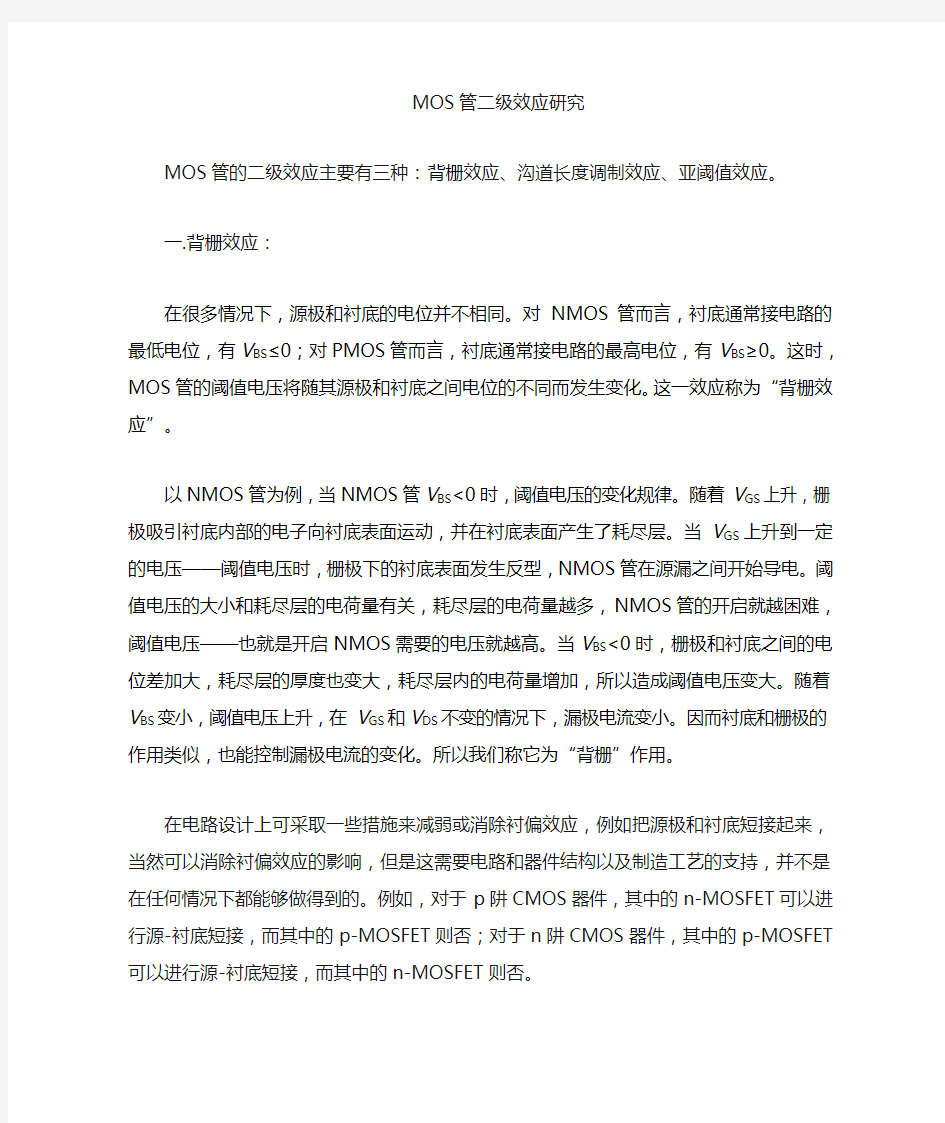

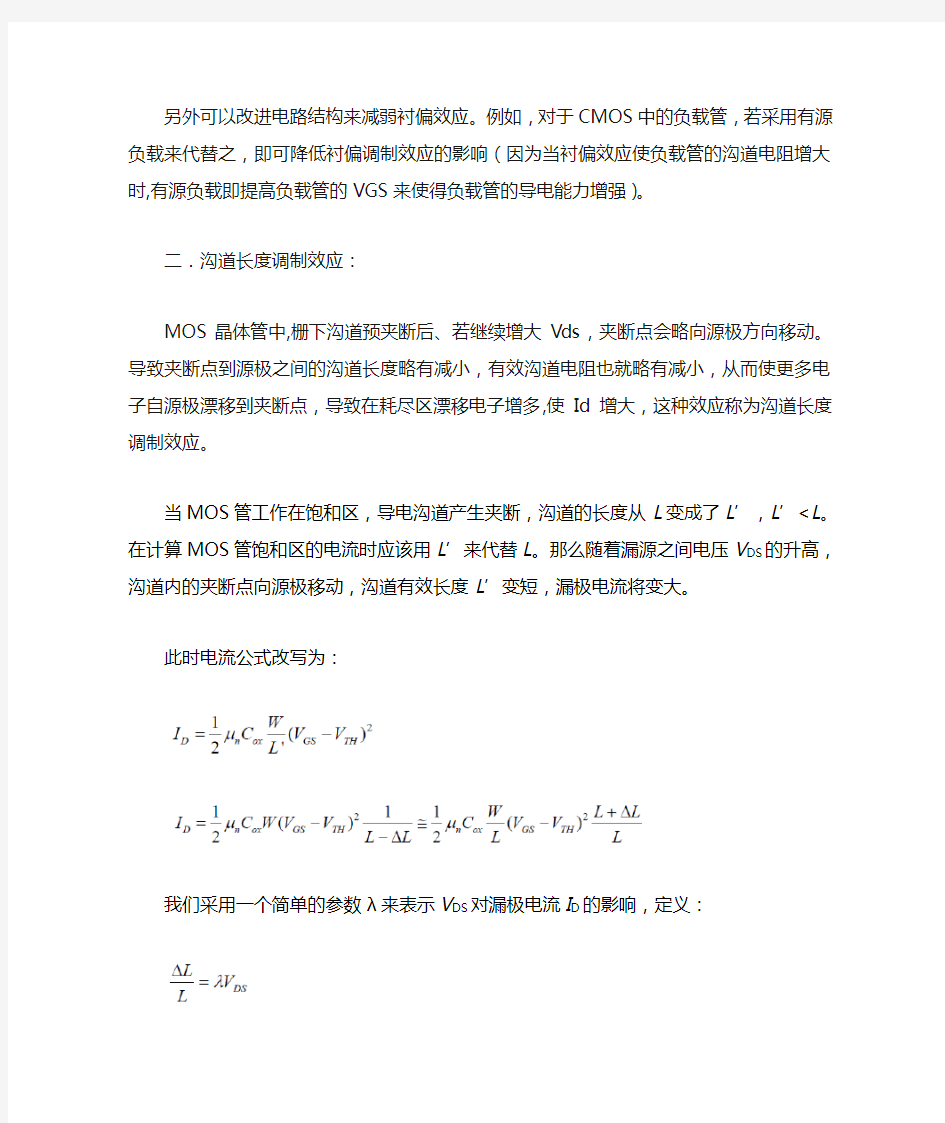

当MOS 管工作在饱和区,导电沟道产生夹断,沟道的长度从L 变成了L ’,L ’ 的升高,沟道内 的夹断点向源极移动,沟道有效长度L ’变短,漏极电流将变大。 此时电流公式改写为: 我们采用一个简单的参数λ来表示V DS 对漏极电流I D 的影响,定义: 由此可以得到考虑了沟道长度调制效应的MOS 管饱和区的电流公式: 由于λ∝1/L ,对于长沟道的器件而言(例如L >10um ), λ的数值很小,λV DS <<1,所以这个误差可以忽略。而沟道越短,这个误差就越大。事实上,对于短沟道的MOS 管,用一个简单的参数λ来体现沟道长度调制效应是非常不准确的。因而我们有时会发现,电路仿真的结果和用公式计算出来的结果完全不同。所以说一阶的近似公式更主要的是起到电路设计的指导作用。 三.亚阈值效应 在前面对MOS 管导电原理的分析中,我们认为当栅源电压V GS ,沟道内就出现了电流。而实际情况并不是这样。即使在V GS 从饱和区的平方律变成了亚阈值区的指数规律。MOS 管的电流-电压关系可以用公式 来表示。其中I D0是和工艺有关的参数,η是亚阈值斜率因子,通常满足1<η<3。当V GS 满足q kT V V TH GS η+<的条件时,一般认为MOS 管进入了亚阈值区域. 当q kT V V TH GS η+> 时,称MOS 管工作在强反型区。 当q kT V V TH GS η +< 时称MOS 管工作在强反型区。 强反型区和弱反型区的划分其实也是对MOS 管实际工作特定的一种近似,只是它比前面讲到的MOS 管的一阶近似更加准确。从公式上分析,强反型区和弱反型区之间同样存在着电流不连续的问题。为了解决这一问题,也是为了建立更精确的MOS 管模型,在这两个区之间又定义了中等反型区。 对于斜率因子η的解释要从MOS 管的电流变化讲起。表征亚阈值特性的一个重要参数是栅极电压的变化幅度,也就是MOS 管从电流导通到电流截止时所需要的栅极电压的变化量。这一特性用亚阈值斜率S 来表示。S 定义为亚阈值电流每变化10倍(一个数量级)所要求栅极电压的变化量。S 越小意味着MOS 管的关断性能越好。 功率场效应晶体管MOSFET 1.概述 MOSFET的原意是:MOS(Metal Oxide Semiconductor金属氧化物半导体),FET(Field Effect Transistor场效应晶体管),即以金属层(M)的栅极隔着氧化层(O)利用电场的效应来控制半导体(S)的场效应晶体管。 功率场效应晶体管也分为结型和绝缘栅型,但通常主要指绝缘栅型中的MOS型(Metal Oxide Semiconductor FET),简称功率MOSFET(Power MOSFET)。结型功率场效应晶体管一般称作静电感应晶体管(Static Induction Transistor——SIT)。其特点是用栅极电压来控制漏极电流,驱动电路简单,需要的驱动功率小,开关速度快,工作频率高,热稳定性优于GTR,但其电流容量小,耐压低,一般只适用于功率不超过10kW的电力电子装置。 2.功率MOSFET的结构和工作原理 功率MOSFET的种类:按导电沟道可分为P沟道和N沟道。按栅极电压幅值可分为;耗尽型;当栅极电压为零时漏源极之间就存在导电沟道,增强型;对于N(P)沟道器件,栅极电压大于(小于)零时才存在导电沟道,功率MOSFET主要是N沟道增强型。 2.1功率MOSFET的结构 功率MOSFET的内部结构和电气符号如图1所示;其导通时只有一种极性的载流子(多子)参与导电,是单极型晶体管。导电机理与小功率MOS管相同,但结构上有较大区别,小功率MOS管是横向导电器件,功率MOSFET大都采用垂直导电结构,又称为VMOSFET (Vertical MOSFET),大大提高了MOSFET器件的耐压和耐电流能力。 按垂直导电结构的差异,又分为利用V型槽实现垂直导电的VVMOSFET和具有垂直导电双扩散MOS结构的VDMOSFET(Vertical Double-diffused MOSFET),本文主要以VDMOS 器件为例进行讨论。 功率MOSFET为多元集成结构,如国际整流器公司(International Rectifier)的HEXFET 采用了六边形单元;西门子公司(Siemens)的SIPMOSFET采用了正方形单元;摩托罗拉公司(Motorola)的TMOS采用了矩形单元按“品”字形排列。 2.2功率MOSFET的工作原理 截止:漏源极间加正电源,栅源极间电压为零。P基区与N漂移区之间形成的PN结J1 反偏,漏源极之间无电流流过。 导电:在栅源极间加正电压UGS,栅极是绝缘的,所以不会有栅极电流流过。但栅极的正电压会将其下面P区中的空穴推开,而将P区中的少子—电子吸引到栅极下面的P区表面 当UGS大于UT(开启电压或阈值电压)时,栅极下P区表面的电子浓度将超过空穴浓度,使P型半导体反型成N型而成为反型层,该反型层形成N沟道而使PN结J1消失,漏极和源极导电。 2.3功率MOSFET的基本特性 第五章 MOS 场效应晶体管 § 5.1 MOS 场效应晶体管的结构和工作原理 1.基本结构 上一章我们简单提到了金属-半导体场效应晶体管(即MESFET ),它的工作原理和JEFET 的工作原理有许多类似之处。如果在金属-半导体结之间加一层氧化物绝缘层(如SiO 2)就可以形成另一种场效应晶体管,即金属-氧化物-半导体场效应晶体管(Metal Oxide Semiconductor Field Effect Transistor ,缩写MOSFET ),如图所示(P172)。 MOS 管主要是利用半导体表面效应而制成的晶体管,参与工作的只有一种载流子(即多数载流子),所以又称为单极型晶体管。在双极型晶体管中,参加工作的不仅有多数载流子,也有少数载流子,故称为双极型晶体管。 本章主要以金属―SiO 2―P 型Si 构成的MOS 管为例来讨论其工作原理。器件的基本参数是:沟道长度L (两个N P +结间的距离);沟道宽度Z ;氧化层厚度x 0;漏区和源区的结深 x j ;衬底掺杂浓度N a 等。 MOS 场效应晶体管可以以半导体Ge 、Si 为材料,也可以用化合物GaAs 、InP 等材料制作,目前以使用Si 材料的最多。MOS 器件栅下的绝缘层可以选用SiO 2、Si 3N 4和Al 2O 3等绝缘材料,其中使用SiO 2最为普遍。 2.载流子的积累、耗尽和反型 (1)载流子积累 我们先不考虑漏极电压V D ,将源极和衬底接地,如图所示。如果在栅极加一负偏压(0G 场效应管和mos管的区别

第五章 MOS场效应晶体管