Power-Aware Test Planning in the Early System-on-Chip Design Exploration Process

- 格式:pdf

- 大小:1.57 MB

- 文档页数:13

可编辑修改精选全文完整版TEST BANKCHAPTER 6: PROCUREMENTMultiple Choice Questions (correct answers are bolded)1. ___________ refers to the raw materials, component parts, and supplies bought from outside organizations to support a company’s operations.a. Inbound logisticsb. Procurementc. Materials managementd. Supply management[LO 6.1: To compare procurement, purchasing, and supply management; Moderate; Concept; AACSB Category 3: Analytical thinking]2. Procurement costs often range between ___________ and ___________ percent of an organization’s revenues.a. 60; 80b. 50; 70c. 40; 60d. 30; 50[LO 6.1: To compare procurement, purchasing, and supply management; Moderate; Application; AACSB Category 3: Analytical thinking]3. Procurement’s historical focus in many organizations was to ___________.a. incur minimal supply disruptionsb. use a limited number of suppliersc. minimize loss and damaged. achieve the lowest possible cost[LO 6.1: To compare procurement, purchasing, and supply management; Moderate; Synthesis; AACSB Category 3: Analytical thinking]4. Procurement and ___________ are viewed as synonymous terms.a. materials managementb. supply managementc. purchasingd. inbound logistics[LO 6.1: To compare procurement, purchasing, and supply management; Easy; Concept; AACSB Category 3: Analytical thinking]5. ___________ involves an increased focus on identifying and using data internally and across a supply chain so that a company can consolidate its purchasing power for enhanced value.a. Supply managementb. Strategic sourcingc. Supply chain managementd. Procurement[LO 6.1: To compare procurement, purchasing, and supply management; Moderate; Concept; AACSB Category 3: Analytical thinking]6. Which of the following is not a potential benefit associated with procurement cards (p-cards)?a. There is a reduced number of invoices.b. Users can make purchases in a more timely fashion.c. Suppliers can be paid in a more timely fashion.d. They can be used in non-domestic markets.[LO 6.1: To compare procurement, purchasing, and supply management; Difficult; Synthesis; AACSB Category 3: Analytical thinking]7. Which of the following is not a potential procurement objective?a. minimizing procurement costsb. supporting organizational goals and objectivesc. managing the supply based. supporting operational requirements[LO 6.2: To review procurement objectives; Moderate; Synthesis; AACSB Category 3: Analytical thinking]8. A focus on satisfying internal customers is associated with which procurement objective?a. managing the supply baseb. supporting operational requirementsc. supporting organizational goals and objectivesd. managing the purchasing process effectively and efficiently[LO 6.2: To review procurement objectives; Moderate; Synthesis; AACSB Category 3: Analytical thinking]9. The selection, development, and maintenance of supply sources is associated with which procurement objective?a.managing the purchasing process effectively and efficientlyb.supporting operational requirementsc.developing relationships with other functional groupsd.managing the supply base[LO 6.2: To review procurement objectives; Moderate; Synthesis; AACSB Category 3: Analytical thinking]10. Buying the right products, at the right price, from the right source, at the right specifications, in the right quantity, and for delivery at the right time to the right internal customer is associated with what procurement objective?a. managing the supply baseb. managing the purchasing process effectively and efficientlyc. supporting operational requirementsd. supporting organizational goals and objectives[LO 6.2: To review procurement objectives; Moderate; Synthesis; AACSB Category 3: Analytical thinking]11. What is the first step in supplier selection and evaluation?a. Prepare a request for proposal.b. Prepare a procurement budget.c. Identify possible suppliers.d. Identify the need for supply.[LO 6.3: To review supplier selection and evaluation approaches; Moderate; Application; AACSB Category 3: Analytical thinking]12. With respect to the supplier selection and evaluation process, ___________ looks at both the internal and external environment within which the supply decision is to be made.a. Identify the need for supply.b. Identify suppliers.c. Perform a situation analysis.d. Evaluate suppliers.[LO 6.3: To review supplier selection and evaluation approaches; Moderate; Application; AACSB Category 3: Analytical thinking]13. What is the final step in the supplier selection and evaluation process?a. Provide feedback.b. Select suppliers.c. Implement the decision.d. Evaluate the decision.[LO 6.3: To review supplier selection and evaluation approaches; Moderate; Application; AACSB Category 3: Analytical thinking]14. Multiple sourcing uses more than one supplier in hopes of increased competition, improved market intelligence, and ___________.a. greater supply risk mitigationb. lower costs per unitc. increased cooperationd. increased communication[LO 6.3: To review supplier selection and evaluation approaches; Moderate; Application; AACSB Category 3: Analytical thinking]15. Single sourcing consolidates purchase volume with a single supplier in hopes of increasing cooperation and communication in the supply relationship as well as ___________.a. greater supply risk mitigationb. increased amounts of competitionc. improved market intelligenced. lower costs per unit[LO 6.3: To review supplier selection and evaluation approaches; Moderate; Application; AACSB Category 3: Analytical thinking]16. Which of the following statements is false?a. Supplier selection and evaluation generally involves multiple criteria.b. The evolution of business practices and philosophies may require new supplier selection criteria.c. Selecting suppliers is the final step of the supplier selection and evaluation process.d. Some supplier selection criteria may be contradictory.[LO 6.3: To review supplier selection and evaluation approaches; Difficult; Synthesis; AACSB Category 3: Analytical thinking]17. Which of the following would not be part of a supplier audit?a. supplier’s structureb. supplier’s resourcesc. supplier’s scorecardd. supplier’s financial and risk health[LO 6.3: To review supplier selection and evaluation approaches; Moderate; Application; AACSB Category 3: Analytical thinking]18. Kraljic’s Portfolio Matrix ___________.a. provides a framework for evaluating warehousing decisionsb. is used by many managers to classify corporate purchases in terms of their importance and supply complexityc. allows managers to evaluate whether to add, or not add, product linesd. is synonymous with the total cost of ownership[LO 6.4: To review Kraljic’s Portfolio Matrix; Moderate; Concept; AACSB Category 3: Analytical thinking]19. Bottleneck, leverage, and strategic are categories associated with ___________.a. Kraljic’s Portfolio Matrixb. Supplier Audit Matrixc. Supplier Development Matrixd. Global Procurement Matrix[LO 6.4: To review Kraljic’s Portfolio Matrix; Moderate; Application; AACSB Category 3: Analytical thinking]20. A degree of aggressive procurement involvement not normally encountered in supplier selection refers to ___________.a. supply managementb. supplier developmentc. materials managementd. physical supply[LO 6.4: To review Kraljic’s Portfolio Matrix; Moderate; Concept; AACSB Category 3: Analytical thinking]21. Supplier development is synonymous with ___________.a. supplier selection and evaluationb. procurementc. materials managementd. reverse marketing[LO 6.4: To review Kraljic’s Portfolio Matrix; Moderate; Concept; AACSB Category 3: Analytical thinking]22. Which of the following is not a reason that purchasers are adopting a more proactive and aggressive role in the procurement process?a. There are myriad inefficiencies associated with suppliers initiating marketing efforts toward purchasers.b. They are achieving a competitive advantage in the supply chain.c. An excess number of suppliers currently exists.d. Purchasers may be aware of important benefits that are not known to the supplier. [LO 6.4: To review Kraljic’s Portfolio Matrix; Difficult; Synthesis; AACSB Category 3: Analytical thinking]23. Which of the following is false?a. In the factor-input strategy, an organization is seeking low-cost or high-quality sources of supply.b. Global procurement refers to buying components and inputs anywhere in the world.c. Planning is the first step in global procurement.d. A market access strategy emphasizes procurement from geographically close countries.[LO 6.5: To establish issues associated with global procurement; Difficult; Synthesis; AACSB Category 3: Analytical thinking]24. What is the first step in a global sourcing development model?a. planningb. specificationc. situation analysisd. problem recognition[LO 6.5: To establish issues associated with global procurement; Moderate; Application; AACSB Category 3: Analytical thinking]25. ___________ is often a major shortcoming of many global procurement plans.a. Confiscationb. Specificationc. Implementationd. Evaluation[LO 6.5: To establish issues associated with global procurement; Moderate; Application; AACSB Category 3: Analytical thinking]26. What concept refers to when firms consider all the costs that can be assigned to the acquisition, use, and maintenance of a purchase?a. activity-based costingb. cost trade-offsc. the systems approachd. total cost of ownership[LO 6.5: To establish issues associated with global procurement; Easy; Application; AACSB Category 3: Analytical thinking]27. Procuring products from s uppliers close to one’s own facilities refers to ___________.a. agglomerationb. near-sourcingc. sustainabilityd. outsourcing[LO 6.5: To establish issues associated with global procurement; Easy; Application; AACSB Category 3: Analytical thinking]28. Which of the following is not a dimension associated with socially responsible procurement?a. profitb. safetyc. the environmentd. human rights[LO 6.6: To identify social and environmental aspects of sustainable procurement; Moderate; Synthesis; AACSB Category 3: Analytical thinking]29. With respect to gift giving and gift receiving, a ___________ refers to money paid before an exchange.a. kickbackb. agglomerationc. bribed. dovetailing[LO 6.6: To identify social and environmental aspects of sustainable procurement; Easy; Concept; AACSB Category 3: Analytical thinking]30. With respect to gift giving and gift receiving, a ___________ refers to money paid after an exchange.a. kickbackb. agglomerationc. bribed. dovetailing[LO 6.6: To identify social and environmental aspects of sustainable procurement; Easy; Concept; AACSB Category 3: Analytical thinking]31. ___________ identifies opportunities to recover revenues or reduce costs associated with scrap, surplus, obsolete, and waste materials.a. Recyclingb. Reusec. Reverse logisticsd. Investment recovery[LO 6.6: To identify social and environmental aspects of sustainable procurement; Easy; Concept; AACSB Category 3: Analytical thinking]32. ___________ materials refer to stock that exceeds the reasonable requirements of an organization.a. Wasteb. Excessc. Obsoleted. Scrap[LO 6.6: To identify social and environmental aspects of sustainable procurement; Moderate; Concept; AACSB Category 3: Analytical thinking]33. ___________ materials are no longer serviceable, have been discarded, or are a by-product of the production process.a. Wasteb. Obsoletec. Scrapd. Excess[LO 6.6: To identify social and environmental aspects of sustainable procurement; Moderate; Concept; AACSB Category 3: Analytical thinking]34. ___________ materials have no economic value.a. Wasteb. Scrapc. Obsoleted. Excess[LO 6.6: To identify social and environmental aspects of sustainable procurement; Moderate; Concept; AACSB Category 3: Analytical thinking]35. ___________ refers to a set of technology and finance-based processes that strive to optimize cash flow by allowing businesses to extend their payment terms to their suppliers while simultaneously allowing their suppliers to get paid early.a. Cash flow managementb. Supply chain financec. Flexible payment systemd. Supplier credit float[LO 6.7: To describe the concept of supply chain finance and how it can be used in procurement relationships; Moderate; Concept; AACSB Category 3: Analytical thinking]True-False Questions1.Procurement refers to the raw materials, component parts, and supplies bought from outsideorganizations to support a company’s operations. (True)[LO 6.1: To compare procurement, purchasing, and supply management; Easy; Concept; AACSB Category 3: Analytical thinking]2.Procurement’s costs often range between 40 and 60 percent of an organization’s revenues.(False)[LO 6.1: To compare procurement, purchasing, and supply management; Moderate; Application; AACSB Category 3: Analytical thinking]3.Procurement’s historical focus in many organizations was to minimize the total number ofoutside suppliers. (False)[LO 6.1: To compare procurement, purchasing, and supply management; Moderate; Synthesis; AACSB Category 3: Analytical thinking]4. A contemporary procurement manager might have responsibility for reducing cycle timesand for generating additional revenues by collaborating with the marketing department.(True)[LO 6.1: To compare procurement, purchasing, and supply management; Moderate; Synthesis; AACSB Category 3: Analytical thinking]5.Procurement and purchasing are viewed as synonymous terms. (True)[LO 6.1: To compare procurement, purchasing, and supply management; Easy; Concept; AACSB Category 3: Analytical thinking]6.Supply chain management refers to a relational exchange approach involving a limitednumber of suppliers. (False)[LO 6.1: To compare procurement, purchasing, and supply management; Moderate; Concept; AACSB Category 3: Analytical thinking]7.Strategic sourcing involves an increased focus on identifying and using data internally andacross the supply chain so that a company can consolidate its purchasing power for enhanced value. (True)[LO 6.1: To compare procurement, purchasing, and supply management; Moderate; Application; AACSB Category 3: Analytical thinking]8.One benefit to procurement cards is that they are easily used outside of their domesticmarket. (False)[LO 6.1: To compare procurement, purchasing, and supply management; Moderate; Synthesis; AACSB Category 3: Analytical thinking]9.First and foremost, procurement’s objectives must manage the purchasing process effectivelyand efficiently. (False)[LO 6.2: To review procurement objectives; Moderate; Synthesis; AACSB Category 3: Analytical thinking]10.One of procurement’s most important responsibilities involves supplier selection andevaluation. (True)[LO 6.3: To review supplier selection and evaluation approaches; Easy; Application; AACSB Category 3: Analytical thinking]11.The first step in supplier selection and evaluation is situation analysis. (False)[LO 6.3: To review supplier selection and evaluation approaches; Moderate; Synthesis; AACSB Category 3: Analytical thinking]12.A benefit to multiple sourcing is increased cooperation and communication in a supplyrelationship. (False)[LO 6.3: To review supplier selection and evaluation approaches; Moderate; Application; AACSB Category 3: Analytical thinking]13.Single sourcing consolidates purchase volume with a single supplier with the hopes ofenjoying lower costs per unit. (True)[LO 6.3: To review supplier selection and evaluation approaches; Easy; Application; AACSB Category 3: Analytical thinking]14.The final step of the supplier selection process is to evaluate the decision. (True)[LO 6.3: To review supplier selection and evaluation approaches; Easy; Synthesis; AACSB Category 3: Analytical thinking]15.Supplier scorecards involve a ssessments of a supplier’s structure, resources, technology,health, and responsibility. (False)[LO 6.3: To review supplier selection and evaluation approaches; Moderate; Concept; AACSB Category 3: Analytical thinking]16.Supplier scorecards can be categorical, weighted point, or cost based in nature. (True)[LO 6.3: To review supplier selection and evaluation approaches; Moderate; Application; AACSB Category 3: Analytical thinking]17.Supplier selection and evaluation generally involve multiple criteria, and these criteria canvary in both number and importance, depending on the particular situation. (True)[LO 6.3: To review supplier selection and evaluation approaches; Moderate; Synthesis; AACSB Category 3: Analytical thinking]18.The Optimal Cost Reliability Model is used by many managers to classify corporatepurchases in terms of their importance and supply complexity. (False)[LO 6.4 To review Kraljic’s Portfolio Matrix; Moderate; Concept; AACSB Category 3: Analytical thinking]19.Bottleneck refers to the low importance, low complexity category of Kraljic’s PortfolioMatrix. (False)[LO 6.4 To review Kraljic’s Portfolio Matrix; Moderate; Application; AACSB Category 3: Analytical thinking]20.Leverage refers to the high importance, low complexity category of Kraljic’s PortfolioMatrix. (True)[LO 6.4 To review Kraljic’s Portfolio Matrix; Moderate; Application; AACSB Category 3: Analytical thinking]21.Supply management refers to a degree of aggressive procurement not normally encounteredin supplier selection. (False)[LO 6.4 To review Kraljic’s Portfolio Matrix; Moderate; Concept; AACSB Category 3: Analytical thinking]22.Supplier development is synonymous with reverse marketing. (True)[LO 6.4 To review Kraljic’s Portfolio Matrix; Easy; Concept; AACSB Category 3: Analytical thinking]23.One reason for the growth of the supplier development concept is that achieving competitiveadvantage in the supply chain is predicated on purchasers adopting a more aggressiveapproach. (True)[LO 6.4 To review Kr aljic’s Portfolio Matrix; Moderate; Application; AACSB Category 3: Analytical thinking]24.Global procurement refers to buying components and inputs anywhere in the world. (True) [LO 6.5: To establish issues associated with global procurement; Easy; Concept; AACSB Category 3: Analytical thinking]25.Global procurement is primarily driven by the input-output and market-access strategies.(False)[LO 6.5: To establish issues associated with global procurement; Moderate; Application; AACSB Category 3: Analytical thinking]26.Problem recognition is the first step in global procurement. (False)[LO 6.5: To establish issues associated with global procurement; Moderate; Synthesis; AACSB Category 3: Analytical thinking]27.Because global sourcing increases the distance that components and inputs must be moved,managers must consider the trade-off between transportation and holding costs. (True) [LO 6.5: To establish issues associated with global procurement; Moderate; Application; AACSB Category 3: Analytical thinking]28.Implementation is often a major shortcoming of many global procurement plans. (True) [LO 6.5: To establish issues associated with global procurement; Moderate; Synthesis; AACSB Category 3: Analytical thinking]29.When taking an activity-based costing approach, firms consider all the costs that can beassigned to the acquisition, use, and maintenance of a purchase. (False)[LO 6.5: To establish issues associated with global procurement; Moderate; Concept; AACSB Category 3: Analytical thinking]30.Dovetailing refers to procuring products from suppliers closer to one’s own facilities. (False) [LO 6.5: To establish issues associated with global procurement; Moderate; Concept; AACSB Category 3: Analytical thinking]31.Sustainable procurement refers to the integration of social and environmental considerationsinto all stages of the purchasing process. (True)[LO 6.6: To identify social and environmental aspects of sustainable procurement; Easy; Concept; AACSB Category 3: Analytical thinking]32.Diversity and philanthropy are two dimensions of socially responsible procurement. (True) [LO 6.6: To identify social and environmental aspects of sustainable procurement; Easy; Application; AACSB Category 3: Analytical thinking]33.With respect to gift giving and gift receiving, bribes refer to money paid after an exchange.(False)[LO 6.6: To identify social and environmental aspects of sustainable procurement; Moderate; Concept; AACSB Category 3: Analytical thinking]34.The relevance, importance, and challenges associated with socially responsible procurementare likely to lessen in the coming years. (False)[LO 6.6: To identify social and environmental aspects of sustainable procurement; Moderate; Application; AACSB Category 3: Analytical thinking]35.Investment recovery identifies opportunities to recover revenues or reduce costs associatedwith scrap, surplus, obsolete, and waste materials. (True)[LO 6.6: To identify social and environmental aspects of sustainable procurement; Easy; Concept; AACSB Category 3: Analytical thinking]36.Investment recovery is often the responsibility of the finance manager. (False)[LO 6.6: To identify social and environmental aspects of sustainable procurement; Moderate; Application; AACSB Category 3: Analytical thinking]37. Excess materials refer to stock that exceeds the reasonable requirements of an organization. (True)[LO 6.6: To identify social and environmental aspects of sustainable procurement; Easy; Concept; AACSB Category 3: Analytical thinking]38.Scrap materials are no longer serviceable, have been discarded, or are a by-product of theproduction process. (True)[LO 6.6: To identify social and environmental aspects of sustainable procurement; Easy; Concept; AACSB Category 3: Analytical thinking]39.Obsolete materials have no economic value. (False)[LO 6.6: To identify social and environmental aspects of sustainable procurement; Moderate; Concept; AACSB Category 3: Analytical thinking]40.Supply chain finance refers to a set of technology and finance-based processes that strive tooptimize cash flow by allowing businesses to extend their payment terms to their suppliers while simultaneously allowing suppliers to be paid early. (True)[LO 6.6: To identify social and environmental aspects of sustainable procurement; Moderate; Concept; AACSB Category 3: Analytical thinking]。

2024届高考英语时文阅读之语法填空专项训练专题04自然灾难与防范基础篇Natural Phenomena: The roaring of floods咆哮的洪水巩固篇search continues for Morocco's quake survivors搜寻摩洛哥地震幸存者提高篇Wildfire spreads on Spain's Tenerife西班牙特内里费岛野火集中专项微练单句语法填空非谓语动词专项训练真题精选高考模拟连接名校真题演练【原创题】【基础篇】There may not always be time to protectyourself, but there are a few tips for dealing1 floods covering three phases:before, during and after a flood. When 2(choose) a place to live, try to avoid thefloodplain-areas close to a water source, 3can experience flooding during heavy rains. Andprepare some first aid bags along with your important 4 (document) in waterproof bags. Meanwhile, keep 5 eye on the warning systems. On July 7, more than 30,000 people in Donglan County, China's Guangxi Zhuang Autonomous Region, were 6 (safe) transferred before flooding thanks to the warning system.When a flood 7 (happen), do not walk, swim or drive through flood waters. 8 (move) water contains great power that can knock you down and sweep your vehicle away. 9 you have to walk in water, make sure the water is not moving and you have things like a safety rope. Don't return home untilauthorities confirm it is safe. And be aware of water hygiene and power lines when you use them. Sometimes animals like snakes could appear in your house, you should wear gloves for sanitation and 10 (safe) .【答案】1. with2. choosing3. which4. documents5. an6. safely7. happens8. Moving9. If 10. safety【巩固篇】People slept in the streets for a third straightnight as soldiers and international aid teams intrucks and 1 (helicopter) began to faninto remote mountain villages hit hardest by themagnitude 6.8 quake, 2 struck 72kilometers southwest of Marrakech late 3Friday night. A Chinese medical team in Moroccoreceived a call from a local hospital shortly afterthe quake, saying a pregnant woman 4 (experience) severe predelivery bleeding. A doctor from the team rushed to the hospital and conducted 5 emergency surgery to deliver a baby girl, according to reports from Chinese media outlets. Both mother and daughter were doing well, the reports 6 (add).The team said it has performed multiple cesarean sections in the aftermath of the disaster, welcoming several new lives into the world. Flags 7 (lower) across Morocco, as King Mohammed VI ordered three days of national mourning starting on Sunday. He thanked Spain, Qatar, the UK and the UAE for 8 (they) assistance in search and rescue efforts, state TV reported. Morocco's deadliest quake was a magnitude 5.8 temblor in 1960 that struck near the city of Agadir, 9 (kill) at least 12,000. It prompted Morocco to change construction rules, but many buildings, 10 (especial) rural homes, are still not built to withstand strong tremors.【答案】1. helicopters2. which3. on4. was experiencing5. an6. added7. were lowered8. their9. killing 10. especially【提高篇】A wildfire on the Spanish island of Tenerifethat has forced thousands of people 1(flee) their homes remained out of control onSunday, despite a slight 2 (improve) inweather conditions during the night. Orange flameslit 3 the night sky from Saturday intoSunday on hillsides just above the lights ofinhabited areas, 4 thick black smokebillowed high into the air.Late on Saturday, emergency services said the fire was now affecting 10 towns, although 11 had been evacuated as a precaution. No major tourist areas 5 (affect). It covered an area of over 8,000 hectares (20,000 acres) with a perimeter of 70 km (40 miles), spreading from 5,000 hectares and a perimeter of 50 km early on Saturday. Regional 6 (authority)said over 12,000 people had been evacuated, revising down their earlier provisional estimate of 26,000.Weather conditions overnight were "better than expected" Tenerife's fire brigade said on Sunday on X,7 (form) known as Twitter. Fernando Clavijo, Canary Islands' regional leader, said the largest firefighting deployment in the history of Tenerife had so-far prevented the loss of any homes. Evacuations were ordered throughout Saturday due to worsening weather conditions. At 8 news conference late on Saturday, the head of Tenerife's local government Rosa Davila described the fire as "devastating" and said it had forced new evacuations.The blaze broke out on Wednesday in a mountainous national park around the Mount Teide volcano - Spain's highest peak. Popular tourist areas on Tenerife, part of the Canaries archipelago in the Atlantic Ocean, have so far been unaffected 9 its two airports have been operating normally. Scorching heat and dry weather this summer have contributed to unusually severe wildfires in Europe, 10 (include) in Spain's La Palma island in July, and Canada. Blazes on Hawaii's Maui island earlier this month killed more than 110 people and wrecked the historic resort city of Lahaina. Scientists say climate change has led to more frequent and more powerful extreme weather events.【答案】1. to flee2. improvement3. up4. while5. have been affected6. authorities7. formerly8. a9. and 10. including【专项微练:非谓语动词】1.__________ (inspire) by the people she met online, she decided to start an IT club. (所给词的适当形式填空)【答案】Inspired【详解】考查非谓语动词。

COMAC航空科技英语等级考试B样题COMAC航空科技英语等级考试B1(技术类)样题Test Time:120 minutes部门_______________ 姓名____________ ⼯号____________Part I Listening (30%)Section 1 Conversation and Lecture(10%)Directions: In this section, you will hear a long conversation and a lecture. At the end of the conversation or the lecture, you will hear five questions. The conversation, the lecture and the questions will be spoken ONLY ONCE. After you hear a question, you must choose the best answer from the four choices.Conversation1. A) They get you directly to holiday destination.B) Their tickets can be bought on the internet.C) They offer excellent services to customers.D) They’re much cheaper than famous airlines.2. A) They have sprung up recently and become successful.B) They change prices on the basis of customers’ demand.C) They always offer travelers the extremely cheap flight.D) They do much advertising but few people ever watch it.3. A) By travelling before public holidays.B) By buying tickets a day in advance.C) By booking at the very last minute.D) By flying at peak time like Fridays.4. A) They try every possible means to reduce expenses.B) They charge different prices depending on demand.C) They don’t serve any food on any of their flights.D) They have increased the speed of their aero planes.5. A) They only offer cheap tickets online.B) They fail to offer satisfactory service.C) They spend little time on the ground.D) They fly to and from smaller airports.Lecture6. A) The 845m2 wing area is large enough to park 70 cars.B) The plane has the potential to carry 550 passengers.C) The tail is about as long as the Great Sphinx in Egypt.D) The two deck fuselage is as high as a 7-storey building.7. A) It is as economical to run as a common jet.B) It burns more fuel than other jumbo jets.C) It can fly an amazing 15,000 km non-stop.D) It can carry more fuel than other planes.8. A) Toulouse in France.B) England and Wales.C) All over the Europe.D) Spain and Germany.9. A) It is remarkably expensive.B) It is impressively efficient.C) It is a nation-wide project.D) It is extremely complicated.10.A) The expenses.B) The designing.C) The electronics.D) The cooperation.Section 2 Compound Dictation (10%)Directions: In this section, you will hear a passage TWICE. You have its script in the following, but with eleven blanks in it. You are required to fill in the first eight blanks with the exact words you have just heard. For last three blanks, you can either use the exact words you have just heard or write down the main points in your own words. Remember, there will be a pause for the last three blanks.Laurence Barron, President of Airbus China, defended the A380 superjumbo jet as its safety performance has been called into question.“The Qantas A380 suffered an (1) ______________ engine failure, a fairly rare event, which also damaged the aircraft itself. The aircraft performed as expected and (2) ______________ safely, so no, there is nothing wrong with the A380. It’s a (3)______________ aircraft.”Barron also says the engine issue will not (4) ______________ next summer’s scheduled delivery of the A380 to China Southern Airlines, the only (5) ______________ carrier to purchase the plane.Meanwhile, Barron explains that the lack of orders for its A350 aircraft, which is under development, from Chinese carriers is due to the country’s (6) ______________ planning structure.“The Chinese government, as you are well aware, works on a 5-year-plan basis, and they are about to (7) ______________ the 12th 5-year-plan which runs from 2011 to 2015. The A350 deliveries that we can offer are now in the what will become the 13th 5-year-plan period.”Eric Chen, Airbus China‘s Vice President, adds that the Chinese carriers’ timid (8) _____________ to the A350 is due to its competing product, Boeing’s 787.“Several years ago, Chinese airlines ordered more than 60 Boeing 787’s and for various reasons, airlines lack this kind of courage and determination to be a launching customer for a new program again. In other words, we are buying the bill for our rivals’ dilemma and consequences.”(9) __________________________________________________________________________________________________________________________________“I don’t really understand the world ‘challenge’. Our industry is challenging. There are lots of challenges but this is not a challenge, this is a competitor. (10) __________________________________________________________________________ Beverly Wyse, Vice President of Boeing’s 737 program, says Boeing is open to work with C919’s manufacturer.“I think (11) __________________________________________________________________________________________________________________________”Four Chinese airlines and two aircraft leasing companies have signed agreements to purchase 100 C919’s as launching costumers.Section 3 Listening and translating (10%)Directions: In this section you are going to hear five short passages. You will hear them ONLY ONCE. In each of these passages some of the sentences are already printed. You are required to translate the missing parts into Chinese. After each of the passages there will be a pause lasting one and a half minutes. The pause is intended for you to do the translation.1)The ARJ21-700 jetliner, China’s first self-designed aircraft, will undertake itsmaiden flight before the end of the year. COMAC chairman, Zhang Qingwei says this first homegrown regional jet has aroused great interest from aviation companies at home and abroad.”I just came back from the United States and Canada. ___________________________________________________________________________________________________________________________________________________________________________________________.”2)Nine top tier US manufacturing companies won competitive contracts to buildand supply the aviation system for China‘s new aircraft program, the C919.Airport infrastructure needs are filling opportunities in the US companies as well.___________________________________________________________________________________________________________________________________________________________________________________________________ 3)The Deputy Chief of the China’s Civic Aviation Administration, Xia Xinghua,says more cooperation is crucial for the Chinese side. “Firstly, we need to strengthen our cooperation on sustainable security development, expanding the relationship in a pragmatic way.________________________________________________________________________________________________________________________________________________________________________”4)The Transportation Secretary Ray LaHood said that the review would becomprehensive covering design, manufacturing and assembly of the Dreamliner.Michael Huerta of the Federal Aviation Administration said emphasis would be put on electrical systems and how these and the plane’s sophisticated mechanical systems interact._____________________________________________________________________________________________________________________________________________________________________________________.5)Though the tricycle arrangement may be most popular today, that was not alwaysthe case. The tail wheel undercarriage dominated aircraft design for the first four decades of flight and is still widely used on many small piston-engine planes.What makes this form of landing gear most attractive is its simplicity. Another potential advantage results from the fact that_____________________________ __________________________________________________________________________________________________________________________________ Part II Reading Comprehension(30%)Section 1 Skimming and Scanning (10%)Directions: In this section there are 10 incomplete statements. Based on the following passage, please complete the statements with the information given in the passage.Commercial aviation is an essential component of the global economy. The cost of aviation fuel is directly determined by the prevailing world price of oil, and it accounts for a major proportion of airplane operating costs. Several airline companies now add a fuel surcharge to the ticket cost of a commercial flight to compensate for the recent rapid rise in fuel costs. World oil prices are expected to remain high for several years. The prospect of sustained high aviation fuel prices could propel airline companies to seek alternative aviation fuels. Seeking alternative fuel could become paramount(最⾼的)for the airlineindustry should the peak-oil phenomenon actually occur.Breakthroughs and ResearchIt may become possible for super-cooled liquid hydrogen(氢)to eventually be used as an alternative fuel for some types of commercial airline service. Other alternative fuels may include high-density energy-storage technologies that result from breakthroughs in research in the areas of nanotechnology(纳⽶技术) and in high-temperature superconductivity(超导性). High-temperature superconductivity holds great promise for use in high-density energy-storage technology. Advances in nanotechnology could enable superconductive materials to eventually be manufactured at a cost that could justify their application in airliner propulsion. Electrical Storage and PropulsionEnergy stored in a superconductive storage technology could power electric motors that drive the identical propulsion fans that are found at the front-end of modern, “high-bypass” turbo-fan aircraft engines. Such fans provide up to 90% of the propulsive thrust of the turbo-fan engine. Each electrically powered propulsion fan may be driven by multiple (induction) lightweight electric motors during take-off. Some electric motors would “cut-out”under reduced power demand at cruising altitude so that the remaining motors will operate at higher efficiency (electric motors have poor part-load efficiency). Coanda fans may propel subsonic commercial aircraft that use high-density electrical storage technology. Such units were originally developed by physicist Henri Coanda and can operate at comparable efficiency and at comparable flight speeds as turbine-driven propulsion fans. Electrically powered aircraft that use either turbine propulsion fans or Coanda fans could be flown in thinner air at higher altitude (up to 65,000-feet) to reduce energy consumption (less drag on aircraft) on extended flights.The cooler air found at such altitudes could assist in keeping the superconductive energy storage systems functioning properly.Superconductive energy storage systems used in future commercial aircraft would likely be cooled by liquid nitrogen(氮). Both systems would need to be frequently recharged, which would likely be both energy-intensive as well as time consuming.It may be possible to design the energy storage systems along with their cooling systems to be removed and replaced during shorts layovers—such technology could help reduce the turn-around time of the aircraft. The introduction of superconductive energy storage systems in commercial aircraft in the long-term future would require that future airport terminals be equipped with power generation technology at or near the premises.Power GenerationThe number of electrically powered and hydrogen powered road and railway vehicles would likely increase during a post peak-oil period. Commuter aircraft that operate short-haul service could be powered by ethanol(⼄醇) or by hydrogen while future supersonic aircraft could use liquid hydrogen as fuel. The commercial aviation industry of the future (post peak oil) could likely require vast amounts of electric power to recharge superconductive energy storage systems, recharge liquid nitrogen cooling systems as well as to generate, compress and supercool large amounts of hydrogen.Modern commercial aircraft are energy intensive during take-off. Airports that serve metropolitan areas presently process continual processions of large long-distance aircraft during peak periods. Such aircraft could require between 300-Mw-hr and 1000-Mw-hr of power to undertake trans-oceanic flights at subsonic speed. The power requirements of a future electrically based commercial aviation industry could likely overwhelm the power generation industry of most developed nations. Major international airports may eventually need to generate electric power on-site to meet the energy needs of future fleets of electrically powered and hydrogen-fueled commercial aircraft. Airport power stations may be nuclear; use hydrogen fusion or be based on some other unconventional power generation technology that is still subject to research.Energy StorageThe ability to store large amounts of energy at or near major airports could gain importance during a post peak-oil period. Electric power could be purchased from the grid during their off-peak periods and put into short-term storage. Airport power stations that encounter off-peak periods could replenish(装满) airport energy storage systems that may include superconductive storage, flow batteries, hydraulic storage in hydroelectric dams in nearby mountains (coastal airports) or off-site pneumatic storage (subterranean salt domes that were emptied). Air that is exhausted from pneumatic storage systems may be sufficiently cold to assist in “replenishing” liquid nitrogen super-cooling systems.Power Regulation (Airports)Power stations that provide energy for air transportation use may have to be excluded from the regulatory framework. Most of the electrically powered airliners that will be recharged would be “foreign”owned, that is, the owners would be domiciled in adifferent jurisdiction(司法权) to where the aircraft would be recharged. The idea of regulators in one jurisdiction looking after the interests of parties who live, do business and pay taxes in another jurisdiction is quite ludicrous. Power stations that supply a future airline industry with electric power would need to be regulatory-free despite the “foreign”airline owners being “captive”customers. It would be possible for power to be supplied to a single airport by several small providers who compete against each other. Power providers and airline companies could negotiate deals, perhaps even on a daily basis. ConclusionFuture scientific breakthroughs are likely to occur in both nanotechnology and in superconductivity. High-density energy storage technologies could be the likely result and appear in the distant future. Electrically powered commercial aircraft that fly at subsonic speeds could appear in the future irrespective of whether or not peak-oil actually occurs. Alternative liquid fuels that are cost-competitive to fossil oil are also likely to appear and find applications in aviation. Large ground-effect aircraft (地效飞⾏器)that fly above water and that carry either passengers or freight between coastal cities are also likely appear in the future.1.The prospect of sustained high aviation fuel prices could propel airline companiesto seek _______________________.2.Breakthroughs in nanotechnology could enable _______________________ to beavailable in their application in airliner propulsion.3.Coanda fans were first developed by _______________________ .4._______________________ could be used to cool superconductive energystorage system used in future commercial aircraft.5._______________________, which operates short-haul service, could be poweredby ethanol(⼄醇) or by hydrogen.6.Future airport power stations may be_______________________; use hydrogenfusion or be based on some other unconventional power generation technology. 7.During a post peak-oil period, the ability to_______________________ at or nearmajor airports could gain importance.8.Power stations that provide energy for air transportation use are likely to be_______________________ from the regulatory framework.9.Electrically powered commercial aircraft that fly at _______________________speeds could appear in the future.10.Aircrafts flying above water and carrying either passengers or freight betweencoastal cities are called _______________________.Section 2 Reading Comprehension (10%)Directions: The following passage is followed by some questions. For each of them there are four choices marked A), B), C) and D). You should choose the best answer from the four choices.Living standards have soared during the twentieth century, and economists expect them to continue rising in the decades ahead. Does that mean that we humans can look forward to increasing Happiness?Not necessarily, warns Richard A. Easterlin, an economist at the University of Southern California, in his new book, Growth Triumphant: The Twenty-first Century in Historical Perspective. Easterlin concedes that richer people are more likely to report themselves as being happy than poorer people are. But steady improvements in the American economy have not been accompanied by steady increases in people’s self-assessments of their own Happiness.The explanation for this paradox(悖论) may be that people become less satisfied over time with a given level of income. In Easterlin’s word: “As incomes rise, the aspiration level does too, and the effect of this increase in aspirations is to vitiate (破坏) the expected growth in Happiness due to higher income.”Money can buy Happiness, Easterlin seems to be saying, but only if one’s amounts get bigger and other people aren’t getting more. His analysis helps to explain sociologist Lee Rainwater’s finding that Americans’perception of the income “necessary to get along” rose between 1950 and 1986 in the same proportion as actual per capita income. We feel rich if we have more than our neighbors, poor if we have less, and feeling relatively well-off is equated with being happy.Easterlin’s findings, challenge psychologist Abraham Maslow’s “hierarchy(等级) of wants” as a reliable guide to future human motivation. Maslow suggested that as people’s basic material wants are satisfied they seek to achieve nonmaterial or spiritual goals. But Easterlin’s evidence points to the persistence of materialism.“Despite a general level of affluence never before realized in the history of the world.” Easterlin observes, “Material concerns in the wealthiest nations today are as pressing as ever and the pursuit of material need as intense.” The evidence suggests there is no evolution toward higher order goals. Rather, each step upward on the ladder of economic development merely stimulates new economic desires that lead the chase ever onward.Needs are limited, but not greeds. Science has developed no cure for envy, so our wealth boosts our Happiness only briefly while shrinking that of our neighbors. Thus the outlook for the future is gloomy in Easterlin’s view. “The triumph of economic growth is not a triumph of humanity over material wants; rather, it is the triumph of material wants over humanity.”1.What does Easterlin warn in his new book?A)Humans can look forward to increasing happiness with soaring livingstandards.B)Humans might not be able to enjoy increasing happiness with soaring livingstandards.C)Richer people tend to report themselves as being happy more than poorerpeople do.D)Richer people tend to report themselves as being happy less than poorerpeople do.2.Which of the following statements may account for the paradox(悖论) mentionedin paragraph 3?A)People become less satisfied though the income rises over time.B)A general level of affluence never before realized in the history of the world.C)Though the American economy improved steadily, there isn’t a steadyincrease in people’s self-assessments of their own happiness.D)As incomes rise, there will be an increase in the aspiration level, which willhamper the expected growth in Happiness due to higher income.3.Whose finding is against the theory of “Hierarchy of wants”?A)Easterlin’s B) Maslow’s C) Rainwater’s D) Lee’s4.According to Easterlin, the outlook of the future of happiness is ________.A)bright B) sad C) unclear D) thrilling5.From the quotation in the end of the passage (paragraph 7), we can infer that___________?A)The triumph of economic growth results in more humanity.B)The triumph of economic growth results in more material wants.C)Humanity contributes more to the triumph of economic growth.D)Material wants contributes more to the triumph of economic growth.Section 3 Short Answer Questions (10%)Directions: Read the following passage and then answer the questions. The answer should not be more than 25 words.The maximum allowable weight for an aircraft is determined by design considerations. However, the maximum operational weight may be less than the maximum allowable weight due to such considerations as high-density altitude or high-drag field conditions caused by wet grass or water on the runway. The maximum operational weight may also be limited by the departure or arrival airport’s runway length.One important preflight consideration is the distribution of the load in the aircraft. Loading the aircraft so the gross weight is less than the maximum allowable is not enough. This weight must be distributed to keep the center of gravity (CG) within the limits specified in the POH or AFM.If the CG is too far forward, a heavy passenger can be moved to one of the rear seats or baggage can be shifted to a rear compartment. If the CG is too far aft, passenger weight or baggage can be shifted forward. The fuel load should be balanced laterally: the pilot should pay special attention to the POH or AFM regarding the operation of the fuel system, in order to keep the aircraft balanced in flight. Weight and balance of a helicopter is far more critical than for an airplane. With some helicopters, they may be properly loaded for takeoff, but near the end of a long flight when the fuel tanks are almost empty, the CG may have shifted enough for the helicopter to be out of balance laterally or longitudinally. Before making any long flight, the CG with the fuel available for landing must be checked to ensure it will be within the allowable range.Changes of fixed equipment may have a major effect upon the weight of the aircraft. The replacement of older, heavy electronic equipment with newer, lightertypes results in a weight reduction, which will probably cause the CG to shift and must be computed and annotated in the weight and balance record.Repairs and alteration are the major sources of weight changes. The A&P mechanic must compute the CG and record the new empty weight and EWCG in the aircraft weight and balance record.The A&P mechanic or repairman conducting an annual or condition inspection must ensure the weight and balance data in the aircraft records is current and accurate. It is the responsibility of the pilot in command to use the most current weight and balance data when operating the aircraft.Questions:1.What conditions might cause the operational weight of a plane to be less than themaximum allowable weight?2.What should be done if the CG is too far aft in an aircraft?3.Why is the weight and balance for a helicopter far more critical than for anairplane?4.According to the passage, what might lead to weight changes and cause the CG toshift in an aircraft?5.Who are responsible for recording and using the most current and accurate data ofthe weight and balance?Part III Translation (15%)Section 1 English-Chinese Translation (10%)Direction: In this section there are two passages in English. Please read these passages and translate the underlined parts into Chinese.Passage 1The airplane propeller consists of two or more blades and a central hub to which the blades are attached. 1) Each blade of an airplane propeller is essentially a rotating wing. As a result of their construction, the propeller blades are like airfoils and produce forces that create the thrust to pull, or push, the airplane through the air.The power needed to rotate the propeller blades is furnished by the engine. The engine rotates the airfoils of the blades through the air at high speeds, and the propeller transforms the rotary power of the engine into forward thrust.2) An airplane moving through the air creates a drag force opposing its forward motion. Consequently, if an airplane is to fly, there must be a force applied to it that is equal to the drag, but acting forward. This force is called “thrust.”Passage 2Aircraft flight control systems are classified as primary and secondary. 3) The primary control systems consist of those that are required to safely control an airplane during flight. Secondary control systems improve the performance characteristics of the airplane, or relieve the pilot of excessive control forces. Those included in the primary control systems are the ailerons, elevator (or stabilator), and rudder. Examples of secondary control systems are wing flaps and trim systems.Airplane control systems are carefully designed to provide a natural feel, and at the same time, allow adequate responsiveness to control inputs. 4) At low airspeeds, the controls usually feel soft and sluggish, and the airplane responds slowly to controlapplications. At high speeds, the controls feel firm and the response is more rapid.Movement of any of the three primary flight control surfaces changes the airflow and pressure distribution over and around the airfoil. These changes affect the lift and drag produced by the airfoil/control surface combination, and allow a pilot to control the airplane about its three axes of rotation.Design features limit the amount of deflection of flight control surfaces. For example, control-stop mechanisms may be incorporated into the flight controls, or movement of the control column and/or rudder pedals may be limited. The purpose of these design limits is to prevent the pilot from inadvertently overcontrolling and overstressing the aircraft during normal maneuvers.5) A properly designed airplane should be stable and easily controlled during maneuvering. Control surface inputs cause movement about the three axes of rotation. The types of stability an airplane exhibits also relate to the three axes of rotation. Section 2 Chinese-English Translation (5%)Direction: In this section there are five sentences in Chinese. Please translate them into English.1.太阳能动⼒飞机的平均飞⾏时速为70公⾥,暂时不会对商⽤飞机构成威胁。

SECTION 1: T rue and False<TOTAL20 marks>For each of the following, place a “T〞if the statement is “true〞, “F〞if the statement is false.(20 marks, 2 marks/ Question)___T__ petitive advantage is a unique strength relative to competitors, often based on quality, time, cost or, innovation.___F__2.Market share can be defined in both currency as well as in units sold. Because both ratios calculate market share, market share will be the same for a firm regardless which measurement is used.___F_3.A “high-involvement purchase〞usually involves a considerable amount of time researching the product and the product is a routine purchase.___T_ 4.A company engaged in environmental scanning is continually acquiring information on events occurring outside the organization to identify and interpret potential trends .__F__5.At the information search stage of the purchase decision process, a consumer compares the product with his or her expectations and is either satisfied or dissatisfied.____F__6.A cohesive marketing mix consists of the product, promotion, price, and personnel.____F__7.Publicity is any paid form of nonpersonal communication about an organization, good, service or idea by an identified sponsor.____T__8.Direct mail and catalog retailing are examples ofnonstore retailing.___F___9.Market segment would have a collection of prospective buyers that areready to buy。

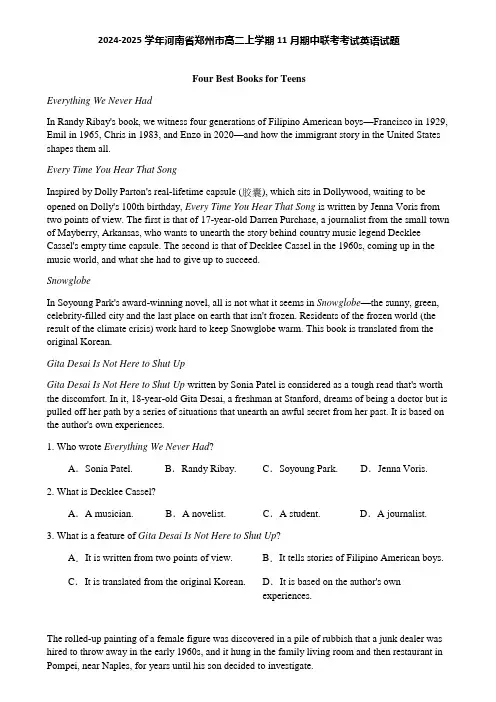

2024-2025学年河南省郑州市高二上学期11月期中联考考试英语试题Four Best Books for TeensEverything We Never HadIn Randy Ribay's book, we witness four generations of Filipino American boys—Francisco in 1929, Emil in 1965, Chris in 1983, and Enzo in 2020—and how the immigrant story in the United States shapes them all.Every Time You Hear That SongInspired by Dolly Parton's real-lifetime capsule (胶囊), which sits in Dollywood, waiting to be opened on Dolly's 100th birthday, Every Time You Hear That Song is written by Jenna Voris from two points of view. The first is that of 17-year-old Darren Purchase, a journalist from the small town of Mayberry, Arkansas, who wants to unearth the story behind country music legend Decklee Cassel's empty time capsule. The second is that of Decklee Cassel in the 1960s, coming up in the music world, and what she had to give up to succeed.SnowglobeIn Soyoung Park's award-winning novel, all is not what it seems in Snowglobe—the sunny, green, celebrity-filled city and the last place on earth that isn't frozen. Residents of the frozen world (the result of the climate crisis) work hard to keep Snowglobe warm. This book is translated from the original Korean.Gita Desai Is Not Here to Shut UpGita Desai Is Not Here to Shut Up written by Sonia Patel is considered as a tough read that's worth the discomfort. In it, 18-year-old Gita Desai, a freshman at Stanford, dreams of being a doctor but is pulled off her path by a series of situations that unearth an awful secret from her past. It is based on the author's own experiences.1. Who wrote Everything We Never Had?A.Sonia Patel. B.Randy Ribay. C.Soyoung Park. D.Jenna Voris.2. What is Decklee Cassel?A.A musician. B.A novelist. C.A student. D.A journalist.3. What is a feature of Gita Desai Is Not Here to Shut Up?A.It is written from two points of view. B.It tells stories of Filipino American boys.C.It is translated from the original Korean. D.It is based on the author's ownexperiences.The rolled-up painting of a female figure was discovered in a pile of rubbish that a junk dealer was hired to throw away in the early 1960s, and it hung in the family living room and then restaurant in Pompei, near Naples, for years until his son decided to investigate.The junk dealer's son Andrea Lo Russo said that his first inkling of the painting's origin came when he saw a Picasso in a middle school textbook, but neither his teacher nor his father was persuaded.His curiosity continued, and in his early 20s, Lo Russo drove to Paris and brought the painting to the Picasso Museum. "They looked, and they said, 'It is not possible, '" Lo Russo recalled. He turned down their invitation to leave the painting for further examination, not wanting to give it up.After decades of trying to determine the painting's origin, Lo Russo believed that a recent battery of tests carried out by the Swiss-based Arcadia Foundation finally offered proof that it's the work of Picasso. "We include lab tests that show the paints used are consistent with Picasso's color palette during the period," said Luca Marcante, a trained chemist who founded the Arcadia Foundation in 2000 to investigate the origin of artworks. "Most recently, a handwriting expert authenticated (证实) the signature on the upper left-hand corner as that of Picasso."The only group that can authenticate the painting is the Picasso Administration in Paris. It hasn't responded to a series of requests over the years. Marcante said that he was preparing to share the most recent findings with them. "The only real one is Lo Russo's because we have examined it in a scientific manner. We are completely sure about our work, and about the results science has given us," Marcante said. "We can touch this painting with our hands. It is real. It is authentic."4. What does the underlined word "inkling" in paragraph 2 probably mean?A.Thought. B.Decision. C.Lesson. D.Report.5. Why did Lo Russo drive to the Picasso Museum?A.To do some tests on his own. B.To pick up his father working there.C.To seek confirmation on a painting. D.To enjoy Picasso's paintings.6. What can be learned from Marcante's words in the last paragraph?A.He avoided touching the painting. B.He was confident of his judgement.C.He was a famous handwriting expert. D.He worked for the PicassoAdministration.7. Which word can best describe Lo Russo?A.Kind-hearted. B.Open-minded. C.Generous. D.Determined. Around the US, educators say students in class routinely send messages, listen to music and shop online. There are also countless other examples of how smartphones disturb teaching and learning. "Students used to have an understanding that they weren't supposed to be on their phone in class. Those days are gone," said James Granger, a high school teacher.The impact that phones have on teenagers in America today is well-documented, but teachers say parents are often not aware to what extent students use them inside the classroom. And increasingly, educators and experts are speaking with one voice on the question of how to handle it: No phones during classes.Last year, Florida became the first state to crack down on phones in school. A law that took effect in July required all Florida public schools to ban (禁止) student cellphone use during class time and block access to social media on district Wi-Fi. Some districts, including Orange County Public Schools, went further and banned phones the entire school day. Oklahoma, Vermont and Kansas have also recently introduced what is becoming known as the "phone-free schools" policy.Some students say such policies cut off their main mode of communication with family and friends. Pushback has also come from parents who fear being cut off from their kids if there is a school emergency. Jaden Willoughey, 14, shares the concern about being out of contact with his parents if there's a crisis."It took a few years to change the cellphone policy and find a system that worked," said Jared Christensen, the school's vice principal. "At first it was a battle. But it has been so worth it. Students are more attentive and engaged during class time. Teachers are able to teach without competing with cellphones. And student learning has increased," he said, citing test scores that were at or above state averages for the first time in years. "I can't definitively say it's because of this policy. But I know it's helping."8. What can we learn from paragraph 1?A.The functions of smartphones are increasing.B.Most of the Americans choose to shop online.C.Listening to music is good for students' mental health.D.More and more US students are using phones in class.9. Florida was the first state in America to ________.A.introduce a course on social media B.provide smartphones for poor kidsC.push for a cellphone ban in school D.allow students to use computers at school 10. What is Jaden Willoughey's attitude to the "phone-free schools" policy?A.Positive. B.Doubtful. C.Unconcerned. D.Unclear.11. Which statement will Jared Christensen probably agree with?A.There is competition among teachers. B.It is worthwhile to battle for freedom.C.His students have made little progress. D.The new cellphone policy is beneficial. Imagine a customer-service center that speaks your language, no matter what it is. Alorica, a company in Irvine, California, which runs customer-service centers around the world, has introduced an artificial intelligence (AI) translation tool that lets its workers talk with customers who speak 200 different languages and 75 dialects. So an Alorica worker who speaks, say, only Spanish can deal with a complaint about an incorrect bank statement from a Cantonese speaker in Hong Kong. And it wouldn't need to hire an employee who speaks Cantonese.However, Alorica isn't cutting jobs. It will increasingly hire those who are comfortable with new technology.Potentially, the threat: Perhaps companies won't need as many employees—and will cut some jobs—if chatbots can handle the workload instead. Consider Suumit Shah, an Indian businessman who caused an uproar last year by saying that he had replaced 90% of his customer support staff with a chatbot named Lina. The move at Shah's company, Dukaan, which helps customers set up e-commerce sites, reduced the response time to an inquiry from 1 minute, 44 seconds to "instant". It also cut the typical time needed to solve problems from more than two hours to just over three minutes.Similarly, researchers at Harvard Business School found in a study last year that job postings for writers, coders and artists decreased greatly within eight months of the arrival of ChatGPT.But being exposed to AI doesn't necessarily mean losing your job to it. The Swedish furniture retailer IKEA, for example, introduced a customer-service chatbot in 2021 to handle simple inquiries. Instead of cutting jobs, IKEA retrained 8,500 customer-service workers to handle such tasks as advising customers on interior design and fielding complex customer calls.The experience at Alorica and IKEA suggests that AI may not prove to be the job killer that many people fear. Instead, the technology might turn out to be more like breakthroughs of the past—the steam engine, electricity and the Internet, which get rid of some jobs while creating others and probably make workers more productive in general to the eventual benefit of workers themselves, their employers and the economy.12. What does the author want to tell us by the example in paragraph 1?A.The power of AI. B.The threat from humans.C.The customer requirements. D.The tips on language learning.13. What advantage does Lina have over other staff?A.Winning the trust of customers. B.Responding to customers faster.C.Selling more products to customers. D.Having a great relationship with Shah.14. What were IKEA's customer-service workers asked to do in 2021?A.Take on other duties. B.Leave their company.C.Move to HongKong. D.Develop latest chatbots.15. What is the best title for the text?A.How Will AI Change Our Lives? B.How Should We Use AI Effectively?C.Will AI Take Away Many Human Jobs? D.What Is the Future of TraditionalCompanies?How to Be Best FriendsThe relationship between best friends is one of the most important ones we experience in our lives. It's why we want to do as much as possible to make sure our best friend enjoys spending time with us. 16 . But every once in a while we need to remind ourselves of the things that make some friends more special than others.Stay together. Best friends don't have to do something crazy to have a good time. Sometimes, it's enough to go over to one of your houses and just hang out. Invite your friend over even when you don't have something special planned. 17 .Share happy moments. As you spend time together, there will be moments that cause the two of you to break into laughter. 18 . It'll make the two of you smile and start laughing again as well as remind both of you of all the happy moments that you've shared with each other.19 . We all have moments in life when we feel bad. If your friend is upset, talk to them and encourage them to express why they're feeling low. Try to see things from their perspective (角度) and offer comfort. They'll see how important they are to you and return the favor when you need it.Accept their weaknesses. No one is perfect. 20 . Don't try to change things about your friend that you think are bad or holding them back. They probably know what they are just as much as you do. In time, you may realize that these weaknesses are what drew the two of you together in the first place.One summer day in 2009, Megan Atherton was driving to her hometown of Pittsburgh. She was 23 years old and couldn't ______ to pay the rent for her apartment in Annapolis. She was ______ she could find a place to stay back home. But about an hour into the drive, Atherton's car ______. Even worse, her cellphone was dead because the ______ had been turned off in the apartment.______ to call for help, Atherton just stood on the side of the road. ______, the police arrived and helped her tow (拖) her car to a nearby repair shop. The ______ wasn't good: Her car would need repairs, which she didn't have ______ to cover.As she felt ______ about what to do next, a woman in the waiting room ______ her. The woman, who introduced herself as Toni, learned about Atherton's problem and offered to help her ______ for the car repair. Atherton was happy and grateful.Once she ______ the city, Atherton was able to find a homeless shelter and begin ______ her life. She never saw Toni again but thought of her often. "It was not possible that I ______ her enough. Itwas a very hard time in my life, and I honestly don't know what would have happened if she hadn't gone so far above and beyond for a ______," she said.21.A.stop B.pretend C.refuse D.afford22.A.worried B.relieved C.hopeful D.regretful23.A.broke down B.moved on C.slowed down D.sped up24.A.shower B.light C.electricity D.gas25.A.Ready B.Unable C.Expected D.Surprised26.A.Eventually B.Secretly C.Recently D.Proudly27.A.weather B.situation C.traffic D.job28.A.energy B.time C.money D.access29.A.excited B.certain C.curious D.lost30.A.approached B.attacked C.admired D.recommended 31.A.account B.pay C.apply D.look32.A.asked about B.searched for C.arrived in D.gave up33.A.replacing B.reporting C.remembering D.rebuilding 34.A.understood B.thanked C.needed D.forgave35.A.repairman B.policeman C.neighbor D.stranger阅读下面短文,在空白处填入1个适当的单词或括号内单词的正确形式。

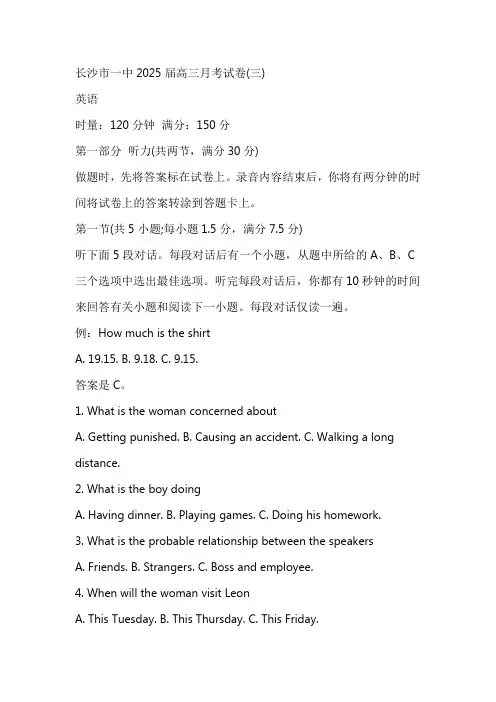

长沙市一中2025届高三月考试卷(三)英语时量:120分钟满分:150分第一部分听力(共两节,满分30分)做题时,先将答案标在试卷上。

录音内容结束后,你将有两分钟的时间将试卷上的答案转涂到答题卡上。

第一节(共5小题;每小题1.5分,满分7.5分)听下面5段对话。

每段对话后有一个小题,从题中所给的A、B、C 三个选项中选出最佳选项。

听完每段对话后,你都有10秒钟的时间来回答有关小题和阅读下一小题。

每段对话仅读一遍。

例:How much is the shirtA. 19.15.B. 9.18.C. 9.15.答案是C。

1. What is the woman concerned aboutA. Getting punished.B. Causing an accident.C. Walking a long distance.2. What is the boy doingA. Having dinner.B. Playing games.C. Doing his homework.3. What is the probable relationship between the speakersA. Friends.B. Strangers.C. Boss and employee.4. When will the woman visit LeonA. This Tuesday.B. This Thursday.C. This Friday.5. What did the woman speaker plan to doA. Do some fitness training.B. Meet friends.C. Attend a show.第二节(共15小题;每小题1.5分,满分22.5分)听下面5段对话或独白。

每段对话或独白后有几个小题,从题中所给的A、B、C三个选项中选出最佳选项。

听每段对话或独白前,你将有时间阅读各个小题,每小题5秒钟;听完后,各小题将给出5秒钟的作答时间。

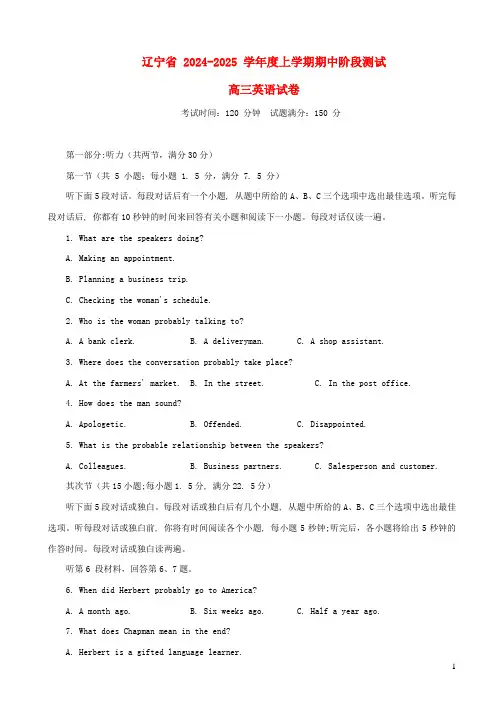

辽宁省 2024-2025 学年度上学期期中阶段测试高三英语试卷考试时间:120 分钟试题满分:150 分第一部分:听力(共两节,满分30分)第一节(共 5 小题;每小题 1. 5 分,满分 7. 5 分)听下面5段对话。

每段对话后有一个小题, 从题中所给的A、B、C三个选项中选出最佳选项。

听完每段对话后, 你都有10秒钟的时间来回答有关小题和阅读下一小题。

每段对话仅读一遍。

1. What are the speakers doing?A. Making an appointment.B. Planning a business trip.C. Checking the woman's schedule.2. Who is the woman probably talking to?A. A bank clerk.B. A deliveryman.C. A shop assistant.3. Where does the conversation probably take place?A. At the farmers' market.B. In the street.C. In the post office.4. How does the man sound?A. Apologetic.B. Offended.C. Disappointed.5. What is the probable relationship between the speakers?A. Colleagues.B. Business partners.C. Salesperson and customer.其次节(共15小题;每小题1. 5分, 满分22. 5分)听下面5段对话或独白。

每段对话或独白后有几个小题, 从题中所给的A、B、C三个选项中选出最佳选项。

听每段对话或独白前, 你将有时间阅读各个小题, 每小题5秒钟;听完后,各小题将给出5秒钟的作答时间。

剑桥雅思阅读10真题解析(test2)雅思阅读部分的真题资料,同学们需要进行一些细致的总结,比如说解析其实就是很重要的内容,接下来就是店铺给同学们带来的关于剑桥雅思阅读10真题解析(test2)的内容,一起来详细的分析一下吧,希望对你们的备考有所帮助。