EDA技术与VHDL 实验指导书

哈尔滨理工大学荣成学院

电气工程系

2013年11月20日

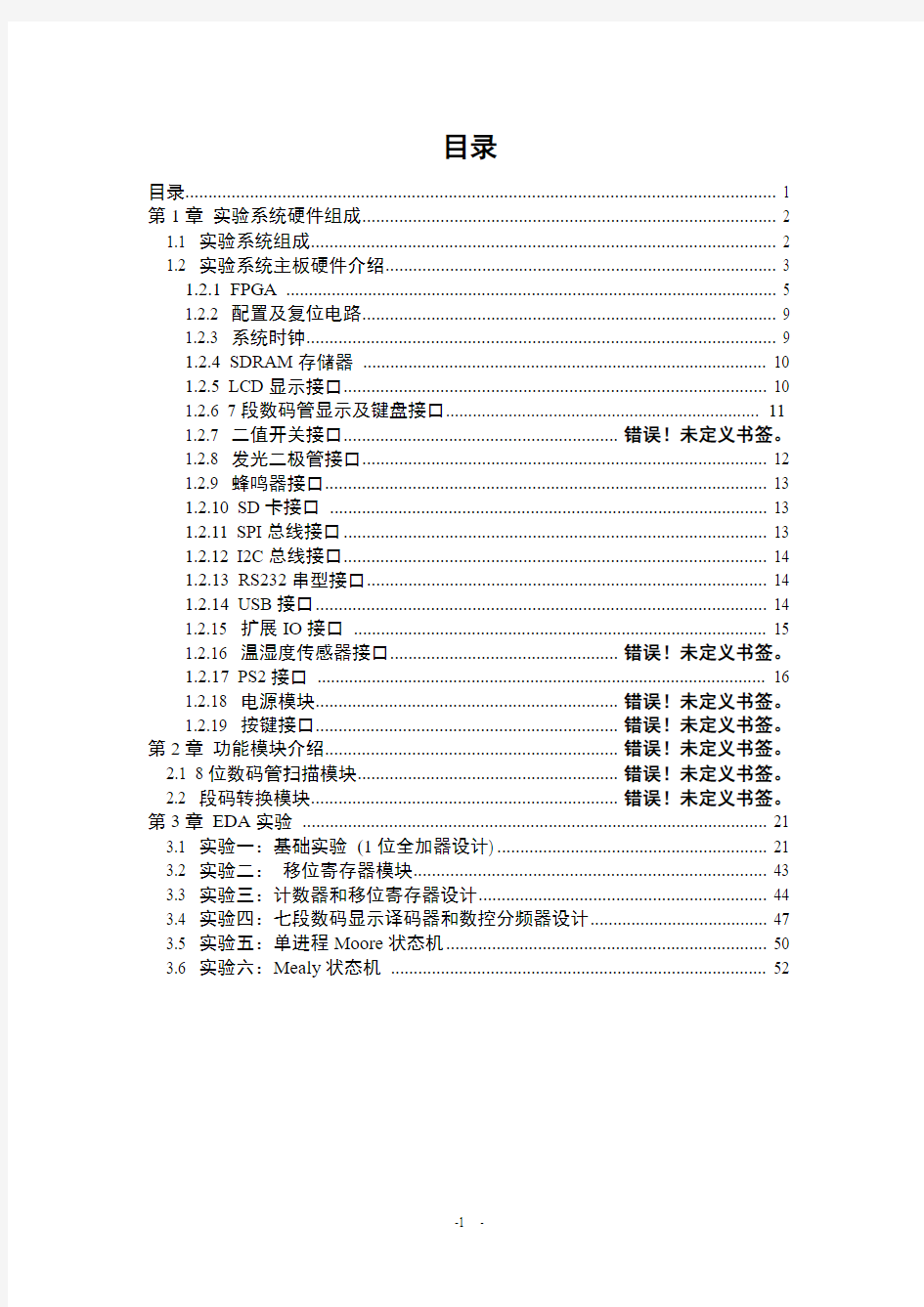

目录

目录 (1)

第1章实验系统硬件组成 (2)

1.1 实验系统组成 (2)

1.2 实验系统主板硬件介绍 (3)

1.2.1 FPGA (5)

1.2.2 配置及复位电路 (9)

1.2.3 系统时钟 (9)

1.2.4 SDRAM存储器 (10)

1.2.5 LCD显示接口 (10)

1.2.6 7段数码管显示及键盘接口 (11)

1.2.7 二值开关接口............................................................ 错误!未定义书签。

1.2.8 发光二极管接口 (12)

1.2.9 蜂鸣器接口 (13)

1.2.10 SD卡接口 (13)

1.2.11 SPI总线接口 (13)

1.2.12 I2C总线接口 (14)

1.2.13 RS232串型接口 (14)

1.2.14 USB接口 (14)

1.2.15 扩展IO接口 (15)

1.2.16 温湿度传感器接口.................................................. 错误!未定义书签。

1.2.17 PS2接口 (16)

1.2.18 电源模块.................................................................. 错误!未定义书签。

1.2.19 按键接口.................................................................. 错误!未定义书签。第2章功能模块介绍................................................................ 错误!未定义书签。

2.1 8位数码管扫描模块......................................................... 错误!未定义书签。

2.2 段码转换模块................................................................... 错误!未定义书签。第3章EDA实验 (21)

3.1 实验一:基础实验(1位全加器设计) (21)

3.2 实验二:移位寄存器模块 (43)

3.3 实验三:计数器和移位寄存器设计 (44)

3.4 实验四:七段数码显示译码器和数控分频器设计 (47)

3.5 实验五:单进程Moore状态机 (50)

3.6 实验六:Mealy状态机 (52)

第1章实验系统硬件组成

1.1实验系统组成

实验系统由一台计算机+实验箱组成。实验系统连接如图1-1所示。

图1-1 CH-4实验系统连接图

实验箱由箱体+ USB Blaster 下载线+开关电源+实验系统主板+扩展板组成。

1.箱体:开关电源固定在箱体的底板上,在箱体的后侧板开有电源插孔,接~220V 电

源。

2. USB Blaster 下载线:通过连接计算机的USB 接口在实验箱上连接到EP4CE15 核心板

的JTAG 口,也可连到它的AS 口。

3.开关电源:型号:台湾明纬T-30B 。输入~220V,输出+5V/3A +12V/1A -12V/0.5A。

4.实验系统主板:板载基础实验所需电路,配置如下:

FPGA:EP4CE15N(15408Les)

配置芯片:M25P64 (64MB)

FLASH: AM29LV320D (32MB)

SDRAM:H57V2562GTR (256MB)

TFT屏:5.0吋TFT LCD屏,屏幕分辨率800x480。颜色位16M色。

2 x16 字符点阵液晶(蓝白)1 块。

数码管(动态扫描):LG5641AHx2 8 位7 段数码管0.5 吋共阴红

数码管(静态驱动):2 位共阴静态驱动数码管,红色。

按键: 4 位OMRON 按键。

键盘:4x4 OMRON 按键。

上电及手动复位电路:

蜂鸣器:5V 无源蜂鸣器 1 个;

5V 有源蜂鸣器1 个。

温度传感器:DS18B20 温度传感器。

实时时钟电路:DS1302。

铁电存储器:AT24C16(16KB)。

SD 卡接口:

PS2 接口:

串口:MAX3232。

USB 接口:真正的USB 接口,分HOST 和SLA VE 接口设计,CH376 驱动。

扩展接口座(20P):20IO 用于与扩展板通信设计。

5. 组成原理/数字逻辑扩展板:EDA_DSA 实验箱中提供连接好的扩展板是组成原理/数字逻辑基础实验模块,实验系统主板通过 4 位IO 口控制组成原理/数字逻辑扩展板的发光

二极管、二值开关、脉冲开关等输入输出资源。

组成原理/数字逻辑扩展模块配置如下:

面包板1 块:

●一个端子条300 个插孔

●两个分配条,100 个插孔

●适用线径:29-20 AWG

●尺寸:83.5x54.5x8.5mm;8.2x5.3x0.85cm

面包板相关实验IO 接口:

LED 发光二极管8 个

二值开关8 位

LED 发光二极管20 个

二值开关20 位

触发按键(上升沿) 2 位

触发按键(下降沿) 2 位

控制器CPLD EPM240T100C5N 1 片

4 路拨码控制,用于设计时钟实验:

1Hz,10Hz,100Hz,1KHz,10KHz,100Khz,1MHz,10MHz 等,分别

用BCD 拨码开关选择,掉电时设置值不丢失。

1.2实验系统主板硬件介绍

ZY-EDA2 实验系统主板硬件结构框图如图2-2 所示。

图1-2 ZY-EDA2 实验系统主板硬件结构框图ZY-EDA2 实验系统主板器件位置如图1-3所示。

图1-3 ZY-EDA2 实验系统主板器件位置

1.2.1FPGA

实验系统使用的FPGA 芯片是芯片是美国Altera 公司的CycloneIV 系列的FPGA 芯片EP4C15E, 基本性能指标如表1-1所示。

表1-1 EP3C16Q240C8基本性能指标

逻辑单元(LEs)15,408

存储器(Kb)504

乘法器56

PLLs 4

全局时钟网络20

I/O引脚数343(最大)

EP4CE15 IO 接口连接如图1-4所示。

图1-4 EP4CE15 IO接口连接图

EP4CE15 与主板上时钟、存储器、LCD、键盘、7 段数码管等电路模块接口分配如表1-2所示。

表1-2 EP4CE15 与主板上IO 接口模块引脚分配AD_OE Output PIN_C14 AD 使能控制

BP_CTR Output PIN_G11 无源蜂鸣器控

制

BUZ_DRV Output PIN_E11 有源蜂鸣器控

制CLOCK Input PIN_R9 系统时钟

DA_CS Output PIN_D12 DA 使能

DA_DIN Output PIN_F13 DA 数据线DBA[7] Output PIN_C3 A 组总线

DBA[6] Output PIN_E6

DBA[5] Output PIN_D6

DBA[4] Output PIN_D8

DBA[3] Output PIN_F8

DBA[2] Output PIN_E9

DBA[1] Output PIN_D9

DBA[0] Output PIN_E10

DBB[7] Output PIN_N11 B 组总线

DBB[6] Output PIN_M10

DBB[5] Output PIN_N9

DBB[4] Output PIN_L7

DBB[3] Output PIN_N8

DBB[2] Output PIN_M7

DBB[1] Output PIN_P6

DBB[0] Output PIN_N5

DBC[7] Bidir PIN_C11 C 组总线

DBC[6] Bidir PIN_C9

DBC[5] Bidir PIN_F9

DBC[4] Bidir PIN_E8

DBC[3] Bidir PIN_E7

DBC[2] Bidir PIN_C6

DBC[1] Bidir PIN_D5

DBC[0] Bidir PIN_D3

DS18DAT Bidir PIN_R1 温度传感器数

据线

EEP_SDA Bidir PIN_F3 铁电存储器数

据线

EP_INT Input PIN_M15 与扩展板接口EPDB[7] Bidir PIN_P11 与扩展板接口EPDB[6] Bidir PIN_M9

EPDB[4] Bidir PIN_M8

EPDB[3] Bidir PIN_P8

EPDB[2] Bidir PIN_M6

EPDB[1] Bidir PIN_N6

EPDB[0] Bidir PIN_K6

F_ASDO Output PIN_C1 Flash 接口

F_DATA0 Input PIN_H2

F_DCLK Output PIN_H1

F_NCS Output PIN_D2

LCM_EN Output PIN_P2 1602使能控制PIO_LED[3] Output PIN_K2 核心板LED PIO_LED[2] Output PIN_K1

PIO_LED[1] Output PIN_J2

PIO_LED[0] Output PIN_J1

PS2_DAT Input PIN_R8 PS2接口

PS2_INT Input PIN_M2

RESET Input PIN_M1 系统复位RXD Input PIN_A8 串口接收

S_A[12] Output PIN_A4 SDRAM 接口S_A[11] Output PIN_B5

S_A[10] Output PIN_D16

S_A[9] Output PIN_A5

S_A[8] Output PIN_B6

S_A[7] Output PIN_A6

S_A[6] Output PIN_B7

S_A[5] Output PIN_A7

S_A[4] Output PIN_C8

S_A[3] Output PIN_G16

S_A[2] Output PIN_G15

S_A[1] Output PIN_F16

S_A[0] Output PIN_F15

S_BA[1] Output PIN_D15

S_BA[0] Output PIN_C16

S_CAS Output PIN_A15

S_CKE Output PIN_B4

S_CLK Output PIN_A3

S_DB[15] Bidir PIN_G1

S_DB[14] Bidir PIN_G2

S_DB[13] Bidir PIN_F1

S_DB[12] Bidir PIN_F2

S_DB[11] Bidir PIN_D1

S_DB[10] Bidir PIN_C2

S_DB[8] Bidir PIN_A2

S_DB[7] Bidir PIN_B13

S_DB[6] Bidir PIN_A13

S_DB[5] Bidir PIN_B12

S_DB[4] Bidir PIN_A12

S_DB[3] Bidir PIN_B11

S_DB[2] Bidir PIN_A11

S_DB[1] Bidir PIN_B10

S_DB[0] Bidir PIN_A10

S_DQM[1] Output PIN_B3

S_DQM[0] Output PIN_A14

S_NCS Output PIN_C15

S_NWE Output PIN_B14

S_RAS Output PIN_B16

SCLK Output PIN_D11 串行时钟SD_CS Output PIN_F14 SD 使能

SHBIT_VGAVS Output PIN_P1 动态数码管位选(复用VGAVS)

SHSEG_VGAB Output PIN_N1 动态数码管段选(复用VGAB)

SK1_EPWR Bidir PIN_L6 独立按键(复用与扩展板接口)

SK2_EPRD Bidir PIN_N3

SK3_EPOE Bidir PIN_L4

SK4_EPRSV Bidir PIN_T3

T_CS Output PIN_D14

T_IRQ Input PIN_E15

TDIN_SDMOSI Input PIN_J12

TDOUT_SDMIS

O

Output PIN_K10

TFT_BL Output PIN_L8 TFT 背光控制

TFT_CS Output PIN_T2 TFT 使能控制TFT_RD Output PIN_K5 TFT 读控制

TFT_RST Output PIN_R3 TFT 复位

TFTRS_LCMRS Output PIN_P3 TFT 数据指令(复用1602数据指令)

TFTWR_LCMWR Output PIN_L3

TFT 写控制(复用1602写控制)

TXD Output PIN_G5 串口接收

USB_A0 Output PIN_K9 USB 接口

USB_INT Input PIN_E16

USB_RD Output PIN_L10

USB_WR Output PIN_J14

VGA_HS Output PIN_L1

VGAG_RTCDAT Bidir PIN_L2 VGAG(复用

RTC 数据)VGAR_RTCRST Output PIN_N2 VGAR(复用

RTC 复位)

1.2.2配置及复位电路

配置及复位电路如图2-5所示。配置芯片采用意法公司的M25P64,容量为64M。EP4CE15可用JTAG、AS 接口配置。可用JTAG 接口将*.sof 文件直接下载到EP4CE15 中;也可用AS 接口将*.pof 配置信息写到M25P64 中。在配置过程中CONFIG_DONE 指示灯将亮,如需重新配置按nCONFIG 按钮。

图1-5 配置及复位电路

1.2.3系统时钟

系统时钟电路设计为双时钟,如图2-6 所示。系统采用3528 表贴封装的 4 脚有源晶振,输出频率为40/50MHz。

图1-6 系统时钟电路

1.2.4SDRAM存储器

EP4CE15 扩展存储器电路如图1-7 所示。扩展存储器型号是HY57V256, 存储结构为4Banks x 16M x 16Bit 的256MB SDRAM。

图1-7 SDRAM 存储器电路

1.2.5TFT及LCD显示接口

系统中LCD 显示屏分别由 5.0 寸TFT 液晶屏和LCD1602 字符液晶构

成。TFT 结构框图如图1-8 所示。。

图1-8 LCD显示接口硬件结构框图

LCD 显示接口电路如图1-9 所示。

图1-9 LCD显示接口电路

1.2.67段数码管显示及键盘接口

7段数码管显示及键盘接口电路如图1-10所示。

图中7 段数码管共8 位,8 位段控由芯片74HCT573 驱动。键盘是4X4 矩阵键盘,矩阵4 行为输出,4 列为输入。

图1-10 7段数码管显示及键盘接口

1.2.7矩阵键盘接口

矩阵键盘接口电路如图2-11 所示。矩阵键盘由4*4 按键排设构成。

图1-11 矩阵键盘接口电路

1.2.8独立按键接口

独立按键接口电路如图1-12 所示。配置有 4 个独立按键。

图1-12 发光二极管接口电路

1.2.9蜂鸣器接口

蜂鸣器分别采用了有源和无源的设计,主要目的是让学员更好的理解蜂鸣器的驱动原理。接口电路如图2-13 所示。

图1-13 蜂鸣器接口电路

1.2.10SD卡接口

SD卡接口电路如图1-14所示。

图1-14 SD卡接口电路

1.2.11串行总线接口

接口实例采用DA TLC5615 ,电路如图1-15所示。

图1-15 串行总线接口电路

1.2.12I2C总线接口

I2C 总线接口实例采用铁电存储器AT24C16,,电路如图1-16所示。

图1-16 I2C总线接口电路

1.2.13RS232串型接口

RS232接口电路如图1-17所示。芯片为MAX3232。

图1-17 RS232串型接口

1.2.14USB接口

USB 接口电路如图1-18 所示。采用芯片为CH376 USB 接口芯片。

图1-18 USB接口电路

1.2.15并行接口

实例设计为AD 转换器TLC5510。接口电路如图1-19 所示。

图1-19 扩展IO接口电路

1.2.16VGA接口

接口电路如图如图1-20所示。

图1-20 VGA 接口电路

1.2.17PS2接口

PS2接口电路如图1-21所示。

图1-21 PS2接口电路

1.3组成原理/数字逻辑扩展模块硬件结构框图

组成原理/数字逻辑扩展板结构框图如图1-22 所示。

可在组成原理/数字逻辑扩展模块面包板上插些器件做接口扩展实验,面包板周围的8位LED 发光二极管(LED7~LED0)、8 位二值开关(SW7~SW0)、电源插孔(±12V、+5V、+3.3V、GND)、16 位IO 插口(IO0~IO15)等可用作扩展实验的电源、输入输出接口。

面包板结构如图1-23 所示。

上下两窄条面包板中每一行25(5x5)个孔连在一起,中间的面包板每竖列的5 个孔连在一起,图中已标出。

图1-22 组成原理/数字逻辑扩展模块结构框图

图1-23 面包板结构图

组成原理/数字逻辑扩展模块上的20 位LED 发光二极管(LED20~LED1),20 位二值开关(S20~S1), 4 位单脉冲按钮(T1~T4)通过 4 位IO 口与实验主板上的CPLDEMP240T100C5 连接,通过与主板的连接接口可以实现通信控制。

包括的外设资源:

1. CPLD 控制核心电路:

2.LED 和二值开关,通过二值开关输入电平控制信号,通过LED 可以输出显示状态:

3.微动开关设计电路:

4.拨动开关设计时钟输出实例:

5.CPLD 用于连接面包板做扩展实验电路: