一、为什么一定要搞定

为什么一定要搞定

时序分析在ASIC设计中的重要性毋须多说(我也不甚了解)。在FPGA设计中,很少进行细致全面的时序约束和分析,Fmax是最常见也往往是一个设计唯一的约束。这一方面是由FPGA的特殊结构决定的,另一方面也是由于缺乏好用的工具造成的。好的时序约束可以指导布局布线工具进行权衡,获得最优的器件性能,使设计代码最大可能的反映设计者的设计意图。

花些功夫在静态时序分析上既可以保证设计质量,也可以促使设计者再认识自己的代码。这后一点,对于我们这些逻辑设计初学者来说,尤为重要。从门级(在Altera的FPGA 器件中是LE级)再认识自己的代码,可以更深入地体会语言的特点,也可以更深入地理解综合工具对语言的处理,对于设计能力的提高帮助很大。

TimeQuest是Altera在6.0版的软件中加入的具备ASIC设计风格的静态时序分析(STA)工具。通过初步试用和观看网络教程,我感觉TimeQuest确实比Timng Analyzer 功能强大一些,而且使用界面比较友好,易于进行深入的时序约束和结果分析。

TimeQuest采用Synopsys Design Constraints(SDC)文件格式作为时序约束输入,不同于Timing Analyzer采用的Quartus Settings File(QSF)约束文件。这正是TimeQuest 的优点:采用行业通用的约束语言而不是专有语言,有利于设计约束从FPGA向ASIC设计流程迁移;有利于创建更细致深入的约束条件。

二、时序分析基本概念

时序分析基本概念

以下内容译自Quartus II Version 10.0 Handbook, Volume 3:Verification的SectionII 7.3:Timing Analysis Overview部分。

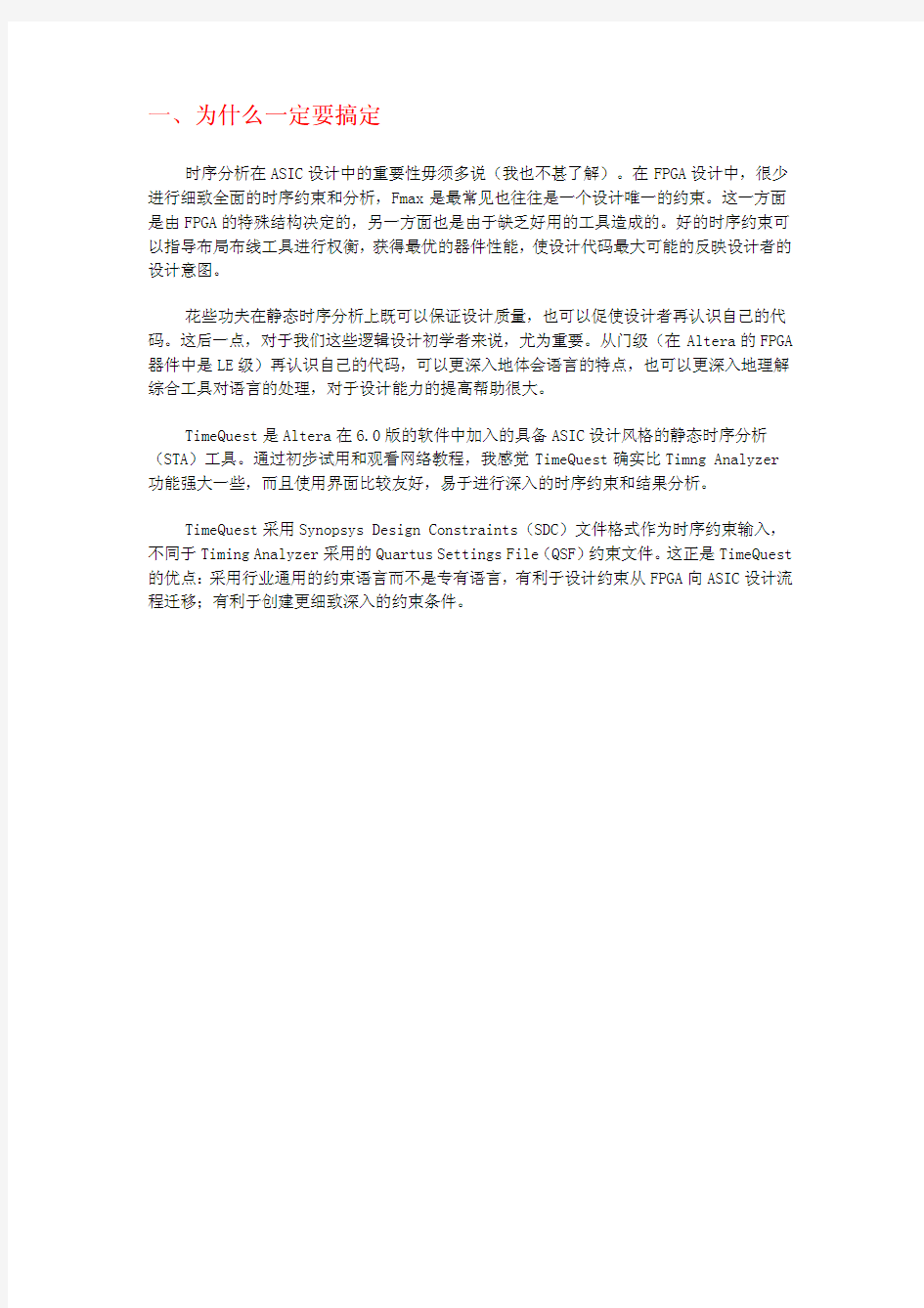

TimeQuest需要读入布局布线后的网表才能进行时序分析。读入的网表是由以下一系列的基本单元构成的:

1. Cells:Altera器件中的基本结构单元(例如,查找表、寄存器、IO单元、PLL、存储器块等)。LE可以看作是Cell。

2. Pins:Cell的输入输出端口。可以认为是LE的输入输出端口。注意:这里的Pins 不包括器件的输入输出引脚,代之以输入引脚对应LE的输出端口和输出引脚对应LE的输入端口。

3. Nets:同一个Cell中,从输入Pin到输出Pin经过的逻辑。特别注意:网表中连接两个相邻Cell的连线不被看作Net,被看作同一个点,等价于Cell的Pin。还要注意:虽然连接两个相邻Cell的连线不被看作Net,但是这个连线还是有其物理意义的,等价于Altera器件中一段布线逻辑,会引入一定的延迟(IC,Inter-Cell)。

4. Ports:顶层逻辑的输入输出端口。对应已经分配的器件引脚。

5. Clocks:约束文件中指定的时钟类型的Pin。不仅指时钟输入引脚。

6. Keepers:泛指Port和寄存器类型的Cell。

7. Nodes:范围更大的一个概念,可能是上述几种类型的组合,还可能不能穷尽上述几种类型。

下面这幅图给出了一个时序网表的示例,展示了基本单元中的一部分。

有了网表的 基本单元,我们就可以描述TimeQuest进行时序分析的对象:Edges。

Edges:Port-Pin,Pin-Pin,Pin-Port的连接关系都是Edges。注意,这里的Pin-Pin 连接关系既包括Cell内部的连接(Net),也包括相邻Cell外部的Pin-Pin连接。

Edges根据起止路径分为三类。

1. Clock paths:从Clock Port或内部生成的clock Pin到寄存器Cell的时钟输入Pin。

2. Data paths:从输入Port到寄存器Cell的数据输入Pin,或从寄存器Cell的数据输出Pin到另一个寄存器Cell的数据输入Pin。

3. Asynchronous paths:从输入Port到寄存器Cell的异步输入Pin,或从寄存器Cell的数据输出Pin到另一个寄存器Cell的异步输入Pin。

下面这幅图给出了三种不同的Edges。

还要注意这样一组概念,这里的edge指的是时钟沿:

1. Launch Edge:前级寄存器发送数据对应的时钟沿,是时序分析的起点。

2. Latch Edge:后级寄存器捕获数据对应的时钟沿,是时序分析的终点。

下面这幅图给出了发送、捕获时钟沿的示意图。本例在launch edge(0 ns)时寄存器reg1发送数据,在latch(5 ns)时寄存器reg2捕获数据。

r -

to to-

-register paths register paths))

Clock path 的延时 + 前级寄存器Cell 从时钟的延时。

Clock path 的延时 (+ uTh)或(-

uTsu)。

Clock path 的延时。

从外部输入引脚到内部寄存器从外部输入引脚到内部寄存器((path from an input port to a internal register path from an input port to a internal register))

Delay to Destination Register – μtSU.

从内部寄存器到从内部寄存器到输出输出输出引脚引脚引脚((path path from from from an internal register to an output port an internal register to an output port an internal register to an output port)) (1)Clock Setup Slack = Data Required Time – Data Arrival Time FPGA---->外部器件

在下一篇分析建立时间和保持时间时,就必须用到上述三个概念。

三、时序分析基本公式

时序分析基本公式

以下内容译自Quartus II Version 7.0 Handbook, Volume 3:Verification的6-28:Clock Analysis部分。

TimeQuest静态时序分析的对象包括:寄存器和寄存器之间的路径、I/O之间、I/O和寄存器之间的路径、异步复位和寄存器之间的路径。TimeQuest根据Data Arrival Time和Data Required Time计算出时序余量(Slack)。当时序余量为负值时,就发生了时序违规(Timing Violation)。

需要特别指出的一点是:由于时序分析是针对时钟驱动的电路进行的,所以分析的对象一定是“寄存器-寄存器”对。在分析涉及到I/O的时序关系对时,看似缺少一个寄存器分析对象,构不成“寄存器-寄存器” 对,其实是穿过FPGA的I/O引脚,在FPGA外部虚拟了一个寄存器作为分析对象。

一、 建立时间(Setup Time)检查:

遵循的原则是信号从Launch edge开始计时,经过一系列的时序路径,到达后级寄存器的数据输入Pin的速度不能太慢,时间不能太长,否则会侵占后级寄存器数据输入Pin

相对于Latch edge的建立时间。刚好满足后级寄存器建立时间的数据到达时间是Data Required Time(相对于Latch edge计算),实际的数据到达时间是Data Arrival Time(相对于Launch edge计算)。显然,在建立时间检查中,Data Arrival Time要小于Data Required Time,否则就会造成建立时间违规。也就是说,Data Required Time是Data Arrival Time 的最大值。二者之差就是建立时间的时序余量。

1)寄存器-寄存器(Register-to-Register)路径检查:

Clock Setup Slack = Data Required Time – Data Arrival Time

Data Arrival Time = Launch Edge + Clock Network Delay Source Register +μtco + Register-to-Register Delay

Data Required Time = Clock Arrival Time – μtsu – Setup Uncertainty

Clock Arrival Time = Latch Edge + Clock Network Delay to Destination Register

2)输入引脚-寄存器(Pin-to-Register)路径检查:

外部器件--->FPGA

Clock Setup Slack Time = Data Required Time – Data Arrival Time

Data Arrival Time = Launch Edge + Clock Network Delay to Source Register + Input Maximum Delay of Pin + Pin-to-Register Delay

Data Required Time = Clock Arrival Time – μtsu

Clock Arrival Time = Latch Edge + Clock Network Delay to Destination Register

3) 寄存器-输出引脚(Register-to-Pin)路径检查:

Clock Setup Slack Time = Data Required Time – Data Arrival Time

Data Arrival Time = Launch Edge + Clock Network Delay to Source Register + μtco + Register-to-Pin Delay

Data Required Time = Clock Arrival Time – Output Maximum Delay of Pin

Clock Arrival Time = Latch Edge + Clock Network Delay to Destination Register

从上面三组公式可以看出:Data Arrival Time的前两项是相同的;Data Required Time 的第一项是相同的;Clock Arrival Time的公式是相同的。

所以,第一组公式可以归纳如下:

Clock Setup Slack Time = Data Required Time – Data Arrival Time

Data Arrival Time = 时钟到达前级寄存器的时刻 + 前级寄存器时钟到后级寄存器数据输入的延迟

Data Required Time = 时钟到达后级寄存器的时刻 – 后级寄存器的建立时间

其中,后两个公式的第二项在其他情况下适当修改即可。

这就和一些书中讲到时序分析时采用的公式一致了。

report_timing -from [get_registers reg1] -to [get_registers reg2] -setup

-npaths 1 -panel_name "Report Timing"

二、 保持时间(Hold Time)检查:

遵循的原则是信号从Launch edge开始计时,经过一系列的时序路径,到达后级寄存器的数据输入Pin的速度不能太快,时间不能太短,否则会侵占后级寄存器数据输入Pin

相对于上一个Latch edge的保持时间。刚好满足后级寄存器保持时间的数据到达时间是Data Required Time(相对于Latch edge计算),实际的数据到达时间是Data Arrival Time (相对于Launch edge计算)。显然,在保持时间检查中,Data Arrival Time要大于Data Required Time,否则就会造成保持时间违规。也就是说,Data Required Time是Data Arrival

Time的最小值。二者之差就是保持时间的时序余量。

相对于建立时间检查,保持时间检查稍微难懂一些。二者都是同步逻辑设计中对同一个规则的不同解释:当前时钟沿发出的数据要在下一个时钟沿被正确捕获,不能晚,也不能早。晚了,会造成下一个时钟沿的建立时间违规,当前时钟沿发送的数据不能被下一个时钟沿捕获;早了,会造成上一个时钟沿发送的数据保持时间违规,上一个时钟沿发送的数据不能被当前时钟沿正确捕获。

二者在计算公式上的区别在于Slack计算公式中减数与被减数关系。

1)寄存器-寄存器(Register-to-Register)路径检查:

Clock Hold Slack = Data Arrival Time – Data Required Time

Data Arrival Time = Launch Edge + Clock Network Delay to Source Register +μtCO + Register to Register Delay

Data Required Time = Clock Arrival Time + μtH + Hold Uncertainty

Clock Arrival Time = Latch Edge + Clock Network Delay to Destination Register

2)输入引脚-寄存器(Pin-to-Register)路径检查:

Clock Setup Slack Time = Data Arrival Time – Data Required Time

Data Arrival Time = Launch Edge + Clock Network Delay to Source Register + Input Minimum Delay of Pin + Pin to Register Delay

Data Required Time = Clock Arrival Time + μtH

Clock Arrival Time = Latch Edge + Clock Network Delay to Destination Register

3) 寄存器-输出引脚(Register-to-Pin)路径检查:

Clock Setup Slack Time = Data Arrival Time – Data Required Time

Data Arrival Time = Launch Edge + Clock Network Delay to Source Register + μtCO + Register to Pin Delay

Data Required Time = Clock Arrival Time – Output Minimum Delay of Pin

Clock Arrival Time = Latch Edge + Clock Network Delay to Destination Register

需要注意的是,上面公式中的Latch Edge实际对应的是上一个Launch Edge。所以,当Launch Clock和Latch Clock是同一个时钟时,上述公式中的Latch Edge等于0;当前级和后级时钟不同时,还需要具体计算Latch Edge的取值。

report_timing -from [get_registers reg1] -to [get_registers reg2] -hold

-npaths 1 -panel_name "Report Timing"

三、 恢复时间(Recovery Time)检查:

遵循的原则是异步控制信号变化的时刻不能介于寄存器的Latch edge和相应的建立时间之间,否则会导致寄存器的建立时间违规,数据输出进入亚稳态。即从前级寄存器的Launch edge开始计时,经过一系列的时序路径,前级寄存器数据输出到达后级寄存器异步控制Pin的速度不能太慢,时间不能太长,否则会破坏后级寄存器在Latch edge的数据建立时间。该检查主要应用于异步控制信号由有效电平向无效电平转换的时刻,在该时刻破坏数据建立时间会导致亚稳态;在异步控制信号由无效电平向有效电平转换的时刻破坏数据的建立时间不会造成亚稳态。

从上述定义,可以得到和建立时间检查类似的公式。

1)寄存器-寄存器(Register-to-Register)路径检查:

Recovery Slack Time = Data Required Time – Data Arrival Time

Data Arrival Time = Launch Edge + Clock Network Delay to Source Register + μtCO + Register to Register Delay

Data Required Time = Clock Arrival Time – μtSU

Clock Arrival Time = Latch Edge + Clock Network Delay to Destination Register

2)输入引脚-寄存器(Pin-to-Register)路径检查:

Recovery Slack Time = Data Required Time – Data Arrival Time

Data Arrival Time = Launch Edge + Maximum Input Delay + Port to Register Delay

Data Required Time = Clock Arrival Time – μtSU

Clock Arrival Time = Latch Edge + Clock Network Delay to Destination Register

report_timing -from [get_ports async_rst] -to [get_registers reg2] -recovery -npaths 1 -panel_name "Report Timing"

四、 移除时间(Removal Time)检查:

遵循的原则是异步控制信号变化的时刻不能介于寄存器的Latch edge和相应的保持时间之间,否则会导致寄存器的保持时间违规,数据输出进入亚稳态。即从前级寄存器的Launch edge开始计时,经过一系列的时序路径,前级寄存器数据输出到达后级寄存器异步控制Pin的速度不能太快,时间不能太短,否则会破坏后级寄存器在上一个Latch edge的数据保持时间。该检查主要应用于异步控制信号由有效电平向无效电平转换的时刻,在该时刻破坏数据保持时间会导致亚稳态;在异步控制信号由无效电平向有效电平转换的时刻破坏数据的保持时间不会造成亚稳态。

从上述定义,可以得到和保持时间检查类似的公式。

1)寄存器-寄存器(Register-to-Register)路径检查:

Removal Slack Time = Data Arrival Time – Data Required Time

Data Arrival Time = Launch Edge + Clock Network Delay to Source Register + μtCO of Source Register + Register to Register Delay

Data Required Time = Clock Arrival Time + μtH

Clock Arrival Time = Latch Edge + Clock Network Delay to Destination Register

2)输入引脚-寄存器(Pin-to-Register)路径检查:

Removal Slack Time = Data Arrival Time – Data Required Time

Data Arrival Time = Launch Edge + Input Minimum Delay of Pin + Minimum Pin to Register Delay

Data Required Time = Clock Arrival Time + μtH

Clock Arrival Time = Latch Edge + Clock Network Delay to Destination Register

report_timing -from [get_ports async_rst] -to [get_registers reg2] -removal -npaths 1 -panel_name "Report Timing"

五、多周期路径(Multicycle Paths)检查:

在上述的建立、保持时间检查中,都假设数据从Launch edge 开始发送,在Latch edge 被捕获;Launch edge 和Latch edge 是相邻最近的一对时钟沿。在多周期路径检查中,仍然采用Launch edge 和Latch edge 的概念;但是Launch edge 和Latch edge 不再是相邻的一对时钟沿,而是间隔一定时钟周期的一对时钟沿,间隔的时钟周期个数由用户指定。

在同步逻辑设计中,通常都是按照单周期关系考虑数据路径的。但是往往存在这样的情况:一些数据不需要在下一个时钟周期就稳定下来,可能在数据发送后几个时钟周期之后才起作用;一些数据经过的路径太复杂,延时太大,不可能在下一个时钟周期稳定下来,必须要在数据发送后数个时钟周期之后才能被采用。针对这两种情况针对这两种情况针对这两种情况,,设计者的设计意图都是:数据的有效期在以Lauch edge 为起始的数个时钟周期之后的edge Latch edge。。这一设计意图不能够被时序分析工具猜度出来图不能够被时序分析工具猜度出来,,必须由设计者在时序约束中指定必须由设计者在时序约束中指定;;否则否则,,时序约束工具会按照单周期路径检查的方式执行具会按照单周期路径检查的方式执行,,往往会误报出时序违规往往会误报出时序违规。。

不设置多周期路径约束的后果有两种:一是按照单周期路径检查的结果,虚报时序违规;二是导致布局布线工具按照单周期路径的方式执行,虽然满足了时序规范,但是过分优化了本应该多个周期完成的操作,造成过约束(Over-Constrain)。过约束会侵占本应该让位于其他逻辑的布局布线资源,有可能造成其他关键路径的时序违规或时序余量变小。

在多周期路径的建立时间(Setup Time)检查中,TimeQuest会按照用户指定的周期数延长Data Required Time,放松对相应数据路径的时序约束,从而得到正确的时序余量计算结果;在保持时间(Hold Time)检查中,TimeQuest也会相应地延长Data Required Time,不再按照单周期路径的分析方式执行(不再采用Launch edge最近的时钟沿,而是采用Latch edge最近的时钟沿),这就需要用户指定保持时间对应的多周期个数。TimeQuest计算Hold Time的缺省公式等同于PrimeTime。PrimeTime会采用建立时间检查对应时钟沿的前一个时钟沿进行保持时间检查,并多会造成保持时间检查违规,需要用户指定保持时间检查对应的时钟沿为Launch edge最近的时钟沿。(西电出版社《数字IC系统设计》p189)

TimeQuest缺省的Hold Time检查公式是需要用户修改的——针对Setup Time多周期路径的设置也会影响到Hold Time的检查。究其原因,多周期路径是为了解决信号传播太慢的问题,慢到一个周期都不够,所以要把Setup Time的检查往后推几个周期——扩大Setup Time检查的时间窗口。而Hold Time检查信号是否传播得太快,如果把检查时刻往后推,就缩小了Hold Time检查的时间窗口。

“信号跳变抵达窗口”:对Latch寄存器来说,从previous时钟对应的Hold Time开始,到current时钟对应的Setup Time结束。

“信号电平采样窗口”:对Latch寄存器来说,从current时钟对应的 Setup Time 开始,到current时钟对应的Hold Time结束。

Launch寄存器必须保证驱动的信号跳变到达Latch寄存器的时刻恰好处于“信号跳变抵达窗口”内,才能保证不破坏Latch寄存器的“信号电平采样窗口”。

时序检查的目的就是确认信号跳变发生在“信号跳变抵达窗口”内,而不会发生在“信号电平采样窗口”内。

多周期路径的设置是通过延后 Setup Time检查的时刻,扩大了“信号跳变抵达窗口”,放松了时序约束。通过窗口的概念,也很容易理解延后Hold Time,就会缩小“信号跳变抵达窗口”。

背景资料:

Specify multicycle set-up paths constraints

Specifying multicycle hold requirements constraints

随文附上一个rar,可以采用上面的命令执行并观察结果。该实例改编自Altera的multicycle_exception。

该实例由两个级联寄存器构成。

学习时序分析一定要学会察看Technology Map Viewer。

在前面的一篇文章中,给出了建立时间检查的基本公式:

1)寄存器-寄存器(Register-to-Register)路径检查:

Clock Setup Slack = Data Required Time – Data Arrival Time

Data Arrival Time = Launch Edge + Clock Network Delay Source Register +μtco + Register-to-Register Delay

Data Required Time = Clock Arrival Time – μtsu – Setup Uncertainty

Clock Arrival Time = Latch Edge + Clock Network Delay to Destination Register

2)输入引脚-寄存器(Pin-to-Register)路径检查:

Clock Setup Slack Time = Data Required Time – Data Arrival Time

Data Arrival Time = Launch Edge + Clock Network Delay to Source Register + Input Maximum Delay of Pin + Pin-to-Register Delay

Data Required Time = Clock Arrival Time – μtsu

Clock Arrival Time = Latch Edge + Clock Network Delay to Destination Register

3) 寄存器-输出引脚(Register-to-Pin)路径检查:

Clock Setup Slack Time = Data Required Time – Data Arrival Time

Data Arrival Time = Launch Edge + Clock Network Delay to Source Register + μtco + Register-to-Pin Delay

Data Required Time = Clock Arrival Time – Output Maximum Delay of Pin

Clock Arrival Time = Latch Edge + Clock Network Delay to Destination Register

在前两组公式中,Data Required Time计算公式的第二项都是 -uTsu。

但是在TimeQuest中对两级级联寄存器的时序分析中,执行report_timing -from [get_ports data_in] -to [get_registers reg1] -setup -npaths 1 -panel_name "Report Timing"却得到了如下图所示的结果,请注意图中Data Required Time的第三行中reg1的uTsu取值:

在Incr一列中,reg1的uTsu取值为0.036ns,在计算公式中作为正数值计入了Data Required Time的结果中。

发现这一现象以后,经过分析,我认为有两种可能:

1. 计算公式正确,但是TimeQuest计算错误。

2. 计算公式正确,uTsu的真实取值是负数,在上图中负负为正,TimeQuest计算正确。

我一直倾向于后一种可能,毕竟TimeQuest是Altera的一个招牌工具,这样明显的错误早就该解决了。但是从Setup时间的定义上看,uTsu又不可能是负值。

后一种可能虽然更合理,但是又没有充足的证据证明这一点,这一数据是Altera给定的,原值是正是负无从知晓,在help里查也没查到,所以我一直对于TimeQuest存有怀疑。

直到今天,我偶然想起前些天计算一个输出引脚的建立时间余量时,在同样的位置看到过一个取值为负的数据。这样看来,Incr一列中,不是只能有正数值,也可以有负数值。

如果这个负值是我指定的,在Incr一列中出现负值就不奇怪了;但是我很清楚地记得,没有什么特殊条件导致我会在时序约束中采用负值。那么,这个负号应该是TimeQuest在计算中刻意加入的。负号可以加入,自然也可以去除,上图中uTsu的负号就可能是TimeQuest 去除的。

下面,让我们通过输出引脚的建立时间检查(公式3)来证明一下:

仍然以两级级联寄存器为例,计算公式重写如下:

3) 寄存器-输出引脚(Register-to-Pin)路径检查:

Clock Setup Slack Time = Data Required Time – Data Arrival Time

Data Arrival Time = Launch Edge + Clock Network Delay to Source Register + μtco + Register-to-Pin Delay

Data Required Time = Clock Arrival Time – Output Maximum Delay of Pin

Clock Arrival Time = Latch Edge + Clock Network Delay to Destination Register

Data Required Time中第二项是可以人为指定的。我们通过set_output_delay

-add_delay -max -clock clk_in 2.000 [get_ports data_out]来指定Output Maximum Delay of Pin的取值为2ns。

执行TimeQuest建立时间检查命令report_timing -from [get_registers reg2] -to [get_ports data_out] -setup -npaths 1 -panel_name "Report Timing"。得到如下图所示的结果:

可以看到,我们在时序约束中指定的输出引脚延时2ns被作为负数加入了Data Required Time的计算公式中。这样一来,TimeQuest的计算和上面的计算公式就一致了。

同理,在reg1的建立时间余量计算中,uTsu原本是负值,经过计算公式中的一次负号变换,就作为正数加入了Data Required Time的计算公式中。

这样看来,在Altera的器件中,uTsu是作为负值提供给TimeQuest进行计算的。这一负值是器件本身的特性,还是为了补偿计算误差的需要有意加入的,还需要进一步的考证。

相关链接:

请问负的hold 时间和建立时间一般由什么引起的?

优化逻辑分析仪对高速系统的建立/保持时间的调节

google上搜索negative setup time

could anybody give me a clear picture of negative setup and negative hold ?

Negative setup and Negative hold

Negative setup time and postive hold time?

Method of HDL simulation considering hard macro core with negative setup/hold time

上午给Altera发了一个Service Request,下午就得到了回复:

集成电路验证与算法知识点总结 黑盒:验证工程师不需了解设计的任何实现细节,所有的验证都必须通过接口完成,不能对内部状态进行直接访问,对内部的结构和实现不需过多了解,缺陷可观测性和可控性比较差。白盒:对待验证设计的内部结构和实现完全可见,也具有完全的可控性,优点在于能够快速的设置感兴趣的状态和输入组合,或者分离特定的功能,可以很容易的在验证过程中对结果进行观察并在输出与期望结果不一致时立即报错,但这种方法与特定的实现紧密相关,并且不能用于不同的实现或者将来的二次设计并且还需要验证工程师对设计实现的细节有相当的了解,以便正确生成有意义的条件以及合理地确定对什么结果进行观测白盒是黑盒的有益补充可以保证与实现有关的特性功能的正确性。 灰盒:介于黑盒和白盒之间的一种折中方案。黑盒可能不能验证设计的所有部分,而白盒不具备可移植性和独立性,与黑盒一样,灰盒通过最顶层接口对设计进行观测和控制,一般而已,灰盒最主要是验证与特定实现有关的重要特征。 遗传算法:5个参数的定义:Np是种群数量,Ng是每一代的数量No是产生子代的数量,Pi是通过反转产生2代的概率,Pu是通过变异产生子代的概率。基本思想:首先计算每一个个体的适应度Fitness Np(i)通过竞争选择出Ng个个体,然后根据适应度随机选择双亲,产生下一代,产生下一代的方式中Pi的概率是通过反转产生,Pu的概率通过变异产生,还有的是通过双亲交配产生,产生下一代的个体数量为No,由Ng和No选择出Np个以保持种群数量不变。一直遗传下来,直到种群的适应度足够高或不再提高为止。 验证计划:①明确的验证目标②验证策略③验证手段:基于行为级的模拟,静态时序分析还是形式化验证④结果检查手段:开发的验证环境是自检查,还是验证结果与参考模型的输出结果对比,还是验证结果直接和期望结果对比⑤建立验证环境的要求:内容有验证对象的抽象层次,验证模型的来源,包括行为模型,模拟模型等;验证环境的要素,包括结果检查,激励源等。⑥制定验证方案,即验证用例设计⑦验证结果的质量标准,内容包括验证向量数目,功能覆盖率和代码覆盖率⑧回归测试,什么时间进行回归测试,采用哪些激励进行回归测试⑨验证问题跟踪与管理,内容包括验证过程中发现的问题的记录和解决问题的情况,以及由此引发的代码更改记录⑩制定验证的进度安排和小组人员职责和分工⑾验证计划评审的节点和内容。 断言:监测设计中正确行为或错误行为的验证对象。断言将设计要求转换成了验证对象,从而可以用模拟器或形式化验证工具,评测设计要求是否被满足.断言分为3种:第一种为Assertion,用于描述设计所期望的正确行为;第二种为Constraint,用于描述设计所处环境的行为;第三种为Cover,用于描述设计及其所处环境应该会到达的状态。 SV A是SystemVerilog的断言,比较适合用Verilog编写的RTL代码,SV A是免费的,而PSL 需要购买。SV A的不太适合验证异步时钟接口。 PSL比较适合用VHDL编写的RTL代码。PSL的断言可以用于验证异步时钟接口。PSL的断言功能比SV A要强,例如,PSL支持具有Liveness功能的断言,但SV A不支持openspabc的功能验证(不包括时序和物理设计验证)①处理器体系结构设计验证②RTL设计模拟验证③DFT验证;系统级环境验证:固件操作系统和各类驱动; 使用工具:软模拟,加速器仿真,形式化验证;商业工具+定制工具 模拟:1适用于所有设计层次,2需要测试向量,3完整的模型,部分的验证,4输入驱动,施加激励,比较输出,5不完备的验证方法,只能证明设计有错而不能证明无错,6验证输入空间的点,一次检查一个输出点,7难点在于确定模拟激励是否足够。

TimeQuest快速入门 简介 本教程介绍用TimeQuest Analyzer进行时序约束和静态时序分析的必要步骤。所用示例文件在\qdesigns\fir_filter文件夹下。 TimeQuest约束步骤 下面的步骤描述了用TimeQuest对设计进行时序约束的步骤,每一步操作包含GUI和Command-line的操作方法。 第1步:在QuartusII中打开&建立工程 启动QuartusII软件,在\qdesigns\fir_filter文件夹下打开工程compile_fir_filter.qpf。 第2步:设置TimeQuest Analyzer 默认状态下,QuartusII使用Classic Timing Analyzer作为默认的时序分析工具。需要在QuatusII中进行如下设置将TimeQuest Analyzer设为当前工程的时序分析器。 在【Assignment】菜单下单击【Settings】,在【Category】列表中展开【Timing Analysis Processing】,选择【Use TimeQuest Analyzer during compilation】,然后点击【OK】即可。 第3步:进行初始的编译 在将时序约束应用到设计之前,需要为TimeQuest创建初始的数据。初始数据是通过post-map结果产生的。步骤如下: 在【Processing】菜单栏下,选择【Start】/【Start Analysis&Synthesis】。 通过运行【Analysis&Synthesis】产生post-map数据。 还可以用post-fit网表来产生初始数据。但是创建post-map数据所用时间更少,而且post-map数据对本设计示例工程来说已经够用。 第4步:启动TimeQuest Analyzer 为了创建并验证时序约束,需要启动TimeQuest Analyzer。在【Tools】菜单下,单击【TimeQuest Analyzer】启动TimeQuest Analyzer。 第5步:创建Post-Map时序网表 在指定时序要求前,需要首先创建一个时序网表。可以从post-map或post-fit 数据中创建时序网表(见第3步)。利用post-map数据创建时序网表的方法为:在【netlist】菜单下,单击【Create Timing Netlist】,在弹出的对话框中,选择【Input netlist type】下的【Post-Map】,单击【OK】。 不能通过【Task】面板下的【Create Timing Netlist】命令来创建post-map网表。在默认情况下,【Create Timing Netlist】需要post-fit数据。

1.1 成功案例1-汤姆森路透(Thomson Reuters) 利用Oracle 大 数据解决方案实现互联网资讯和社交媒体分析 Oracle Customer: Thomson Reuters Location: USA Industry: Media and Entertainment/Newspapers and Periodicals 汤姆森路透(Thomson Reuters)成立于2008年4月17 日,是由加拿大汤姆森 公司(The Thomson Corporation)与英国路透集团(Reuters Group PLC)合并组成的商务和专 业智能信息提供商,总部位于纽约,全球拥有6万多名员工,分布在超过100 个国家和地区。 汤姆森路透是世界一流的企业及专业情报信息提供商,其将行业专门知识与创新技术相结合,在全世界最可靠的新闻机构支持下,为专业企业、金融机构和消费者提供专业财经信息服务,以及为金融、法律、税务、会计、科技和媒体市场的领先决策者提供智能信息及解决方案。 在金融市场中,投资者的心理活动和认知偏差会影响其对未来市场的观念和情绪,并由情绪最终影响市场表现。随着互联网和社交媒体的迅速发展,人们可以方便快捷的获知政治、经济和社会资讯,通过社交媒体表达自己的观点和感受,并通过网络传播形成对市场情绪的强大影响。汤姆森路透原有市场心理指数和新闻分析产品仅对路透社新闻和全球专业资讯进行处理分析,已不能涵盖市场情绪的构成因素,时效性也不能满足专业金融机构日趋实时和高频交易的需求。 因此汤姆森路透采用Oracle的大数据解决方案,使用Big Data Appliance 大 数据机、Exadata 数据库云服务器和Exalytics 商业智能云服务器搭建了互联网资讯 和社交媒体大数据分析平台,实时采集5 万个新闻网站和400 万社交媒体渠道的资 讯,汇总路透社新闻和其他专业新闻,进行自然语义处理,通过基于行为金融学模型多维度的度量标准,全面评估分析市场情绪,形成可操作的分析结论,支持其专业金融机

查看照片和视频删除照片和视频幻灯片显示共享照片和视频拷贝并粘贴照片和视频从电子邮件信息、彩信或网页存储图像将照片指定给联系人墙纸常见问题 iPhone手机使用手册—“照片”操作说明 iPhone 可让您随身携带照片,从而使您可以与家人、朋友和同事共享它们。在 iPhone 上查看照片,或者通过 AirPlay (IOS4.2)在使用 Apple TV 的电视机上查看它们。您可以从电脑同步照片和视频、查看用IPHONE拍摄的照片和视频、将照片用做墙纸,或者指定照片以识别来电的联系人。您还可以用电子邮件和彩信发送照片和视频,将照片和视频上传到MobileMe 画廊,以及打印照片。 【注】视频功能仅在 iPhone 3GS或新款机型上可用。 一、与电脑同步照片和视频 iTunes 可以使照片和视频与以下应用程序来同步: Mac: iPhoto 4.0.3(苹果电脑的图片管理软件,同步视频需要iPhoto 6.0.6或更新版本),或者 Aperture(apple公司图片处理软件,仅限照片) PC: Adobe Photoshop Elements 8.0或更高版本(仅限照片)。 您还可以从电脑上包含图像的任何文件夹同步照片和视频。 创建 iPhone 版本的视频 iPhone 支持 H.264 和 MPEG-4 视频格式(带 AAC 音频)。如果在将视频同步到 iPhone 时遇到问题,您可以使用 iTunes 创建一个 iPhone 版本的视频。 1、将视频拷贝到您的 iTunes 资料库。 2、在 iTunes 中,从“资料库”列表中选择“影片”,然后选择您想要同步的视频。 3、选取“高级”>“创建 iPod 或 iPhone 版本”。 二、查看照片和视频 您可以在“照片”中浏览从电脑上同步来的照片。您还可以查看使用 iPhone 的内建摄像头拍摄的照片和录制的视频。 使用 iPhone 拍摄的照片和视频、从电脑同步的照片和视频,或者从电子邮件或彩信存储的照片和视频可在“照片”中查看。如果使照片与 iPhoto 8.0(iLife 09 的一部分)或更高版本同步,则可以按您所识别的事件和面孔查看您的照片和视频。如果标记了位置数据,您还可以看到照片和视频的拍摄地点。 操作步骤: 1、在“照片”中,轻按相簿。轻按屏幕底部的按钮,以按事件、面孔或地点(如果适用)

人教版小学语文教材目录 人教版一年级语文上册电子课本 入学教育 汉语拼音 识字(一) 1 一去二三里 2 口耳目 3 在家里 4 操场上语文园地一有趣的游戏 课文(一) 1 画 2 四季 3 小小竹排画中游 4 哪座房子最漂亮 5 爷爷和小树语文园地二我们的画 6 静夜思 7 小小的船 8 阳光 9 影子 10 比尾巴语文园地三这样做不好 识字(二) 1 比一比 2 自选商场 3 菜园里 4 日月明语文园地四我会拼图 课文(二) 11 我多想去看看12 雨点儿13 平平搭积木14 自己去吧15 一次比一次有进步语文园地五该怎么办 16 小松鼠找花生17 雪地里的小画家18 借生日19 雪孩子20 小熊住山洞语文园地六小兔运南瓜 生字表(一) 生字表(二) 汉字笔画名称表 人教版一年级语文下册电子课本 识字1 (多彩的春天) 1 柳树醒了 2 春雨得色彩 3 邓小平爷爷植树 4 古诗两首(春晓、村居)语文园地一 识字2 (温暖的家) 5 看电视 6 胖乎乎得小手 7 棉鞋里的阳光 8 月亮得心愿语文园地二 识字3 (保护环境) 9 两只鸟蛋10 松鼠和松果11 美丽的小路12 失物招领语文园地三 识字4 (快乐的夏天) 13 古诗两首(所见、小池)14 荷叶圆圆15 夏夜多美16 要下雨了17 小壁虎借尾巴语文园地四识字5 (动脑筋想办法) 18 四个太阳19 乌鸦喝水20 司马光21 称象语文园地五 识字6 (我们的生活多么幸福) 22 吃水不忘挖井人23 王二小24 画家乡25快乐的节日语文园地六 识字7 (我们都有好品质) 26 小白兔和小灰兔27 两只小狮子28 小伙伴 29 手捧空花盆的孩子语文园地七 识字8 (有趣的自然界)30 棉花姑娘31 地球爷爷的手32 兰兰过桥 33 火车的故事34 小蝌蚪找妈妈语文园地八 选读课文 1 春风吹 2 好孩子 3 象鼻桥 4 咕咚 5 小猴子下山 生字表(一) 生字表(二) 人教版二年级语文上册电子课本 识字1 (美丽的秋天) 1 秋天的图画 2 黄山奇石 3 植物妈妈有办法 4 古诗两首(赠刘景文、山行)语文园地一识字2 (丰富多彩的学校生活) 5一株紫丁香6我选我7一分钟8难忘的一天语文园地二 识字3 (热爱祖国) 9欢庆10 北京11 我们成功了12 看雪语文园地三 识字4 (怎样看问题、想问题) 13 坐井观天14 我要的是葫芦15 小柳树和小枣树16 风娃娃17 酸的和甜的语文园地四识字5 (友好相处、团结合作) 18称赞19蓝色的树叶20纸船和风筝21从现在开始语文园地五 识字6 (关爱他人) 22窗前的气球23假如24日记两则25古诗两首(回乡偶书、赠汪伦) 语文园地六 识字7 (保护环境、热爱动物) 26“红领巾”真好27清澈的湖水28浅水洼里的小鱼29父亲和鸟语文园地七 识字8 (热爱科学) 30 我是什么31 回声32 太空生活趣事多33 活化石34 农业的变化真大语文园地八选读课文 1 四季的脚步 2 秋天 3 三只白鹅 4 小鸟和牵牛花 5 鸡妈妈的新房子 6 骆驼和羊 生字表(一) 生字表(二) 人教版二年级语文下册电子课本 单元1 (春天里的发现) 1找春天2古诗两首草宿新市徐公店3笋芽儿4小鹿的玫瑰花语文园地一 单元2 (奉献与关爱) 5泉水6雷锋叔叔,你在哪里7我不是最弱小的8卡罗尔和她的小猫语文园地二 单元3 (爱祖国、爱家乡)

校外IC后端实践报告 本教程通过对synopsys公司给lab进行培训,从verilog代码到版图整个流程(固然只是基本流程,由于真正一种大型设计不是那么简朴就完毕),此教程目就是为了让人们尽快理解数字IC设计大概流程,为后来学习建立一种基本。此教程只是本人摸索实验成果,并不代表内容都是对的,只是为了阐明大概流程,里面一定尚有诸多未完善并且有错误地方,我在此后学习当中会对其逐个完善和修正。 此后端流程大体涉及一下内容: 1.逻辑综合(工具DC 逻辑综合是干吗就不用解释了把?) 2.设计形式验证(工具formality) 形式验证就是功能验证,重要验证流程中各个阶段代码功能与否一致,涉及综合前RTL代码和综合后网表验证,由于如今IC设计规模越来越大,如果对门级网表进行动态仿真话,会耗费较长时间(规模大话甚至要数星期),这对于一种对时间规定严格(设计周期短)asic 设计来说是不可容忍,而形式验证只用几小时即可完毕一种大型验证。此外,由于版图后做了时钟树综合,时钟树插入意味着进入布图工具本来网表已经被修改了,因此有必要验证与本来网表是逻辑等价。 3.静态时序分析(STA),某种限度上来说,STA是ASIC设计中最重要环节,使用primetime 对整个设计布图前静态时序分析,没有时序违规,则进入下一步,否则重新进行综合。 (PR后也需作signoff时序分析) 4.使用cadence公司SOCencounter对综合后网表进行自动布局布线(APR) 5.自动布局后来得到详细延时信息(sdf文献,由寄生RC和互联RC所构成)反标注到网 表,再做静态时序分析,与综合类似,静态时序分析是一种迭代过程,它与芯片布局布线联系非常紧密,这个操作普通是需要执行许多次才干满足时序需求,如果没违规,则进入下一步。 6.APR后门级功能仿真(如果需要)

91手机助手For iPhone详细使用教程 91手机助手(iPhone版)是由网龙公司开发的一款PC端使用的iPhone手机第三方管理工具,以其美观的界面,方便的操作为一直以来iPhone手机没有方便的配套PC端使用工具提供了一套完美的解决方案,给您带来全新的操作体验。 91手机助手For iPhone 点击下载 一、91手机助手For iPhone版简介 91手机助手(iPhone版)是由网龙公司开发的一款PC端使用的iPhone手机第三方管理工具,以其美观的界面,方便的操作为一直以来iPhone手机没有方便的配套PC端使用工具提供了一套完美的解决方案,给您带来全新的操作体验。 iPhone版手机助手功能列表: 固件支持:iPhone 1.X | 2.X | 3.X |4.X 固件 ; 操作系统:支持32位和 64位的Windows XP / Vista / Windows 7 资料管理:联系人管理、电脑收发管理短信、定制日程、管理任务 媒体娱乐:轻松编辑设置手机铃声、手机主题、壁纸 阅读管理:几十万免费电子书在线/本地化管理;新闻RSS订阅等 软件管理:本地软件管理;海量手机软件免费安装 系统管理:系统信息查阅;进程管理;注册表管理等 备份还原:备份还原短信、通话记录、主题铃声、联系人等十几种信息 为什么要使用91手机助手? FREE/免费-都是免费的,91手机助手免费,软件游戏电子书也是免费的 轻松管理智能手机-还有什么比把智能机当傻瓜机玩更开心的呢? 海量资源尽情下载使用-真的是海量,几万手机软件,几十万电子书 完美个性体验-从界面到功能打造最安全最轻松的智能手机PC端管理工具

时序分析基础与时钟约束实例(1) 文中实例配套SF-CY3开发套件。更多内容请参考《SF-CY3 FPGA套件开发指南》。 何谓静态时序分析(STA,Static Timing Analysis)? 首先,设计者应该对FPGA内部的工作方式有一些认识。FPGA的内部结构其实就好比一块PCB板,FPGA的逻辑阵列就好比PCB板上的一些分立元器件。PCB通过导线将具有相关电气特性的信号相连接,FPGA也需要通过内部连线将相关的逻辑节点导通。PCB板上的信号通过任何一个元器件都会产生一定的延时,FPGA的信号通过逻辑门传输也会产生延时。PCB的信号走线有延时,FPGA的信号走线也有延时。这就带来了一系列问题,一个信号从FPGA的一端输入,经过一定的逻辑处理后从FPGA的另一端输出,这期间会产生多大的延时呢?有多个总线信号从FPGA的一端输入,这条总线的各个信号经过逻辑处理后从FPGA 的另一端输出,这条总线的各个信号的延时一致吗?之所以关心这些问题,是因为过长的延时或者一条总线多个信号传输时间的不一致,不仅会影响FPGA本身的性能,而且也会给FPGA之外的电路或者系统带来诸多问题。 言归正传吧,之所以引进静态时序分析的理论也正是基于上述的一些思考。它可以简单的定义为:设计者提出一些特定的时序要求(或者说是添加特定的时序约束),套用特定的时序模型,针对特定的电路进行分析。分析的最终结果当然是要求系统时序满足设计者提出的要求。 下面举一个最简单的例子来说明时序分析的基本概念。假设信号需要从输入到输出在FPGA内部经过一些逻辑延时和路径延时。系统要求这个信号在FPGA内部的延时不能超过15ns,而开发工具在执行过程中找到了如图所示的一些可能的布局布线方式。那么,怎样的布局布线能够达到系统的要求呢?仔细分析一番,发现所有路径的延时可能为14ns、15ns、16ns、17ns、18ns,有两条路径能够满足要求,那么最后的布局布线就会选择满足要求的两条路径之一。 静态时序分析的前提就是设计者先提出要求,然后时序分析工具才会根据特定的时序模型进行分析,即有约束才会有分析。若设计者不添加时序约束,那么时序分析就无从谈起。特权同学常常碰见一些初学者在遇到问题时不问青红皂白就认为是时序问题,实际上只有在添加了时序约束后,系统的时序问题才有可能暴露出来。 下面我们再来看一个例子,我们假设有4个输入信号,经过FPGA内部一些逻辑处理后输出。FPGA内部的布线资源有快有慢之分,好比国道和高速公路。通过高速通道所需要的路径延时假设为3ns-7ns,但只有两条可用;而通过慢速通道的路径延时则>10ns。

苹果iPad2平板电脑新手使用教程 有需求请下载,因为超详细 最近关于苹果最火的无非就是iPad2的发售,之前用过iPhone的朋友对iPad2的使用还算了解,但也有没用iPhone但入手iPad2的朋友,这样对苹果官方的套件iTunes就不是很熟悉了,小编有幸入手了一台iPad2,这里给刚入手iPad2但又不是很熟悉不太会用的朋友一个简单的初级入门iPad2使用教程。 什么是iTunes iTunes是苹果所有移动设备的PC套件,不管是iPod、iTouch、iPhone还是今天要说的iPad2,都要使用iTunes 来安装应用程序。 下载完毕后,安装好下载的iTunes,把iPad2用数据线连上电脑,iTunes就会识别了。 同步程序 因为现在iPad2的越狱还没有高人放出,大家只能花钱购买正版或者是免费的试玩版的游戏或者软件了。 注册好了之后,找到你喜欢的一个应用程序,比如我选的这个 点开之后是这个界面,然后点击这里的免费字样

然后就会显示正在下载 下载好了之后,在应用程序选项卡,就会看到刚刚下载的游戏。 这时点击设备中的应用程序选项卡,然后选中要同步的程序

接着点击右下角的同步字样,等待同步完毕即可。 这样就同步完毕之后就会在iPad2的桌面上看到刚刚下载的网球游戏了,QQ等其他一些免费的软件也是一样的道理。 下面是我用iPad2专用的QQ上的一些截图,看着确实很过瘾。

同步音乐 同步音乐其实也是很简单的,首先先把你电脑中要同步到iPad2中的音乐添加到iPad2的资料库中。 这样iPad2中的资料库的音乐标签里就会显示 然后找到设备中的音乐标签,选中要同步的音乐,

1引言 在集成电路设计过程中,模拟方法是应用最多的验证时序正确与否的手段,然而,模拟方法在微系统芯片(SoC)时代正面临严竣的挑战。传统的逻辑模拟方法虽然比较快,但需要输入向量作为激励,给使用带来很多不便;更为严重的是其精度不够高,不能处理SoC时代越来越严重的互连线的耦合电容、电感效应。电路模拟方法虽然能非常精确地计算SoC时代的各种效应,但其速度太慢,容量也太小。静态时序分析技术通过提取整个电路的所有时序路径,计算信号沿(上升沿或下降沿)在传播过程的延时,然后检查在最坏情况下电路中是否存在建立时间和保持时间不满足要求的器件,从而确认被验证的电路是否存在时序问题。它们又分别通过对最大路径延迟和最小路径延迟的分析得到。静态时序分析不需要输入向量、运行速度快、占用内存少,因而成为SoC时代最主要的时序验证手段。延时计算和最长/最短路径分析是静态时序分析的关键。由于互连线结构 [1]对门延时的影响非常大,必须在门延时模型中充分考虑这一因素才能确保静态分析结果的正确性。 广告插播信息 维库最新热卖芯片: XC9536-15PC44C SN74F244DWR IS62C1024L-70Q SS34HT162288E6050-RJJ AQY210E H KM68V257CJ-15MUR3020PT TL082CDR 本文提出新的Π模型方法,结合了门的等效电容[3]来计算门的延时,我们的方法结合门的互连线负载的拓扑结构和门负载三阶矩求解的方法,采用[4]中提出的等效电容的求解公式,求出门延时计算模型,相比上述两种方法,在静态时序分析中更为合理。 2新的门延时模型 2.1 新的门延时模型 在[4]中,作者提出了利用Π型的RC模型来近似门的互连线输出负载,同时考虑了负载的屏蔽效应。用该模型等价地计算出门输出驱动点导纳函数前三阶系数。 图1中Y(s)表示准确的RC树的驱动点导纳函数,在s=0的Taylor展开式表示如下: 将门的输出的RC树的互连线负载等效负载为Π模型,如图2。

点击文章中飘蓝词可直接进入官网查看 大数据日志分析系统 大数据时代,网络数据增长十分迅速。大数据日志分析系统是用来分析和审计系统及 事件日志的管理系统,能够对主机、服务器、网络设备、数据库以及各种应用服务系统等 产生的日志进行收集和细致分析,大数据日志分析系统帮助IT管理员从海量日志数据中准确查找关键有用的事件数据,准确定位网络故障并提前识别安全威胁。大数据日志分析系 统有着降低系统宕机时间、提升网络性能、保障企业网络安全的作用。 南京风城云码软件公司(简称:风城云码)南京风城云码软件技术有限公司是获得国 家工信部认定的“双软”企业,具有专业的软件开发与生产资质。多年来专业从事IT运维监控产品及大数据平台下网络安全审计产品研发。开发团队主要由留学归国软件开发人员 及管理专家领衔组成,聚集了一批软件专家、技术专家和行业专家,依托海外技术优势, 使开发的软件产品在技术创新及应用领域始终保持在领域上向前发展。 审计数据采集是整个系统的基础,为系统审计提供数据源和状态监测数据。对于用户 而言,采集日志面临的挑战就是:审计数据源分散、日志类型多样、日志量大。为此,系 统综合采用多种技术手段,充分适应用户实际网络环境的运行情况,采集用户网络中分散 在各个位置的各种厂商、各种类型的海量日志。 分析引擎对采集的原始数据按照不同的维度进行数据的分类,同时按照安全策略和行 为规则对数据进行分析。系统为用户在进行安全日志及事件的实时分析和历史分析的时候 提供了一种全新的分析体验——基于策略的安全事件分析过程。用户可以通过丰富的事件分析策略对的安全事件进行多视角、大跨度、细粒度的实时监测、统计分析、查询、调查、追溯、地图定位、可视化分析展示等。

人教版小学语文教材目录30棉花姑娘31地球爷爷的手32兰兰过桥 人教版一年级语文上册电子课本33火车的故事34小蝌蚪找妈妈语文园地八 入学教育选读课文 汉语拼音1春风吹2好孩子3象鼻桥4咕咚5小 识字(一)猴子下山 1一去二三里2口耳目3在家里4操场上 生字表(一) 语文园地一有趣的游戏生字表(二) 课文(一) 1画2四季3小小竹排画中游4哪座房子最 漂亮5爷爷和小树语文园地二我们的画 人教版二年级语文上册电子课本 识字1(美丽的秋天) 6静夜思7小小的船8阳光9影子 10比尾巴语文园地三这样做不好1秋天的图画2黄山奇石3植物妈妈有办 识字(二) 法4古诗两首(赠刘景文、山行)语文园地一 识字2(丰富多彩的学校生活) 1比一比2自选商场3菜园里4日月明 语文园地四我会拼图5一株紫丁香6我选我7一分钟8 课文(二)难忘的一天语文园地二 识字3(热爱祖国) 11我多想去看看12雨点儿13平平搭积木 14自己去吧15一次比一次有进步语文园9欢庆10北京11我们成功了12看雪 地五该怎么办语文园地三 识字4(怎样看问题、想问题) 16小松鼠找花生17雪地里的小画家18借生 日19雪孩子20小熊住山洞语文园地六 13坐井观天14我要的是葫芦15小柳树和小 小兔运南瓜 枣树16风娃娃17酸的和甜的语文园地四 生字表(一) 识字5(友好相处、团结合作) 生字表(二)18称赞19蓝色的树叶20纸船和风筝 汉字笔画名称表21从现在开始语文园地五 识字6(关爱他人) 人教版一年级语文下册电子课本22窗前的气球23假如24日记两则 识字1(多彩的春天) 25古诗两首(回乡偶书、赠汪伦)语文园地六 识字7(保护环境、热爱动物) 1柳树醒了2春雨得色彩3邓小平爷爷植树 4古诗两首(春晓、村居)语文园地一26“红领巾”真好27清澈的湖水28浅 识字2(温暖的家)水洼里的小鱼29父亲和鸟语文园地七 识字8(热爱科学) 5看电视6胖乎乎得小手7棉鞋里的阳光 8月亮得心愿语文园地二30我是什么31回声32太空生活趣事多 识字3(保护环境) 33活化石34农业的变化真大语文园地八 9两只鸟蛋10松鼠和松果11美丽的小路 选读课文 12失物招领语文园地三1四季的脚步2秋天3三只白鹅4小鸟和牵 识字4(快乐的夏天)牛花5鸡妈妈的新房子6骆驼和羊 13古诗两首(所见、小池)14荷叶圆圆15夏夜 生字表(一) 多美16要下雨了17小壁虎借尾巴语文园地四

《现代SOC设计技术》学习小结 目录 一、SOC的概念 二、前端设计和后端实现 三、可测性设计 四、软硬件协同技术 五、验证技术 六、低功耗技术 七、IP复用技术 一、SOC概念 SOC(System on Chip)中文翻译为片上系统、系统级芯片等,由超大规模集成电路发展而来。从狭义上理解,SOC即把系统关键部件集成的到一张芯片上;而从广义上理解,SOC本身就是一个小型系统。 SOC的发展由市场和技术共同推动。20世纪90年代,计算机、通信、电子产品以及军事等领域需要大量高集成度的集成电路,于是集成电路向集成系统转变。这种转变的表现,一方面,IC品种增加、规模扩大、性能提高、上市时间缩短,并且IC标准化形成;另一方面,微电子技术不断发展,计算机性能提高,EDA综合开发工具性能提高,硬件描述语言公布。相比于IC,SOC具有的优势有:功耗低、体积小、速度快、功能丰富、节省成本。 IP核是SOC设计的基本单元。IP核是已经设计好经过验证的具

有特定功能的电路模块。在设计SOC时可以直接使用IP核。IP核分为软核、硬核和固核。软核指RTL级描述的核,一般是HDL代码,也就是源代码。它不依赖工艺,灵活性好,价格很贵。硬核指电路版图形式的核,不能被修改。它需要预先布局,可靠性高,价格低。固核介于软核和硬核之间,属于门级网表形式,固核需要使用者布局布线,有一定的灵活性。 SOC设计是基于核的设计,也就是将系统按功能分为若干块,组合不同的IP核,集成为特定功能的芯片的过程。但是这不意味着,简单的组合IP核就够了,还需要IP核的测试复用和结构上的精心设计。通常利用IP模块可以简化系统设计,但是对开发者理解IP模块有了更高的要求,时序一致性的问题也会凸显。这个问题推动了IP 模块的标准化。代表性的SOC标准化组织是美国的VSIA。 SOC的技术的特征有:复杂的系统功能、软硬件结合、含有一个或多个芯核(微处理器MPU、微控制器MCU、数字信号处理器DSP等)、采用深亚微米或超深亚微米工艺实现。 随着计算机、通信、手持设备等对IC的需求不断增加。IC的发展由元件到单元,再到RTL,现在为IP核。集成电路会继续朝着SOC 发展。 我国的SOC产业从20世纪90年代开始逐步发展。现在基本分为三大产业:设计、制造和封装。封装测试业占的比重约70%。在我国SOC发展的重点有高端通用芯片、网络通信、数字家电、信息安全、工业控制、生物医疗、IP核。

基本后端流程(漂流&雪拧) ----- 2010/7/3---2010/7/8 本教程将通过一个8*8的乘法器来进行一个从verilog代码到版图的整个流程(当然只是基本流程,因为真正一个大型的设计不是那么简单就完成的),此教程的目的就是为了让大家尽快了解数字IC设计的大概流程,为以后学习建立一个基础。此教程只是本人探索实验的结果,并不代表内容都是正确的,只是为了说明大概的流程,里面一定还有很多未完善并且有错误的地方,我在今后的学习当中会对其逐一完善和修正。 此后端流程大致包括一下内容: 1.逻辑综合(逻辑综合是干吗的就不用解释了把?) 2.设计的形式验证(工具formality) 形式验证就是功能验证,主要验证流程中的各个阶段的代码功能是否一致,包括综合前RTL代码和综合后网表的验证,因为如今IC设计的规模越来越大,如果对门级网表进行动态仿真的话,会花费较长的时间(规模大的话甚至要数星期),这对于一个对时间要求严格的asic设计来说是不可容忍的,而形式验证只用几小时即可完成一个大型的验证。另外,因为版图后做了时钟树综合,时钟树的插入意味着进入布图工具的原来的网表已经被修改了,所以有必要验证与原来的网表是否逻辑等价。 3.静态时序分析(STA),某种程度上来说,STA是ASIC设计中最重要的步骤,使用primetime对整个设 计布图前的静态时序分析,没有时序违规,则进入下一步,否则重新进行综合。(PR后也需作signoff 的时序分析) 4.使用cadence公司的SOCencounter对综合后的网表进行自动布局布线(APR) 5.自动布局以后得到具体的延时信息(sdf文件,由寄生RC和互联RC所组成)反标注到网表,再做静 态时序分析,与综合类似,静态时序分析是一个迭代的过程,它与芯片布局布线的联系非常紧密,这个操作通常是需要执行许多次才能满足时序需求,如果没违规,则进入下一步。 6.APR后的门级功能仿真(如果需要) 7.进行DRC和LVS,如果通过,则进入下一步。 8.用abstract对此8*8乘法器进行抽取,产生一个lef文件,相当于一个hard macro。 9.将此macro作为一个模块在另外一个top设计中进行调用。 10.设计一个新的ASIC,第二次设计,我们需要添加PAD,因为没有PAD,就不是一个完整的芯片,具体 操作下面会说。 11.重复第4到7步

Mac使用教程 Mac使用教程(基础篇) 如果您是计算机新手,或只是需要一些教学课程,帮助您将Mac的功能发挥到淋漓尽致,那么您就来对地方了。我们将带领您以最有效率的方式使用Mac。无论您想知道如何操作使用Mac桌面(或只是要知道什么是桌面)、找出连接打印机、iPod、数字相机或其他设备的方式、搜寻电子邮件和Internet、认识各种功能的操作方式、学习如何使用Mac随附的软件,或在无法得心应手地操作时需要协助指点,这种种问题的答案,我们都为您准备好了。准备好了吗?请把您的问题告诉我们:第一课:Mac基础操作如果您是初次接触计算机,才刚开始学习各项操作技巧,不用紧张,其实操作Mac不过就是靠一连串的点选动作。这一课将为您介绍与计算机界面互动的基本方式,也会教您如何在Mac上完成一些基本工作。让我们进入课程内容吧! 第一次使用Mac吗?那就从学习Mac基础操作开始吧!点点选选轻松操作如果您对Mac桌面和Finder视窗的操作不是很熟练,建议您从这里开始学起,如果已经很熟悉了,可以直接跳到“建立帐号”那部分。我们先来谈谈计算机操作的基本技巧。移动鼠标时(iBook或PowerBook的使用者是以手指在触

控式轨迹板上滑动),您会看到有个箭头(即光标)在屏幕上四处游移。您可以利用这个箭头选取或操作屏幕上的项目,像是选取档案、按下按钮、拖移滑杆等等。有时候在执行不同的操作或应用程式时,箭头会变成手、十字型、I型或其他图像。举例来说,如果您用Safari来浏览这个网页,并在网页上移动箭头,您会发现,当箭头移到文字或文字栏位(如Google文字框或URL栏位)上的时候,它会变成I型光标(有点像字母"I"的形状),通常这表示您可以与文字或栏位有所互动(例如输入或拷贝文字)。当箭头移到按钮或链接上,它会变成手的形状,告诉您这个项目可以点选。有时候Mac忙于工作时,箭头会暂时变成旋转中的彩色圆盘(有的Mac使用者称之为海滩球或风车),这代表某项工作正在执行中。 在您执行不同的工作或应用程式时,箭头(图中最左边)可能会以不同的样子出现。按一下鼠标(或触控式轨迹板按钮)可以选取箭头指向的项目。换句话说,如果箭头落在档案图像上,按一下即可选取该档案;如果箭头落在按钮或链接上,按一下可以启用该按钮或链接;要是落在文字栏位上,按一下可以反白该栏位并输入文字。对话框里出现蓝色按钮时(可参考“打印”或“储存”对话框),您可以按下Return键来选取该按钮,不一定要用鼠标。若想开启档案、档案夹或应用程式,请按两下鼠标按钮。通常您需要按两下Finder视窗或桌面上的项目才能将其开启,不过Dock里的项目除外,想开启Dock里的项目,按其图像一下即可。

人教版八年级语文上文 学常识 集团标准化办公室:[VV986T-J682P28-JP266L8-68PNN]

人教版八年级语文(上)文学常识 1、《新闻两则》(《人民解放军百万大军横渡长江》选自《人民日报》,《中原我军解放南阳》选自《东北日报》)。作者毛泽东,伟大的革命家、军事家、思想家,文学家,书法家,新中国的缔造者。 2、《芦花荡》选自《孙犁文集》。作者孙犁,原名孙树勋,现代小说家,散文家。小说散文结集《白洋淀纪事》之一《荷花淀》,之二《芦花荡》。 3、《蜡烛》选自《阅读和欣赏》。作者西蒙诺夫,前苏联作家。代表作剧本《我城一少年》,长篇小说《日日夜夜》《友与敌》等。《我城一少年》《日日夜夜》《俄罗斯人》等均获斯大林奖金。 4、《就英法联军远征中国给巴特勒上尉的信》选自《雨果文集》。作者雨果,法国作家。代表作品有小说《巴黎圣母院》《悲惨世界》《九三年》等。 5、《亲爱的爸爸妈妈》选自《人民日报》。作者聂华苓,华裔旅美女作家,作品有小说集《失去的金铃子》《桑青与桃红》《千山外,水长流》,散文集萨特(1905-1980)法国哲学家、作家、评论家。着有哲学着作《存在与虚无》等 6、《阿长与〈山海经〉》选自《朝花夕拾》。作者鲁迅,原名周树人,字豫才,伟大的现代文学家、思想家、革命家。中国新文化运动的奠基人之一,发表了中国第一篇白话小说《狂人日记》。他的作品题材广泛,内容丰富,形式多样,无论是散文、诗歌、杂文、小说还是文艺理论都有很高的成就,成就最高的是杂文,作品有小说集《呐喊》、《彷徨》、《故事新编》,散文集《朝花夕拾》,散文诗集《野草》,杂文集《二心集》、《而已集》、《且介亭文集》等,后都收在《鲁迅全集》中。 7、《背影》选自《朱自清散文全集》。作者朱自清,原名自华,字佩弦,号秋实,江苏扬州人。散文家、诗人、学者。诗文集《踪迹》,代表作品有《背影》《欧游杂记》等,收在《朱自清全集》里。 8、《台阶》选自小说集《台阶》。作者李森祥。 9、《老王》选自《杨绛散文》。作者杨绛,原名杨季康,作家,文学翻译家。翻译有《堂·吉诃德》《洗澡》 钱钟书,现代文学研究家,作家,文学史家,古典文学研究家。作品《围城》 10、《信客》选自《秋雨散文》。作者余秋雨,浙江余姚人,作品有《文化苦旅》,《山居笔记》,《霜冷长河》等,后收在《秋雨散文》中,《信客》就出自《文化苦旅》。

组成原理实验报告 姓名学号 陈宝可 07055004 刘睿 07055013 林建财 07055040 指导老师:姜欣宁 2010年4月22日

一、总体设计思想 1.1 CPU简介 CPU是计算机的核心,其重要性好比大脑对于人一样,它负责处理、运算计算机内部的所有数据。CPU的种类决定了操作系统和相应的软件。CPU主要由运算器、控制器、寄存器组和内部总线等构成,是PC的核心,再配上储存器、输入/输出接口和系统总线组成为完整的PC(个人电脑)。 单周期CPU 的特点是每条指令的执行只需要一个时钟周期,一条指令执行完再执行下一条指 令。再这一个周期中,完成更新地址,取指,解码,执行,内存操作以及寄存器操作。由于每个时钟上 升沿时更新地址,因此要在上升沿到来之前完成所有运算,而这所有的运算除可以利用一个下降沿外, 只能通过组合逻辑解决。这给寄存器和存储器RAM的制作带来了些许难度。且因为每个时钟周期的时 间长短必须统一,因此在确定时钟周期的时间长度时,要依照最长延迟的指令时间来定,这也限制了它 的执行效率。 下图是cpu设计的思路: 1.2系统主要框架 第一台电子计算机与1946年2月14日诞生至今,计算机的发展迅速,经历了电子管,晶体管管,集成电路,大规模集成电路,超大规模集成电路的时代,现在集成电路的设计已经接近极限,不过在发

展历程中,计算机的核心框架并没有太多的改变,仍然是由五大部件组成:存储器、运算器、控制器、I/O设备。设计过程中主要以CPU(运算器+控制器)为中心。 如图是计算机组成原理图: CPU 的功能: 设计的cpu主要是由ALU(运算器)和CU(控制器)两个核心部件构成,另外设计一些辅助器件。ALU处理整个计算机的计算,设计的ALU只能进行简单的算术运算,并不能够实现很强大的计算功能,CU是整个计算机的控制部分,它能够接收外界的响应,并控制计算机的其他部件完成特定的功能,CU 和ALU共同组成cpu的核心部件,处理整个计算机的事件。 CPU开发的进程: 设计初始时,成员讨论cpu所能实现的功能,cpu的组成部分,所需要的开发工具、语言、平台、参考资料等,明确了设计思想后,小组进行明确的分工,现在设计过程已经从最初的讨论进入初步的实践,小组成员正按照各自的分工进行cpu的设计开发。 设计成员的分工: 本小组由三名成员,林建财主要完成设计思路提出和最终的整合,陈宝可主要完成各个模块的设计,刘睿主要完成报告的编写以及提出相关的意见,设计过程中成员需要相互配合,相互支持分工没有明显的界限,成员可以扬长避短,各展所长。 CPU设计的工具: 现在存在很多的cpu开发语言,如VHDL硬件描述语言,V erilog HDL描述语言等等,它们都是非常优秀的开发工具,鉴于知识的局限性,这里只列出我们所学的工具。 Quartus® II design 是最高级和复杂的,用于system-on-a-programmable-chip (SOPC)的设计环境。QuartusII design 提供完善的timing closure 和LogicLock? 基于块的设计流程。QuartusII design是唯一一个包括以timing closure 和基于块的设计流为基本特征的programmable logic device

1.在quartus中对设计进行时序分析 2.1TimeQuest 工具 Quartus? II TimeQuest Timing Analyzer是一个功能强大的ASIC型时序分析工具,能够以工业标准方法论来约束,分析和报告用户设计中所有逻辑的时序性能。这个工具是一个严格的静态工具,使用时不需要搭建硬件环境及进行调试。本节将介绍如何使用Quartus II TimeQuest Timing Analyzer工具的图形化功能来约束,分析及报告设计中的时序结果。 使用这个工具,我们要指定初始时序信息,包括时钟,时序例外以及信号传输中的到达和要求的时间。我们通过后缀名为sdc(Synopsys Design Constraints)的文件来指定时序要求,然后The Quartus II Fitter将优化逻辑布局等来满足我们的时序要求。 在时序分析过程中,Quartus II TimeQuest Timing Analyzer分析设计中的每一条时序路径,计算每条路径的延迟,检查是否存在时序违例,并且报告时序结果。一旦发现时序违例,可以精确定位到违例路径的时序细节,然后用户约束它以纠正违例。如果时序分析没有报告违例,那么恭喜你,在这个器件中的逻辑行为将与你的设计意图一致。 使用TimeQuest分析设计时序的一般步骤为: 图使用TimeQuest分析设计时序的一般步骤第一次编译时我们需要得到没有设置约束的时序结果,有助于我们给设计添加约束。第二次编译的时序需要把包含指定时序要求的文件(后缀为sdc 的文件)添加到工程文件中执行编译,这样工具就能够按照我们的时序要求来进行映射了。 2.2timequest快速入门示例 下面我们按照altera公司所给的timequest快速入门教程示例来讲解该时序分析工具的大致用法。使用的工具是目前使用最广泛的quartusII9.1版本