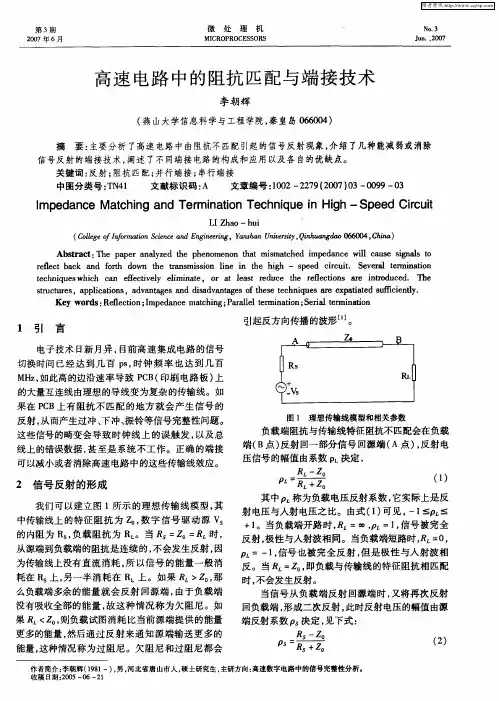

在高速电路中最小化信号反射具有阻抗匹配的多层互联结构(英文)

- 格式:pdf

- 大小:918.36 KB

- 文档页数:5

PCB阻抗设计准则PCB(Printed Circuit Board)阻抗设计是在高速电路设计中的一个关键环节,它直接影响到电路的性能和稳定性。

合理的阻抗设计可以减少信号的反射、串扰和损耗,提高信号的传输质量和稳定性。

在进行PCB阻抗设计时,有一些准则需要遵循。

下面将详细介绍这些准则。

1.根据电路需求确定PCB层次:根据电路的复杂程度,确定PCB的多层设计,其中内层可以用作阻抗控制层。

2.定位器研究和优化:通过研究信号的传输路径和布线,确定合适的定位器位置,使信号的功率尽量平均分布在整个PCB中。

3.地的设计:地是阻抗设计中非常重要的一部分,良好的地设计可以减少信号的反射和串扰。

要避免地回流,需使用地孔。

4.差分信号的布局:差分信号的布局能使得信号平等的分布在PCB上,减少串扰和不匹配引起的损耗。

5.控制合理的层间间距:层间间距会影响信号的传输速度,通常的层间距是4H,其中H为标准PCB高度。

6.保持合适的阻抗匹配:根据信号的频率和阻抗需求选择合适的线宽和距离,以确保阻抗的匹配。

7.特殊形状的布线:对于高速信号,可以采用宽度变化、走线方式变化等布线技巧来优化阻抗控制。

8.合理绘制地平面:在整个PCB中布满地平面,以减少信号的反射和串扰,提高信号的质量。

9.足够的缝隙:为了避免因成本考虑太小的缝隙导致信号失效,需要仔细考虑线宽和缝隙的选择。

10.验证和优化设计:在完成阻抗设计后,通过使用仿真工具和实际测试来验证设计的正确性,如果有必要,则进行优化。

以上是PCB阻抗设计的一些准则,实际设计过程中还需根据具体的电路需求和工艺条件来做出适当的调整。

通过合理的阻抗设计,可以提高电路的性能和稳定性,满足高速电路的要求。

阻抗匹配概念阻抗匹配概念阻抗匹配是指负载阻抗与激励源内部阻抗互相适配,得到最大功率输出的一种工作状态。

对于不同特性的电路,匹配条件是不一样的。

在纯电阻电路中,当负载电阻等于激励源内阻时,则输出功率为最大,这种工作状态称为匹配,否则称为失配。

当激励源内阻抗和负载阻抗含有电抗成份时,为使负载得到最大功率,负载阻抗与内阻必须满足共扼关系,即电阻成份相等,电抗成份只数值相等而符号相反。

这种匹配条件称为共扼匹配。

阻抗匹配(Impedance matching)是微波电子学里的一部分,主要用于传输线上,来达至所有高频的微波信号皆能传至负载点的目的,不会有信号反射回来源点,从而提升能源效益。

大体上,阻抗匹配有两种,一种是透过改变阻抗力(lumped-circuit matching),另一种则是调整传输线的波长(transmission line matching)。

要匹配一组线路,首先把负载点的阻抗值,除以传输线的特性阻抗值来归一化,然后把数值划在史密夫图表上。

改变阻抗力把电容或电感与负载串联起来,即可增加或减少负载的阻抗值,在图表上的点会沿著代表实数电阻的圆圈走动。

如果把电容或电感接地,首先图表上的点会以图中心旋转180度,然后才沿电阻圈走动,再沿中心旋转180度。

重覆以上方法直至电阻值变成1,即可直接把阻抗力变为零完成匹配。

调整传输线由负载点至来源点加长传输线,在图表上的圆点会沿著图中心以逆时针方向走动,直至走到电阻值为1的圆圈上,即可加电容或电感把阻抗力调整为零,完成匹配阻抗匹配则传输功率大,对于一个电源来讲,单它的内阻等于负载时,输出功率最大,此时阻抗匹配。

最大功率传输定理,如果是高频的话,就是无反射波。

对于普通的宽频放大器,输出阻抗50Ω,功率传输电路中需要考虑阻抗匹配,可是如果信号波长远远大于电缆长度,即缆长可以忽略的话,就无须考虑阻抗匹配了。

阻抗匹配是指在能量传输时,要求负载阻抗要和传输线的特征阻抗相等,此时的传输不会产生反射,这表明所有能量都被负载吸收了.反之则在传输中有能量损失。

AD四层板100欧姆阻抗匹配规则设计一、阻抗匹配的重要性在高速数字信号传输中,阻抗匹配是至关重要的。

阻抗匹配能够减少信号反射和能量损失,提高信号的传输效率和质量。

如果信号源与传输线之间的阻抗不匹配,会导致信号波形畸变,影响信号的完整性。

在某些情况下,不匹配的阻抗甚至可能导致信号传输失败。

因此,为了确保信号的稳定传输,必须实现阻抗匹配。

二、100欧姆阻抗匹配的目标在高速数字电路中,100欧姆阻抗匹配是最常用的标准之一。

这个阻抗值能够确保信号的稳定传输,减小反射和干扰。

在设计过程中,应尽量使线路的电感和电容值接近100欧姆,以达到最佳的阻抗匹配效果。

三、AD四层板的层叠结构AD四层板是一种常见的印刷电路板(PCB)类型,其由四层导体和绝缘层组成。

其层叠结构对于实现100欧姆阻抗匹配至关重要。

通过合理配置电源和接地层、信号层的数量和位置,可以减小信号回路的电感和电容,从而提高阻抗匹配的效果。

四、微带线与带状线的选择在AD四层板设计中,微带线和带状线是两种常用的传输线类型。

微带线具有较低的辐射损耗和较高的特性阻抗,适用于高频信号传输。

带状线则具有较低的寄生电容和电感,适用于低频信号传输。

根据具体应用需求选择合适的传输线类型,可以提高阻抗匹配的效果。

五、线宽与间距的设计线宽和间距是影响线路阻抗的主要因素之一。

通过合理设计线宽和间距,可以调整线路的电感和电容值,从而实现最佳的阻抗匹配效果。

线宽越宽,间距越大,线路的电感和电容值越小,反之亦然。

在AD四层板设计中,应根据具体需求和参数进行线宽和间距的计算和选择。

六、层间耦合与串扰抑制在多层PCB中,层间耦合和串扰问题对阻抗匹配的影响不容忽视。

相邻层之间的信号线之间存在耦合电容和耦合电感,这会影响线路的阻抗值。

此外,当信号线之间的距离过近时,可能会产生串扰现象,影响信号的完整性。

为了减小层间耦合和串扰问题对阻抗匹配的影响,应合理设计层间布局和布线,保持适当的间距和采用噪声抑制措施。

通信设备面板英文介绍1A communication device panel is an important part that we often interact with. Let's take a router as an example.On the router panel, there are several key components. First, there is the power indicator. It's usually a small light. When it's on, it means the router is powered up and ready to work. It gives you a sense of security, like a little friend saying "I'm here and ready". Then, there are the network interfaces. These are the places where you can connect your Ethernet cables. They are like the doors for data to come in and go out of the router.For a mobile communication device panel, the signal display is very crucial. When you see several bars showing up, it tells you how strong the signal is. If there are many bars, you can feel relieved and know that you can make calls or use the Internet smoothly. And the keys on the panel also have their functions. For example, the power key can turn the device on and off. The volume keys can adjust the sound level so that you can hear clearly when having a call or listening to music.In general, understanding these components and their functions on the communication device panel can help us use these devices more effectively.中文翻译:通信设备面板是我们经常与之交互的重要部分。

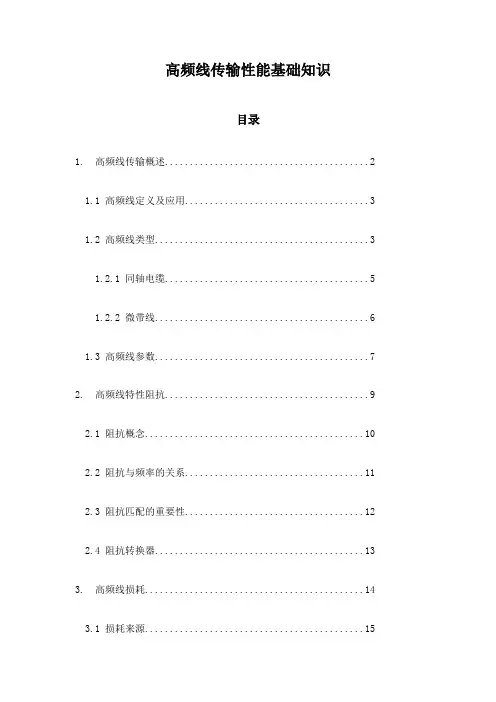

高频线传输性能基础知识目录1. 高频线传输概述 (2)1.1 高频线定义及应用 (3)1.2 高频线类型 (3)1.2.1 同轴电缆 (5)1.2.2 微带线 (6)1.3 高频线参数 (7)2. 高频线特性阻抗 (9)2.1 阻抗概念 (10)2.2 阻抗与频率的关系 (11)2.3 阻抗匹配的重要性 (12)2.4 阻抗转换器 (13)3. 高频线损耗 (14)3.1 损耗来源 (15)3.1.1 阻抗不匹配 (17)3.1.2 导体电阻 (18)3.1.3 ید电损耗 (19)3.2 损耗计算 (19)3.3 损耗与频率的关系 (20)3.4 降低损耗的方法 (22)4. 高频线传输特性 (23)5. 高频线应用案例 (24)5.1 射频 (RF) 系统 (25)5.2 产测线 (26)5.3 通信系统 (28)5.4 数据传输系统 (29)1. 高频线传输概述高频线传输(HighFrequency Wire Transmission, HFWT)是一种利用导线传输高频信号的通信方法。

与传统的低频传输相比,高频线传输能够在较短时间内传输大量信息,适合于高速数据传输、无线电通信以及雷达系统等领域。

本章节将概述高频线传输的基础知识、原理及其应用。

频率:在物理学中,频率是指单位时间内波形发生的次数,通常以赫兹(Hz)为单位。

高频信号意味着信号具有较高的频率分量。

波速:电磁波在介质中的传播速度称为波速,其值取决于介质的性质,例如光在真空中的波速接近光速c(300,000公里秒)。

带宽:带宽指的是信号频率范围的总和,通常以赫兹为单位表示。

频率从低到高,体现为一个特定的频段范围。

反射和折射:当高频信号波遇到不同介质的界面时,可能会发生反射和折射现象。

高频线传输的基本原理基于电磁场理论,当在导线上施加一个高频变化的电压时,会在导线上产生交变的电场,进而引发磁场的变化,从而在导线周围空间形成交变的电磁场。

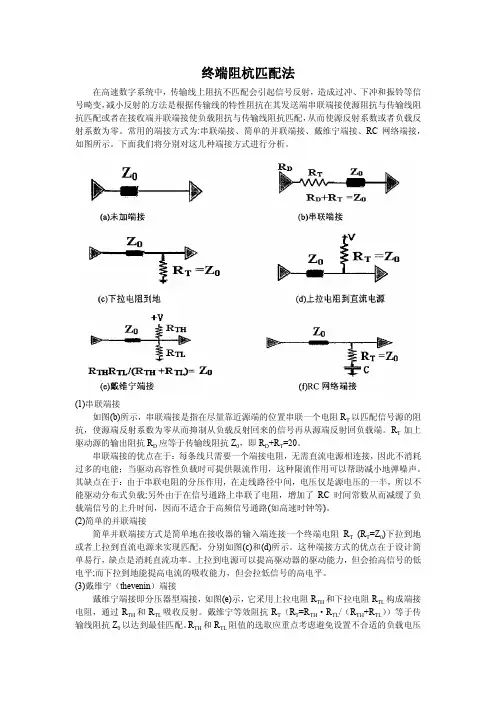

终端阻杭匹配法在高速数字系统中,传输线上阻抗不匹配会引起信号反射,造成过冲、下冲和振铃等信号畸变,减小反射的方法是根据传输线的特性阻抗在其发送端串联端接使源阻抗与传输线阻抗匹配或者在接收端并联端接使负载阻抗与传输线阻抗匹配,从而使源反射系数或者负载反射系数为零。

常用的端接方式为:串联端接、简单的并联端接、戴维宁端接、RC网络端接,如图所示。

下面我们将分别对这几种端接方式进行分析。

(1)串联端接如图(b)所示,串联端接是指在尽量靠近源端的位置串联一个电阻R T以匹配信号源的阻抗,使源端反射系数为零从而抑制从负载反射回来的信号再从源端反射回负载端。

R T加上驱动源的输出阻抗R D应等于传输线阻抗Z0,即R D+R T=20。

串联端接的优点在于:每条线只需要一个端接电阻,无需直流电源相连接,因此不消耗过多的电能;当驱动高容性负载时可提供限流作用,这种限流作用可以帮助减小地弹噪声。

其缺点在于:由于串联电阻的分压作用,在走线路径中间,电压仅是源电压的一半,所以不能驱动分布式负载;另外由于在信号通路上串联了电阻,增加了RC时间常数从而减缓了负载端信号的上升时间,因而不适合于高频信号通路(如高速时钟等)。

(2)简单的并联端接简单并联端接方式是简单地在接收器的输入端连接一个终端电阻R T(R T=Z0)下拉到地或者上拉到直流电源来实现匹配,分别如图(c)和(d)所示。

这种端接方式的优点在于设计简单易行,缺点是消耗直流功率。

上拉到电源可以提高驱动器的驱动能力,但会抬高信号的低电平;而下拉到地能提高电流的吸收能力,但会拉低信号的高电平。

(3)戴维宁(thevenin)端接戴维宁端接即分压器型端接,如图(e)示,它采用上拉电阻R TH和下拉电阻R TL构成端接电阻,通过R TH和R TL吸收反射。

戴维宁等效阻抗R T(R T=R TH·R TL/(R TH+R TL))等于传输线阻抗Z0以达到最佳匹配。

R TH和R TL阻值的选取应重点考虑避免设置不合适的负载电压参考电平,该电平用于高低逻辑变换点。

高速信号阻抗匹配机理高速信号阻抗匹配是电路设计中至关重要的一部分,因为在高速信号传输中,阻抗失配会导致信号反射和干扰,从而影响电路的性能。

在本文中,我们将探讨高速信号阻抗匹配机理。

什么是阻抗?阻抗是电路中的一种特性,它描述了电路对电流的阻碍程度。

与电阻不同,阻抗的值包含有频率和相位这两个方面,因此阻抗可以用复数的形式表示,即Z=R+jX,其中R是电阻,X是电感或电容的虚部。

阻抗失配的影响在高速信号传输中,阻抗失配会导致信号反射和干扰。

当信号到达阻抗失配处时,一部分信号将被反射回去,而另一部分信号将继续传输。

这些反射信号会干扰正在传输的信号,导致信号失真和噪声增加。

因此,在高速信号传输中,阻抗匹配是非常重要的。

如何进行阻抗匹配?阻抗匹配的目的是将发送器和接收器的阻抗匹配,以最大限度地减少信号反射和干扰。

常见的阻抗匹配技术包括:1. 阻抗变换器阻抗变换器是一种电路,可以将发送器或接收器的阻抗变换成适合另一端使用的阻抗。

例如,如果发送器的输出阻抗为50欧姆,而接收器的输入阻抗为100欧姆,那么可以使用阻抗变换器将发送器的输出阻抗变换成100欧姆,以匹配接收器的输入阻抗。

2. 背负线转换背负线转换是一种常见的阻抗匹配技术,可以用于将高速信号传输线的阻抗匹配。

在背负线转换中,将一条传输线的两端都连接到地面,可以将传输线的阻抗转换为两倍的值。

例如,如果一条传输线的阻抗为50欧姆,那么使用背负线转换后,它的阻抗将变成100欧姆。

3. 阻抗匹配电路阻抗匹配电路是一种特殊的电路,可以将发送器和接收器的阻抗匹配。

例如,可以使用一个高斯滤波器来将发送器的输出阻抗变换成适合接收器使用的阻抗。

此外,还可以使用串联电容或并联电感器来进行阻抗匹配。

总结。

LVDS(低电压差分信号)原理简介1 LVDS信号介绍LVDS:Low Voltage Differential Signaling,低电压差分信号。

LVDS传输支持速率一般在155Mbps(大约为77MHZ)以上。

LVDS是一种低摆幅的差分信号技术,它使得信号能在差分PCB线对或平衡电缆上以几百Mbps的速率传输,其低压幅和低电流驱动输出实现了低噪声和低功耗。

IEEE在两个标准中对LVDS信号进行了定义。

ANSI/TIA/EIA-644中,推荐最大速率为655Mbps,理论极限速率为1.923Mbps。

1.1 LVDS信号传输组成图1 LVDS信号传输组成图LVDS信号传输一般由三部分组成:差分信号发送器,差分信号互联器,差分信号接收器。

差分信号发送器:将非平衡传输的TTL信号转换成平衡传输的LVDS信号。

通常由一个IC来完成,如:DS90C031差分信号接收器:将平衡传输的LVDS信号转换成非平衡传输的TTL信号。

通常由一个IC来完成,如:DS90C032差分信号互联器:包括联接线(电缆或者PCB走线),终端匹配电阻。

按照IEEE规定,电阻为100欧。

我们通常选择为100,120欧。

1.2 LVDS信号电平特性LVDS物理接口使用1.2V偏置电压作为基准,提供大约400mV摆幅。

LVDS驱动器由一个驱动差分线对的电流源组成(通常电流为3.5mA),LVDS接收器具有很高的输入阻抗,因此驱动器输出的电流大部分都流过100Ω的匹配电阻,并在接收器的输入端产生大约350mV 的电压。

电流源为恒流特性,终端电阻在100――120欧姆之间,则电压摆动幅度为:3.5mA * 100 = 350mV ;3.5mA * 120 = 420mV 。

下图为LVDS与PECL(光收发器使用的电平)电平变化。

图2 LVDS与PECL电平图示由逻辑“0”电平变化到逻辑“1”电平是需要时间的。

由于LVDS信号物理电平变化在0。

阻抗匹配在高频设计中是一个常用的概念,下面对这个“阻抗匹配”进行解析。

阐述什么是阻抗匹配。

阻抗匹配(Impedance matching)是微波电子学里的一部分,主要用于传输线上,来达至所有高频的微波信号皆能传至负载点的目的,不会有信号反射回来源点,从而提升能源效益。

大体上,阻抗匹配有两种,一种是透过改变阻抗力(lumped-circuit matching),另一种则是调整传输线的波长(transmission line matching)。

要匹配一组线路,首先把负载点的阻抗值,除以传输线的特性阻抗值来归一化,然后把数值划在史密夫图表上。

改变阻抗力把电容或电感与负载串联起来,即可增加或减少负载的阻抗值,在图表上的点会沿著代表实数电阻的圆圈走动。

如果把电容或电感接地,首先图表上的点会以图中心旋转180度,然后才沿电阻圈走动,再沿中心旋转180度。

重覆以上方法直至电阻值变成1,即可直接把阻抗力变为零完成匹配。

调整传输线由负载点至来源点加长传输线,在图表上的圆点会沿著图中心以逆时针方向走动,直至走到电阻值为1的圆圈上,即可加电容或电感把阻抗力调整为零,完成匹配阻抗匹配则传输功率大,对于一个电源来讲,单它的内阻等于负载时,输出功率最大,此时阻抗匹配。

最大功率传输定理,如果是高频的话,就是无反射波。

对于普通的宽频放大器,输出阻抗50Ω,功率传输电路中需要考虑阻抗匹配,可是如果信号波长远远大于电缆长度,即缆长可以忽略的话,就无须考虑阻抗匹配了。

阻抗匹配是指在能量传输时,要求负载阻抗要和传输线的特征阻抗相等,此时的传输不会产生反射,这表明所有能量都被负载吸收了.反之则在传输中有能量损失。

高速 PCB布线时,为了防止信号的反射,要求是线路的阻抗为50欧姆。

这是个大约的数字,一般规定同轴电缆基带50欧姆,频带75欧姆,对绞线则为100欧姆,只是取个整而已,为了匹配方便.阻抗从字面上看就与电阻不一样,其中只有一个阻字是相同的,而另一个抗字呢?简单地说,阻抗就是电阻加电抗,所以才叫阻抗;周延一点地说,阻抗就是电阻、电容抗及电感抗在向量上的和。

2022.12 物联网应用师(初级)考前冲刺题A1卷1.【单选题】当软件给感知数据赋予一定的背景时,比如“温度18°,湿度25%”,像这样拥有背景的数据称为( )。

A:数据B:信息C:知识D:智能决策正确答案:B答案解析:拥有背景的数据就是信息。

2.【单选题】物联网的英文表述是()。

A:Block-chainB:Aritifitial IntelligenceC:Internet of ThingsD:Edge正确答案:C答案解析:Internet of Things3.【单选题】在Wi-Fi网络中,称提供AP之间互联的系统为( )。

A:SATB:APC:BSSD:DS正确答案:D答案解析:Wi-Fi网络的组成部分4.【单选题】在物联网体系结构中,()能让物品“开口说话、发布信息”,是融合物理世界和信息世界的重要一环。

A:控制器B:感知层C:网络层D:数据层正确答案:B答案解析:物联网感知层5.【单选题】嵌入式系统的软件体系和通用计算机软件体系类似,下列哪个不属于软件系统的分层( )。

A:驱动层B:指令层C:操作系统层D:应用层正确答案:B答案解析:嵌入式系统的组成6.【单选题】通过标签和阅读器实现的定位方法是( )。

A:Wi-Fi定位技术B:移动通信定位技术C:RFID定位技术D:无线传感网络定位技术正确答案:C答案解析:RFID的定位原理是,通过一组固定的阅读器读取目标RFID标签的特征信息,采用近邻法、多边定位法、接收信号强度等方法确定标签所在位置。

7.【单选题】目前常见串行通信接口标准描述错误的一项是( )。

A:RS-232——常用于计算机与外部设备间通信,是一种异步通信B:RS-485——工业总线标准,能够有效支持多个分节点,通信距离远,常用于工业设备间通信,是一种异步通信C:CAN——常用于工业设备或分离式系统模块间以及汽车内部设备间的通信,是一种异步通信D:SPI——常用于板级元件或模块间通信,如SPI总线FLASH闪存,是一种异步通信正确答案:D8.【单选题】物联网的英语缩写是( )。

电子设备的组装设计就必须考虑信号完整性的设计与实现问题,在模拟电路中,由于采用的是单频或窄频带信号,实现电路功能最关心的是信噪比,通常不需要讨论信号波形和波形畸变。

但是,在数字电路中实现电路功能的方式发生了根本性的变化:采用的信号为周期脉冲,工作的方式是突发性的,逻辑关系成为核心,需要严格保证时间间隔和时序关系。

于是,就提出了保证信号完整性的设计要求。

一般可以认为信号完整性应该包括如下几点含义:信号的波形畸变应该控制在一定的范围之内,信号流的时序图能满足逻辑要求,在突发状态下信号的产生与传输过程平稳。

信号完整性的破坏主要来源于两个原因,首先是由于外界干扰,特别是传导通道的干扰包括传输通道阻抗失配造成的反射影响,破坏了原来的波形;其次,数字信号在传播时会自然地发生频谱分散效应,改变了原来的波形。

当时钟频率比较高时,例如时钟达到10MHz以上或脉冲的边沿时间达到1ns 以下时,我们会发现将信号传输到预想的地方并不很容易,有许多因素会影响信号完整性问题,其中包括抖动、延迟、地电位弹跳、反射、串扰、开关噪声、电源失配、衰减、脉冲展宽、时序混乱等问题。

信号完整性问题总是要涉及信号的整个过程,因此,信号完整性保证需要整个信号工作的物理环境来实现。

为此,有必要建立信号完整性系统模型。

信号完整性系统模型应该包括完整信号源、信号的物理协调通道、信号完整接收三个部分。

三个部分主要内容如下:(1)完整信号源:保证产生信号的完整性。

其中包括电源保证、噪声的滤除、地电位、共模消除、输出阻抗保证等内容。

(2)信号的物理协调通道: 保障信号在传输中不发生改变。

其中包括:串音、延时、通道陷落、反射和谐振、带宽、衰减、阻抗控制、电路链接等等。

(3)信号完整接收:保证无失真地高效率地接收。

其中包括:输入阻抗匹配、接地处理、多端网络互阻抗、退耦电容、滤波电容、输入网络信号分配和信号保护等问题。

信号完整性系统模型可以示意地画成下图的形式。

随着信息宽带化和高速化的发展,以前的低速PCB已完全不能满足日益增长信息化发展的需要,人们对通信需求的不断提高,要求信号的传输和处理的速度越来越快,相应的高速PCB的应用也越来越广,设计也越来越复杂。

高速电路有两个方面的含义,一是频率高,通常认为数字电路的频率达到或是超过45MHZ 至50MHZ,而且工作在这个频率之上的电路已经占到了整个系统的三分之一,就称为高速电路;二是从信号的上升与下降时间考虑,当信号的上升时小于6倍信号传输延时时即认为信号是高速信号,此时考虑的与信号的具体频率无关。

高速PCB的出现将对硬件人员提出更高的要求,仅仅依靠自己的经验去布线,会顾此失彼,造成研发周期过长,浪费财力物力,生产出来的产品不稳定。

高速电路设计在现代电路设计中所占的比例越来越大,设计难度也越来越高,它的解决不仅需要高速器件,更需要设计者的智慧和仔细的工作,必须认真研究分析具体情况,解决存在的高速电路问题。

一般说来主要包括三方面的设计:信号完整性设计、电磁兼容设计、电源完整性设计。

在电子系统与电路全面进入1GHz以上的高速高频设计领域的今天,在实现VLSI芯片、PCB和系统设计功能的前提下具有性能属性的信号完整性问题已经成为电子设计的一个瓶颈。

从广义上讲,信号完整性指的是在高速产品中有互连线引起的所有问题,它主要研究互连线与数字信号的电压电流波形相互作用时其电气特性参数如何影响产品的性能。

传统的设计方法在制作的过程中没有仿真软件来考虑信号完整性问题,产品首次成功是很难的,降低了生产效率。

只有在设计过程中融入信号完整性分析,才能做到产品在上市时间和性能方面占优势。

对于高速PCB设计者来说,熟悉信号完整性问题机理理论知识、熟练掌握信号完整性分析方法、灵活设计信号完整性问题的解决方案是很重要的,因为只有这样才能成为21世纪信息高速化的成功硬件工程师。

信号完整性的研究还是一个不成熟的领域,很多问题只能做定性分析,为此,在设计过程中首先要尽量应用已经成熟的工程经验;其次是要对产品的性能做出预测和评估以及仿真。

在高速电路中最小化信号反射具有阻抗匹配的多层互联结构Soorya Krishna K and M. S. Bhat摘要——集成电路工作在吉赫兹(GHz)频率时通过互联结造成的阻抗不匹配引起的信号反射,是信号完整性的一个主要问题。

在此文章中,我们提出一个方法来减少这种通过诱导信号反射在芯片上的总体的互联线。

我们可以得出,在交界片上适当加入一个电容性负载,可以实现阻抗匹配,并派生出用来确定被添加在互联结的电容的表达式。

仿真结果表明,在1GHz到10GHz的频率范围内使用65nm 技术这种方法使得信号反射减小至少-10dB。

以下提出的方法是检测两种类型的模型:(i)通过一个单一的连接点连接两个互联层。

(ii)从6层到1层通过5个过孔的两个互联层。

索引——互连线,信号反射,过孔I、简介数百万个元器件集成在单一集成电路(IC)芯片上的超大规模集成电路(VLSI)技术已经超过了8个金属层[1],紧密地放置在不同的互联层的IC芯片和被广泛使用的通孔来连接不同的金属层。

随着数据通信速度超过1千兆比特每秒的增加,在成功传输数据方面,信号完整性成为越来越重要的角色。

在交界处阻抗的不连续和整体的互连线导致了信号反射和信号的损失。

在信号的传输中,为了增加效率,设计师尽可能的消除每一个沿高速信号路径的阻抗不匹配,因为这些不连续性会产生抖动,降低眼图的张开率和最大限度的传输数据。

两个金属层过孔之间不恰当的连接,产生了很明显的击穿电压,信号衰减,串扰,开关噪声等等。

对不同类型过孔的研究,他们的性质和影响传播的信号是由[2]-[5]。

电路板的过孔是很小的,在以低频率运行时,焊盘被忽视或者近似为电容和电感,当信号传输频率超过1GHz时,焊盘需要建模为分布式RLC结构。

在将来,由于扩展的需要,节点会越来越少,但通过阻力大幅增加(0.3Ω~0.7nm-8Ω~90nm)[6]。

不同技术文献中多层互联结构中减少信号反射的描述各不相同,输电线路的形状通过帮助减少附近信号反射和表现在[7]。

武汉理工大学班级:___电子与通信工程153班_____姓名:_________ ___________学号:_______________教师:____ ____________¥高速电路传输线反射问题分析与解决(武汉理工大学信息工程学院,武汉,430070)摘要:高速数字信号的传输线反射问题是影响现代数字电路设计的重要原因因素之一,严重的反射将破坏信号的完整性,并引起过冲现象,从而出现错误的数字逻辑和影响电路上元器件的正常使用。

本文重点的分析高速电路中信号反射产生的原因,和给出解决反射问题的方案。

关键词:传输线;反射;解决方案Abstract: Reflection high-speed digital signal is an important factor affecting the modern digital circuit design, serious reflection would undermine the integrity of the signal, and cause overshoot phenomenon, which appears erroneous digital logic and destruction devices. This paper analyzes in detail the causes of signal reflections and phenomena, and give a reflection solution.)Keyword: Transmission line;reflection; solution1.引言反射就是在传输线上的回波,如果传输线的长度满足长线时,且没有合适的终端匹配,那么来自于驱动端的信号脉冲在接收端被反射,从而引起非预期效应,使信号轮廓失真。

反射是传输线的基本效应,即当信号沿着传输线传输时,碰到阻抗不连续时会发生反射。