I2C总线简介(很经典)

- 格式:docx

- 大小:356.96 KB

- 文档页数:12

i2c电平采样时间点摘要:1.I2C总线简介2.I2C电平采样原理3.I2C电平采样时间点的重要性4.影响I2C电平采样时间点的因素5.优化I2C电平采样时间点的方法6.总结正文:i2c电平采样时间点是I2C(Inter-Integrated Circuit)总线通信中的一个重要概念。

I2C总线是一种串行通信总线,它主要由两条信号线组成:数据线(SDA)和时钟线(SCL)。

在I2C通信过程中,数据的传输离不开电平采样。

本文将从I2C总线简介、I2C电平采样原理、I2C电平采样时间点的重要性等方面进行阐述,并提出影响因素及优化方法。

1.I2C总线简介I2C总线是由Philips(现为NXP)公司在1980年代研发的一种串行通信总线,主要用于低速、短距离的双向通信。

I2C总线具有简单的硬件接口和较高的灵活性,可连接多个外部设备。

在众多嵌入式系统中,I2C总线已成为一种常用的通信方式。

2.I2C电平采样原理I2C电平采样是基于I2C总线上的电平状态进行的。

在I2C通信过程中,数据线SDA和时钟线SCL的电平状态会随着数据传输而发生变化。

在每个时钟周期内,电平采样点对数据线SDA的电平进行检测,以判断当前传输的数据。

电平采样点通常在SDA线上的高电平或低电平状态结束时进行。

3.I2C电平采样时间点的重要性I2C电平采样时间点对于数据传输的正确性具有至关重要的作用。

合适的电平采样时间点可以确保数据的准确性,降低误判率。

如果电平采样时间点设置不当,可能导致数据传输错误,影响系统的正常运行。

4.影响I2C电平采样时间点的因素影响I2C电平采样时间点的因素主要有:- 总线速度:总线速度越高,电平采样时间点越重要。

- 设备延迟:不同设备响应速度的差异,可能导致电平采样时间点的调整。

- 噪声干扰:噪声干扰可能导致电平采样点出现偏差,影响数据传输的正确性。

5.优化I2C电平采样时间点的方法优化I2C电平采样时间点的方法包括:- 合理设置采样触发条件:根据实际需求,合理设置电平采样触发条件,提高数据准确性。

I2C总线原理介绍AT24C02内部原理介绍I2C总线原理介绍:I2C (Inter-Integrated Circuit)总线是一种用于在集成电路之间进行通信的串行通信总线协议。

它最初由飞利浦半导体公司(现在的NXP半导体)开发,旨在解决多个IC之间的通信问题。

I2C总线协议包括了两种设备,即主设备和从设备。

主设备负责控制总线及发送和接收数据,而从设备则依从主设备的控制。

主设备通过发送一个起始条件开始通信,并通过发送地址和数据进行控制。

从设备则根据主设备发送的地址和数据进行相应的响应。

1.双向通信:I2C总线允许主设备和从设备之间双向通信,即主设备可以发送数据给从设备,也可以从从设备接收数据。

2.多主模式:I2C总线支持多个主设备同时驱动总线,这可以实现多个主设备之间的协同工作。

3.硬件地址和数据传输:I2C总线使用7位或10位地址来寻址从设备,并以字节为单位传输数据。

4.起始和停止条件:I2C总线使用起始和停止条件来控制通信的开始和结束。

5.错误检测:I2C总线通过校验和来检测传输过程中的错误。

6.时钟同步:I2C总线使用时钟信号来同步主设备和从设备之间的通信。

AT24C02内部原理介绍:AT24C02是一种常见的I2C EEPROM (Electrically Erasable Programmable Read-Only Memory)芯片,用于存储数据。

它的内部原理如下:1.存储单元:AT24C02由256个8位字节构成,每个字节具有一个唯一的地址。

地址范围从0到255,可以存储共计2048位的数据。

2.寻址和读写:AT24C02通过I2C总线进行寻址和读写操作。

主设备发送启始条件和设备地址,然后发送要读取或写入的数据的地址,最后发送或接收实际数据。

3.数据传输:AT24C02的数据以字节为单位被写入和读取。

写入操作通过I2C总线将字节数据写入到指定地址处。

读取操作通过I2C总线将字节数据从指定地址读出。

I2C总线——总结I2C总线是一种串行数据通信协议,用于连接集成电路之间进行通信。

它由Phillips公司于1982年首次提出,并在随后的几十年中得到广泛应用和发展。

I2C总线采用两根线(SDA和SCL)进行通信,具有简单、高效的特点,适用于较短距离的通信。

首先,I2C总线的架构包括两个主要组成部分:主设备和从设备。

主设备通常是微控制器或其他控制器,负责发起和控制通信。

从设备是主设备的外围设备,例如传感器、电池芯片、存储器等。

主设备通过发送信号来控制从设备,并接收从设备发送的响应信号。

在I2C通信中,数据以字节为单位传输,每个字节都包含8位。

通信的起始由主设备发起,并发送设备地址标识。

从设备必须匹配该地址才能进入通信状态。

在通信过程中,主设备发送读取或写入指令,然后发送或接收数据。

每个数据字节都由从设备发送确认信号,以确保数据的准确接收。

除了基本的读写操作,I2C总线还支持一些高级功能,例如时钟同步、主从模式切换和热插拔功能。

这些功能使得I2C总线适用于各种应用场景,包括电子设备、通信系统、工业控制和汽车电子等。

然而,尽管I2C总线具有许多优点,但也存在一些限制和挑战。

首先,I2C总线在传输速度方面不如其他通信协议(如SPI和CAN)。

其次,长距离传输可能受到电压下降、信号失真和干扰等因素的影响。

此外,I2C总线的主设备需要额外的控制逻辑和处理能力,这可能增加系统的复杂性和成本。

综上所述,I2C总线是一种非常常用和实用的串行通信协议。

它具有简单、高效的特点,适用于较短距离的设备间通信。

通过多主机配置和高级功能支持,I2C总线可以满足各种应用的需求。

然而,需要根据具体的应用场景和要求来选择合适的通信协议,以确保系统的性能和可靠性。

一. I2C总线简介I2C管理总线:(Intel-Integrated Circuit bus)I2C总线是一种由飞利浦Philip公司开发的串行总线,产生于80年代,最初为音频和视频设备开发,现主要在服务器管理中使用。

是两条串行的总线,它由一根数据线(SDA)和一根时钟线(SDL)组成。

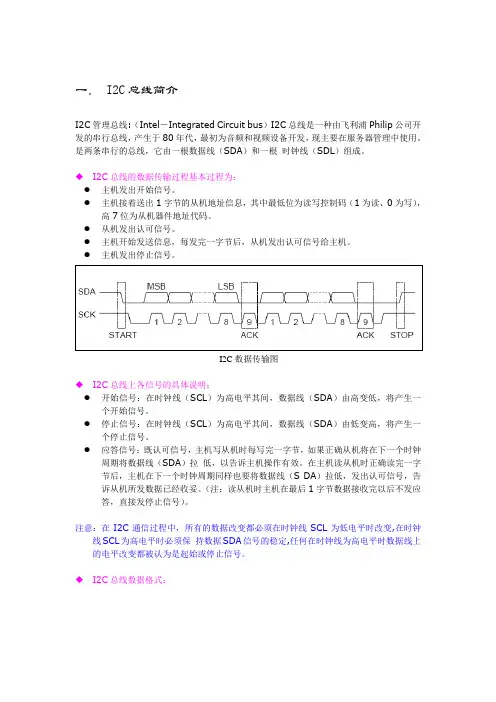

◆I2C总线的数据传输过程基本过程为:●主机发出开始信号。

●主机接着送出1字节的从机地址信息,其中最低位为读写控制码(1为读、0为写),高7位为从机器件地址代码。

●从机发出认可信号。

●主机开始发送信息,每发完一字节后,从机发出认可信号给主机。

●主机发出停止信号。

I2C数据传输图◆I2C总线上各信号的具体说明:●开始信号:在时钟线(SCL)为高电平其间,数据线(SDA)由高变低,将产生一个开始信号。

●停止信号:在时钟线(SCL)为高电平其间,数据线(SDA)由低变高,将产生一个停止信号。

●应答信号:既认可信号,主机写从机时每写完一字节,如果正确从机将在下一个时钟周期将数据线(SDA)拉低,以告诉主机操作有效。

在主机读从机时正确读完一字节后,主机在下一个时钟周期同样也要将数据线(S DA)拉低,发出认可信号,告诉从机所发数据已经收妥。

(注:读从机时主机在最后1字节数据接收完以后不发应答,直接发停止信号)。

注意:在I2C通信过程中,所有的数据改变都必须在时钟线SCL为低电平时改变,在时钟线SCL为高电平时必须保持数据SDA信号的稳定,任何在时钟线为高电平时数据线上的电平改变都被认为是起始或停止信号。

◆I2C总线数据格式:I2C数据格式图I2C支持两种数据格式:_ 7-bit/10-bit 寻址数据格式_ 7-bit/10-bit 寻址和重复开始信号的数据格式✧S ―I2C 开始标识✧Slava address ―从设备地址。

有两种从地址类型:1)固定的从地址,I2C总线只能接一个同类型的固定的从地址设备。

2)半固定的从地址,前半部分地址是固定的,后半部分地址是可编程的,I2C总线只能接多个同类型的半固定的从地址设备。

1 I2C总体介绍I2C总线是由PHILIPS公司开发的两线式串行总线,用于连接微控制器及其外围设备。

是微电子通信控制领域广泛采用的一种总线标准。

它是同步通信的一种特殊形式,具有接口线少,控制方式简单,器件封装形式小,通信速率较高等优点。

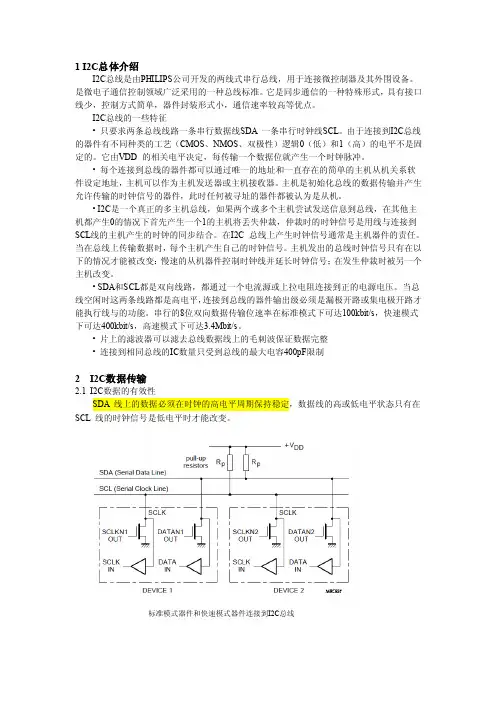

I2C总线的一些特征•只要求两条总线线路一条串行数据线SDA一条串行时钟线SCL。

由于连接到I2C总线的器件有不同种类的工艺(CMOS、NMOS、双极性)逻辑0(低)和1(高)的电平不是固定的。

它由VDD 的相关电平决定,每传输一个数据位就产生一个时钟脉冲。

•每个连接到总线的器件都可以通过唯一的地址和一直存在的简单的主机从机关系软件设定地址,主机可以作为主机发送器或主机接收器。

主机是初始化总线的数据传输并产生允许传输的时钟信号的器件,此时任何被寻址的器件都被认为是从机。

• I2C是一个真正的多主机总线,如果两个或多个主机尝试发送信息到总线,在其他主机都产生0的情况下首先产生一个1的主机将丢失仲裁,仲裁时的时钟信号是用线与连接到SCL线的主机产生的时钟的同步结合。

在I2C 总线上产生时钟信号通常是主机器件的责任。

当在总线上传输数据时,每个主机产生自己的时钟信号。

主机发出的总线时钟信号只有在以下的情况才能被改变:慢速的从机器件控制时钟线并延长时钟信号;在发生仲裁时被另一个主机改变。

• SDA和SCL都是双向线路,都通过一个电流源或上拉电阻连接到正的电源电压。

当总线空闲时这两条线路都是高电平,连接到总线的器件输出级必须是漏极开路或集电极开路才能执行线与的功能。

串行的8位双向数据传输位速率在标准模式下可达100kbit/s,快速模式下可达400kbit/s,高速模式下可达3.4Mbit/s。

•片上的滤波器可以滤去总线数据线上的毛刺波保证数据完整•连接到相同总线的IC数量只受到总线的最大电容400pF限制2I2C数据传输2.1I2C数据的有效性SDA线上的数据必须在时钟的高电平周期保持稳定,数据线的高或低电平状态只有在SCL 线的时钟信号是低电平时才能改变。

12 C总线入门I)最近学习5 1单片机,学到A/D, D/A转换的时候发现我板子上的转换芯片•不是书上所讲的ADCO 8 0 4和DACO 8 3 2而是P CF 8 591 T ,看了一下它的数据手册,发现它并不是书上所说的并行传输数据,是使用I2C总线传输的。

搞了两天才搞懂,写出来给大家分享一下,不足之处请务必不吝指岀。

1. i?c gtt 介绍I J C Ata(IMer IC Bu≤) Ih PHlUPS公司捡Hl∙绘近"束锻电FMIm控Sw皱城广泛采冊的M标ML它肚附通信的Jlff按口仪少■控Mm*>妙件MKB :仁违估JaE较扁第优点.Λ hΛ⅛f∣M∙.砒以“7个总IUl件的时按到Fc总线上•Af?的暮件AJl川知0的按【】• Ii过淮址来谏別迪仃对叙便它们町以性曲l j CJ^ it irdMur.I J Cfitt由数飙嫂SDA和时伸饮$ci・IWi剣农购成通仙找烁Kt町发iX&«.也廨・Λ CPυ1J≪F? ICZrn]∙ IC I HCZrWJΛ5<Oh ¾l⅛αiX.为40Ok协.⅛冲檢检器件均幷联比总找1:•但树个畐件秋冋的地址•花仿息传输过程中.FC总找匕井联的婷TsB件Bt 足粧担11(咸主检as人(Λft½ah这取决F它所宴知®的功能∙CPU发出的控制仙号分为地址印和敦IK 码曲挪分X 颐码用來选⅛L即按通;U婆控制的电Wh數!K码足遇倚的内笫这样#IC控财电*总饯匕妙彼此独t以上是I2C总线的简单介绍。

就比如说AT 2 4C0 2存储芯片,和PCF8591数模模数转换芯片都支持I 2C端口。

(如下图)8-lead PDlP以上是I 2 C 总线通信的格式。

21 82 34 AOE Al 匚 A2□ GND 匚 □ VCC WP ZJS □ SDAA N N3 AI NV 辽叵rlF匡叵Jθ] v DD 回 AoUT 回 迢 AGND PCFδ591P — 卫IExT 2 )接下来看如何使用I 2C 总线进行通信 3. FC 总线通信格式 图8.1.2为I 2C 总线上进厅一次数据传输的通信格式• N A山上图可以看出进行通信需要以下儿个步骤a.初始化I 2 C总线就是把SDA和SCL都变成高电平。

I2C总线入门1)最近学习51单片机,学到A/DQ/A转换的时候发现我板子上的转换芯片不是书上所讲的ADC0804和DAC0832而是PCF859仃,看了一下它的数据手册, 发现它并不是书上所说的并行传输数据,是使用I2C总线传输的。

搞了两天才搞懂,写出来给大家分享一下,不足之处请务必不吝指出。

! ≡tt f Itiief II R J Ih PHiLlPSt j ΓC bFC 口対由⅞⅛⅞κΓt r SDA IUB L f W r■I. SeiL閃離找L#參G [⅛总蠻H件嗣时Mtfl ι⅛X⅛ttStM'QUIA ft/i CPU 1√ Kf?IC ZlHh IC J J Ie Z糾幣町遊i;I^I ILW*s4t∣ιIkh i P"⅛.BtflK硏是Jl伯的内评.iaiT IT K以上是I2C总线的简单介绍。

就比如说AT24C02存储芯片,和PCF8591数模模数转换芯片都支持I2C端口(如下图)2)接下来看如何使用I2C总线进行通信3. I S C总线通信格式图8,i+2 ⅛ PC总统上进彳J -次数撫传输的通信格式HJ. λ5WuJΓ IMPuJT λWλ√[T+ *1⅛∕'f ⅛ff融戟代答ftK >⅛祎:J*j*hrn⅛释止他号图S.I .2 I3C总纽上遊打谀散据传输的JfflG⅛A 以上是I2C 总线通信的格式。

由上图可以看出进行通信需要以下几个步骤S-Iead PDlPAOL1 8□ VCCAl匚⅛WPA2匚3GND匚4£AJNOITU迴VDDAINlI 2ISj AOUTAIN2 3]回” RE FAIN3 I 41^I3] AGNDPCF8591PAO ^5∏^↑2∖ EXTAt叵TrlOSCA2 T/JO)SeL^kVSS叵(VJ SDAIH2引脚图(Dlla.初始化I2C总线就是把SDA和SCL都变成高电平。

Void in it() 〃初始化{SDA=1;delay();SCL=1;delay();}delay ()为延时函数void delay() 〃延时4-5个微秒{;;}b.发送起始信号就是保持SCL为高电平,而SDA从高电平降为低电平(这是I2C总线的规定, 别问我为什么)void Start()// 起始信号{SDA=1;delay();SCL=1;delay();SDA=0;delay();}C.发送地址字(芯片的硬件地址)74地址12C总线象统中的每一片PCF859J通过发送有效地址封该黠件来激活。

历史悠久的I2C总线今天,我们来重温一下历史悠久的I2C总线。

I2C(Inter-Integrated Circuit,内部集成电路总线)是由Philips公司开发的两线式串行总线,用于连接微控制器及其外围设备。

它是微电子通信控制领域广泛采用的一种总线标准,是同步通信的一种特殊形式,具有接口线少,控制方式简单,器件封装形式小,通信速率较高等优点。

第一代具有I2C总线功能的集成电路出现于30多年前,1982年由飞利浦半导体公司(Philips Semiconductor)开发,它是简单的串行总线,用于控制电视机内的各种芯片。

虽然I2C历史悠久,但现在它仍在不断改进中,出现了很多改进之处,例如,使用差分信号以改进抗噪声能力,改进总线仲裁以便更容易将总线连接在一起。

I2C总线版本演进I2C总线代表了全行业的规范,共经历了4个版本。

最新版本于2012年推出,总线的运行速度已经由原来的100kHz 升至5MHz。

我们先对I2C总线的历史作一个简短回顾。

1.0版本的规范发布于1992年,运行速度可达400KHz。

1998年的2.0版本增加了一个高速模式和若干节能选项。

2007年的主要规范将运行速度升至1MHz(快速模式Plus或Fm+)。

2012年最近的一次版本升级引入了一个单向5MHz的可选项,称之为超快速模式(UFm)。

I2C总线发生了许多变化。

有一些名称的更改是出于对飞利浦半导体公司在总线某些关键技术上的专利权保护。

原专利已于2004年过期,所有商标和知识产权转移到NXP半导体公司(2006年从飞利浦公司分拆出来)。

I2C总线是ACCESS.总线、VESA显示数据信道(DDC)接口、系统管理总线(SMBus)、电源管理总线(PMBus)和智能平台管理总线(智能平台管理接口)的通信协议。

I2C总线的构成及信号类型I2C总线是由数据线SDA和时钟SCL 构成的串行总线,可发送和接收数据。

在IC与IC之间进行双向传送,最高传送速率100kbps。

I2C总线1.简介I2C(Inter-IC)总线10多年前由Philips公司推出,是近年来在微电子通信控制领域广泛采用的一种新型总线标准。

它是同步通信的一种特殊形式,具有接口线少,控制方式简化,器件封装形式小,通信速率较高等优点。

在主从通信中,可以有多个I2C总线器件同时接到I2C总线上,通过地址来识别通信对象。

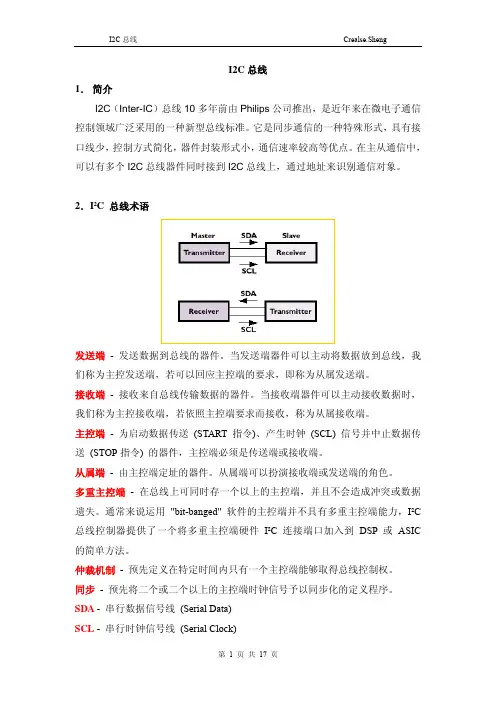

2.I²C 总线术语发送端 - 发送数据到总线的器件。

当发送端器件可以主动将数据放到总线,我们称为主控发送端,若可以回应主控端的要求,即称为从属发送端。

接收端- 接收来自总线传输数据的器件。

当接收端器件可以主动接收数据时,我们称为主控接收端,若依照主控端要求而接收,称为从属接收端。

主控端 - 为启动数据传送 (START 指令)、产生时钟 (SCL) 信号并中止数据传送 (STOP指令) 的器件,主控端必须是传送端或接收端。

从属端 - 由主控端定址的器件。

从属端可以扮演接收端或发送端的角色。

多重主控端 - 在总线上可同时存一个以上的主控端,并且不会造成冲突或数据遗失。

通常来说运用 "bit-banged" 软件的主控端并不具有多重主控端能力,I²C 总线控制器提供了一个将多重主控端硬件 I²C 连接端口加入到 DSP 或 ASIC 的简单方法。

仲裁机制- 预先定义在特定时间内只有一个主控端能够取得总线控制权。

同步 - 预先将二个或二个以上的主控端时钟信号予以同步化的定义程序。

SDA- 串行数据信号线 (Serial Data)SCL - 串行时钟信号线 (Serial Clock)3.I2C总线结构I2C 总线上数据的传输速率在标准模式下可达100kbit/s,在快速模式下可达400kbit/s,在高速模式下可达3.4Mbit/s。

I2C串行总线一般有两根信号线,一根是双向的数据线SDA,另一根是时钟线SCL。

所有接到I2C总线设备上的串行数据SDA都接到总线的SDA上,各设备的时钟线SCL接到总线的SCL上。

i2c上拉电阻压降I2C总线是一种常用的串行通信协议,广泛应用于各种电子设备中。

在I2C总线中,上拉电阻起着重要的作用,它能够确保信号的正常传输和稳定性。

本文将以I2C上拉电阻压降为主题,介绍其原理、作用和选择方法。

一、I2C总线简介I2C(Inter-Integrated Circuit)总线是一种由飞利浦公司提出的串行通信协议,广泛应用于各种数字集成电路之间的通信。

它采用两根传输线(SDA和SCL),能够同时连接多个设备,实现高效的数据传输。

二、上拉电阻的作用在I2C总线中,上拉电阻起着重要的作用。

由于I2C总线是开漏输出的,即总线上的设备只能拉低总线,而不能直接拉高。

为了确保总线上的信号能够正常传输,需要通过上拉电阻将总线上的电平拉高。

上拉电阻的作用主要有两个方面:1. 确保总线上的信号能够正常传输:上拉电阻使总线上的电平在空闲时保持高电平,只有当设备需要发送低电平时,才能拉低总线电平。

这样可以避免总线上的信号冲突,确保数据传输的稳定性。

2. 提供设备的地址:在I2C总线中,每个设备都有唯一的地址,上拉电阻通过将总线电平拉高,为设备提供一个默认的地址。

当设备需要发送数据时,可以通过改变总线电平来通知其他设备。

三、上拉电阻的原理上拉电阻的原理很简单,它利用电阻的特性将总线电平拉高。

当总线上没有设备拉低总线电平时,上拉电阻将总线电平拉高到高电平,确保总线上的信号稳定。

上拉电阻的阻值选择很重要,一般常用的阻值为4.7kΩ。

选择合适的阻值可以在保证总线电平稳定的同时,降低功耗和电流消耗。

四、如何选择上拉电阻选择上拉电阻时,需要考虑以下几个因素:1. 总线上的设备数量:如果总线上连接的设备较多,电流消耗也会相应增加。

因此,需要根据总线上设备的数量来选择合适的电阻阻值,以平衡功耗和稳定性。

2. 总线长度:总线的长度越长,电阻的值也需要相应增加,以保证电平的稳定性。

如果总线长度超过一定范围,可能需要采取其他措施来弥补信号衰减。

I2C总线1.I2C(Inter-Integrated Circuit)总线是一种由PHILIPS公司开发的两线式串行总线,用于连接微控制器及其外围设备。

2. 在消费者电子和工业电子中应用很多:例如:微控器(MCU)LCD、外设PHY芯片、RAM、EEPROM等3. I2C 总线的一些特征:●只要求两条总线线路一条串行数据线SDA 一条串行时钟线SCL●每个连接到总线的器件都可以通过唯一的地址和一直存在的简单的主机、从机关系软件设定地址主机可以作为主机发送器或主机接收器●它是一个真正的多主机总线如果两个或更多主机同时初始化数据传输可以通过冲突检测和仲裁防止数据被破坏●串行的8 位双向数据传输位速率在标准模式下可达100kbit/s快速模式下可达400kbit/s 高速模式下可达3.4Mbit/s●片上的滤波器可以滤去总线数据线上的毛刺波保证数据完整4. 在I2C 总线上产生时钟信号通常是主机器件提供5. SDA和SCL都是双向的线路,他们的电位标准取决于逻辑“0”和“1”6. SDA 线上的数据必须在时钟的高电平周期保持稳定数据线的高或低电平状态只有在SCL 线的时钟信号是低电平时才能改变7.起始和停止条件8. 发送到SDA 线上的每个字节必须为8 位每次传输可以发送的字节数量不受限制每个字节后必须跟一个响应位。

在响应的时钟脉冲期间接收器必须将SDA 线拉低使它在这个时钟脉冲的高电平期间保持稳定的低电平9. 数据传输的地址格式数据的传输遵循下图所示的格式在起始条件S 后发送了一个从机地址这个地址共有7位,紧接着的第8 位是数据方向位R/W :0 表示发送写1 表示请求数据读。

典型器件:AT24C系列EEPROM参考它的datasheetP2是它的结构图P3页是管脚定义P6是设备的操作参考时序p11-p12一般的测试设计流程:●根据设计的规格书,设计需要测试的接口,总线模型●定义要测试的功能列表,对测试进行分类●确定各个测试案例(testcase)的内容、个数BFM: (Bus Function Model ) 总线功能模型BFM应该描述的是具有某种具体功能的电路。

I2C总线简介1.概述:I²C是Inter-Integrated Circuit的缩写,发音为"eye-squared cee" or"eye-two-cee", 它是一种两线接口。

I²C 只是用两条双向的线,一条 Serial Data Line (SDA) ,另一条Serial Clock (SCL)。

SCL:上升沿将数据输入到每个EEPROM器件中;下降沿驱动EEPROM器件输出数据。

(边沿触发)SDA:双向数据线,为OD门,与其它任意数量的OD与OC门成"线与"关系。

2.输出级每一个I2C总线器件内部的SDA、SCL引脚电路结构都是一样的,引脚的输出驱动与输入缓冲连在一起。

其中输出为漏极开路的场效应管,输入缓冲为一只高输入阻抗的同相器,这种电路具有两个特点:1)由于SDA、SCL为漏极开路结构(OD),因此它们必须接有上拉电阻,阻值的大小常为1k8, 4k7 and 10k ,但1k8 时性能最好;当总线空闲时,两根线均为高电平。

连到总线上的任一器件输出的低电平,都将使总线的信号变低,即各器件的SDA及SCL都是线"与"关系。

2)引脚在输出信号的同时还将引脚上的电平进行检测,检测是否与刚才输出一致,为"时钟同步"和"总线仲裁"提供了硬件基础。

3.主设备与从设备系统中的所有外围器件都具有一个7位的"从器件专用地址码",其中高4位为器件类型,由生产厂家制定,低3位为器件引脚定义地址,由使用者定义。

主控器件通过地址码建立多机通信的机制,因此I2C总线省去了外围器件的片选线,这样无论总线上挂接多少个器件,其系统仍然为简约的二线结构。

终端挂载在总线上,有主端和从端之分,主端必须是带有CPU的逻辑模块,在同一总线上同一时刻使能有一个主端,可以有多个从端,从端的数量受地址空间和总线的最大电容 400pF的限制。

I2C总线详细介绍I2C是一种串行总线的外设接口,它采用同步方式串行接收或发送信息,两个设备在同一个时钟下工作。

I2C总线只用两根线:串行数据SDA(Serial Data)、串行时钟SCL(Serial Clock)。

由于I2C只有一根数据线,因此其发送信息和接收信息不能同时进行。

信息的发送和接收只能分时进行。

I2C串行总线工作时传输速率最高可达400K bit/s。

I2C总线上的所有器件的SDA线并接在一起,所有器件的SCL线并接在一起,且SDA线和SCL线必须通过上拉电阻连接到正电源。

I2C总线的数据传输协议要比SPI总线复杂一些,因为I2C总线器件没有片选控制线,所以I2C总线数据传输的开始必须由主器件产生通信的开始条件(SCL高电平时,SDA产生负跳变);通信结束时,由主器件产生通信的结束条件(SCL高电平时,SDA产生正跳变)。

SDA线上的数据在SCL高电平期间必须保持稳定,否则会被误认为开始条件或结束条件,只有在SCL低电平期间才能改变SDA线上的数据。

I2C总线的数据传输波形图如下图所示。

I2C应用实例AT24C系列为美国ATMEL公司推出的串行COMS型E2PROM,具有功耗小,宽电压范围等优点。

下图为AT24C系列E2PROM的引脚图。

图中A0、A1、A2为器件地址引脚,Vss为地,Vcc 为正电源,WP为写保护,SCL为串行时钟线,SDA为串行数据线。

AT24C系列E2PROM采用I2C总线,I2C总线上可挂接多个接口器件,在I2C总线上的每个器件应有唯一的器件地址,按I2C总线规则,器件地址为7位二进制数,它与一位数据方向位构成一个器件寻址字节。

器件寻址字节的最低位(D0)为方向位(读/写),最高4位(D7~D4)为器件型号地址(不同的I2C 总线接口器件的型号地址由厂家给定,AT24C系列E2PROM的型号地址都为1010);其余3位(D3~D1)与器件引脚地址A2A1A0相对应。

I2C总线协议介绍(易懂)目录CONTENTS•I2C总线协议产生背景•I2C总线协议内容介绍•I2C总线协议总结一、I2C总线协议产生背景1电视机内IC 之间相互连接,IC 芯片体积增大功耗增大 成本增加 IC 芯片应用不便飞利浦公司为了硬件电路最简化,效益最大化,给芯片设计制造者和芯片应用者带来极大益处。

2 I2C 总线Logo3飞利浦公司将这种集成电路互连通信电路命名为Inter-Integrated Circuit,简称为Inter-IC,或I2C(数字“2”为上标)。

因为I2C中的两根导线(SDA和SCL)构成了两根Bus,实现了Bus的功能;由于I2C电路能实现Bus的功能,故把I2C 电路称为 I2C-Bus,中文叫I2C总线(I2C总线是一个两线总线)。

4在正式的书面场合,全称写作Inter-Integrated Circuit,简写Inter-IC(IIC)或者I2C(数字“2”书写为上标,,英文读作“I squared C”,中文读作“I平方C”)5I2C总线术语及定义,如表(1)所示:表(1) I2C总线术语及定义6最初,I2C总线的运行速度被限制在100 Kbit /s。

随着技术的发展,对该规范进行了多次补充与更新,现在有五种运行速度模式,如表(2)所示:表(2)I2C总线传输速度模式二、I2C总线协议内容1I2C Bus 只要求两条双向线路:串行数据线(serial data SDA)与串行时钟线SCL(serialclock SCL),两条线都是双向传输的。

每个连接到总线的器件都有唯一的地址,主控制器发出的控制信息分为地址码和控制量两部分,地址码用来选择需要控制的I2C设备,控制量包含类别(写与读)2I2C总线是一种多控制器总线,总线上可以连接多个控制器和多个从机,这些控制器都可以发起对总线的控制,通过仲裁机制,同一个时刻,只能有一个控制器获得控制权,其他控制器轮流获取总线的控制权。

一文了解I2C----总线概述I2C(Inter-Integrated Circuit)总线是一种由PHILIPS公司开发的两线式串行总线,用于连接微控制器及其外围设备。

I2C总线产生于在80年代,最初为音频和视频设备开发,如今主要在服务器管理中使用,其中包括单个组件状态的通信。

I2C版本概况:版本1.0-1992l 删除了用软件编程从机地址的内容, 因为实现这个功能相当复杂,而且不被使用.l 删除了”低速模式”,实际上这个模式是整个I2C总线规范的子集,不需要明确的详细说明.l 增加了快速模式,它将位速率增加4倍到达400kbit/s,快速模式器件都向下兼容,即她们可以在0~100kbit/s的I2C总线系统中使用.l 增加了10位寻址,允许1024个额外的从机地址. l 快速模式器件的斜率控制和输入滤波改善了EMC性能.版本2.0-1998l 增加了高速模式(Hs模式),它将位速率增加到3.4Mbit/s,Hs模式的器件可以和I2C总线系统中快速和标准模式器件混合使用,位速率从0~3.4Mbit/s.l 电源电压是2V或更低的器件的低输出电平和滞后调整到符合噪声容限的要求,而且保持和电源电压更高的器件兼容.l 快速模式输出级的0.6V6mA要求被删除. l 新器件的固定输入电平被总线电压相关的电平代替. l 增加了双向电平转换器的应用信息.版本2.1-2000l在Hs模式的重复起始条件后,可以延长始终信号SCLH.l Hs模式中的一些时序参数变得更随意.I2C总线支持任何IC生产过程(NMOS,CMOS,双极性).两线—串行数据(SDA)和串行时钟(SCL)线在连接到总线的器件间传递信息.每个器件都有唯一的地址识别(无论是微控制器,LCD驱动器,存储器或键盘接口),而且都可以作为一个发送机或接收机(由器件的功能决定).I2C总线是一个多主机的总线,可以连接多个能控制总线的器件到总线.。

I2C总线简介1.概述:I²C是Inter-Integrated Circuit的缩写,发音为"eye-squared cee" or"eye-two-cee", 它是一种两线接口。

I²C 只是用两条双向的线,一条 Serial Data Line (SDA) ,另一条Serial Clock (SCL)。

SCL:上升沿将数据输入到每个EEPROM器件中;下降沿驱动EEPROM器件输出数据。

(边沿触发)SDA:双向数据线,为OD门,与其它任意数量的OD与OC门成"线与"关系。

2.输出级每一个I2C总线器件内部的SDA、SCL引脚电路结构都是一样的,引脚的输出驱动与输入缓冲连在一起。

其中输出为漏极开路的场效应管,输入缓冲为一只高输入阻抗的同相器,这种电路具有两个特点:1)由于SDA、SCL为漏极开路结构(OD),因此它们必须接有上拉电阻,阻值的大小常为1k8, 4k7 and 10k ,但1k8 时性能最好;当总线空闲时,两根线均为高电平。

连到总线上的任一器件输出的低电平,都将使总线的信号变低,即各器件的SDA及SCL都是线"与"关系。

2)引脚在输出信号的同时还将引脚上的电平进行检测,检测是否与刚才输出一致,为"时钟同步"和"总线仲裁"提供了硬件基础。

3.主设备与从设备系统中的所有外围器件都具有一个7位的"从器件专用地址码",其中高4位为器件类型,由生产厂家制定,低3位为器件引脚定义地址,由使用者定义。

主控器件通过地址码建立多机通信的机制,因此I2C总线省去了外围器件的片选线,这样无论总线上挂接多少个器件,其系统仍然为简约的二线结构。

终端挂载在总线上,有主端和从端之分,主端必须是带有CPU的逻辑模块,在同一总线上同一时刻使能有一个主端,可以有多个从端,从端的数量受地址空间和总线的最大电容 400pF的限制。

••主端主要用来驱动SCL line;•从设备对主设备产生响应;二者都可以传输数据,但是从设备不能发起传输,且传输是受到主设备控制的。

4.速率:普通模式:100kHz;快速模式:400kHz;高速模式:3.4MHz;没有任何必要使用高速SCL,将SCL保持在100k或以下,然后忘了它吧。

一、协议1.空闲状态I2C总线总线的SDA和SCL两条信号线同时处于高电平时,规定为总线的空闲状态。

此时各个器件的输出级场效应管均处在截止状态,即释放总线,由两条信号线各自的上拉电阻把电平拉高。

2.起始位与停止位的定义:•起始信号:当SCL为高期间,SDA由高到低的跳变;启动信号是一种电平跳变时序信号,而不是一个电平信号。

•停止信号:当SCL为高期间,SDA由低到高的跳变;停止信号也是一种电平跳变时序信号,而不是一个电平信号。

3.ACK发送器每发送一个字节,就在时钟脉冲9期间释放数据线,由接收器反馈一个应答信号。

应答信号为低电平时,规定为有效应答位(ACK简称应答位),表示接收器已经成功地接收了该字节;应答信号为高电平时,规定为非应答位(NACK),一般表示接收器接收该字节没有成功。

对于反馈有效应答位ACK的要求是,接收器在第9个时钟脉冲之前的低电平期间将SDA线拉低,并且确保在该时钟的高电平期间为稳定的低电平。

如果接收器是主控器,则在它收到最后一个字节后,发送一个NACK信号,以通知被控发送器结束数据发送,并释放SDA线,以便主控接收器发送一个停止信号P。

如下图逻辑分析仪的采样结果:释放总线后,如果没有应答信号,sda应该一直持续为高电平,但是如图中蓝色虚线部分所示,它被拉低为低电平,证明收到了应答信号。

这里面给我们的两个信息是:1)接收器在SCL的上升沿到来之前的低电平期间拉低SDA;2)应答信号一直保持到SCL的下降沿结束;正如前文红色标识所指出的那样。

4.数据的有效性:I2C总线进行数据传送时,时钟信号为高电平期间,数据线上的数据必须保持稳定,只有在时钟线上的信号为低电平期间,数据线上的高电平或低电平状态才允许变化。

我的理解:虽然只要求在高电平期间保持稳定,但是要有一个提前量,也就是数据在SCL 的上升沿到来之前就需准备好,因为在前面I2C总线之(一)---概述一文中已经指出,数据是在SCL的上升沿打入到器件(EEPROM)中的。

5.数据的传送:在I2C总线上传送的每一位数据都有一个时钟脉冲相对应(或同步控制),即在SCL串行时钟的配合下,在SDA上逐位地串行传送每一位数据。

数据位的传输是边沿触发。

二、工作过程总线上的所有通信都是由主控器引发的。

在一次通信中,主控器与被控器总是在扮演着两种不同的角色。

1.主设备向从设备发送数据主设备发送起始位,这会通知总线上的所有设备传输开始了,接下来主机发送设备地址,与这一地址匹配的slave将继续这一传输过程,而其它slave将会忽略接下来的传输并等待下一次传输的开始。

主设备寻址到从设备后,发送它所要读取或写入的从设备的内部寄存器地址;之后,发送数据。

数据发送完毕后,发送停止位:写入过程如下:发送起始位•发送从设备的地址和读/写选择位;释放总线,等到EEPROM拉低总线进行应答;如果EEPROM接收成功,则进行应答;若没有握手成功或者发送的数据错误时EEPROM不产生应答,此时要求重发或者终止。

•发送想要写入的内部寄存器地址;EEPROM对其发出应答;•发送数据•发送停止位.•EEPROM收到停止信号后,进入到一个内部的写入周期,大概需要10ms,此间任何操作都不会被EEPROM响应;(因此以这种方式的两次写入之间要插入一个延时,否则会导致失败,博主曾在这里小坑了一下)详细:需要说明的是:①主控器通过发送地址码与对应的被控器建立了通信关系,而挂接在总线上的其它被控器虽然同时也收到了地址码,但因为与其自身的地址不相符合,因此提前退出与主控器的通信;2.主控器读取数据的过程:读的过程比较复杂,在从slave读出数据前,你必须先要告诉它哪个内部寄存器是你想要读取的,因此必须先对其进行写入(dummy write):•发送起始位;•发送slave地址+write bit set;•发送内部寄存器地址;•重新发送起始位,即restart;•重新发送slave地址+read bit set;•读取数据主机接收器在接收到最后一个字节后,也不会发出ACK信号。

于是,从机发送器释放SDA线,以允许主机发出P信号结束传输。

•发送停止位详细:为了加深对I2C总线的理解,用C语言模拟IIC总线,边看源代码边读波形:如下图所示的写操作的时序图:读时序的理解同理。

对于时序不理解的朋友请参考“I2C总线之(二)---时序”完整的程序如下:#include<reg51.h>#define uchar unsigned char#define uint unsigned int#define write_ADD 0xa0#define read_ADD 0xa1uchar a;sbit SDA=P2^0;sbit SCL=P2^1;void SomeNop(); //短延时void init(); //初始化void check_ACK(void);void I2CStart(void);void I2cStop(void);void write_byte(uchar dat);//写字节void delay(uint z);uchar read_byte(); //读字节void write(uchar addr,uchar dat); //指定地址写uchar read(uchar addr); //指定地址读bit flag; //应答标志位void main(){init();write_add(5,0xaa); //向地址5写入0xaadelay(10); //延时,否则被坑呀P1=read_add(5); //读取地址5的值while(1);}//*************************************************************************** void delay()//简单延时函数{ ;; }//***************************************************************************void start() //开始信号 SCL在高电平期间,SDA一个下降沿则表示启动信号{sda=1; //释放SDA总线delay();scl=1;delay();sda=0;delay();}//***************************************************************************void stop() //停止 SCL在高电平期间,SDA一个上升沿则表示停止信号{sda=0;delay();scl=1;delay();sda=1;delay();}//***************************************************************************void respons() //应答 SCL在高电平期间,SDA被从设备拉为低电平表示应答{uchar i;scl=1;delay();//至多等待250个CPU时钟周期while((sda==1)&&(i<250))i++;scl=0;delay();}//***************************************************************************void init()//总线初始化将总线都拉高一释放总线发送启动信号前,要先初始化总线。

即总有检测到总线空闲才开始发送启动信号{sda=1;delay();scl=1;delay();}//***************************************************************************void write_byte(uchar date) //写一个字节{uchar i,temp;temp=date;for(i=0;i<8;i++){temp=temp<<1;scl=0;//拉低SCL,因为只有在时钟信号为低电平期间按数据线上的高低电平状态才允许变化;并在此时和上一个循环的scl=1一起形成一个上升沿delay();sda=CY;delay();scl=1;//拉高SCL,此时SDA上的数据稳定delay();}scl=0;//拉低SCL,为下次数据传输做好准备delay();sda=1;//释放SDA总线,接下来由从设备控制,比如从设备接收完数据后,在SCL为高时,拉低SDA作为应答信号delay();}//***************************************************************************uchar read_byte()//读一个字节{uchar i,k;scl=0;delay();sda=1;delay();for(i=0;i<8;i++){scl=1;//上升沿时,IIC设备将数据放在sda线上,并在高电平期间数据已经稳定,可以接收啦delay();k=(k<<1)|sda;scl=0;//拉低SCL,使发送端可以把数据放在SDA上delay();}return k;}//***************************************************************************void write_add(uchar address,uchar date)//任意地址写一个字节{start();//启动write_byte(0xa0);//发送从设备地址respons();//等待从设备的响应write_byte(address);//发出芯片内地址respons();//等待从设备的响应write_byte(date);//发送数据respons();//等待从设备的响应stop();//停止}//***************************************************************************uchar read_add(uchar address)//读取一个字节{uchar date;start();//启动write_byte(0xa0);//发送发送从设备地址写操作 respons();//等待从设备的响应write_byte(address);//发送芯片内地址respons();//等待从设备的响应start();//启动write_byte(0xa1);//发送发送从设备地址读操作 respons();//等待从设备的响应date=read_byte();//获取数据stop();//停止return date;//返回数据}。