xilinx ISE使用错误和警告

- 格式:docx

- 大小:21.05 KB

- 文档页数:5

ISE开发环境使用指南简介ISE(Integrated Software Environment)是Xilinx公司开发的一套FPGA设计软件工具。

本文档将为您介绍如何使用ISE开发环境进行FPGA开发,包括环境的安装、基本操作和常见问题解决方法。

环境安装1.在Xilinx官网上下载最新版本的ISE软件。

2.双击安装文件,按照向导指示完成安装过程。

3.完成安装后,打开ISE软件,进行必要的设置和配置。

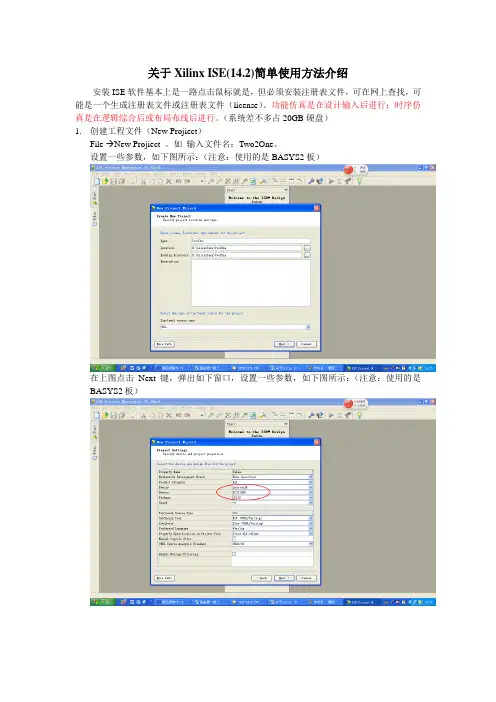

基本操作创建工程1.打开ISE软件,选择“File” -> “New Project”。

2.在弹出的对话框中输入工程名称和路径,选择FPGA型号等相关参数,点击“Next”。

3.添加源文件和约束文件,点击“Next”。

4.点击“Finish”完成工程创建。

编译工程1.在ISE软件中选择“Project” -> “Run Implementation”进行工程编译。

2.检查编译过程中是否有错误,根据提示进行修正。

下载到FPGA1.将FPGA与电脑连接,选择“Tools” -> “iMPACT”打开下载工具。

2.配置下载参数,选择对应的FPGA型号和文件路径。

3.点击“Program”开始下载程序到FPGA。

常见问题解决方法编译错误•检查代码中是否有语法错误或逻辑问题。

•检查约束文件是否设置正确。

下载失败•检查FPGA与电脑的连接是否正常。

•检查下载工具配置是否正确。

总结通过本文档的介绍,您应该对如何使用ISE开发环境进行FPGA开发有了一定了解。

希望您在实际操作中能够顺利完成项目的开发和调试。

如果遇到任何问题,可以参考本文档中提供的常见问题解决方法或参考Xilinx官方文档进行进一步学习和搜索。

ISE 10.1Steps1 new project (1)2 new source (3)3 run behavior simulation (5)4 ChipScope (7)5 Constraints (12)6 synthesize your design (13)7 implement your design (13)8 Generate Programming File (13)9Analyze Design Using Chipscope (13)1 new project1. 双击桌面Xilinx ISE10.1 快捷方式打开ISE 工程管理器(Project Navigator)。

2. 打开 Project Navigator 后,选择File → New Project ,弹出新建工程对话框,填写工程名字,工程存放发热位置。

注意,不要填写含有中文的名字,以免发生错误。

3.点击 Next 按钮,弹出器件特性对话框。

Device Family选择“Virtex2P”,Device选“XC2VP30 ,Package选择ff896,Speed选 -7”,其他选择如下图所示。

其中这些选择由按FPGA开发板的型号来决定的。

然后点击NEXT,继续单击Next 按钮,然后单击Finish按钮完成对工程的建立和基本设置。

2 new source1在工程的Source for下在的空白处单击右键选择New Source菜单2然后在弹出的对话框中选择Verilog Module,并且在右边的File name中输入你的模块名称,然后单击Next按钮。

2.这是一个设置输入输出端口的对话框,可以设置,也可以不设置。

一般选择不设置,直接点击NEXT,最后单击Finish按钮完成成对Verilog Module模块资源的添加。

3.双击Source for下面的.v文件(本实验双击counter.v)进入源代码编辑框中,并在里面编写Verilog源程序,然后点击保存按钮。

FPGA常见的错误Quartus II常见错误1.Found clock-sensitive change during active clock edge at time <time> on register "<name>"原因:vector source file中时钟敏感信号(如:数据,允许端,清零,同步加载等)在时钟的边缘同时变化。

而时钟敏感信号是不能在时钟边沿变化的。

其后果为导致结果不正确。

措施:编辑vector source file2.Verilog HDL assignment warning at <location>: truncated with size <number> to match size of target (<number>原因:在HDL设计中对目标的位数进行了设定,如:reg[4:0] a;而默认为32位,将位数裁定到合适的大小措施:如果结果正确,无须加以修正,如果不想看到这个警告,可以改变设定的位数3.All reachable assignments to data_out(10) assign '0', register removed by optimization原因:经过综合器优化后,输出端口已经不起作用了4.Following 9 pins have nothing, GND, or VCC driving datain port -- changes to this connectivity may change fitting results原因:第9脚,空或接地或接上了电源措施:有时候定义了输出端口,但输出端直接赋…0‟,便会被接地,赋…1‟接电源。

如果你的设计中这些端口就是这样用的,那便可以不理会这些warning5.Found pins ing as undefined clocks and/or memory enables原因:是你作为时钟的PIN没有约束信息。

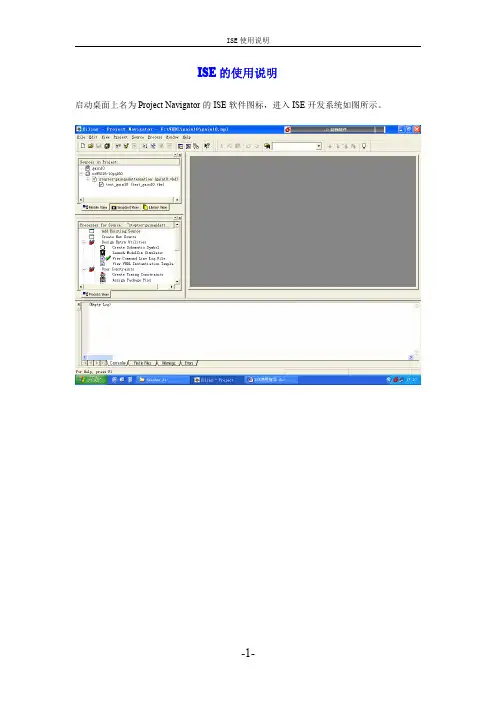

ISE软件使用说明ISE(Integrated Software Environment)软件是由赛灵思公司(Xilinx Inc.)开发的一款用于设计和开发数字电路的软件工具。

该软件提供了一个集成的环境,用于设计、模拟和验证数字电路。

本文将介绍ISE软件的安装和基本使用方法,以帮助用户快速上手。

一、安装ISE软件2.根据安装程序的提示,选择安装的目标文件夹和所需的组件。

3.等待安装程序完成安装。

二、打开ISE软件打开ISE软件后,会出现一个欢迎界面,用户可以选择新建项目、打开已有项目或者直接进入ISE工具链。

三、创建新项目1. 点击“New Project”按钮,进入新项目设置页面。

2.输入项目的名称和路径,选择项目类型和芯片系列。

3. 点击“Next”按钮,进入项目配置页面。

4.在此页面中,用户可以添加需要使用的源文件、约束文件和IP核等。

5. 点击“Next”按钮,进入总结页面。

6. 点击“Finish”按钮,完成项目创建。

四、设计源文件在ISE软件中,用户可以使用HDL(硬件描述语言)进行设计源文件的编写。

ISE软件支持的HDL语言有VHDL和Verilog。

1. 在项目视图中,右键点击“Source”文件夹,选择“New Source”。

2.在弹出的对话框中,选择源文件类型和语言。

3. 输入文件的名称和路径,点击“Finish”按钮。

五、添加约束文件约束文件用于定义电路的时序、引脚映射等信息,以确保电路的正常工作。

1. 在项目视图中,右键点击“Constraints”文件夹,选择“New Source”。

2.在弹出的对话框中,选择约束文件类型。

3. 输入文件的名称和路径,点击“Finish”按钮。

六、综合与实现在进行综合和实现之前,需要根据设计需求进行一些设置和配置。

1. 在项目视图中,右键点击项目名称,选择“Properties”。

2.在弹出的对话框中,选择“SYNTHESIS”或“IMPLEMENTATION”选项卡。

vivado中critical warning -回复关于Vivado 中的Critical Warning,究竟是什么?Vivado 是Xilinx 公司提供的一种EDA (Electronic Design Automation)工具套件,用于FPGA (Field-Programmable Gate Array)设计和开发。

在Vivado 的设计过程中,开发人员可能会遇到各种警告信息,其中之一就是Critical Warning(致命警告)。

那么,什么是一个Critical Warning,为什么它被认为是“致命”的?我们将在下文中一步一步回答这些问题,并了解如何处理这些警告信息。

首先,我们需要了解Critical Warning 的定义。

在Vivado 中,警告信息被分为三个级别:INFO(信息)、WARNING(警告)和CRITICAL WARNING(致命警告)。

Critical Warning 是指在设计中发现的一个严重问题,可能导致设计无法工作或产生不可预测的结果。

与之相对,普通的Warning 通常是指设计中的一些潜在问题,不太可能导致设计完全失败,但仍然需要引起注意。

为什么Critical Warning 被认为是“致命”的?这是因为一个Critical Warning 可能会导致以下一种或多种情况:1. 功能失败:Critical Warning 可能会导致设计无法按预期的方式工作。

这可能会导致产品功能的失败,从而无法达到原定的设计要求。

2. 不可预测的结果:Critical Warning 可能会导致设计产生不可预测的结果。

这意味着设计可能会在不同的运行时刻产生不一致的输出结果,这对于任何产品来说都是不可接受的。

3. 性能降低:Critical Warning 可能会导致设计性能的下降。

这可能会导致产品无法实现所需的响应时间或数据处理速度,从而无法满足市场需求。

接下来,我们将重点关注如何逐步处理Critical Warning。

ISE的使用说明ISE(Integrated Software Environment)是一种集成软件环境,用于设计和验证硬件开发项目。

它由Xilinx公司开发,旨在为FPGA(Field-Programmable Gate Array)和SoC(System-on-a-Chip)设计提供完整的解决方案。

ISE具有多种功能和工具,可以帮助工程师在整个开发过程中完成各种任务。

ISE的安装:ISE的主要功能:ISE为硬件设计和验证提供了全面的解决方案。

以下是ISE的主要功能:2.综合和优化:ISE包含了综合和优化工具,将HDL代码转换为布尔函数表示。

综合工具会分析代码并生成等效的硬件电路电路。

优化工具会尝试将电路改进为更有效的形式,以提高性能和减少资源消耗。

3.约束和分析:在设计过程中,您通常需要对硬件进行约束,以满足特定的要求。

ISE提供了工具来定义时序约束、电气约束和物理约束,并分析设计是否满足这些约束。

4.实现和布局:一旦设计和优化完成,ISE将使用实现和布局工具将电路映射到目标FPGA或SoC中。

这些工具将选择适当的逻辑资源,并将其布局在特定的芯片区域,以最大程度地提高性能和效率。

5.仿真和调试:在设计过程中,您需要对硬件进行仿真和调试,以验证其正确性和性能。

ISE提供了仿真工具,可以对设计进行功能仿真、时序仿真和混合信号仿真。

它还提供了调试功能,可帮助您定位和解决问题。

以下是使用ISE的一般步骤:1.创建新工程:在ISE中,您需要先创建一个新的工程,用于存储和组织设计文件。

可以在ISE中创建一个新的工程,并选择适当的目标设备。

2. 添加设计文件:一旦工程创建完成,您可以添加设计文件到工程中。

通过右键单击工程文件夹,并选择“Add Source”来添加设计文件。

选择适当的文件类型,并在文件对话框中选择要添加的文件。

3. 设置约束:在设计过程中,您需要为硬件设计设置约束,以满足特定的要求。

通过右键单击工程文件夹,并选择“Add Constraints”来添加约束文件。

Xilinx是全球领先的可编程逻辑完整解决方案的供应商,研发、制造并销售应用范围广泛的高级集成电路、软件设计工具以及定义系统级功能的IP(Intellectual Property)核,长期以来一直推动着FPGA技术的发展。

Xilinx的开发工具也在不断地升级,由早期的Foundation 系列逐步发展到目前的ISE 9.1i系列,集成了FPGA开发需要的所有功能,其主要特点有:Foundation Series ISE具有界面友好、操作简单的特点,再加上Xilinx的FPGA芯片占有很大的市场,使其成为非常通用的FPGA工具软件。

ISE 作为高效的EDA设计工具集合,与第E9.1 软件安装的基本硬件要求如下:CPU 在 P III 以上,内存大于 256M ,硬盘大于 4G 的硬件环境安装。

为了更好地使用软件,至少需要 512M 内存,CPU 的主频在 2GHz 以上。

本 书使用的集成开发环境是 ISE 9.1,仿真工具是 ModelSim 6.2b ,综合工具为 Synplify Pro 8.8。

其中 ISE 、ModelSim 软件和 Synplify 软件不同版本之间的差异不是很大,所以操作和设计购买了正版软件后,最常用的方法就是通过网站注册获取安装所需的注册码。

首先在Xilinx 帐号,输入CD 盒上的产品序列号(序号的格式为:3 个字符+9 个数字),会自动生成163.下一个对话框是Xilinx 软件的授权声明对话框,选中“I accept the terms of this software4.接下来的几个对话框分别是选择安装组件选择,如图 4-4 所示,用户需要选择自己使用5.随后进入设置环境变量页面,保持默认即可。

如果环境变量设置错误,则安装后不能正 常启动 ISE 。

选择默认选项,安装完成后,在“我的电脑”上单击右键,选择属性 环境变量中,图比较常用,显示了源文件的层次关系。

ise管脚约束设置参数详解以ISE管脚约束设置参数详解概述ISE(Integrated Software Environment)是Xilinx公司开发的一款用于设计和实现FPGA(Field-Programmable Gate Array)的软件工具。

在使用ISE进行FPGA设计时,管脚约束是非常重要的一部分,它用于指定FPGA芯片上的输入输出引脚的功能和连接关系,以确保设计的正确性和可靠性。

本文将详细介绍ISE管脚约束设置参数的相关知识。

1. 管脚约束的作用管脚约束是将设计的逻辑电路与FPGA芯片上的引脚进行连接的关键步骤。

通过正确设置管脚约束参数,可以确保逻辑电路与硬件之间的正确通信,同时还可以优化电路性能和资源利用率。

在ISE中,管脚约束的设置包括输入输出管脚的引脚类型、电平标准、时钟频率等多个方面。

2. 管脚约束的设置方法在ISE中,可以使用UCF(User Constraints File)文件或XDC (Xilinx Design Constraints)文件来进行管脚约束的设置。

UCF 文件是ISE早期版本使用的约束文件格式,而XDC文件是ISE 14.1及以后版本引入的新约束文件格式。

下面将分别介绍这两种约束文件的设置方法。

2.1 UCF文件的设置方法UCF文件是一种文本文件,可以使用任何文本编辑器进行编辑。

UCF文件中的每一行都对应着一个管脚的约束设置。

以下是UCF文件的一些常用约束参数及其设置方法:- NET:用于定义逻辑电路中的信号名称;- LOC:用于定义信号连接到FPGA芯片上的具体引脚位置;- IOSTANDARD:用于定义引脚的电平标准;- SLEW:用于定义引脚的输出斜率控制;- DRIVE:用于定义引脚的驱动能力;- PULLUP:用于定义引脚的上拉电阻;- PULLDOWN:用于定义引脚的下拉电阻。

通过在UCF文件中逐行设置这些约束参数,可以完成对管脚的约束设置。

十分钟学会ISE声明本系列文档、软件的版权为Digital Power Studio工作组所有。

Digital Power Studio工作组保留所有权利。

欢迎转载,但请保留这段版权声明;请勿用于商业用途。

Copyright (c) 2004, Digital Power Studio. All rights reserved.HistoryRevision Date Issuer NotesRelease1.0 Mar 3, 2005 Badfish First目录概述 (4)实验目的 (4)软件准备 (5)流程介绍 (5)新建项目: (5)编写和导入代码文件 (8)调用Modsim进行仿真 (11)约束文件 (13)综合与实现 (15)下载 (16)十分钟学会ISE 概述这个文档主要帮助大家熟悉利用ISE进行Xilinx公司FPGA代码开发的基本流程。

主要是帮助初学者了解和初步掌握ISE的使用,不需要FPGA的开发基础,所以对每个步骤并不进行深入的讨论。

本文介绍的内容从新建project一直到下载到硬件观察现象为止,涵盖整个开发过程。

考虑到我们的开发一般以Verilog HDL或VHDL为主,在本文中未介绍原理图输入工具和IP核使用工具等。

这同时是出于为了使文章脉络更清晰,让大家更快地学会ISE的考虑。

关于这些专用工具,可以参看HELP或者其他文档。

为了有个更直观的理解,我们需要一个实验平台,在本文中,采用的是Digital Power Studio工作组FPGA SPARK1.1综合开发平台的Xilinx标准型开发系统。

如图1所示(图中为Altera子板,只需改成Xilinx的即可)。

在该开发系统中,所采用的芯片是SPARTAN II系列的XC2S200。

可以参看/solution/fpgaspark.htm中对该系统的介绍。

图1 FPGA SPARK1.1 外观图实验目的在如上系统中右边有一个128×64带背光的点阵型液晶。

Xilinx ISE中的DCM的使用(转)2008-05-05 11:56目前,大型设计一般推荐使用同步时序电路。

同步时序电路基于时钟触发沿设计,对时钟的周期、占空比、延时和抖动提出了更高的要求。

为了满足同步时序设计的要求,一般在FPGA设计中采用全局时钟资源驱动设计的主时钟,以达到最低的时钟抖动和延迟。

FPGA全局时钟资源一般使用全铜层工艺实现,并设计了专用时钟缓冲与驱动结构,从而使全局时钟到达芯片内部的所有可配置单元(CLB)、I/O单元(IOB)和选择性块RAM(Block Select RAM)的时延和抖动都为最小。

为了适应复杂设计的需要,Xilinx的FPGA中集成的专用时钟资源与数字延迟锁相环(DLL)的数目不断增加,最新的Virtex II器件最多可以提供16个全局时钟输入端口和8个数字时钟管理模块(DCM)。

与全局时钟资源相关的原语常用的与全局时钟资源相关的Xilinx器件原语包括:IBUFG、IBUFGDS、BUFG、BUFGP、BUFGCE、BUFGMUX、BUFGDLL和DCM等,如图1所示。

1. IBUFG即输入全局缓冲,是与专用全局时钟输入管脚相连接的首级全局缓冲。

所有从全局时钟管脚输入的信号必须经过IBUF元,否则在布局布线时会报错。

IBUFG支持AGP、CTT、GTL、GTLP、HSTL、LVCMOS、LVDCI、LVDS、LVPECL、LVTTL、PCI、PCIX和SSTL等多种格式的IO标准。

G 单2. IBUFGDS是IBUFG的差分形式,当信号从一对差分全局时钟管脚输入时,必须使用IBUFGDS作为全局时钟输入缓冲。

IBUFG支持BLVDS、LDT、LVDSEXT、LVDS、LVPECL和ULVDS等多种格式的IO标准。

3. BUFG是全局缓冲,它的输入是IBUFG的输出,BUFG的输出到达FPGA内部的IOB、CLB、选择性块RAM的时钟延迟和抖动最小。

VHDL上机手册(基于Xilinx ISE)___________________________________________________1 ISE 软件的运行2 创建一个新工程3 创建一个VHDL源文件框架4 输入VHDL程序*5 仿真6 创建Testbench波形源文件7 设置输入仿真波形___________________________________________________VHDL上机手册(基于Xilinx ISE)1 创建一个新工程Step1. 单击“开始->程序->Xilinx ISE7.1->Project Navigator”,进入ISE 软件。

Step2. 选择File->New Project…,出现如图2所示的窗口。

这个窗口与以前版本的差别较大,以前的版本出现的窗口中可以直接选取器件类型、封装、门数、速度等级等信息。

而在ISE6.1 中需要单击“下一步”才能看到这些设置信息。

在本例中,我们先选择工程存放的路径,然后输入工程名称。

系统自动为每一个工程设定一个目录,目录名为工程名。

再选择顶层模块类型为HDL。

图2新工程项对话框(其他几种类型说明如下:Schematic为原理图输入类型,类似于我们制作PCB 原理图时的情况,可以从库中选取器件,也可以用HDL 语言来生成器件,在后续章节会介绍原理图为设计输入的情况;EDIF为网表输入类型,EDIF 是Electronic Data Interchange Format 的缩写,是一种描述设计网表的标准的工业文件格式,可以由第三方工具生成,在ISE 中可以将其作为一种标准的输入格式。

NGC 文件是一种包含了逻辑设计数据和约束的网表,所谓约束是指FPGA 设计中的一些特定的要求,例如,我们分配设计中的信号到具体的管脚时,需要一个文件来指定如何分配,这就是一种约束文件,由于NGC 网表包含了设计和约束,因此一个文件足够描述一个设计了。

Xilinx FPGA 中“Done did not go high”的解决办法讨论---------苏柏亚整理在使用ISE进行FPGA的bit文件下载时,经常会遇到下载失败的问题,提示:"DONE did not go high".在Xilinx官网上有对此问题的答复如下:下面提供以下解决方案(根据不同的情况,产生上述问题的原因实在太多,不一一解释了)1. 关闭工程后重新打开ISE,将下载电缆重新安装(或进行更换),必要时重启电脑;2. 若(1)方案失败,则右击“Processes”窗口中的"Generate Programming File",点击“Process Properties”左边的"Configuration Options" ,找到"Unused IOB Pins"选项,将其修改为“float”。

3. 若(2)方案也失效,则进入第三步,在iMpact界面中的Edit ——> Preferences ——> IMPACT-Configuration Preferences 中选中"Use HighZ intstead of Bypass"一项即可。

4. 若(3)方案也失效,则进入第四步,在生成Bit文件之前,右击“Processes”窗口中的"Generate Programming File",点击"Startup Options",找到"Match Cycle",将该项修改为最大值"6"。

以上资料均来自网络,非我跟人原创。

今稍作整理,以方便大家查询。

也有人提出说ISE7.1 没有这种BUG。

但我没试过。

xilinx ISE使用错误和警告

(2012-03-22 15:46:49)

转载▼

标签:

xilinx

(1)编dcm时钟控制测试程序时,设置好了ip,例化输出,综合时出现错误

ERROR:Xst:2035 - Port <clk> has illegal connections. This port is connected to an input buffer and other components.

查到的解决方法是禁掉自动I/O Buffer insertion 功能,具体的做法是右击synthesize,然后properties->Xilinx Specific Options,把add I/O buffer 的勾去掉,综合通过。

但是这样处理了之后在map时又引入了许多的warning,而且还会引发错误。

方法出处一会转帖出来。

(2)dac8812的控制时序测试时,综合没问题,但是map时出现错误

Pack:198 - NCD was not produced. All logic was removed from design. 其实这个错误的来源是下面的这几个warning导致

MapLib:701 - Signal clk connected to top level port clk has been removed.

MapLib:701 - Signal dad connected to top level port dad has been removed.

以下省略很多这样的warning,这个问题之前一直没注意,后来才知

道问题出在我在问题(1)中的处理,按照同样的流程把add I/O buffer 勾上,综合到route都没什么问题,可见warning也是不能忽略的呀。

(3)刚才不知道怎么了,行为仿真的时候出现下面的error

ERROR:HDLParsers:3482 - Could not resolve instantiated unit dacinter in Verilog module work/datest_top in any library

意思好像是找不到我top里例化的模块了,重新添加了一下,好用了。

(4)行为仿真发现没有波形,全是XX或者ZZZ,以前改一下clk 频率就好了,这回这招不好使了,后来尝试改了一下rst的时间点,向后一段时间,发现好用了,仿真用的是ise自带的simulation。

(5)综合错误:ERROR:Xst:528 - Multi-source in Unit <entity> on signal <sig>

大多数时候应该是同一个变量,在两个always模块中赋值了。

还查到一些其他情况,一并粘贴:

Solution 1

This error appears when XST determines that there is contention on a particular signal. If the processes assigning values to this signal are mutually exclusive (as in the case of 3-state buffers), this message can be ignored.

However, in most cases, XST is able to determine when multiple drivers are illegal, and will stop synthesis soon after this message.

Check this signal and modify your code to avoid the existing contention.

Solution 2

In some cases, XST ties unconnected output ports to ground. If the output port is part of a 3-state bus, which in turn connects to another 3-state bus, then connecting one bit of the bus to ground will cause a multiple-driver error. Verify that this is not occurring in your design by searching for the following warning:

"WARNING:Xst:1305 - Output <dataout<23>> is never assigned. Tied to value 0."

To work around this issue, remove the unused output port.

Solution 3

This has also been seen in the following condition:

When there is an association signal named to_qvm_d4.Q_num.

When using association signal(to_qvm_d4.Q_num), XST will rename it to "to_qvm_d4_Q_num" during synthesis. There is signal named

"to_qvm_d4_Q_num" in the same architecture. XST is confused with these two signals and errors.

To work around this issue, rename either of the two signals.

Solution 4

EDK Designs

For EDK Designs using bidirectional signals DIR=IO and

THREE_STATE=FALSE, the external port name must match the connecting signal name exactly. NOTE: IOB_STATE is deprecated in

future EDK versions.

(6)ERROR:Xst:902 - "dec_seg.v" line 38: Unexpected event in always block sensitivity list.

一个组合电路,综合出错,上网查说是敏感表中不能既有电平又有边沿,而且也不能同一个信号的上升沿和下降沿同时出现,去掉敏感表中的边沿,运行OK了。

(7)map的时候出现错误ERROR:Pack:679 - Unable to obey design constraints (LOC = ...) which require the combination of the following symbols into a single slice component:

检查ucf文件,发现有一个管脚被重复分配,改了一下,运行OK!(8)ERROR:NgdBuild:604 - 'GTP_DUAL_1' could not be resolved,这个错误在translate的时候报,是软件的bug,网上查说ise12.2多发,但是我用的9.1也出了这个,原因大概是ISE只复制了顶层的NGC 文件,即mycpu.ngc,而顶层mycpu还包含其它ngc文件,因此找不到,报错。

按照查到的解决办法,有两种。

解决办法1是:在mycpu module前面加上

(* box_type = "user_black_box" *)

如:

(* box_type = "user_black_box" *)

mycpu my_cpu_moudle (.fpga_0_clk_1_sys_clk_pin(sys_clk),

.fpga_0_rst_1_sys_rst_pin(sys_rst_n),

.fpga_0_RS232_RX_pin(uart_rxd),

.fpga_0_RS232_TX_pin(uart_txd),

.led_out_GPIO_IO_O_pin(led_out[0:3]));

办法2是在ISE 的processes栏下,选中Translate,右键process propreties.....

弹出Translate Properties对话框,

在-sd macro search path 中加上EDK工程的implementation子目录的路径就可以了

一开始采用了第一种解决方案,translate通过,但在map时出错。

改用第二种,问题是,我用了两个ip core,这个指定的路径只能是一个最直接的目录,所以只能完全解决其中一个core的错误,把两个core 的文件夹里的文件全拷到工程目录中,指定工程目录路径为implementation子目录路径,搞定。

可以忽略的warning

(1)ProjectMgmt - "F:/verilogworks/FPGATESTS/datest_top_map.ncd" line 0 duplicate design unit: 'Module|datest_top'。