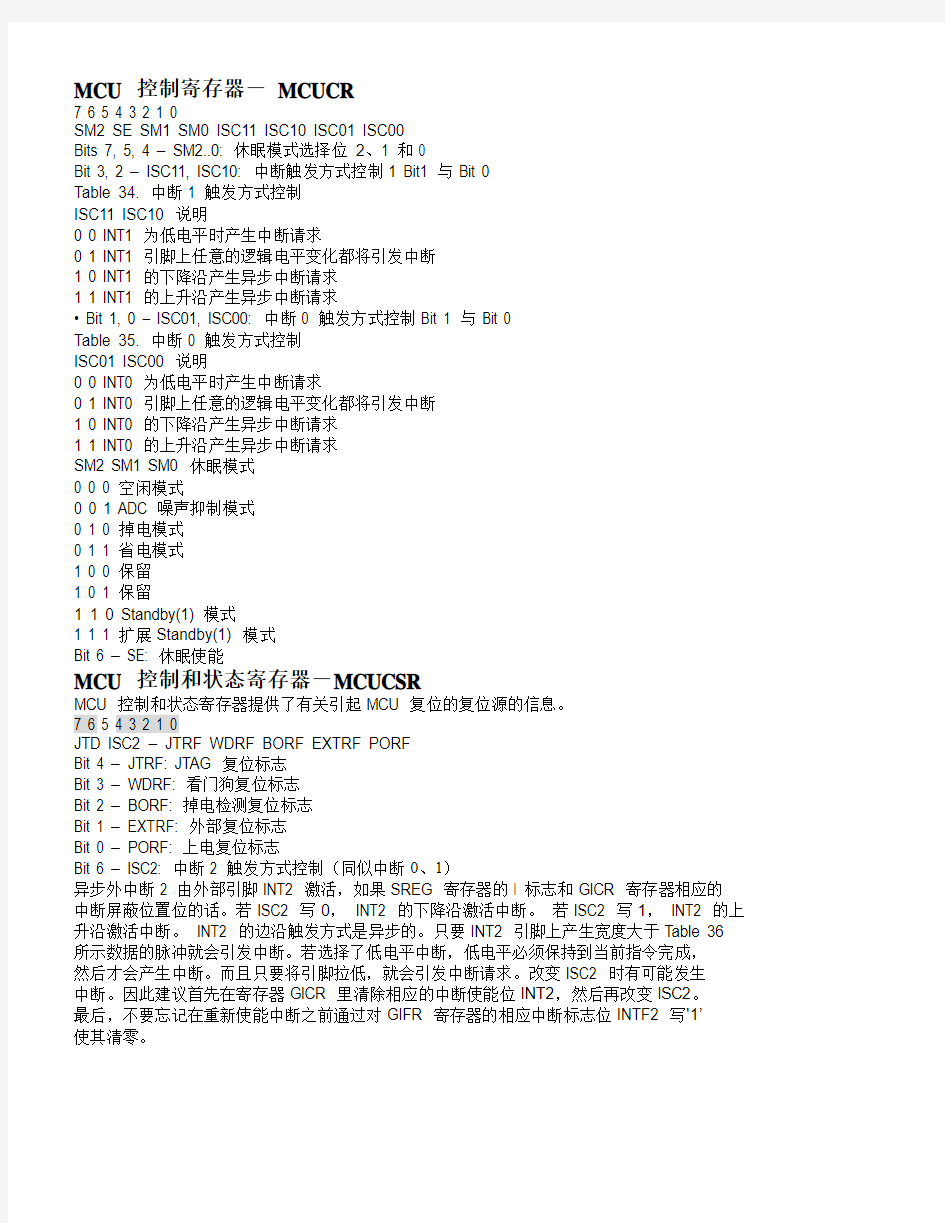

MCU 控制寄存器-MCUCR

7 6 5 4 3 2 1 0

SM2 SE SM1 SM0 ISC11 ISC10 ISC01 ISC00

Bits 7, 5, 4 – SM2..0: 休眠模式选择位2、1 和0

Bit 3, 2 – ISC11, ISC10: 中断触发方式控制1 Bit1 与Bit 0

Table 34. 中断1 触发方式控制

ISC11 ISC10 说明

0 0 INT1 为低电平时产生中断请求

0 1 INT1 引脚上任意的逻辑电平变化都将引发中断

1 0 INT1 的下降沿产生异步中断请求

1 1 INT1 的上升沿产生异步中断请求

? Bit 1, 0 – ISC01, ISC00: 中断0 触发方式控制Bit 1 与Bit 0

Table 35. 中断0 触发方式控制

ISC01 ISC00 说明

0 0 INT0 为低电平时产生中断请求

0 1 INT0 引脚上任意的逻辑电平变化都将引发中断

1 0 INT0 的下降沿产生异步中断请求

1 1 INT0 的上升沿产生异步中断请求

SM2 SM1 SM0 休眠模式

0 0 0 空闲模式

0 0 1 ADC 噪声抑制模式

0 1 0 掉电模式

0 1 1 省电模式

1 0 0 保留

1 0 1 保留

1 1 0 Standby(1) 模式

1 1 1 扩展Standby(1) 模式

Bit 6 – SE: 休眠使能

MCU 控制和状态寄存器-MCUCSR

MCU 控制和状态寄存器提供了有关引起MCU 复位的复位源的信息。

7 6 5 4 3 2 1 0

JTD ISC2 – JTRF WDRF BORF EXTRF PORF

Bit 4 – JTRF: JTAG 复位标志

Bit 3 – WDRF: 看门狗复位标志

Bit 2 – BORF: 掉电检测复位标志

Bit 1 – EXTRF: 外部复位标志

Bit 0 – PORF: 上电复位标志

Bit 6 – ISC2: 中断2 触发方式控制(同似中断0、1)

异步外中断2 由外部引脚INT2 激活,如果SREG 寄存器的I 标志和GICR 寄存器相应的

中断屏蔽位置位的话。若ISC2 写0,INT2 的下降沿激活中断。若ISC2 写1,INT2 的上升沿激活中断。INT2 的边沿触发方式是异步的。只要INT2 引脚上产生宽度大于Table 36 所示数据的脉冲就会引发中断。若选择了低电平中断,低电平必须保持到当前指令完成,

然后才会产生中断。而且只要将引脚拉低,就会引发中断请求。改变ISC2 时有可能发生

中断。因此建议首先在寄存器GICR 里清除相应的中断使能位INT2,然后再改变ISC2。

最后,不要忘记在重新使能中断之前通过对GIFR 寄存器的相应中断标志位INTF2 写'1’

使其清零。

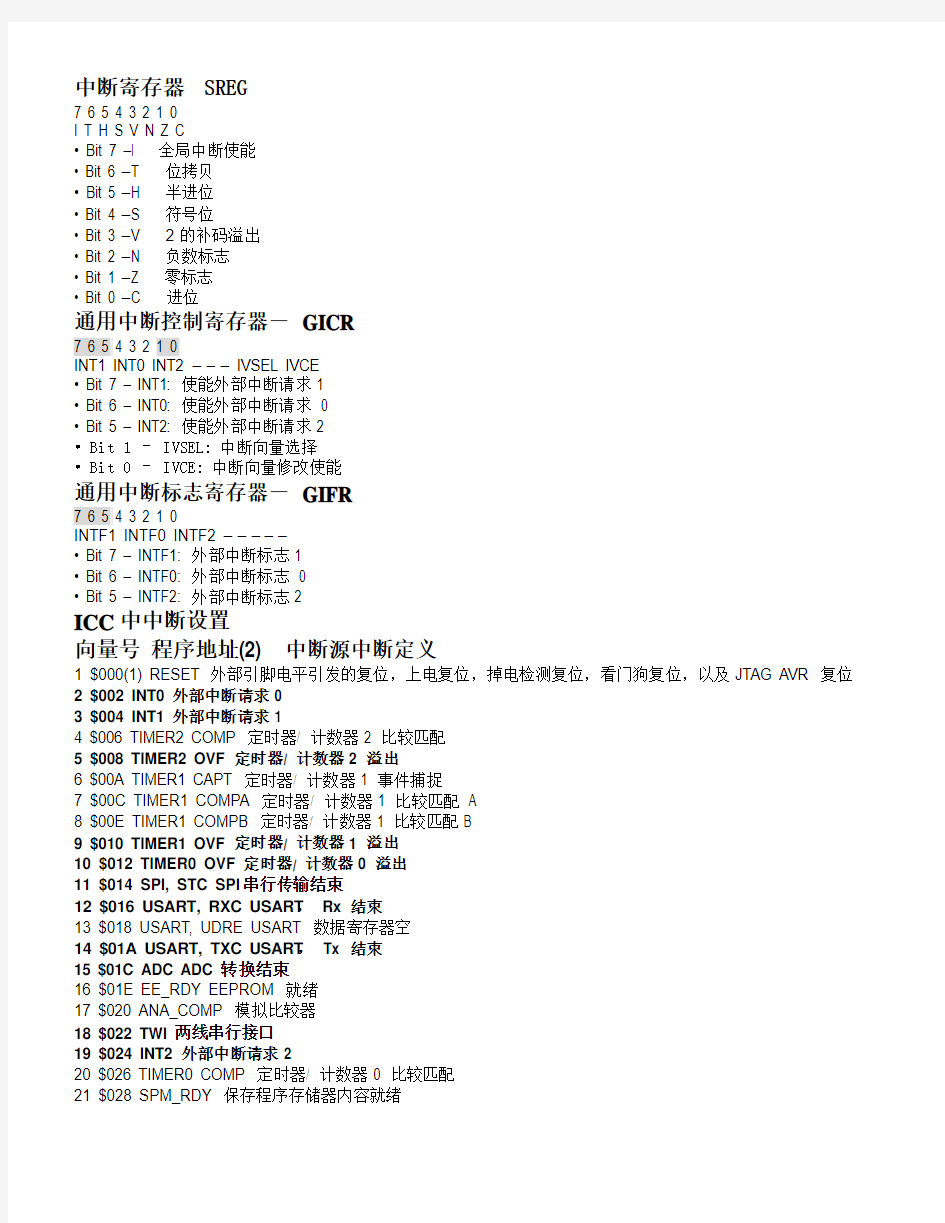

中断寄存器 SREG

7 6 5 4 3 2 1 0

I T H S V N Z C

? Bit 7 –I 全局中断使能

? Bit 6 –T 位拷贝

? B it 5 –H 半进位

? Bit 4 –S 符号位

? Bit 3 –V 2的补码溢出

? Bit 2 –N 负数标志

? Bit 1 –Z 零标志

? Bit 0 –C 进位

通用中断控制寄存器-GICR

7 6 5 4 3 2 1 0

INT1 INT0 INT2 ––– IVSEL IVCE

? Bit 7 – INT1: 使能外部中断请求1

? Bit 6 – INT0: 使能外部中断请求0

? Bit 5 – INT2: 使能外部中断请求2

? Bit 1 – IVSEL: 中断向量选择

? Bit 0 – IVCE: 中断向量修改使能

通用中断标志寄存器-GIFR

7 6 5 4 3 2 1 0

INTF1 INTF0 INTF2 –––––

? Bit 7 – INTF1: 外部中断标志1

? Bit 6 – INTF0: 外部中断标志0

? Bit 5 – INTF2: 外部中断标志2

ICC中中断设置

向量号程序地址(2) 中断源中断定义

1 $000(1) RESET 外部引脚电平引发的复位,上电复位,掉电检测复位,看门狗复位,以及JTAG AVR 复位

2 $002 INT0 外部中断请求0

3 $00

4 INT1 外部中断请求1

4 $006 TIMER2 COMP 定时器/ 计数器2 比较匹配

5 $008 TIMER2 OVF 定时器/ 计数器2 溢出

6 $00A TIMER1 CAPT 定时器/ 计数器1 事件捕捉

7 $00C TIMER1 COMPA 定时器/ 计数器1 比较匹配A

8 $00E TIMER1 COMPB 定时器/ 计数器1 比较匹配B

9 $010 TIMER1 OVF 定时器/ 计数器1 溢出

10 $012 TIMER0 OVF 定时器/ 计数器0 溢出

11 $014 SPI, STC SPI 串行传输结束

12 $016 USART, RXC USART,Rx 结束

13 $018 USART, UDRE USART 数据寄存器空

14 $01A USART, TXC USART,Tx 结束

15 $01C ADC ADC 转换结束

16 $01E EE_RDY EEPROM 就绪

17 $020 ANA_COMP 模拟比较器

18 $022 TWI 两线串行接口

19 $024 INT2 外部中断请求2

20 $026 TIMER0 COMP 定时器/ 计数器0 比较匹配

21 $028 SPM_RDY 保存程序存储器内容就绪

Avr-gcc 为重写中断例程提供两个宏来解决细节的问题,它们是 SIGNAL(signame)和INTERRUPT(signame)。参数signame 为中断名称,它的定义在io.h 中包含。表4-1 列出了ATMega8 的signame 定义,其它器件的signame 定义可查阅相应的ioxxxx.h 文件

表4-1 ATMega8 中断名称定义

signame 中断类型

SIG_INTERRUPT0 外部中断INT0

SIG_INTERRUPT1 外部中断INT1

SIG_OUTPUT_COMPARE2 定时器/计数器2比较匹配中断

SIG_OVERFLOW2 定时器/计数器2 溢出中断

SIG_INPUT_CAPTURE1 定时器/计数器1输入捕获中断

SIG_OUTPUT_COMPARE1A 定时器/计数器1 比较匹配A

SIG_OUTPUT_COMPARE1B 定时器/计数器1 比较匹配B

SIG_OVERFLOW1 定时器/计数器1 溢出中断

SIG_OVERFLOW0 定时器/计数器0 溢出中断

SIG_SPI SPI 操作完成中断

SIG_UART_RECV USART 接收完成

SIG_UART_DATA USART 寄存器空

SIG_UART_TRANS USART 发送完成

SIG_ADC ADC 转换完成

SIG_EEPROM_READY E2PROM 准备就绪

SIG_COMPARATOR 模拟比较器中断

SIG_2WIRE_SERIAL TWI 中断

SIG_SPM_READY 写程序存储器准备好

SIGNAL(SIG_OVERFLOW2)

{

}

表示是定时/计数器2溢出中断口

端口引脚配置

DDxn PORTxn PUD(in SFIOR) I/O上拉电阻说明

0 0 X Input No 高阻态(Hi-Z)

0 1 0 Input Yes 被外部电路拉低时将输出电流

0 1 1 Input No 高阻态(Hi-Z)

1 0 X Output No 输出低电平( 吸收电流)

1 1 X Output No 输出高电平( 输出电流)

特殊功能I/O 寄存器-SFIOR

7 6 5 4 3 2 1 0

ADTS2 ADTS1 ADTS0 – ACME PUD PSR2 PSR10

? Bit 0 – PSR10: T/C1 与T/C0 预分频器复位

Bit 2 – PUD: 禁用上拉电阻

? Bit 1 – PSR2: 预分频复位T/C2

? Bit 3 – ACME: 模拟比较器多路复用器使能

? Bit 7:5 – ADTS2:0: ADC 自动触发源

Table 86. ADC 自动触发源选择

ADTS2 ADTS1 ADTS0 触发源

0 0 0 连续转换模式

0 0 1 模拟比较器

0 1 0 外部中断请求0

0 1 1 定时器/ 计数器0 比较匹配

1 0 0 定时器/ 计数器0 溢出

1 0 1 定时器/ 计数器比较匹配B

1 1 0 定时器/ 计数器1 溢出

1 1 1 定时器/ 计数器1 捕捉事件

Table 22. 端口A 的第二功能

端口引脚第二功能

PA7 ADC7 (ADC 输入通道7)

PA6 ADC6 (ADC 输入通道6)

PA5 ADC5 (ADC 输入通道5)

PA4 ADC4 (ADC 输入通道4)

PA3 ADC3 (ADC 输入通道3)

PA2 ADC2 (ADC 输入通道2)

PA1 ADC1 (ADC 输入通道1)

PA0 ADC0 (ADC 输入通道0)

Table 25. 端口 B 的第二功能

端口引脚第二功能

PB7 SCK (SPI 总线的串行时钟)

PB6 MISO (SPI 总线的主机输入/ 从机输出信号)

PB5 MOSI (SPI 总线的主机输出/ 从机输入信号)

PB4 SS (SPI 从机选择引脚)

PB3 AIN1 ( 模拟比较负输入) OC0 (T/C0 输出比较匹配输出)

PB2 AIN0 ( 模拟比较正输入) INT2 ( 外部中断2 输入)

PB1 T1 (T/C1 外部计数器输入)

PB0 T0 (T/C0 外部计数器输入) XCK (USART 外部时钟输入/ 输出) Table 28. 端口 C 的第二功能

端口引脚第二功能

PC7 TOSC2 ( 定时振荡器引脚2)

PC6 TOSC1 ( 定时振荡器引脚1)

PC5 TDI (JTAG 测试数据输入)

PC4 TDO (JTAG 测试数据输出)

PC3 TMS (JTAG 测试模式选择)

PC2 TCK (JTAG 测试时钟)

PC1 SDA ( 两线串行总线数据输入/ 输出线)

PC0 SCL ( 两线串行总线时钟线)

Table 31.端口 D 的第二功能

端口引脚第二功能

PD7 OC2 (T/C2 输出比较匹配输出)

PD6 ICP1 (T/C1 输入捕捉引脚)

PD5 OC1A (T/C1 输出比较A 匹配输出)

PD4 OC1B (T/C1 输出比较B 匹配输出)

PD3 INT1 ( 外部中断1 的输入)

PD2 INT0 ( 外部中断0 的输入)

PD1 TXD (USART 输出引脚)

PD0 RXD (USART 输入引脚)

8 位定时器/ 计数器寄存器的说明T/C 控制寄存器-TCCR0

7 6 5 4 3 2 1 0

FOC0 WGM00 COM01 COM00 WGM01 CS02 CS01 CS00

Bit 7 – FOC0: 强制输出比较

FOC0仅在WGM00指明非PWM模式时才有效。但是,为了保证与未来器件的兼容性,在

使用PWM 时,写TCCR0 要对其清零。对其写1 后,波形发生器将立即进行比较操作。

比较匹配输出引脚 OC0 将按照COM01:0 的设置输出相应的电平。要注意FOC0 类似一

个锁存信号,真正对强制输出比较起作用的是COM01:0 的设置。

0 0 普通端口操作,非OC1A/OC1B 功能

0 1 比较匹配时OC0 电平取反

1 0 比较匹配时清零OC0( 输出低电平)

1 1 比较匹配时置位 OC0 ( 输出高电平)

在CTC 模式下得到波形输出,可以设置OC0 在每次比较匹配发生时改变逻辑电平。

这可以通过设置COM01:0 = 1 来完成。在期望获得OC0 输出之前,首先要将其端口设置

为输出。波形发生器能够产生的最大频率为fOC0 = fclk_I/O/2 (OCR0 = 0x00)。频率由如下公式确定:

f OCnPWM=f clk_I/O/2*N*(1+OCRn)

变量N 代表预分频因子(1、8、64、或1024)。

快速PWM 频率可以通过如下公式计算得到:

f OCnPWM=f clk_I/O/N*256

相位修正模式时PWM 频率可由下式公式获得:

f OCnPWM=f clk_I/O/N*510

变量N 代表分频因子

通过设定OC0 在比较匹配时进行逻辑电平取反(COM01:0 = 1),可以得到占空比为50%

的周期信号。OCR0 为0 时信号有最高频率foc2 = fclk_I/O/2。这个特性类似于CTC 模式下的OC0 取反操作,不同之处在于快速PWM 模式具有双缓冲。

? Bit 2:0 – CS02:0: 时钟选择

Table 42. 时钟选择位定义

CS02 CS01 CS00 说明

0 0 0 无时钟,T/C 不工作

0 0 1 clkI/O/1 ( 没有预分频)

0 1 0 clkI/O/8 ( 来自预分频器)

0 1 1 clkI/O/64 ( 来自预分频器)

1 0 0 clkI/O/256 ( 来自预分频器)

1 0 1 clkI/O/1024 ( 来自预分频器)

1 1 0 时钟由T0 引脚输入,下降沿触发

1 1 1 时钟由T0 引脚输入,上升沿触发

T/C 寄存器-TCNT0

输出比较寄存器-OCR0

输出比较寄存器包含一个8 位的数据,不间断地与计数器数值TCNT0 进行比较。匹配事

件可以用来产生输出比较中断,或者用来在OC0 引脚上产生波形。

T/C 中断屏蔽寄存器- TIMSK

7 6 5 4 3 2 1 0

OCIE2 TOIE2 TICIE1 OCIE1A OCIE1B TOIE1 OCIE0 TOIE0

? Bit 1 – OCIE0: T/C0 输出比较匹配中断使能

? Bit 0 – TOIE0: T/C0 溢出中断使能

? Bit 5 – TICIE1: T/C1 输入捕捉中断使能

? Bit 4 – OCIE1A: 输出比较 A 匹配中断使能

? Bit 3 – OCIE1B: T/C1 输出比较 B 匹配中断使能

? Bit 2 – TOIE1: T/C1 溢出中断使能

? Bit 7 – OCIE2: T/C2 输出比较匹配中断使能

? Bit 6 – TOIE2: T/C2 溢出中断使能

T/C 中断标志寄存器-TIFR

7 6 5 4 3 2 1 0

OCF2 TOV2 ICF1 OCF1A OCF1B TOV1 OCF0 TOV0

? Bit 1 – OCF0: 输出比较标志0

当T/C0 与OCR0( 输出比较寄存器0) 的值匹配时,OCF0 置位。

? Bit 0 – TOV0: T/C0 溢出标志

当T/C0 溢出时,TOV0 置位。

? Bit 5 – ICF1: T/C1 输入捕捉标志位

? Bit 4 – OCF1A: T/C1 输出比较A 匹配标志位

? Bit 3 – OCF1B: T/C1 输出比较B 匹配标志位

? Bit 2 – TOV1: T/C1 溢出标志

? Bit 7 – OCF2: 输出比较标志2

? Bit 6 – TOV2: T/C2 溢出标志

16 位定时器/ 计数器寄存器的说明T/C1 控制寄存器A -TCCR1A

7 6 5 4 3 2 1 0

COM1A1 COM1A0 COM1B1 COM1B0 FOC1A FOC1B WGM11 WGM10

? Bit 7:6 – COM1A1:0: 通道A 的比较输出模式

? Bit 5:4 – COM1B1:0: 通道B 的比较输出模式

COM1A1:0与COM1B1:0分别控制OC1A 与OC1B状态。如果COM1A1:0(COM1B1:0)的

一位或两位被写入"1”,OC1A(OC1B) 输出功能将取代I/O 端口功能。此时OC1A(OC1B)

相应的输出引脚数据方向控制必须置位以使能输出驱动器

比较输出模式,非PWM

COM1A1/COM1B1 COM1A0/COM1B0说明

0 0 普通端口操作,非OC1A/OC1B 功能

0 1 比较匹配时OC1A/OC1B 电平取反

1 0 比较匹配时清零OC1A/OC1B( 输出低电平)

1 1 比较匹配时置位 OC1A/OC1B ( 输出高电平)

? Bit 3 – FOC1A: 通道A 强制输出比较

? Bit 2 – FOC1B: 通道B 强制输出比较

? Bit 1:0 – WGM11:0: 波形发生模式

这两位与位于TCCR1B 寄存器的WGM13:2 相结合,用于控制计数器的计数序列——计数器计数的上限值和确定波形发生器的工作模式(见下页表格)

T/C1 控制寄存器B -TCCR1B

7 6 5 4 3 2 1 0

ICNC1 ICES1 – WGM13 WGM12 CS12 CS11 CS10

? Bit 7 – ICNC1: 输入捕捉噪声抑制器置位ICNC1将使能输入捕捉噪声抑制功能

? Bit 6 – ICES1: 输入捕捉触发沿选择

? Bit 4:3 – WGM13:2: 波形发生模式

? Bit 2:0 – CS12:0: 时钟选择

CS12 CS11 CS10 说明

0 0 0 无时钟源(T/C 停止)

0 0 1 clkI/O/1 ( 无预分频)

0 1 0 clkI/O/8 ( 来自预分频器)

0 1 1 clkI/O/64 ( 来自预分频器)

1 0 0 clkI/O/256 ( 来自预分频器)

1 0 1 clkI/O/1024 ( 来自预分频器)

1 1 0 外部T1 引脚,下降沿驱动

1 1 1 外部T1 引脚,上升沿驱动

T/C1数据寄存器TCNT1-TCNT1H 与TCNT1L

TCNT1[15:8] TCNT1H

TCNT1[7:0] TCNT1L

TCNT1H与TCNT1L组成了T/C1的数据寄存器TCNT1。通过它们可以直接对定时器/计数器单元的16 位计数器进行读写输出比较寄存器1A -OCR1AH与OCR1AL

OCR1A[15:8] OCR1AH

OCR1A[7:0] OCR1AL

输出比较寄存器1B -OCR1BH与OCR1BL

OCR1B[15:8] OCR1BH

OCR1B[7:0] OCR1BL

该寄存器中的16 位数据与TCNT1 寄存器中的计数值进行连续的比较,一旦数据匹配,将产生一个输出比较中断,或改变OC1x 的输出逻辑电平。

输入捕捉寄存器1 -ICR1H 与ICR1L

ICR1[15:8] ICR1H

ICR1[7:0] ICR1L

当外部引脚ICP1(或T/C1的模拟比较器)有输入捕捉触发信号产生时,计数器TCNT1中的值写入ICR1 中。ICR1 的设定值可作为计数器的TOP 值。

8 位有PWM 与异步操作的定时器/ 计数器2 T/C 控制寄存器-TCCR2

7 6 5 4 3 2 1 0

FOC2 WGM20 COM21 COM20 WGM21 CS22 CS21 CS20

? Bit 7 – FOC2: 强制输出比较

? Bit 6, 3 – WGM21:0: 波形产生模式

? Bit 5:4 – COM21:0: 比较匹配输出模式

? Bit 2:0 – CS22:0: 时钟选择

T/C 可以由内部同步时钟或外部异步时钟驱动。 clkT2 的缺省设置为MCU 时钟clkI/O。当

ASSR寄存器的AS2置位时,时钟源来自于TOSC1和TOSC2连接的振荡器。

CS22 CS21 CS20 说明

0 0 0 无时钟,T/C 不工作

0 0 1 clkT2S/1( 没有预分频)

0 1 0 clkT2S/8 ( 来自预分频器)

0 1 1 clkT2S/32 ( 来自预分频器)

1 0 0 clkT2S/64 ( 来自预分频器)

1 0 1 clkT2S/128 ( 来自预分频器)

1 1 0 clkT2S/256 ( 来自预分频器)

1 1 1 clkT2S/1024 ( 来自预分频器)

BOTTOM 计数器计到0x00 时即达到BOTTOM

MAX 计数器计到0xFF ( 十进制的255) 时即达到MAX

TOP 计数器计到计数序列的最大值时即达到TOP。TOP 值可以为固定值0xFF

(MAX),或是存储于寄存器OCR2 里的数值,具体由工作模式确定

定时器/ 计数器寄存器-TCNT2 TCNT2[7:0]

通过T/C 寄存器可以直接对计数器的8 位数据进行读写访问

输出比较寄存器-OCR2 OCR2[7:0]

输出比较寄存器包含一个8 位的数据,不间断地与计数器数值TCNT2 进行比较。匹配事

件可以用来产生输出比较中断,或者用来在OC2 引脚上产生波形。

异步状态寄存器-ASSR

7 6 5 4 3 2 1 0

–––– AS2 TCN2UB OCR2UB TCR2UB

? Bit 3 – AS2: 异步T/C2

? Bit 2 – TCN2UB: T/C2 更新中写TCNT2将引起TCN2UB置位更新完毕后由硬件清零

? Bit 1 – OCR2UB: 输出比较寄存器2 更新中,写OCR2将引起OCR2UB置位更新完毕后由硬件清零

? Bit 0 – TCR2UB: T/C2 控制寄存器更新中,写TCCR2将引起TCR2UB置位更新完毕后由硬件清零

定时器/ 计数器2 的异步操作T/C2 工作于异步模式时要考虑如下几点:

? 警告:在同步和异步模式之间的转换有可能造成TCNT2、OCR2 和TCCR2 数据的损

毁。安全的步骤应该是:

1. 清零OCIE2 和TOIE2 以关闭T/C2 的中断

2. 设置AS2 以选择合适的时钟源

3. 对TCNT2、OCR2 和TCCR2 写入新的数据

4. 切换到异步模式:等待TCN2UB、OCR2UB 和TCR2UB 清零

5. 清除T/C2 的中断标志

6. 需要的话使能中断

串行外设接口-SPI

/SS引脚的功能

从机模式当SPI 配置为主机时,从机选择引脚SS 总是为输入。SS 为低将激活SPI 接口,MISO成为输出( 用户必须进行相应的端口配置) 引脚,其他引脚成为输入引脚。当SS 为高时所有的引脚成为输入,SPI 逻辑复位,不再接收数据。SS引脚对于数据包/字节的同步非常有用,可以使从机的位计数器与主机的时钟发生器同步。当SS 拉高时SPI从机立即复位接收和发送逻辑,并丢弃移位寄存器里不完整的数据。

主机模式当SPI 配置为主机时(MSTR 的SPCR 置位),用户可以决定SS 引脚的方向。若SS 配置为输出,则此引脚可以用作普通的I/O 口而不影响SPI 系统。典型应用是用来驱动从机的SS 引脚。

如果SS 配置为输入,必须保持为高以保证SPI 的正常工作。若系统配置为主机,SS 为输入,但被外设拉低,则SPI 系统会将此低电平解释为有一个外部主机将自己选择为从机。为了防止总线冲突,SPI 系统将实现如下动作:

1. 清零SPCR 的MSTR 位,使SPI 成为从机,从而MOSI 和SCK 变为输入。

2. SPSR 的SPIF 置位。若SPI 中断和全局中断开放,则中断服务程序将得到执行。

因此,使用中断方式处理SPI 主机的数据传输,并且存在SS 被拉低的可能性时,中断服务程序应该检查MSTR 是否为"1”。若被清零,用户必须将其置位,以重新使能SPI 主机模式。

SPI 控制寄存器-SPCR

7 6 5 4 3 2 1 0

SPIE SPE DORD MSTR CPOL CPHA SPR1 SPR0

? Bit 7 – SPIE: 使能SPI 中断

? Bit 6 – SPE: 使能SPI

? Bit 5 – DORD: 数据次序

DORD 置位时数据的LSB 首先发送;否则数据的MSB 首先发送。

? Bit 4 – MSTR: 主/ 从选择

MSTR置位时选择主机模式,否则为从机。如果MSTR为"1”,SS配置为输入,但被拉低,则MSTR 被清零,寄存器SPSR 的SPIF 置位。用户必须重新设置MSTR 进入主机模式

? Bit 3 – CPOL: 时钟极性

CPOL 置位表示空闲时SCK 为高电平;否则空闲时SCK 为低电平

Table 56. CPOL 功能

CPOL 起始沿结束沿

0 (低电平)上升沿下降沿

1 (高电平)下降沿上升沿

? Bit 2 – CPHA: 时钟相位

CPHA 决定数据是在SCK 的起始沿采样还是在SCK 的结束沿采样。

Table 57. CPHA 功能

CPHA 起始沿结束沿

0 采样设置

1 设置采样

CPOL: 时钟极性与CPHA: 时钟相位决定SPI 模式(见table 59)

? Bits 1, 0 – SPR1, SPR0: SPI 时钟速率选择1 与0

确定主机的SCK 速率。SPR1 和SPR0 对从机没有影响。

Table 58. SCK 和振荡器频率的关系

SPI2X (SPI 的速度加倍)SPR1 SPR0 SCK 频率

0 0 0 fosc/4

0 0 1 fosc/16

0 1 0 fosc/64

0 1 1 fosc/128

1 0 0 fosc/2

1 0 1 fosc/8

1 1 0 fosc/32

1 1 1 fosc/64

SPI 状态寄存器-SPSR

7 6 5 4 3 2 1 0

SPIF WCOL ––––– SPI2X

? Bit 7 – SPIF: SPI 中断标志

串行发送结束后,SPIF 置位。若此时寄存器SPCR 的SPIE 和全局中断使能位置位,SPI

中断即产生。如果SPI 为主机,SS 配置为输入,且被拉低,SPIF 也将置位。进入中断

服务程序后SPIF自动清零。或者可以通过先读SPSR,紧接着访问SPDR来对SPIF清零。

? Bit 6 – WCOL: 写碰撞标志

在发送当中对SPI 数据寄存器SPDR写数据将置位WCOL。WCOL可以通过先读SPSR,

紧接着访问SPDR 来清零。

? Bit 0 – SPI2X: SPI 倍速

置位后SPI 的速度加倍

SPI 数据寄存器-SPDR

7 6 5 4 3 2 1 0

MSB LSB

SPI 数据寄存器为读/写寄存器,用来在寄存器文件和SPI移位寄存器之间传输数据。写寄

存器将启动数据传输,读寄存器将读取寄存器的接收缓冲器

数据模式

Table 59. CPOL 与CPHA 功能

起始沿结束沿SPI 模式

CPOL= 0, CPHA = 0 采样( 上升沿) 设置( 下降沿) 0

CPOL = 0, CPHA = 1 设置( 上升沿) 采样( 下降沿) 1

CPOL = 1, CPHA = 0 采样( 下降沿) 设置( 上升沿) 2

CPOL = 1, CPHA = 1 设置( 下降沿) 采样( 上升沿) 3

USART

通用同步和异步串行接收器和转发器(USART) 是一个高度灵活的串行通讯设备

寄存器描述

USART I/O 数据寄存器-UDR

RXB[7:0] UDR (Read)

TXB[7:0] UDR (Write)

将数据写入UDR 时实际操作的是发送数据缓冲器存器(TXB),读UDR 时实际返回的是接收数据缓冲寄存器(RXB) 的内容

只有当UCSRA寄存器的UDRE标志置位后才可以对发送缓冲器进行写操作。如果UDRE没有置位,那么写入UDR 的数据会被USART 发送器忽略。当数据写入发送缓冲器后,若移位寄存器为空,发送器将把数据加载到发送移位寄存器。然后数据串行地从TxD 引脚输出。

USART 控制和状态寄存器A -UCSRA

7 6 5 4 3 2 1 0

RXC TXC UDRE FE DOR PE U2X MPCM

? Bit 7 – RXC: USART 接收结束

接收缓冲器中有未读出的数据时RXC 置位,否则清零

? Bit 6 – TXC: USART 发送结束

发送移位缓冲器中的数据被送出,且当发送缓冲器 (UDR) 为空时TXC 置位。执行发送结束中断时TXC 标志自动清零

? Bit 5 – UDRE: USART 数据寄存器空

UDRE标志指出发送缓冲器(UDR)是否准备好接收新数据。UDRE为1说明缓冲器为空,已

准备好进行数据接收。UDRE标志可用来产生数据寄存器空中断

? Bit 4 – FE: 帧错误

如果接收缓冲器接收到的下一个字符有帧错误,即接收缓冲器中的下一个字符的第一个

停止位为0,那么FE 置位。这一位一直有效直到接收缓冲器(UDR) 被读取。当接收到的

停止位为1 时, FE 标志为0。对UCSRA 进行写入时,这一位要写0

? Bit 3 – DOR: 数据溢出

? Bit 2 – PE: 奇偶校验错误

当奇偶校验使能(UPM1 = 1),且接收缓冲器中所接收到的下一个字符有奇偶校验错误时UPE 置位。这一位一直有效直到接收缓冲器 (UDR) 被读取。对UCSRA 进行写入时,这一位要写0。

? Bit 1 – U2X: 倍速发送

? Bit 0 – MPCM: 多处理器通信模式

设置此位将启动多处理器通信模式。MPCM 置位后, USART 接收器接收到的那些不包

含地址信息的输入帧都将被忽略。发送器不受MPCM设置的影响。详细信息请参考P150“多处理器通讯模式”

USART 控制和状态寄存器B -UCSRB

7 6 5 4 3 2 1 0

RXCIE TXCIE UDRIE RXEN TXEN UCSZ2 RXB8 TXB8

? Bit 7 – RXCIE: 接收结束中断使能

? Bit 6 – TXCIE: 发送结束中断使能

? Bit 5 – UDRIE: USART 数据寄存器空中断使能

? Bit 4 – RXEN: 接收使能

? Bit 3 – TXEN: 发送使能

? Bit 2 – UCSZ2: 字符长度(与UCSZ1 UCSZ0 决定字符的长度)

? Bit 1 – RXB8: 接收数据位8

? Bit 0 – TXB8: 发送数据位8

USART 控制和状态寄存器C -UCSRC

7 6 5 4 3 2 1 0

URSEL UMSEL UPM1 UPM0 USBS UCSZ1 UCSZ0 UCPOL

? Bit 7 – URSEL: 寄存器选择

通过该位选择访问UCSRC 寄存器或UBRRH 寄存器。当读UCSRC 时,该位为1 ;当写UCSRC 时,URSEL 为1。

? Bit 6 – UMSEL: USART 模式选择

Table 63. UMSEL 设置

UMSEL 模式

0 异步操作

1 同步操作

? Bit 5:4 – UPM1:0: 奇偶校验模式

Table 64. UPM 设置

UPM1 UPM0 奇偶模式

0 0 禁止

0 1 保留

1 0 偶校验

1 1 奇校验

? Bit 3 – USBS: 停止位选择

Table 65. USBS 设置

USBS 停止位位数

0 1

1 2

? Bit 2:1 – UCSZ1:0: 字符长度

Table 66. UCSZ 设置

UCSZ2 UCSZ1 UCSZ0 字符长度

UCSZ1:0与UCSRB寄存器的 UCSZ2结合在一起可以设置数据帧包含的数据位数(字符长度)。

0 0 0 5 位

0 0 1 6 位

0 1 0 7 位

0 1 1 8 位

1 0 0 保留

1 0 1 保留

1 1 0 保留

1 1 1 9 位

? Bit 0 – UCPOL: 时钟极性

这一位仅用于同步工作模式。使用异步模式时,将这一位清零。UCPOL 设置了输出数据

的改变和输入数据采样,以及同步时钟XCK 之间的关系。

Table 67. UCPOL 设置

UCPOL 发送数据的改变(TxD 引脚的输出) 接收数据的采样(RxD 引脚的输入)

0 XCK上升沿XCK 下降沿

1 XCK下降沿XCK 上升沿

USART 波特率寄存器-UBRRL 和UBRRH

15 14 13 12 11 10 9 8

URSEL ––– UBRR[11:8] UBRRH

UBRR[7:0] UBRRL

? Bit 15 – URSEL: 寄存器选择

通过该位选择访问UCSRC 寄存器或UBRRH 寄存器。当读UBRRH 时,该位为0 ;当写UBRRH 时, URSEL 为0。

两线串行接口TWI

Table 72. TWI 词汇

单词说明

主机启动和停止传输的设备。主机同时要产生SCL 时钟

从机被主机寻址的设备

发送器将数据放到总线上的设备

接收器从总线读取数据的设备

TWI 寄存器说明

TWI 比特率寄存器-TWBR

7 6 5 4 3 2 1 0

TWBR7 TWBR6 TWBR5 TWBR4 TWBR3 TWBR2 TWBR1 TWBR0

? Bits 7..0 – TWI 比特率寄存器

SCL 的频率根据以下的公式产生:

SCL frequency =CPU Clock frequency/(16 +2(TWBR) *4TWPS)

? TWBR = TWI比特率寄存器的数值

? TWPS = TWI 状态寄存器预分频的数值

TWI 控制寄存器-TWCR

7 6 5 4 3 2 1 0

TWINT TWEA TWSTA TWSTO TWWC TWEN – TWIE

? Bit 7 – TWINT: TWI 中断标志

? Bit 6 – TWEA: 使能TWI 应答

TWEA 标志控制应答脉冲的产生。若TWEA 置位,出现如下条件时接口发出ACK 脉冲:

1. 器件的从机地址与主机发出的地址相符合

2. TWAR 的TWGCE 置位时接收到广播呼叫

3. 在主机/ 从机接收模式下接收到一个字节的数据

? Bit 5 – TWSTA: TWI START 状态标志

当CPU 希望自己成为总线上的主机时需要置位TWSTA。

? Bit 4 – TWSTO: TWI STOP 状态标志

在主机模式下,如果置位TWSTO,TWI 接口将在总线上产生STOP 状态,然后TWSTO

自动清零。在从机模式下,置位TWSTO 可以使接口从错误状态恢复到未被寻址的状态。

此时总线上不会有STOP 状态产生,但TWI 返回一个定义好的未被寻址的从机模式且释

放SCL 与SDA 为高阻态。

? Bit 3 – TWWC: TWI 写碰撞标志

当TWINT 为低时写数据寄存器TWDR 将置位TWWC。当TWINT 为高时,每一次对

TWDR 的写访问都将更新此标志

? Bit 2 – TWEN: TWI 使能

? Bit 0 – TWIE: 使能TWI 中断

当SREG 的I 以及TWIE 置位时,只要TWINT 为"1”,TWI 中断就激活

TWI 状态寄存器-TWSR

7 6 5 4 3 2 1 0

TWS7 TWS6 TWS5 TWS4 TWS3 – TWPS1 TWPS0

? Bits 7..3 – TWS: TWI 状态

这5 位用来反映TWI 逻辑和总线的状态

存放状态码,查询它可以知道TWI运行于何种状态

主机发送模式的状态码

状态码(TWSR) 预分频位为"0” 2线串行总线和2线串行硬件的状态

$08 START 已发送

$10 重复START 已发送

$18 SLA+W 已发送;接收到ACK

$20 SLA+W 已发送接收到NOT ACK

$28 数据已发送接收到ACK

$30 数据已发送接收到NOT ACK

$38 SLA+W 或数据的仲裁失败

主机接收模式的状态码

状态码(TWSR) 预分频位为"0” 2线串行总线和2线串行硬件的状态

$08 START 已发送

$10 重复START 已发送

$38 SLA+R 或NOT ACK 的仲裁失败

$40 SLA+R 已发送接收到ACK

$48 SLA+R 已发送接收到NOT ACK

$50 接收到数据ACK 已返回

$58 接收到数据NOT ACK 已返回

从机接收模式的状态码

状态码(TWSR) 预分频位为"0” 2线串行总线和2线串行硬件的状态

$60 自己的SLA+W 已经被接收ACK 已返回

$68 SLA+R/W 作为主机的仲裁失败;自己的SLA+W 已经被接收ACK 已返回$70 接收到广播地址ACK 已返回

$78 SLA+R/W 作为主机的仲裁失败;接收到广播地址 ACK 已返回

$80 以前以自己的 SLA+W 被寻址;数据已经被接收ACK 已返回

$88 以前以自己的 SLA+W 被寻址;数据已经被接收NOT ACK 已返回

$90 以前以广播方式被寻址;数据已经被接收ACK 已返回

$98 以前以广播方式被寻址;数据已经被接收NOT ACK 已返回

$A0 在以从机工作时接收到STOP或重复START

从机发送模式的状态码

状态码(TWSR) 预分频位为"0” 2线串行总线和2线串行硬件的状态

$A8 自己的SLA+R 已经被接收ACK 已返回

$B0 SLA+R/W 作为主机的仲裁失败;自己的SLA+R 已经被接收ACK 已返回$B8 TWDR里数据已经发送接收到ACK

$C0 TWDR里数据已经发送接收到NOT ACK

$C8 TWDR 的一字节数据已经发送(TWAE = “0”);接收到ACK

其它状态码

状态码(TWSR) 预分频位为”0” 2线串行总线和2线串行硬件的状态

$F8 没有相关的状态信息;TWINT = “0”

$00 由于非法的START 或STOP 引起的总线错误

? Bits 1..0 – TWPS: TWI 预分频位

Table 73. TWI 比特率预分频器

TWPS1 TWPS0 预分频器值

0 0 1

0 1 4

1 0 16

1 1 64

TWI 数据寄存器-TWDR

7 6 5 4 3 2 1 0

TWD7 TWD6 TWD5 TWD4 TWD3 TWD2 TWD1 TWD0

TWI( 从机) 地址寄存器-TWAR

7 6 5 4 3 2 1 0

TWA6 TWA5 TWA4 TWA3 TWA2 TWA1 TWA0 TWGCE

? Bit 0 – TWGCE: 使能TWI 广播识别

? Bits 7..1 – TWA: TWI 从机地址寄存器

数据传输模式

TWI 可以工作于4 个不同的模式:主机发送器(MT)、主机接收器(MR)、从机发送器(ST)及从机接收器(SR)。

模拟比较

模拟比较器对正极AIN0 的值与负极AIN1 的值进行比较。当AIN0 上的电压比负极AIN1上的电压要高时,模拟比较器的输出ACO 即置位。比较器的输出可用来触发定时器/ 计数器1 的输入捕捉功能。此外,比较器还可触发自己专有的、独立的中断

模拟比较器控制和状态寄存器-ACSR

7 6 5 4 3 2 1 0

ACD ACBG ACO ACI ACIE ACIC ACIS1 ACIS0

? Bit 7 – ACD: 模拟比较器禁用

ACD 置位时,模拟比较器的电源被切断

? Bit 6 – ACBG: 选择模拟比较器的能隙基准源

ACBG 置位后,模拟比较器的正极输入由能隙基准源所取代。否则, AIN0 连接到模拟比较器的正极输入。ATmega16 具有片内能隙基准源,用于掉电检测,或者是作为模拟比较器或ADC的输入。ADC 的2.56V 基准电压由此片内能隙基准源产生

? B it 5 – ACO: 模拟比较器输出

? Bit 4 – ACI: 模拟比较器中断标志

当比较器的输出事件触发了由ACIS1 及ACIS0 定义的中断模式时,ACI 置位。如果ACIE

和SREG 寄存器的全局中断标志I 也置位,那么模拟比较器中断服务程序即得以执行,同

时ACI 被硬件清零。ACI 也可以通过写"1” 来清零。

? Bit 3 – ACIE: 模拟比较器中断使能

? Bit 2 – ACIC: 模拟比较器输入捕捉使能

ACIC置位后允许通过模拟比较器来触发T/C1 的输入捕捉功能。此时比较器的输出被直接

连接到输入捕捉的前端逻辑,从而使得比较器可以利用T/C1 输入捕捉中断逻辑的噪声抑

制器及触发沿选择功能。

? Bits 1, 0 – ACIS1, ACIS0: 模拟比较器中断模式选择

Table 79. ACIS1/ACIS0 设置

ACIS1 ACIS0 中断模式

0 0 比较器输出变化即可触发中断

0 1 保留

1 0 比较器输出的下降沿产生中断

1 1 比较器输出的上升沿产生中断

模拟比较器多工输入

可以选择ADC7..0 之中的任意一个来代替模拟比较器的负极输入端。ADC 复用器可用来完成这个功能。当然,为了使用这个功能首先必须关掉ADC。如果模拟比较器复用器使能位(SFIOR 中的ACME) 被置位,且ADC 也已经关(ADCSRA 寄存器的ADEN 为0),则可以通过ADMUX 寄存器的MUX2..0 来选择替代模拟比较器负极输入的管脚,

Table 80. 模拟比较器复用输入

ACME ADEN MUX2..0 模拟比较器负极输入

0 x xxx AIN1

1 1 xxx AIN1

1 0 000 ADC0

1 0 001 ADC1

1 0 010 ADC2

1 0 011 ADC3

1 0 100 ADC4

1 0 101 ADC5

1 0 110 ADC6

1 0 111 ADC7

●模数转换器ADC 多工选择寄存器-ADMUX

7 6 5 4 3 2 1 0

REFS1 REFS0 ADLAR MUX4 MUX3 MUX2 MUX1 MUX0

? Bit 7:6 – REFS1:0: 参考电压选择

Table 83. ADC 参考电压选择

REFS1 REFS0 参考电压选择

0 0 AREF,内部Vref 关闭

0 1 AVCC,AREF 引脚外加滤波电容

1 0 保留

1 1 2.56V 的片内基准电压源,AREF 引脚外加滤波电容

ADC的参考电压源(VREF)反映了ADC的转换范围。若单端通道电平超过了VREF,其结果将

接近0x3FF。VREF 可以是AVCC、内部2.56V 基准或外接于AREF 引脚的电压。

? Bit 5 – ADLAR: ADC 转换结果

ADLAR影响ADC转换结果在ADC数据寄存器中的存放形式。ADLAR置位时转换结果为左对齐,否则为右对齐(默认的)? Bits 4:0 – MUX4:0: 模拟通道与增益选择位

通过这几位的设置,可以对连接到ADC 的模拟输入进行选择。也可对差分通道增益进行选择。

MUX4..0 单端输入

00000 ADC0

00001 ADC1

00010 ADC2

00011 ADC3

00100 ADC4

00101 ADC5

00110 ADC6

00111 ADC7

…..正差分输入负差分输入增益

在默认条件下,逐次逼近电路需要一个从50 kHz到200 kHz的输入时钟以获得最大精度。

如果所需的转换精度低于10 比特,那么输入时钟频率可以高于200 kHz,以达到更高的

采样率。

ADC 模块包括一个预分频器,它可以由任何超过100 kHz 的CPU 时钟来产生可接受的

ADC 时钟。预分频器通过ADCSRA 寄存器的ADPS 进行设置。置位ADCSRA 寄存器的

ADEN 将使能ADC,预分频器开始计数。只要ADEN 为1,预分频器就持续计数,直到

ADEN 清零。

ADC 控制和状态寄存器A -ADCSRA

7 6 5 4 3 2 1 0

ADEN ADSC ADATE ADIF ADIE ADPS2 ADPS1 ADPS0

? Bit 7 – ADEN: ADC 使能

? Bit 6 – ADSC: ADC 开始转换

在单次转换模式下,ADSC 置位将启动一次ADC 转换。在连续转换模式下,ADSC 置位将启动首次转换? Bit 5 – ADATE: ADC 自动触发使能

ADATE置位将启动ADC自动触发功能。触发信号的上跳沿启动ADC转换。

触发信号源通过SFIOR 寄存器的ADC 触发信号源选择位ADTS 设置。

特殊功能IO 寄存器- SFIOR

7 6 5 4 3 2 1 0

ADTS2 ADTS1 ADTS0 – ACME PUD PSR2 PSR10

ADC 自动触发源选择

ADTS2 ADTS1 ADTS0触发源

0 0 0 连续转换模式

0 0 1 模拟比较器

0 1 0 外部中断请求0

0 1 1 定时器/ 计数器0 比较匹配

1 0 0 定时器/ 计数器0 溢出

1 0 1 定时器/ 计数器1 比较匹配B

1 1 0 定时器/ 计数器1 溢出

1 1 1 定时器/ 计数器1 捕捉事件

? Bit 4 – ADIF: ADC 中断标志在ADC 转换结束,且数据寄存器被更新后,ADIF 置位。

? Bit 3 – ADIE: ADC 中断使能若ADIE 及SREG 的位I 置位,ADC 转换结束中断即被使能。

? Bits 2:0 – ADPS2:0: ADC 预分频器选择位

由这几位来确定XTAL 与ADC 输入时钟之间的分频因

Table 85. ADC 预分频选择

ADPS2 ADPS1 ADPS0 分频因子

0 0 0 2

0 0 1 2

0 1 0 4

0 1 1 8

1 0 0 16

1 0 1 32

1 1 0 64

1 1 1 128

ADC 数据寄存器-ADCL 及ADCH

ADLAR = 0(右对齐、默认)ADLAR = 1(左对齐)

ADC 转换结束后,转换结果存于这两个寄存器之中。如果采用差分通道,结果由2 的补码形式表示。读取ADCL 之后,ADC 数据寄存器一直要等到ADCH 也被读出才可以进行数据更新。因此,如果转换结果为左对齐,且要求的精度不高于8 比特,那么仅需读取ADCH 就足够了。否则必须先读出ADCL 再读ADCH。

JTAG 接口和片上调试系统OCD(On-chipDebug)

? TMS: 测试模式选择。此引脚用来实现TAP 控制器各个状态之间的切换。

? TCK: 测试时钟。JTAG 操作是与TCK 同步的。

? TDI: 测试数据输入--需要移位到指令寄存器或数据寄存器(扫描链)的串行输入数据。

? TDO: 测试数据输出-- 自指令寄存器或数据寄存器串行移出的数据。

I/O 存储器里与片上调试相关的寄存器

片上调试寄存器- OCDR

7 6 5 4 3 2 1 0

(MSB/IDRD)-------

OCDR 寄存器为运行于微控制器的程序和调试器提供了一个通信信道。CPU 可以通对该字节进行写操作将一个字节传输到调试器。与此同时, I/O 调试寄存器脏位–IDRD –被置位,以此来告知调试器寄存器已经被进行了写操作。CPU 读取OCDR 寄存器时,7 个LSB 来自于OCDR 寄存器,而MSB 是IDRD 位。调试器读完信息后清除IDRD 位。在一些AVR 器件中,这个寄存器与标准I/O 存储单元共享。此时,只有在熔丝位OCDEN被编程,并且调试器访问OCDR 寄存器功能被使能, MCU 访问的才是OCDR 寄存器。在其他情况下, MCU 访问的则是标准的I/O 存储单元

JTAG 编程支持:

? Flash编程和校验

? EEPROM 编程和校验

? 熔丝位编程和校验

? 锁定位编程和校验

AUXR:辅助寄存器 字节地址=8EH,不可位寻址 - - - WDIDLE DISRTO - - DISALE WDIDLE:WTD在空闲模式下的禁止/允许位 当WDIDLE=0时,WDT在空闲模式下继续计数 当WDIDLE=1时,WDT在空闲模式下暂停计数 DISRTO:禁止/允许WDT溢出时的复位输出 当DISRTO=0时,WDT定时器溢出时,在RST引脚输出一个高电平脉冲 当DISRT0=1时,RST引脚为输入脚 DISALE :ALE禁止/允许位 当DISALE=0时,ALE有效,发出恒定频率脉冲 当DISALE=1时,ALE仅在CPU执行MOVC和MOVX类指令时有效,不访问外寄存器时,ALE不输出脉冲信号 AUXR1:辅助寄存器1字节地址A2,不可位寻 - - - -- - - DPS DPS:数据指针寄存器选择位 当DPS=0时,选择数据指针寄存器DPRT0 DPRT1时,选择数据指针寄存器DPS 当= PSW:程序状态字 CY——进位标记 AC——半进位标记 F0——用户设定标记 RS1、RS0——4个工作寄存器区的选择位。 VO——溢出标记 P——奇偶校验标记 PCON:电源控制器及波特率选择寄存器 字节地址=87H,不可位寻址 SMOD - - POF GF1 GF0 PD IDL SMOD——波特率倍增位 GF1、GF0——用户通用标记 PD——掉电方式控制位,PD=1时进入掉电模式 IDL——空闲方式控制位,IDL=1时进入空闲方式 在AT89S51中PCON.4是电源断电标记位POF,上电是为1 IE:中断允许控制寄存器

EA:中断允许总控制位 当EA=0时,中断总禁止。 当EA=1时,中断总允许后中断的禁止与允许由各中断源的中断允许控制位进行设置。 EX0( EX1):外部中断允许控制位 当EX0( EX1)=0 禁止外中断 当EX0( EX1)=1 允许外中断 ET0(EX1):定时/计数中断允许控制位 当ET0(ET1)=0 禁止定时(或计数)中断 当ET0(ET1)=1 允许定时(或计数)中断 ET2:定时器2中断允许控制位,在AT89S52、AT89C52中 ES:串行中断允许控制位 当ES=0 禁止串行中断 当ES=1 允许串行中断 IP:中断优先级控制寄存器 PX0——外部中断0优先级设定位 PT0——定时中断0优先级设定位 PX1——外部中断1优先级设定位 PT1——定时中断1优先级设定位 PS——串口中断优先级设定位 优先级设定位2PT2——定时器SCON:串行口控制寄存器 SM0、SM1:串行口工作方式选择位 SM2:多机通信控制位 REN:允许/禁止串行口接收的控制位 TB8:在方式2和方式3中,是被发送的第9位数据,可根据需要由软件置1或清零,也可以作为奇偶校验位,在方式1中是停止位。

https://www.doczj.com/doc/942900743.html,/p-20032411.html

寄存器和存储器的区别

如果仅是讨论CPU的范畴 寄存器在cpu的内部,容量小,速度快 存储器一般都在cpu外部,容量大,速度慢 回答者:athlongyj - 高级经理六级6-1 08:52 从根本上讲,寄存器与RAM的物理结构不一样。 一般寄存器是指由基本的RS触发器结构衍生出来的D触发, 就是一些与非门构成的结构,这个在数电里面大家都看过; 而RAM则有自己的工艺,一般1Bit由六MOS管构成。所以, 这两者的物理结构不一样也导致了两者的性能不同。寄存器 访问速度快,但是所占面积大。而RAM相反,所占面积小, 功率低,可以做成大容量存储器,但访问速度相对慢一点。 1、 寄存器存在于CPU中,速度很快,数目有限; 存储器就是内存,速度稍慢,但数量很大; 计算机做运算时,必须将数据读入寄存器才能运算。 2、 存储器包括寄存器, 存储器有ROM和RAM 寄存器只是用来暂时存储,是临时分配出来的,断电,后,里面的内容就没了`````

寄存器跟存储器有什么区别? 一般数据在内存里面,要处理(或运算)的时候, 独到寄存器里面。 然后CPU到寄存器里面拿值,拿到运算核内部, 算好了在送到寄存器里面 再到内存 寄存器跟存储器有什么区别? 寄存器跟存储器有什么区别? 寄存器上:“一个操作码+一个操作数”等于一条微指令吗?一条微指令是完成一条机器指令的一个步骤对吗?cpu是直接跟寄存器打交道的对吗?也就是说寄存器是运算器、控制器的组成部分对不? 设计一条指令就是说把几条微指令组合起来对吗? 刚开始学硬件相关知识,学的晕头转向的!! 存储器与寄存器区别 2009-06-09 12:27 寄存器是CPU内部存储单元,数量有限,一般在128bit内,但是速度快,CPU访问几乎没有任何延迟。分为通用寄存器和特殊功能寄存器。 通常说的存储器是独立于cpu之外的,比如内存,硬盘,光盘等。 所有数据必须从存储器传入寄存器后,cpu才能使用。

P0SEL(P1SEL相同):各个I/O口的功能选择,0为普通I/O功能,1为 P2SEL:(D0到D2位)端口2 功能选择和端口1 外设优先级控制 什么是外设优先级:当PERCFG分配两个外设到相同的引脚时,需要设置这两 PERCFG:设置部分外设的I/O位置,0为默认I位置1,1为默认位置2

P0DIR(P1DIR相同):设置各个I/O的方向,0为输入,1为输出 P2DIR :D0~D4设置P2_0到P2_4的方向 D7、D6位作为端口0外设优先级的控制

P0INP(P1INP意义相似) :设置各个I/O口的输入模式,0为上拉/下拉,1 需要注意的是:P1INP中,只有D7~D2分别设置对应I/O口的输入模式。D1D0两位无作用。 P2INP:D0~D4控制P2_0~P2_4的输入模式,0为上拉/下拉,1为三态; D5~D7设置对P0、P1和P2的上拉或下拉的选择。0为上拉,1

P0IFG(P1IFG相同):终端状态标志寄存器,当输入端口有中断请求时,相应的标志位将置1。 P0IEN(P1IEN相同):各个控制口的中断使能,0为中断禁止,1为中断使能。 P2IFG:D0~D4为P2_0~P2_4的中断标志位D5为USD D+中断状态标志,当D+线有一个中断请求未决时设置该标志,用于检测USB挂起状态下的USB恢复事件。当USB控制器没有挂起时不设置该标志。 P2IEN:D0~D4控制P2_0~P2_4的中断使能 D5控制USB D+的中断使能

PICTL:D0~D3设置各个端口的中断触发方式,0为上升沿触发,1为下降沿触发。 D7控制I/O引脚在输出模式下的驱动能力。选择输出驱动能力增强来补偿引脚DVDD的低I/O电压,确保在较 低的电压下的驱动能力和较高电压下相同。0为最小驱动能力增强。1为最大 IEN0:中断使能0,0为中断禁止,1为中断使能 IEN1:中断使能1,0为中断禁止,1为中断使能

一、中断 (2) 1、中断优先级控制IP (2) 2、中断请求控制标志TCON (2) 3、中断允许控制IE (3) 4、写中断函数(不用在main函数前声明): (3) 二、定时器 (4) 1、工作方式寄存器TMOD:写程序时选择定时器和工作方式(设置M0、M1)。 (4) 2、对定时器装初值: (4) 3、设置中断: (4) 4、启动定时器控制寄存器: (4) 5、写中断函数(不用再main函数前声明): (5) 6、注意:中断函数中的功能程序代码的执行时间不要超过定时时间。 (5) 三、串行接口 (6) 1、将TMOD设置成定时器1,工作方式为2 (6) 2、计算T1的初值:TH1和TL1的值相同: (6) 3、启动定时器T1(对TCON设置):TR1=1; (6) 4、确定串行口控制SCON: (6) 5、串行口工作在中断方式时,进行中断设置: (6) 6、写中断函数。 (6) 串口补充:波特率的计算: (6)

一、中断 中断涉及到的寄存器和写程序时的操作顺序: 1、中断优先级控制IP IP的每一位需用程序置一,某个控制位置一,相应得中断源就设定为高级中断。 同一优先级中的中断申请不止一个时,则有中断优先权排队问题。同一优先级的中断优先权排队,由中断系统硬件确定的自然优先级形成,其排列如所示: 2、中断请求控制标志TCON IT0(TCON.0),外部中断0触发方式控制位。 当IT0=0时,为电平触发方式,P3.2引脚低电平有效。 当IT0=1时,为边沿触发方式,P3.2引脚下降沿有效。 IE0(TCON.1),外部中断0中断请求标志位。单片机硬件自动置位和自动清零,不用编写在程序中。 IT1(TCON.2),外部中断1触发方式控制位。 当IT0=0时,为电平触发方式,P3.3引脚低电平有效。 当IT0=1时,为边沿触发方式,P3.3引脚下降沿有效。

51系列单片机特殊功能寄存器总结 第一节:片内RAM映射: 51:00H_7FH 128B片内(DATA),其中00H-07H: bank0,08H-0FH: bank1, 10H-17H: bank2,18H-1FH:bank3. 20H-2FH: 位寻址区(bdata) 30H-7FH: 堆栈区。 80H-FFH: SFR区 52:增加了80H-FFH间接寻址的片内RAM(IDATA) 第二节:特殊功能寄存器(51) ①TCON,地址:88H,定时器计数器控制,中断控制 IT0/1:外部中断触发方式控制,置0,为低电平触发,置1,为下降沿触发。每个机器周期的S5P2器件多外部触发采样。响应中断需要两个机器 周期。 IE0/1:外部中断请求标志,CPU响应中断后,硬件自动将IE清0 TFx,定时器Tx溢出标志,计数溢出时,硬件将其置位,响应中断后,硬件将其清0,该位可由程序查询。 TRx, 定时器x运行控制,置1则启动定时器,清0则停止定时器。 ②TMOD,地址:89H, 定时器计数器工作方式控制 counter对外部输入外冲计数,计一次数需要两个机器周期。 GATE: 取反后与外部中断输入或运算后再同TCON的TRx位相与控制计数器的启与停,GATE为0时,允许TRx开启或停止计数器,为1时,允许INTx开启或停止计数器。 ③TL0, 地址:8AH, 定时器0低八位 ④TL1, 地址:8BH, 定时器1低八位

⑤TH0, 地址:8CH, 定时器0高八位 ⑥TH1, 地址:8DH, 定时器1高八位1 ⑦SCON, 地址:98H,串行通信控制寄存器 S M2:方式2和方式3的多机通信控制位,在方式0中,SM2应置0。 REN:允许串行接收位,由软件置1时,允许接收,清0时。禁止接收 TB8:方式2和方式3中,发送的第9位数据,需要时由软件置位或复位。 RB8: 方式2和方式3中,接收到的第9位数据,在方式1时,RB是接收到停止位,在方式0时,不使用RB8. TI:接收中断标志,由硬件置1,在方式0时,串行发送到第8位结束时置1;在其他方式,串行口发送停止位时置1。TI必须由软件清0。 RI:接收中断标志,由硬件置1。在方式0时(SM2应置0),接收到第8位结束时置1,当SM2=0的其他方式(方式0,1,3)时,接收到停止位置位“1”,当SM2=1时,若串口工作在方式2和3,接收到的第9位数据(RB8)为1时,才激活RI。在方式1时,只有接收到有效的停止位时才会激活RI。RI必须由软件清0 ⑧SBUF, 地址:99H,串行通信数据缓冲器 ⑨IE, 地址:A8H,中断使能控制寄存器 EA: globle interuption Enable, 1: Enable, 0: Disable ET2: timers2 flowover interuption Enable for52, 1: Enable, 0: Disable ES: serrial port interuption Enable, 1: Enable, 0: Disable ET1/0: timers1/0 flowover interuption Enable, 1: Enable, 0: Disable EX1/0: external interuption Enable, 1: Enable, 0: Disable

一、数据在存储器中的存储方式 1、数据格式及要求 A〉数据格式:即指数据的长度和表示方式。B〉要求:S7-200对数据的格式有一定的要求,指令与数据之间的格式一致才能正常工作。 2、用一位二进制数表示开关量 A〉一位二进制数:一位二进制数有0(OFF)和1(ON)两种不同的取值,分别对应于开关量(或数字量)的两种不同的状态。B〉位数据的数据类型:布尔(Bool)型。C〉位地址:由存储器标识符、字节地址和位号组成,如I3.4等。D〉其它CPU存储区的地址格式:由存储器标识符和起始字节号(一般取藕字节)组成,如V B 100、V W 100、V D 100等。 3、多位二进制数(8421码) A〉数及数制:数用于表示一个量的具体大小。根据计数方式的不同,有十进制(D)、二进制(B)、十六进制(H)和八进制等不同的计数方式。B〉二进制数的表示:在S7-200中用2#来表示二进制常数,例如“2# 10111010 ”。C〉二进制数的大小:将二进制数的各位(从右往左第n位)乘以对应的位权(×2n-1),并将结果累加求和可得其大小。例如:2# 10111010 = 1×27+0×26+1×25+1×24+1×23+0×22+1×21+0×20 = 186 4、十六进制数 A〉十六进制数的引入:将二进制数从右往左每4位用一个十六进制数表示,可以实现对多位二进制数的快速准确的读写。B〉不同进制数的表示方法:( 表3-2-1 不同进制数的表示方 法) C〉十六进制数的表示:在S7-200中用16#来表示十六进制常数,例如“2# 1010 1110 0111 0101 可转换为16# AEF7 ”。D〉十六进制数的大小:将十六进制数的各位(从右往左第n位)乘以对应的位权(×16n-1),并将结果累加求和可得其大小。例如:16# 2F = 2×161+15×160 = 47 5、数据长度:字节(Byte)、字(Word)、双字(DoubleWord) A〉字节(B):从0号位开始的连续8位二进制数称为一个字节。B〉字(W):相邻的两个字节组成一个字的长度。C〉双字(DW):相邻的四个字节组成一个双字的长度。D〉字、双字长数据的存储特点:高位存低字节、地位存于高字节。 6、负数(有符号数)的表示方法 A〉负数的表示:PLC一般用二进制的补码来表示有符号数,其最高位为符号位(0 ——正数、1 ——负数)。B〉绝对值相等的正负有符号数间的关系:正数的补码是它本身。C〉不同数据的取值范围:( 表3-2-2 数据的位数与取值范围) 7、BCD码

成绩:实验报告 课程名称:计算机组成原理 实验项目:寄存器的原理及操作 姓名: 专业:计算机科学与技术 班级: 学号:

计算机科学与技术学院 实验教学中心 20 16年6月20日

实验项目名称:寄存器的原理及操作 一、实验目的 1.了解模型机中 A, W 寄存器结构、工作原理及其控制方法。 2.了解模型机中寄存器组 R0..R3 结构、工作原理及其控制方法。 3.了解模型机中地址寄存器 MAR,堆栈寄存器 ST,输出寄存器 OUT寄存器结构、工作原理及其控 制方法。 二、实验内容 1、A、W寄存器:利用 COP2000实验仪上的K16..K23 开关做为DBUS的数据,其它开关做为控制信号, 将数据写入寄存器A, W。 2、R0、R1、R2、R3 寄存器实验:利用COP2000实验仪上的K16..K23 开关做为DBUS的数据,其它开 关做为控制信号,对数据寄存器组R0..R3 进行读写。 3、MAR、ST、OUT寄存器:利用COP2000实验仪上的K16..K23 开关做为DBUS的数据,其它开关做为 控制信号,将数据写入地址寄存器MAR,堆栈寄存器ST,输出寄存器OUT。 三、实验用设备仪器及材料 伟福 COP2000 系列计算机组成原理实验系统 四、实验原理及接线 实验 1:A,W 寄存器实验

实验 2 :R0,R1, R2,R3寄存器实验

MAR为存储器地址寄存器,其功能是存储操作数在内存中的地址,信号MAREN的功能是将数据总线DBUS上数据 MAR,信号 MAROE的功能是将MAR的值送到地址总线ABUS上 ST 堆栈寄存器的作用,是出现中断或子程序调用时,保存断点处PC 的值,以便中断或子程序结束时, 能继续执行原程序。图中,信号STEN的作用是将数据总线DBUS上数据存入堆栈寄存器ST 中

单片机涉及寄存器知识点汇总 第六章两个串口寄存器 1:串行口控制寄存器SCON(98H) 按位解释: (1)SM0、SM1——串行口4种工作方式的选择位 SM0 SM1 方式功能说明 0 0 0 同步移位寄存器方式(用于扩展I/O口) 0 1 1 8位异步收发,波特率可变(由定时器控制) 1 0 2 9位异步收发,波特率为fosc/64或fosc/32 1 1 3 9位异步收发,波特率可变(由定时器控制)(2)SM 2 ——多机通信控制位 在方式二,三情况下:SM2=0,不管第九位是啥,RI=1,产生中断;SM2=1,第九位为1,才产生中断,为0,舍弃前八位。 (3)REN——允许串行接收位 REN=1 允许串行口接收数据。 REN=0 禁止串行口接收数据。 由软件置“1”或清“0” (4)TB8,发送第九位,方式2,3中可作为奇偶校验位或者识别地址帧或数据帧的标志。

(5)RB8,接收的第九位,适用于方式二和方式三。方式一中若SM2=0,RB8接收到的是停止位。 (6)TI——发送中断标志位 方式0时,串行发送第8位数据结束时由硬件置“1”, 其它工作方式,串行口发送停止位的开始时置“1”。 TI=1,表示一帧数据发送结束,可申请中断。CPU响应中断后, 向SBUF写入要发送的下一帧数据。 TI必须由软件清0。 (7)RI——接收中断标志位 方式0时,接收完第8位数据时,RI由硬件置1。 其它工作方式,串行接收到停止位时,该位置“1”。 RI=1,表示一帧数据接收完毕,并申请中断。 RI必须由软件清“0”。 2、特殊功能寄存器PCON (87H) 就一个波特率选择位。 3:四种工作方式

符号 地址功能介绍 B F0H B寄存器 ACC E0H 累加器 PSW D0H 程序状态字 IP B8H 中断优先级控制寄存器 P3 B0H P3口锁存器 IE A8H 中断允许控制寄存器 P2 A0H P2口锁存器 SBUF 99H 串行口锁存器 SCON 98H 串行口控制寄存器 P1 90H P1口锁存器 TH1 8DH 定时器/计数器1(高8位)TH0 8CH 定时器/计数器1(低8位)TL1 8BH 定时器/计数器0(高8位)TL0 8AH 定时器/计数器0(低8位) TMOD 89H 定时器/计数器方式控制寄存器 TCON 88H 定时器/计数器控制寄存器 DPTR 82H 83H 83H数据地址指针(高8位) PC SP 81H 堆栈指针 P0 80H P0口锁存器 PCON 87H 电源控制寄存器 、PSW-----程序状态字。 D7D6D5D4D3D2D1D0 CY AC F0 RS1 RS0 OV P 下面我们逐一介绍各位的用途 CY:进位标志。 AC:辅助进、借位(高半字节与低半字节间的进、借位)。 F0:用户标志位,由用户(编程人员)决定什么时候用,什么时候不用。 RS1、RS0:工作寄存器组选择位。这个我们已知了。 0V:溢出标志位。运算结果按补码运算理解。有溢出,OV=1;无溢出,OV=0。什么是溢出我们后面的章节会讲到。

P :奇偶校验位:它用来表示ALU 运算结果中二进制数位“1”的个数的奇偶性。若为奇数,则P=1,否则为0。 运算结果有奇数个1,P =1;运算结果有偶数个1,P =0。 例:某运算结果是78H (01111000),显然1的个数为偶数,所以P=0。 定时/计数器寄存器 1.工作方式寄存器TMOD(P134) TMOD 为T0.T1的工作方式寄存器,其各位的格式如下:TMOD D7 D6 D 5 D4 D3 D2 D1 D0 GATE C/-T M1 M0 GATE C/-T M1 M0 定时器1 定时器0 位7 GATE ——T1的门控位。 当GATE=0时,只要控制TR1置1,即可启动定时器T1开始工作; 当GATE=1时,除需要将TR1置1外,还要使INT1引脚为高电平,才能启动相应的定时器开始工作。 位6 C/—T ——T1的功能选择位。 当C/—T=0时,T1为定时器方式; 当C/—T=0时,T1为计数器方式; 位5和位4 M1和M0——T1的方式选择位。 由这两位的组合可以定义T1的3种工作方式 定时器T1工作方式选择表 如右表: 位3 GATE ——T0的门控位。 当GATE=0时,只要控制TR0置1,即可启动定时器T0开始工作; 当GATE=1时,除需要将TR0置1外,还要使INT0引脚为高电平,才能启动相应的定时器开始工作。 位2 C/T ——T1的功能选择位。 当C/—T=0时,T0为定时器方式; 当C/—T=0时,T0为计数器方式; 位1和位0 M1和M0—T0的方式选择位。 由这两位的组合可以定义T1的3种工作方式 定时器T0工作方式选择表 TMOD 不能进行位寻址,只能用字节传送指令设置定时器工作方式,低半节定义定时器0,高半字节定义定时器1。复位时,TMOD 所有位均为0,定时器处于停止工作状态。 定时/计数器控制寄存器中断请求标志寄存器TCON(P183) TCON 的作用是控制定时器的启/停,标志定时器的溢出和中断情况。定时器控制寄存器TCON 各位格式如下:TCON(88H) 8FH 8EH 8DH 8CH 8BH 8AH 89H 88H TF1 TR1 TF0 TR0 IE1 IT1 IE0 IT0 当有中断源发出请求时,有硬件将相应的中断标志位置 1.在中断请求被响应前,相应中断标志位被锁存在特殊功能寄存器TCON 或SCON 中。 TCON 为定时器T0和T1的控制寄存器,同时也锁住T0和T1的溢出中断标志及外部中断——INT0和— M1 M0 工作方式 功能描述 0 0 方式0 13位计数器 0 1 方式1 16位计数器 1 0 方式 2 自动再装入8位计数器 1 1 方式3 定时器1:停止计数 M1 M0 工作方式 功能描述 0 0 方式0 13位计数器 0 1 方式1 16位计数器 1 0 方式 2 自动再装入8位计数器 1 1 方式3 定时器0:分成2个8位计数器

详细分析MCS-51单片机内部数据存储器RAM 8051单片机的内部RAM共有256个单元,通常把这256个单元按其功能划分为两部分:低128单元(单元地址00H~7FH)和高128单元(单元地址80H~FFH)。如图所示为低128单元的配置图。 寄存器区 8051共有4组寄存器,每组8个寄存单元(各为8),各组都以R0~R7作寄存单元编号。寄存器常用于存放操作数中间结果等。由于它们的功能及使用不作预先规定,因此称之为通用寄存器,有时也叫工作寄存器。4组通用寄存器占据内部RAM的00H~1FH单元地址。 在任一时刻,CPU只能使用其中的一组寄存器,并且把正在使用的那组寄存器称之为当前寄存器组。到底是哪一组,由程序状态字寄存器PSW中RS1、RS0位的状态组合来决定。通用寄存器为CPU提供了就近存储数据的便利,有利于提高单片机的运算速度。此外,使用通用寄存器还能提高程序编制的灵活性,因此,在单片机的应用编程中应充分利用这些寄存器,以简化程序设计,提高程序运行速度。 位寻址区 内部RAM的20H~2FH单元,既可作为一般RAM单元使用,进行字节操作,也可以对单元中每一位进行位操作,因此把该区称之为位寻址区。位寻址区共有16个RAM单元,计128位,地址为00H~7FH。MCS-51具有布尔处理机功能,这个位寻址区可以构成布尔处理机的存储空间。这种位寻址能力是MCS-51的一个重要特点。 用户RAM区 在内部RAM低128单元中,通用寄存器占去32个单元,位寻址区占去16个单元,剩下80个单元,这就是供用户使用的一般RAM区,其单元地址为30H~7FH。对用户RAM 区的使用没有任何规定或限制,但在一般应用中常把堆栈开辟在此区中。 内部数据存储器高128单元

1) 芯片的振荡模式选择。 2) 片内看门狗的启动。 3) 上电复位延时定时器PWRT的启用。 4) 低电压检测复位BOR模块的启用。 5) 代码保护。 __CONFIG_CP_OFF &_WDT_OFF &_BODEN_OFF &_PWRTE_ON &_XT_OSC &_WRT_OFF &_LVP_OFF &_CPD_OFF ; _CP_OFF 代码保护关闭 _WDT_OFF 看门狗关闭 _BODEN_OFF _PWRTE_ON 上电延时定时器打开 _XT_OSC XT振荡模式 _WRT_OFF 禁止Flash程序空间写操作 _LVP_OFF 禁止低电压编程 _CPD_OFF EEPROM数据读保护关闭 LVP Low Voltage Program 低电压编程 CP Code Protect 代码保护 Date EE Read Protect EEPROM数据读保护 Brown Out Detect Power Up Timer Watchdog Timer Flash Program Write 外部时钟输入(HS,XT或LP OSC配置)如下图: 陶瓷(ceramic)谐振器电容的选择如下表:

一般情况为:11 1111 0011 0001 0x3F31 或0x3F71 位13 CP:闪存程序存储器代码保护位1 1=代码保护关闭 0=所有程序存储器代码保护 位12 未定义:读此位为1 1 位11 DEBUG:在线调试器模式位1 1=禁止在线调试器,RB6和RB7是通用I / O引脚 0=在线调试功能开启,RB6和RB7专用于调试 位10:9 WRT1:WRT0:闪存程序存储器的写使能位11 PIC16F876A / 877A 11=写保护关闭,所有的程序存储器可能被写入由EECON控制 10=0000h-00FFh写保护,0100h-1FFFh写入由EECON控制 01=0000h-07FFh写保护,0800h-1FFFh写入由EECON控制 00=0000h-0FFFh写保护,1000h-1FFFh写入由EECON控制 位8 CPD:数据EEPROM存储器代码保护位(Code Protection bit) 1 1=数据EEPROM存储器代码保护关闭 0=数据EEPROM存储器代码保护功能开启 位7 LVP:低电压(单电源)在线串行编程使能位(Low V oltage Program) 0 1=RB3/PGM引脚有PGM功能,低电压编程启用 0=RB3是数字I / O 引脚,HV(高电压13V左右) 加到MCLR必须用于编程 位6 BOREN:欠压复位使能位(低电压检测复位)(Brown-out Reset(Detect)) 0 1=低电压检测复位BOR(BOD)模块启用 0=低电压检测复位BOR(BOD)模块关闭 位5:4 未定义:读此两位均为1 11 位3 PWRTEN:上电定时器使能位(上电复位延时定时器)(Power-up Timer) 0 1=上电定时器关闭 0=上电定时器开启 位2 WDT:看门狗定时器使能位0晶体振荡器电容的选择 1=看门狗开启如右图: 0=看门狗关闭 位1:0 Fosc1:Fosc0:振荡器选择位01 11=RC振荡器 10=晶体振荡器HS模式。参考振荡频率范围:>2 MHz 01=晶体振荡器XT模式。参考振荡频率范围:100 kHz ~ 4 MHz 00=晶体振荡器LP模式。参考振荡频率范围:<200 kHz

51单片机特殊功能寄存器功能一览表 21个特殊功能寄存器(52系列是26个)不连续地分布在128个字节的SFR存储空间中,地址空间为80H-FFH,在这片SFR空间中,包含有128个位地址空间,地址也是80H-FFH,但只有83个有效位地址,可对11个特殊功能寄存器的某些位作位寻址操作(这里介绍一个技巧:其地址能被8整除的都可以位寻址)。 在51单片机内部有一个CPU用来运算、控制,有四个并行I/O口,分别是P0、P1、P2、P3,有ROM,用来存放程序,有RAM,用来存放中间结果,此外还有定时/计数器,串行I/O口,中断系统,以及一个内部的时钟电路。在单片机中有一些独立的存储单元是用来控制这些器件的,被称之为特殊功能寄存器(SFR)。这样的特殊功能寄存器51单片机共有21个并且都是可寻址的列表如下(其中带*号的为52系列所增加的特殊功能寄存器):

分别说明如下: 1、ACC---是累加器,通常用A表示 这是个什么东西,可不能从名字上理解,它是一个寄存器,而不是一个做加法的东西,为什么给它这么一个名字呢?或许是因为在运算器做运算时其中一个数一定是在ACC中的缘故吧。它的名字特殊,身份也特殊,稍后在中篇中我们将学到指令,可以发现,所有的运算类指令都离不开它。自身带有全零标志Z,若A=0则Z=1;若A≠0则z=0。该标志常用作程序分枝转移的判断条件。 2、B--一个寄存器 在做乘、除法时放乘数或除数,不做乘除法时,随你怎么用。 3、PSW-----程序状态字。 这是一个很重要的东西,里面放了CPU工作时的很多状态,借此,我们可以了解CPU的当前状态,并作出相应的处理。它的各位功能请看下表: 下面我们逐一介绍各位的用途 CY:进位标志。 8051中的运算器是一种8位的运算器,我们知道,8位运算器只能表示到0-255,如果做加法的话,两数相加可能会超过255,这样最高位就会丢失,造成运算的错误,怎么办?最高位就进到这里来。这样就没事了。有进、借位,CY=1;无进、借位,CY =0 例:78H+97H(01111000+10010111) AC:辅助进、借位(高半字节与低半字节间的进、借位)。

单片机的存储器有几种?多存放何种内容和信息? 答:单片机的存储器有程序存储器ROM与数据存储器RAM两种。 这两种存储器在使用上是严格区分的,不得混用。 程序存储器存放程序指令,以及常数,表格等;而数据存储器则存放缓冲数据。 MCS-51单片机存储器的结构有哪几部分? 答:MCS-51单片机存储器的结构共有3部分: 一是程序存储器 二是内部数据存储器 三是外部数据存储器 MCS-51单片机的存储器分为哪几类? 答:MCS-51单片机的存储器可分为5类:程序存储器、内部数据存储器、特殊功能寄存器、位地址空间、外部数据存储器。 程序存储器用于存放什么内容?它可寻址的地址空间是多少? 答:程序存储器用于存放编号的程序和表格常数 程序存储器以程序计数器PC作地址指针 由于MCS-51单片机的程序计数器为16位,因此可寻直的地址为64KB。 MCS-51单片机复位后,对系统有何要求? 答:单片机复位后,程序计数器PC的内容为0000H,所以系统必须从0000H单元开始取指令来执行程序。

0000H单元是系统的起始地址,一般在该单元存放一条绝对跳转指令(LJMP) 而用户设计的主程序,则从跳转后的地址开始安放。 MCS-51单片机内部数据存储器是怎样设置的? 答:MCS-51单片机内部有128个字节的数据存储器,内部RAM编址为00H~7FH。 MCS-51对其内部的RAM存储器有很丰富的操作指令,方便了程序设计。 单片机内部数据存储器的特点是什么? 答:工作寄存器和数据存储器是统一编址的,这是单片机内部存储器的主要特点。 什么是堆栈?MCS-51单片机的堆栈怎样设置的? 答:程序设计时,往往需要一个后进先了的RAM区,以保存CPU的现场。这种后进先出的缓冲区,就称为堆栈。 MCS-51单片的堆栈原则上设在内部RAM的任意区域内。但是,一般设在31H~7FH的范围之间,栈顶的位置由栈指针SP指出。 什么是特殊功能寄存器? 答:特殊功能寄存器是用来对片内各功能模块进行管理、控制、监视的控制寄存器和状态寄存器,是一个特殊功能的RAM区。 MCS-51单片机特殊功能寄存器的作用是什么? 答:特殊功能寄存器的作用是对片内各功能模块进行管理、控制和监视。 MCS-51单片机特殊功能寄存器是怎样设置的? 答:MCS-51单片机内的I/O口锁存器、定时器、串行口缓冲器以及各种控制寄存器和状态寄存器都以特殊功能寄存器的形式出现。

单片机寄存器汇总表 Company number【1089WT-1898YT-1W8CB-9UUT-92108】

51单片机寄存器功能一览表 21个特殊功能寄存器(52系列是26个)不连续地分布在128个字节的SFR存储空间中,地址空间为80H-FFH,在这片SFR空间中,包含有128个位地址空间,地址也是80H-FFH,但只有83个有效位地址,可对11个特殊功能寄存器的某些位作位寻址操作(这里介绍一个技巧:其地址能被8整除的都可以位寻址)。 在51单片机内部有一个CPU用来运算、控制,有四个并行I/O口,分别是P0、P1、P2、P3,有ROM,用来存放程序,有RAM,用来存放中间结果,此外还有定时/计数器,串行I/O口,中断系统,以及一个内部的时钟电路。在单片机中有一些独立的存储单元是用来控制这些器件的,被称之为特殊功能寄存器(SFR)。这样的特殊功能寄存器51单片机共有21个并且都是可寻址的列表如下(其中带*号的为52系列所增加的特殊功能寄存器):

分别说明如下: 1、ACC---是累加器,通常用A表示 这是个什么东西,可不能从名字上理解,它是一个寄存器,而不是一个做加法的东西,为什么给它这么一个名字呢或许是因为在运算器做运算时其中一个数一定是在ACC中的缘故吧。它的名字特殊,身份也特殊,稍后在中篇中我们将学到指令,可以发现,所有的运算类指令都离

不开它。自身带有全零标志Z,若A=0则Z=1;若A≠0则z=0。该标志常用作程序分枝转移的判断条件。 2、B--一个寄存器 在做乘、除法时放乘数或除数,不做乘除法时,随你怎么用。 3、PSW-----程序状态字。 这是一个很重要的东西,里面放了CPU工作时的很多状态,借此,我们可以了解CPU的当前状态,并作出相应的处理。它的各位功能请看下表: 下面我们逐一介绍各位的用途 CY:进位标志。 8051中的运算器是一种8位的运算器,我们知道,8位运算器只能表示到0-255,如果做加法的话,两数相加可能会超过255,这样最高位就会丢失,造成运算的错误,怎么办最高位就进到这里来。这样就没事了。有进、借位,CY=1;无进、借位,CY=0 AC:辅助进、借位(高半字节与低半字节间的进、借位)。 例:57H+3AH(01010111+00111010)

指令类型助记符对标志寄存器的影响备注 ZF CF PF SF OF AF DF IF TF 数据传送类通用MOV 不影响标志位 交换XCHG 堆栈 操作 PUSH POP 地址 传送 LEA LDS LES 累加器 专用IN OUT XALT 标志 寄存器 LAHF SAHF 标志寄存器低八位的内容由AH的值决定CF,AF,ZF,SF,PF的值会被影响 PUSHF 不影响标志位 POPF 标志寄存器的内容由装入的具体值决定可能影响所有标志位 算术运算类加法 指令 ADD √√√√√√ ADC √√√√√√ INC √√√√√INC指令不影响CF AAA ?√???√?表示不确定或者未定义 DAA √√√√?√ 减法 指令 SUB √√√√√√ SBB √√√√√√ DEC √√√√√DEC指令不影响CF AAS ?√???√ DAS √√√√?√DAA指令不影响OF 乘法 指令 MUL ?√??√? IMUL ?√??√? AAM √?√√?? 除法 指令 DIV ??????√√此指令可能会产生中断,故影响IF,TF IDIV ??????√√同上 AAD √?√√?? 符号位 扩展 CBW 不影响标志位 CWD 不影响标志位 比较指令CMP 由计算结果确定标志位的值不会影响到DF,IF,TF 逻辑运算类单 操 作 数 逻 辑 指 求反NOT 不影响标志位 移位 SAL √√√√见 备 注 ?OF标志位只在移位次数是1时 有效,AF未定义SHL √√√√? SAR √√√√? SHR √√√√? 循环 移位 ROL √√? 循环移位指令影响OF和CF,ROR √√?

51单片机寄存器功能一览表 21个特殊功能寄存器(52系列是26个)不连续地分布在128个字节的SFR存储空间中,地址空间为80H-FFH,在这片SFR空间中,包含有128个位地址空间,地址也是80H-FFH,但只有83个有效位地址,可对11个特殊功能寄存器的某些位作位寻址操作(这里介绍一个技巧:其地址能被8整除的都可以位寻址)。 在51单片机部有一个CPU用来运算、控制,有四个并行I/O口,分别是P0、P1、P2、P3,有ROM,用来存放程序,有RAM,用来存放中间结果,此外还有定时/计数器,串行I/O 口,中断系统,以及一个部的时钟电路。在单片机中有一些独立的存储单元是用来控制这些器件的,被称之为特殊功能寄存器(SFR)。这样的特殊功能寄存器51单片机共有21个并且都是可寻址的列表如下(其中带*号的为52系列所增加的特殊功能寄存器):

分别说明如下: 1、ACC---是累加器,通常用A表示 这是个什么东西,可不能从名字上理解,它是一个寄存器,而不是一个做加法的东西,为什么给它这么一个名字呢?或许是因为在运算器做运算时其中一个数一定是在ACC中的缘故吧。它的名字特殊,身份也特殊,稍后在中篇中我们将学到指令,可以发现,所有的运算类指令都离不开它。自身带有全零标志Z,若A=0则Z=1;若A≠0则z=0。该标志常用作程序分枝转移的判断条件。 2、B--一个寄存器 在做乘、除法时放乘数或除数,不做乘除法时,随你怎么用。 3、PSW-----程序状态字。 这是一个很重要的东西,里面放了CPU工作时的很多状态,借此,我们可以了解CPU 的当前状态,并作出相应的处理。它的各位功能请看下表: 下面我们逐一介绍各位的用途 CY:进位标志。

存储器寻址方式 存储器寻址方式的操作数存放在主存储器中,用其所在主存的位置表示操作数。在这种寻址方式下,指令中给出的是有关操作数的主存地址信息。8088的存储器空间是分段管理的。程序设计时采用逻辑地址;由于段地址在默认的或用段超越前缀指定的段寄存器,所以采用偏移地址,称之为有效地址(Effective Address, EA) 1.直接寻址 在这种寻址方式下,指令中直接包含了操作数的有效地址,跟在指令操作码之后。其默认的段地址在DS段寄存器中,可以采用段超越前缀。 例将数据段中偏移地址2000H处的内存数据送至AX寄存器。 MOV AX, [2000H] 该指令中给定了有效地址2000H, 默认与数据段寄存器DS一起构成操作数所在存储单元的物理地址。 如果DS=1429H,则操作数所在的物理地址为1429H*16+2000H=16920H. 该指令的执行结果是将16920H单元的内容传送至AX寄存器,其中,高字节内容送AH寄存器,低字节内容送AL寄存器。

MOV AX, [2000H];指令代码:A1 00 20 例: 将附加段中偏移地址2000H 处的内存数据送至AX 寄存器。 MOV AX, ES:[2000H]; 指令代码:26 A1 00 20 变量指示内存的一个数据,直接引用变量就是采用直接寻址方式。变量应该在数据段进行定义,常用的变量定义伪指令DB 和DW 分别表示字节变量和字变量,例如 WV AR DW 1234H; 定义字变量WV AR ,它的初值是1234H 这样,标示符WV AR 表示具有初值1234H 的字变量,并由汇编程序为它内存分配了两个连续的字节单元。假设它在数据段偏移地址是0010H 。 例:将数据段的变量WV AR (即该变量名指示的内存单元数据)送至AX 寄存器。 MOV AX, WV AR; 指令功能: 上述指令实质就是如下指令: AX WV AR AX DS :[0010H]

EAX:累加寄存器 ECX:计数寄存器,常用于计数 EDX :数据寄存器,常用于数据传递 EBX :基址寄存器,常用于地址索引 ESP :ESP为堆栈指针,指向当前栈顶 EBP :EBP为帧指针,当前活动记录的顶部 ESI :变址寄存器,源地址指针,存储单元在段内的偏移量, EDI :变址寄存器目标地址指针 EIP :指令寄存器,存放当前指令的下一条指令的地址 ES:附加段寄存器 CS:代码段寄存器 SS:堆栈段寄存器 DS:数据段寄存器 FS:寄存器指向当前活动线程的TEB结构 000 指向SEH链指针 004 线程堆栈顶部 008 线程堆栈底部 00C SubSystemTib 010 FiberData 014 ArbitraryUserPointer 018 FS段寄存器在内存中的镜像地址 020 进程PID 024 线程ID 02C 指向线程局部存储指针 030 PEB结构地址(进程结构) 034 上个错误号 GS:全局寄存器 EFL:标志位寄存器,各标志位的含义如下图, DF:是控制标志位为方向标志,在串处理指令中控制处理信息的方向用。当DF为1时,每次操作后使变址寄存器SI和DI减小,这样就使串处理从高地址向低地址方向处理。当DF为0时相反. TF当TF被置为1时,CPU进入单步执行方式,即每执行一条指令,产生一个单步中断请求。这种方式主要用于程序的调试

ZF表示目的操作数结果为零 AF表示(AL为一个字节)相加进行到一半(低4位)有没有向另一半(高4位)进位,也可以表示是否借位(减法) PF表示为偶数 CF表示已经发生进位,也可以表示借位 操作标志位寄存器汇编指令 LAHF 标志寄存器传送,把标志装入AH. SAHF 标志寄存器传送,把AH内容装入标志寄存器. PUSHF 标志入栈. POPF 标志出栈. PUSHD 32位标志入栈. POPD 32位标志出栈. 浮点寄存器:(80位) ST0 ST1 ST2 ST3 ST4 ST5 ST6 ST7 FST :协处理器状态寄存器 FCW:浮点控制寄存器具体参考https://www.doczj.com/doc/942900743.html,/design/processor/manuals/253665.pdf MM0:多媒体指令寄存器 MM1 MM2 MM3 MM4 MM5 MM6 MM7 DR0 :调试寄存器 DR1 DR2