A Formal Semantics on Net Delay in Verilog-HDL

- 格式:pdf

- 大小:129.92 KB

- 文档页数:6

Softw Syst ModelDOI10.1007/s10270-006-0043-7S P E C I A L S E C T I O N PA P E RSupporting UML-based development of embedded systems by formal techniquesJozef Hooman·Hillel Kugler·Iulian Ober·Anjelika Votintseva·Yuri YushteinReceived:20December2005/Revised:2October2006/Accepted:9October2006©Springer-Verlag2007Abstract We describe an approach to support UML-based development of embedded systems by formal techniques.A subset of UML is extended with timing annotations and given a formal semantics.UML models are translated,via XMI,to the input format of formal tools,to allow timed and non-timed model checking and interactive theorem proving.Moreover,the Play-Engine Communicated by Dr.Susanne Graf.This work has been supported by EU-project IST33522–OMEGA“Correct Development of Real-Time Embedded Systems in UML”.For more information,seehttp://www-omega.imag.fr/.During this project,the second author was at the Weizmann Institute of Science,the third author at VERIMAG,the fourth author at OFFIS,and thefifth author at NLR.J.Hooman(B)Embedded Systems Institute,Eindhoven,The Netherlandse-mail:hooman@cs.ru.nlJ.HoomanRadboud University,Nijmegen,The NetherlandsH.KuglerNew York University,New York,NY,USAe-mail:kugler@I.OberToulouse-II University,Toulouse,Francee-mail:ober@univ-tlse2.frA.VotintsevaCT SE1Siemens AG,Munich,Germanye-mail:anjelika.votintseva@Y.YushteinCIMSOLUTIONS B.V.,Vianen,The Netherlandse-mail:yushtein@xs4all.nl tool is used to execute and analyze requirements by means of live sequence charts.We apply the approach to a part of an industrial case study,the MARS system,and report about the experiences,results and conclusions.Keywords Formal methods·UML·Embedded systems·Real-time1IntroductionWe report about our results and experiences on com-bining a number of formal techniques with UML-based development.This work has been carried out in the con-text of the EU project OMEGA(Correct Development of Real-Time Embedded systems in UML).A general aim of this project is to improve the quality of software for embedded systems by the use of formal techniques.Embedded systems typically have an intensive real-time interaction with their environment.Although UML [3]has not been designed originally for such systems,one can observe an increasing use of object-oriented tech-niques and UML in this domain.There exists a num-ber of specialized methods[43,11],a UML profile for Schedulability,Performance and Time[35]and several dedicated CASE tools(e.g.,Artisan’s Real-time Stu-dio,Rhapsody of I-Logix,Rational Rose RealTime,and Telelogic TAU).Embedded applications typically have strong require-ments on the correctness of the software.This,however, is not easy to achieve,since these applications are typi-cally highly innovative,have intricate assumptions about the behavior of their environment,and are developed quite incrementally.Hence,it is important to detect errors as soon as possible during the development pro-cess.In this paper,we address the use of formal methodsJ.Hooman et al.to improve the quality of UML-based development of embedded systems.There exists already a number of formal techniques that have been applied to UML[41,30].Early approaches to formal verification based on model check-ing UML models actually only consider single sub-languages of UML,like statecharts[29,26],and they effectively verify only a single object in isolation.The vUML tool[38]provides a predefined set of checks of invariants,e.g.,absence of deadlocks,queue overflows, and unreachability of invalid states.The specification language of[44]is the temporal logic of the underlying model checker,hence far from the level of UML.The work on model checking of xUML[46]is closest to the UVE approach described in this paper.A rich set of UML language concepts and features,like parallelism, inheritance,object creation/destruction,etc.are sup-ported by the xUML approach.But it only deals with closed systems without taking a non-deterministic envi-ronment into account.Moreover,the used requirement specification language is restricted to a set of temporal patterns and has no graphical representation.Related to the IFx tool considered in this paper for model checking real-time properties is the translation of timed UML state machines[24]to Uppaal[28].Relevant is also the work in the context of the Fujaba real-time tool suite for UML-based development on the integra-tion of Uppaal[7].To support interactive verification of untimed UML models,a development environment has been developed[45],based on the theorem prover PVS[36].A proposal for a general framework to inte-grate tools for UML and formal methods can be found in[32].However,most techniques are not coupled to CASE tools and are based on a very small subset of UML. Often,it is difficult to express timing properties con-veniently and at a sufficient level of abstraction,and assumptions about the environment can usually be expressed only by including the environment explic-itly in the model,leading to a closed system.In the OMEGA project we investigated how this situation can be improved.We mention a few important points of the OMEGA approach:a tight integration of formal tech-niques in the development process,a sufficiently large subset of UML which allows convenient modeling of embedded systems,and the combination of techniques.To be able to integrate formal techniques,we have established a coupling with commercial UML-based CASE tools by translating the standard XMI repre-sentation of a UML model into the format of formal tools,such as model checkers and theorem provers.In this way,the formal tools can be applied to a UML model that has been edited by means of any commercial UML-based CASE tool which is able to generate XMI. Although XMI is the XML standard for UML,unfor-tunately,most current UML tools use slightly different versions of XMI.In OMEGA we have concentrated on the XMI versions of Rational Rose and Rhapsody of I-Logix.The latter has been used for all experiments described in this paper.To obtain a coherent set of tools,without having to deal immediately with the full UML language,we have defined a convenient subset of UML,called the OMEGA kernel language,which is close to the core UML language described in[13].Basically,this consists of class diagrams for specifying the structure of the sys-tem,including structural relationships like generaliza-tion,association,and composition,and state machines to describe the behavior of classes.Objects may communi-cate by means of(asynchronous)signals and operations.The language has been extended with suitable prim-itives to express real-time behavior.Timing extensions have been proposed,called the OMEGA real-time pro-file for UML,based on the profile for Schedulability, Time and Performance.Details can be found in[12]. The sequence diagrams of UML have been replaced by LSCs[8]which are more expressive[25]and also have been extended with primitives to express timing[19]. LSCs can be captured by the user by means of a sepa-rate tool,the Play-Engine.Note that our work on UML was mainly based on UML1.4,since that was the stan-dard during most of our project.Because we concentrate on the core modeling capability of UML,the differences with UML2.0[34]are not very relevant.Clearly the coherence of this tool set also requires a common semantic model.Within OMEGA,this led to extensive discussions and decisions on semantic varia-tion points and unclear issues in the definition of UML. Our starting point was an operational semantics[10,9] which was especially inspired by the execution mecha-nism of Rhapsody.Whereas many formal methods requireflat state machines,this semantics also includes hierarchy and orthogonality which is convenient for modeling.This semantic model,based on labeled tran-sition systems,turned out to be convenient for the inte-gration of the commercial tool and model checking.We reformulated the semantics to make it more suit-able for interactive theorem proving.For instance,we abstracted from the pending request table for operation calls in[9]and used explicit synchronization between caller and callee.Moreover,the semantics has been defined in an incremental way,starting from a basic non-timed semantics.This has been extended with a continuous notion of time in an orthogonal way.Sim-ilarly,threads of control have been added in a modular way.More details can be found in[23],which clarifies aSupporting UML-based development of embedded systems by formal techniquesnumber of semantic questions and decisions,e.g.,con-cerning the passing of control and the dispatching of signal events.Another relevant aspect of the OMEGA approach is the combination of various formal techniques,to obtain flexible support with e.g.,various specification styles, different visualizations,the possibility to deal with both closed and open systems—with assumptions about the environment,and both automated checks and user guided verification,depending on the properties to be verified.By experimenting with various tools on indus-trial examples,the aim is to derive guidelines about when and how to use the formal techniques.In particular,we consider the support of UML-based development by the following four formal techniques:–Live Sequence Charts(LSCs),to capture specifica-tions,using the Play-Engine tool–Model checking of functional properties by means of the UVE tool–Timed model checking,using the IFx tool–Interactive verification supported by the PVS theo-rem proverMore details about these techniques will be given in Sect.3.The main aim of this paper is to describe the appli-cation of the formal techniques to UML models of an industrial case study,which has been provided by one of the industrial partners of the OMEGA project.We pres-ent the results of applying thefirst versions of the devel-oped tools to the original model,leading to an interme-diate conclusion about what had to be improved.Next the application has been remodeled and we put more emphasis on the combined application of the improved tools.In general,the emphasis of this paper is on global results,experiences with the case studies,and general conclusions.Hence,we will neither expose all features of the techniques used,nor show the full functionality of all tools.During the case study we have often used preliminary versions of the tools,and the experiments illustrate tool development within the OMEGA project. Moreover,note that the aim is not to compare the tools, which would also be difficult because they have different goals and are rather complementary.Instead,the focus is on the synergy of the approaches and the possibilities to exploit the combination of the tools.The rest of this paper is structured as follows.In Sec-tion2we introduce the industrial case study,the UML model of a part of it,and the properties to be verified for this part.Section3contains a brief introduction to the four formal techniques used,illustrated by their applica-tion to the UML model of the case study.Next,in Sect.4 we redesign the considered part of the case study,to facilitate compositional techniques and abstraction,and apply the OMEGA techniques to this new model.An evaluation of the specification and verification experi-ments is presented in Sect.5.Finally,concluding remarks can be found in Sect.6.2The MARS systemWe describe a selected part of the MARS system (Medium Altitude Reconnaissance System)from the NLR.1This system has been used as a common real-time embedded application within the OMEGA project.The system controls the operation of a reconnais-sance photo camera in an aircraft;ground survey pho-tographs are taken by the camera during theflight.To obtain high-resolution images,the MARS system coun-teracts the image quality degradation caused by the for-ward motion of the aircraft by creating a compensation motion of thefilm during thefilm exposure,based on the current aircraft altitude,ground speed,etc.The sys-tem also performs health monitoring and alarm process-ing functions.The Reconnaissance Control Unit(RCU) is responsible for the three major categories of tasks: camera andfilm exposure control,film annotation,and system health monitoring and alarm processing.In order to perform the camera andfilm-exposure control functions the RCU acquires the current altitude and velocity data from the avionics data bus of the air-craft.Based on these values it computes thefilm Frame Rate to be used and the value for the Forward Motion Compensation(FMC)signal.The computed values are sent to the trigger and exposure module via a serial link.To perform thefilm annotation functions,the RCU acquires the current navigation data(latitude,longitude and heading)as well as the time-of-day value from the avionics data bus of the aircraft.It formats the data and sends it to the annotation module via the serial link. Upon completion of each frame exposure,the camera halts thefilm and issues an annotation request to the annotation module.Upon reception of this request the annotation module provides the current annotation data to the camera to annotate the current frame.The anno-tation cycle must be completed before the next frame exposure begins.The navigation and altitude data messages are pro-vided by the corresponding subsystems of the aircraft. These data sources are independent and not synchro-1National Aerospace Laboratory,the Netherlands,http:// www.nlr.nl.J.Hooman et al.nized;they provide data with a period P of25ms and a jitter J of±5ms(i.e.data may arrive up to5ms earlier or later).Data messages may occasionally be lost due to transmission errors.The system has hard timing constraints,such as requirements on the age of data used for exposure con-trol,on the data acquisition and on processing time in order to accommodate the data rate of the avionics data bus.The system is mission-critical as it is used for medium altitude reconnaissance missions over poten-tially hostile territories.Corrupted mission results will involve unnecessary additional risks to both the air-craft and the pilot in repeated attempts to execute the mission.2.1UML model of part of the MARS systemHere we present only a small part of the complete sys-tem,namely the data bus manager which is part of the data acquisition subsystem of the MARS system;the class diagram is given in Fig.1.For simplicity,we often refer to the DatabusManager as the MARS system.The focus is on the classes ControllerMonitor and Message-Receiver in an environment represented by the classes DatabusController,altDataSource,and navDataSource. The last two actors represent the data sources for alti-tude and navigation data.The main class is the Mes-sageReceiver which processes the incoming data.The controller monitor periodically calls an operation of the bus controller to obtain its status.In case of an error the monitor will send the evControllerError signal to the message receiver.The monitor sends the evControlle-rOK signal to the receiver if the bus controller indicates that the error situation is resolved.For each class the behavior of its objects is defined by means of a state machine and methods(program text)for its so-called primitive operations.Non-primi-tive operations of a class are defined by means of its state machine(this is not used in the MARS case study).The state machine of the class DataSource,is depicted in Fig.2.It expresses that,non-deterministically,either data is sent,represented by primitive operation send-Data,or no data is transmitted.The primitive operation sendData is overridden by the subclasses altDataSource and navDataSource to generate events evAltDataMsg and evNavDataMsg,respectively.This state machine uses interval conditions on clocks to model the non-determinism introduced by the starting time and by jit-ter.All transitions here are interpreted as delayable according to the terminology of timed automata with urgency[4],meaning that once they are enabled,they will be taken before their time guard becomes false (unless they are disabled by some other discrete tran-sition).Together with usual non-Zenoness assumption, this guarantees in this example that the computation cannot get stalled in any state.The behavior of the MessageReceiver is modeled by the state machine diagram depicted in Fig.3.The speci-fication of the system expresses that a few failures from the data sources can be tolerated,but if one of theFig.1Class diagram of the data bus managerSupporting UML-based development of embedded systems by formal techniques Fig.2State machinediagram of a data sourceFig.3State machine diagram of the Message Receiversources fails to send data for three consecutive times, the receiver enters a BusError state.In state Operational failures are detected by the time-out of timers navDa-taTimer and altDataTimer.The number of consecutive failures of each data source is stored into failure coun-ters NavMsgTimeoutCount and AltMsgTimeoutCount. If one of these counters has value3,the receiver enters the bus error state(note that by the run to completion assumption adopted in UML,this will be done before accepting a new signal event).The receiver recovers from the bus error state if it receives correct data for at least two consecutive times from both data sources.In the BusError state,the coun-ters NavMsgCount and AltMsgCount are used to count consecutively accepted messages of each type.BusEr-ror is also the initial state,since the system should only be in state operational when sufficient messages have been received from both sources.State ControllerError is entered and exited based on the events received from the controller monitor.J.Hooman et al.Similarly,the behavior of the ControllerMonitor has been modeled by means of state machines.Details are not shown here,since the main focus is on the detection of failures of the data sources and the response to these failures.2.2Properties of the MARS systemDuring our verification experiments,we concentrated on the following two properties of the MARS system: 1.Timely detection of a Databus Controller error,leading to the ControllerError state of the Message Receiver,and proper recovery,i.e.returning to state BusError if the Controller is OK again.2.Timely detection of an error in the databus,basedon data message arrival monitoring,leading to state BusError,and proper recovery.These properties include timing constraints to specify maximum response times.As shown in Fig.4,for prop-erty2this can be split into two cases:–Maximal response time to errors.This is defined as the upper bound on the time R1between the moment the last message has been received froma faulty data source and the moment of the switch tostate BusError.–Maximal response time to recovery.This is defined as the upper bound on the time R2between the receipt of thefirst message in a series of correct messages and the actual moment of the switch to state Opera-tional.2.3Abstracting from real-timeOften system specifications are split into functional and non-functional(including timing)requirements.This provides an opportunity to apply non-timed modeling and verification to the functional properties.To investi-gate this on the MARS system,we have extracted a non-timed version of the message receiver by abstracting from the setting of timers to particular time-out values. In order to make message loss observable in this non-timed model,the signals evNavDataMsgTimeout and evAltDataMsgTimeout have been introduced.The data sources non-deterministically choose between sending a data message or sending a time-out event which models message loss.The state machine of the message receiver is depicted in Fig.5.3Applying OMEGA techniquesWe briefly describe the OMEGA techniques and mainly focus on the results of applying them to the MARS case study.We start with the LSCs in Sect.3.1,present func-tional and timed model checking by UVE and IFx in Sects.3.2and3.3,respectively,andfinally describe inter-active theorem proving by means of PVS in Sect.3.4.3.1LSCThe Play-Engine tool[20,21]supports the specification and execution of scenario-based requirements.The underlying language for requirement specification is that of live sequence charts(LSCs)[8].Live sequence charts are a powerful extension of the classical message sequence charts(MSCs)[48],that while retaining the intuitive spirit of MSCs,enhances their expressive power.LSCs distinguish between behaviors that may happen in the system(existential)from those that must happen(universal).Among other extensions they also allow specifying timing requirements[19]and generic properties using symbolic instances[31].The Play-Engine assumes a discrete time model and adopts the synchrony hypothesis.As mentioned above,one of the main extensions in LSCs—relative to classical MSCs—is the ability to distinguish between possible and mandatory behavior,Fig.4Response times of the message receiverSupporting UML-based development of embedded systems by formal techniquesFig.5Non-timed state machine diagram of the message receiver Fig.6High level systembehavior of camera controlJ.Hooman et al.using two types of charts.An existential chart describes a possible scenario in the system.Figure6depicts an exis-tential chart,as denoted by the dashed border,which represents a high level system behavior of the camera control.The vertical instances correspond to the partic-ipating objects—AvionicsDatabus,RCU,Exposu-reModule,Camera and the external object Control-Panel.Time progresses from top to bottom,thus the order of the events in this chart is NavData,AltDa-ta,ComputeFramerate,ComputeFMC,FrameRate, FMC,StartFilming,ActivateExposures,trig-gerExposure and FMC.In general,a scenario defines a partial order on the events appearing in the chart, where events on the same object line occur according to the visual order from top to bottom,and any given mes-sage can be received only after being sent.Since Fig.6is an existential chart,it specifies that there exists at least one run of the system which exhibits the sequence of events described above.An example of a universal chart appears in Fig.7.A universal chart contains a prechart(dashed hexagon), which specifies the scenario which,if successfully exe-cuted,forces the system to satisfy the actual chart body. In Fig.7the prechart starts with a time tick,followed by two assignments(first ADS_Time variable stores the global time,denoted by Time,and then AltSend vari-able stores the value of ADS_Time modulo the altitude data cycle AD_Cycle)and a condition which together check whether time has reached a multiple of the alti-tude data cycle AD_Cycle.If this is the case,the behav-ior specified in the main chart must follow.The main chart consists of an if-then-else construct;in this case the condition is a probabilistic choice,where with95% probability the altitude message is sent within5time units with no error and with5%probability there is an error with the altitude message.In a similar way the cyclic behavior for the navigation data is specified.The expressive power of universal charts,based on the pattern“prechart implies main chart”,forms the basis of an executable semantics for an LSC require-ment model.As a response to an external event or time progress,a prechart may be satisfied,thus triggering the system events in the main chart to be executed according to the partial order,and these events may in turn acti-vate additional universal charts.Play-out,the executable mechanism implemented in the Play-Engine tool,mon-itors progress along charts and performs system events in the main charts for universal charts that have been activated,trying to complete all universal charts suc-cessfully.As the events are being executed,their effects are visualized via a Graphical User Interface(GUI), thus providing an animation of the system behavior.The same GUI is used in an earlier stage called“play-in”to Fig.7Universal chart concerning the altitude data source capture the LSCs by demonstrating the scenarios,while the Play-Engine records the behavior in the from of an LSC,thus providing an intuitive way for capturing the scenario-based requirements.The work described here addresses the execution and the analysis of the require-ments rather then on the process of capturing them;the interested reader is referred to[20]for more informa-tion on play-in.Play-out is actually an iterative process where after each step taken by the user,the Play-Engine computes a super-step,which is a sequence of events carried out by the system as its response to the event input by the user.One of the problems with play-out in its origi-nal form is related to the inherent non-determinism allowed by the LSC language.LSCs is a declarative, inter-object language,and as such it enables formulating high level behavior in pieces(e.g.,scenario fragments), leaving open details that may depend on the implemen-tation.This non-determinism,although very useful in early requirement stages,can cause undesired under-Supporting UML-based development of embedded systems by formal techniquesspecification when one attempts to consider LSCs as the system’s executable behavior.The play-out mechanism of[20]is rather naive when faced with non-determinism, and makes essentially an arbitrary choice among the possible responses.This choice may later cause a viola-tion of the requirements,whereas by making a different choice the requirements could have been satisfied.To address this challenge,[15]introduces a more pow-erful technique for executing LSCs,called smart play-out.It takes a significant step towards removing the sources of non-determinism during execution,proceed-ing in a way that eliminates some of the dead-end exe-cutions that lead to violations.Smart play-out[15,16] uses verification methods,mainly model-checking,to execute and analyze LSCs.There are various modes in which smart play-out can work.In one of the modes, smart play-out functions as an enhanced play-out mech-anism,helping the execution to avoid deadlocks and vio-lations.In this mode,smart play-out utilizes verification techniques to run programs,rather than to verify them. In another mode,smart play-out is given an existential chart and asked if it can be satisfied without violating any of the universal charts.If it manages to satisfy the existential chart,the satisfying run is played out,provid-ing full information on the execution and reflecting the behavior via the GUI.3.1.1Results of LSC experimentsWe have specified a high-level requirements model for the MARS application using universal LSCs.To explore the behavior of the system,the model has been simu-lated using the play-out capabilities of the Play-Engine. During play-out the active charts are displayed with a line which specifies how much progress has been made by each instance,as shown in Fig.8.Existential charts were used to test and verify system behavior;they do not drive the execution,but can be traced during play-out mode(depicted by a magnifying glass containing the letter“T”in the upper left corner) showing the progress along the scenario as shown in Fig.9.Another example of an existential chart is depicted in Fig.10.In this scenario,after AltMsg(True)occurs at the BusController,the RCU sends receiveExpDa-ta to the ExposureModule.This scenario also includes a timing constraint;time is stored immediately after AltMsg(True)occurs and the timed condition speci-fies that no more than70time units should have passed before the receiveExpData is received.Being an existential chart,Fig.10implies that there is at least one run of the system satisfying this scenario.In early system design such charts serve as“sanitychecks”Fig.8Example of play-outshowing that certain desirable behavior can be exhibited by the system.The user can then run play-out mode and attempt to drive the system behavior to satisfy the chart by providing the appropriate external events.A system-atic way to check if a given existential chart can be sat-isfied by a set of universal charts is by invoking smart play-out with this query.If a satisfying run is found by smart play-out it will be displayed to the user,otherwise smart play-out proves that that it is impossible to satisfy the existential chart.The ability to prove that an exis-tential chart cannot be satisfied is an advantage of smart play-out over the“naive”play-out mechanism.We have used this capability in our model by setting existential charts to designate a scenario that should never occur (anti-scenario);if this existential chart is traced to com-pletion it indicates a problem in the design or in the specification of the universal charts.If smart play-out proves that this existential chart cannot be satisfied,we are guaranteed that this bad behavior is not allowed to occur.。

对温斯顿·丘吉尔《关于希特勒入侵苏联的演讲》的文体分析6200字本文从分析文体的角度出发对温斯顿·丘吉尔的著名演讲《关于希特勒入侵苏联的演讲》中所使用的文体手段进行了详尽的分析,引导读者赏析中大量使用的平行、重复、押韵、比喻等修辞手法是如何使演讲稿达到音、形、义的完美结合,进而对演讲文体的风格进行了简要的论述。

文体学;音位学;词汇和语法;语义学The style of writing to Winston Churchill“Speech on Hitler’sInvasion of the U.S.S.R.” is analysedLi TingThe detailed analysis the main body of a book has been carried out from angle style of writing means used by the middle starting off giving a lecture “give a lecture about that Hitler invades Soviet” to Churchillian Winston ? q famousness analysing style of writing, guides reader to award Xi paralleling in the original Da Liang Shi Yong, repeats, is in rhyme, allegory waits rhetoric gimmick has been that draft reaches the tone, the shape, righteous consummation combines how to make to give a lecture, the style of writing style has carried out brief discussion on to giving a lecture then.Stylistics; Phonemics; Vocabulary and grammar; SemanticsG89C1673-8209(2009)02-0236-02Written by Winston Churchill, Speech on Hitler’s Invasion of the U.S.S.R. is full of powerful thoughts, magnificent expressions and well-structured. At that time, the U.S.S.R. was in danger and the disaster would quickly turn to the British. The goal of this speech was to arouse British people and win the cooperation of the USA, so, this speech is persuasive as its functional tenor is concerned; so far as the personal tenor is concerned, it is formal. General features of this speech can be summarized as: this persuasive speech is the speaking of what is written to be spoken to an audience on a formal occasion, so it presents features of formal written language while exhibiting characteristics of the written mode with its highly logical organization of thoughts, closely-knit structure and formal language. Just as language is multifunctional, so style is multileveled: Stylistic features can be formed at the three distinct levels: ① The level of Phonology; ② The level of Lexis and Grammar; ③ The level of Semantics. In order to find out the items of stylistic significance in this famous speech, this paper aims at analyzing it from one level of its language to another.1 Stylistic features at the first level―phonological features.Repetition of the previous initial sound may arouse the addressees’ sensitivity to the sound quality of a text, which includes Alliteration, as in “dull, drilled, docile”, “for his hearth and home”,Assonance, as in “clanking, heel-clicking”, “cowing and tying”. Besides, when the phoneticsymbolism is concerned, explosive sounds like[b],[p],[t],[d],[g],[k]usually gives a feeling of suddenness and strength while liquids and nasals a sense of peace and harmony. Winston used a series of explosives like “dandified, dull, docile, drilled, brutish, plodding, etc.” to impress his audience with the violent aggression of the Nazi army.2 Stylistic features at the second level―grammatical and lexical features.As public speeches are intended to inform, to persuade, and to appeal, most sentences are statements, as is shown in Churchill’s speech with only one question and two commands used in the whole speech. We know that casual speech tends to use short sentences. But a glance at Churchill’s speech reveals that its sentences are mostly long and complex ones. Though there can be several clauses in a longer sentence, they mainly come after the main clause, which presents no difficulty for the audience to comprehend. There are no sentences that are incomplete or elliptical. These characteristics show the double traits of public speaking: it is formal as is required of written language, and it is yet not difficult to understand at the time of the delivery as is required of the spoken mode. Stressing the idea by using synonyms or repeating the same word impinges on the audience’s ears, adding force, clearness or balance to a sentence. Examples for this can be found in Winston’s speech, e.g. “We have but one aim and one single, irrevocable purpose.” “…for we must speak out now at once, without a day’s delay.”3 Stylistic features at the third level―semantic features.The level of semantics concentrates on how the cohesive devices, paragraphing, discourse patterning, rhetorical devices and role structures contribute to the meaning of the text as a whole. Here, we will mainly focus on the rhetorical devices used in the speech. Clear organization is vital to speech making. Persuasive speeches, especially policy speeches often fall into problem-solution order. In Churchill’s speech, he showed how serious the problem was and the real intension of the Nazi regime. After having convinced the audience, Churchill called them to act with united strength. Besides, rhetorical devices are also employed by Churchill to make his speech vivid and forceful. Parallel structures are not only even in structure, but also coherent in meaning. They function not only as a kind of rhetoric device, but as a means of coherence as well. With its repetition of the sentence structure, the theme of the speech is closely connected and clearly illustrated. With so many parallel structures, the whole speech goes on smoothly and logically. The use of many parallel structures in this speech has filled the speech with strength and clear logic, e.g. “We will never parley, we will never negotiate…” “Behind all this glare, behind all this storm…” Repetition of the same word at the beginning or end of successive clauses or sentences helps create a strong emotional effect. For example: “ Any man or state who… Any man or state who…”In conclusion, Churchill’s Speech on Hitler’s Invasion of the U.S.S.R. is very typical of public persuasive speeches, with its stylistic characteristics on semantic, grammatical, lexical and phonological levels. As an excellent combination of sound, form and meaning, this speech has no doubt made significant contributions in the history and the present.参考文献[1] 张汉熙.《高级英语》上册[M],北京:外语教学与研究出版社,1995[2]徐有志.《英语文体学教程》[M].高等教育出版社,2005[3]徐有志.《现代英语文体学》[M].开封:河南大学出版社,1992[4]秦秋白.《英语文体和文体要略》[M]. 上海:上海外语教育出版社出,2006[5]霍晓军.《从文体学角度看FROST的诗》[J]. 太原:太原教育学院学报,2004。

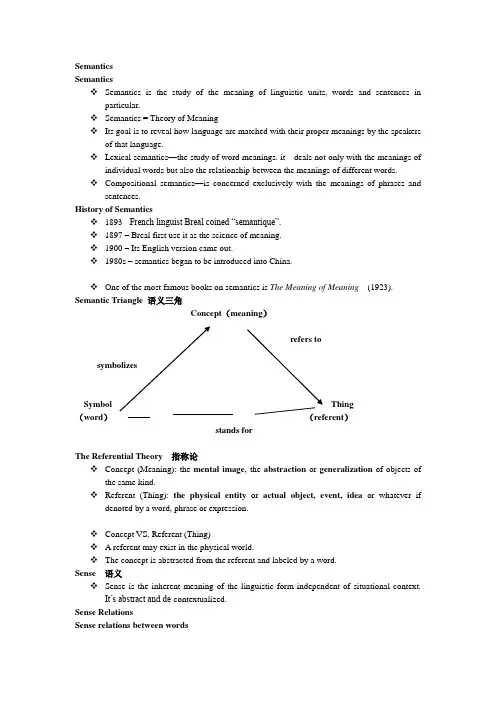

SemanticsSemanticsSemantics is the study of the meaning of linguistic units, words and sentences in particular.Semantics = Theory of MeaningIts goal is to reveal how language are matched with their proper meanings by the speakers of that language.Lexical semantics—the study of word meanings. it deals not only with the meanings of individual words but also the relationship between the meanings of different words.Compositional semantics—is concerned exclusively with the meanings of phrases and sentences.History of Semantics1893 - French linguist Breal coined ―semantique‖.1897 – Breal first use it as the science of meaning.1900 – Its English version came out.1980s – semantics began to be introduced into China.One of the most famous books on semantics is The Meaning of Meaning(1923). Semantic Triangle 语义三角Concept(meaning)refers tosymbolizesSymbol Thing(word)(referent)stands forThe Referential Theory 指称论Concept (Meaning): the mental image, the abstraction or generalization of objects of the same kind.Referent (Thing): the physical entity or actual object, event, idea or whatever if denoted by a word, phrase or expression.Concept VS. Referent (Thing)A referent may exist in the physical world.The concept is abstracted from the referent and labeled by a word.Sense 语义Sense is the inherent meaning of the linguistic form independent of situational context.It’s abstract and de-contextualized.Sense RelationsSense relations between wordsWords are in different sense relations with each other.There are generally 5 kinds of sense relations:1) synonymy 同义2) antonymy 反义3) hyponymy 上下义4) polysemy 一词多义5) homonymy 同音同形异义1. SynonymyIt is the sameness or close similarity of meaning.Words that are close in meaning are called synonyms.2. AntonymyIt is the oppositeness of meaning.Words that are opposite in meaning are antonyms.Oppositeness can be found on different dimensions:Gradable antonymyComplementary antonymyConverse antonymy (relational opposites)Gradable antonymy 分级反义词good/ bad, long /short, narrow/ wideThe members of a pair differ in terms of degree. The denial of one is not necessarily the assertion of the other. There are often intermediate forms between them.Not good≠badHot ---warm---cool---coldComplementary antonymy 互补反义词alive/ dead, male/ female, present/ absent, pass/ fail , boy/ girlIt is characterized by the feature that the denial of one member of the pair implies the assertion of the other and the assertion of one means the denial of the other.Converse antonymy 换位反义词(relational opposites关系对立反义词)buy/ sell, lend/ borrow, before /after,teacher/ student, above /belowThe members of a pair do not constitute a positive-negative opposition. They show the reversal of a relationship between two entities.ExerciseClassify the following pairs of antonyms:Gradable antonymyComplementary antonymyConverse antonymymarried-single male-female hot-coldgive-take big-small awake-asleepnorth-south logical-illogical win-losebuy-sell doctor-patient above-below3. Hyponymy上下义关系It is the sense relation between two words in which the meaning of one word is included in the meaning of another word.HyponymyMusical instruments ---piano flute guitar violin tuba tromboneFish---snapper salmon bass sole troutSalmon---chinook spring coho king sockey4. PolysemyA word is polysemic if it has more than one meaning.Wood:family treea geographical area with many trees5. HomonymyWhen two or more words are the same in pronunciation or in spelling or in both but different in meaning, they are called homonyms.3 types of homonyms:perfect homonyms(同音同形异义词)homographs(同形异义词)homophones (同音异义词).Perfect homonymsPerfect homonyms are words which are the same in both pronunciation and spelling but different in meaning.bank (银行、河岸)bear (容忍、生(孩子))sound (声音、完美的)HomographsHomographs are words which are the same in spelling, but different in pronunciation and meaning."bow" /bəʊ/ -----"弓―"bow" /bau/ -----"鞠躬"HomophonesHomophones are words which are the same in pronunciation, but different in spelling and meaning.tail / taleto / two / toopair / pearsee / seaI / eyepiece / peace。

An OCL Semantics Specified with QVTSlaviˇs a Markovi´c and Thomas Baar´Ecole Polytechnique F´e d´e rale de Lausanne(EPFL)School of Computer and Communication SciencesCH-1015Lausanne,Switzerland{slavisa.markovic,thomas.baar}@epfl.chAbstract.Metamodeling became in the last decade a widely acceptedtool to describe the(abstract)syntax of modeling languages in a con-cise,but yet precise way.For the description of the language’s semantics,the situation is less satisfactory and formal semantics definitions are stillseen as a challenge.In this paper,we propose an approach to specifythe semantics of modeling languages in a graphical way.As an example,we describe the evaluation semantics of OCL by transformation ruleswritten in the graphical formalism QVT.We believe that the graphicalformat of our OCL semantics has natural advantages with respect to un-derstandability compared to existing formalizations of OCL’s semantics.Our semantics can also be seen as a reference implementation of an OCLevaluator,because the transformation rules can be executed by any QVTcompliant transformation engine.1IntroductionModeling is an important activity in all engineering disciplines,including soft-ware development.While the general purpose modeling language UML has proven to be versatile enough for many different domains(see,e.g.,chapter 1of[1]),it has also been recognized that the structure and the behavior of the system under development can often be captured as well with a much simpler, domain-specific modeling language[2].UML and DSLs have much in common.Their abstract syntax is usually de-fined by a metamodel and UML’s core modeling concepts such as Class,Object, State,etc.can also be found,possibly under a different name,in many DSLs. If a DSL comprises a constraint language,i.e.a language to impose restrictions on the modeled system,then some core concepts of UML’s constraint language OCL such as model navigation,variable quantification and pre-defined functions are likely to be used.In this paper,we present a new approach to define the se-mantics of constraint languages formally.We illustrate our approach on a rather complex example,the semantics of OCL,but since our technique is based on gen-eral techniques such as metamodeling and model transformation,the semantics of other constraint languages can be defined in a similar way.This work was supported by Swiss National Scientific Research Fund under the reference number200020-109492/1.Before sketching existing approaches to define the semantics of OCL it isworthwhile to reflect the purpose and semantics of UML diagrams that can alsobe used without OCL constraints.A diagrammatic UML model describes thestructure and behavior of a system at a certain level of details.The structureof the system clarifies which states(in UML jargon also called snapshots)thesystem can have and the behavioral description imposes restrictions on systemchanges.The question on how a class diagram corresponds to the state spaceof the system it describes has particular relevance for our later considerations.This correspondence(or semantics)of class diagrams has been given in theliterature in many different forms,e.g.by an informal description(see UMLUser Guide[1]),by a mapping of classes into a set-theoretic domain(see[3]),bya metamodel of the semantic domain.The metamodel for the semantic domainbecame in UML1.x a part of the UML language standard because it is the basisfor object diagrams,which are used to visualize system states.The purpose of an OCL constraint is to make the already existing diagram-matic UML model more precise.For instance,a constraint attached as an invari-ant to a class shrinks the statespace to those states of the system,in which theconstraint is evaluated to true.A pair of OCL constraints(preCond,postCond)attached as pre-/postcondition to an operation op means that the implementa-tion of op can realize only those state transitions(preState,postState),for whichpostCond is evaluated in postState to true whenever preCond is evaluated inpreS to true.No matter for which purpose an OCL constraint is used(as an in-variant,as a guard,within pre-/postcondition),the semantics of the constraintcan always be reduced to the question,how the evaluation of a constraint ina given state is defined.In the literature,the evaluation function eval:Con-straint x State→{true,false,undefined}is defined either mathematically by structural induction over Constraint(see official OCL semantics,appendix Ain[4])or by embedding OCL into another logic[5].While these two approacheshave basically succeeded in describing the evaluation of OCL constraints in aformal,non-ambiguous manner,they still have some disadvantages.One draw-back is the gap between OCL’s official syntax definition(which is given as ametamodel)and the OCL syntax,given by structural induction,that is assumedin the semantics definition.The main,very related drawback,however,is under-standability.We made the experience that many of our students,who learnedOCL in our course,were quite reluctant to deepen their knowledge on OCLby reading the official mathematical semantics,just because it is presented ina format they are not very familiar with(in set theory).If the purpose of thesemantics is to inform the prospective OCL users about all the details of thelanguage,then the semantics should be given in a format OCL users are familiarwith.One technique how this can be achieved is metamodeling.Metamodels arealready frequently used in abstract syntax definitions.Metamodels are very ex-pressive and easy to understand for people who have a background in modeling(at least,these are our personal experiences we made with students).As men-tioned above,metamodeling has already been applied to cover also the semanticsof class diagrams.Even more,the section’Semantics Described using UML’in [4]presents already a metamodeling approach for the evaluation of OCL ex-pressions.We took this approach as a starting point but added some impor-tant improvements.The most striking difference is how the evaluation process is modeled:In[4],evaluation is modeled by Evaluation-metaclasses whereas in our approach this is described by transformation rules written in QVT.We also changed the metamodel of the semantic domain significantly for many reasons; one was to have a better representation of predefined datatypes.Our approach has been implemented using the QVT engine provided by Together Architect for Eclipse.To summarize,our semantics of OCL is specified with a metamodeling ap-proach using MOF,OCL and QVT as a formalism at the metalevel.Since QVT depends also heavily on OCL,there is the natural question if our approach does not describe the OCL semantics in terms of OCL and thus has fallen into the trap of meta-circularity.We have avoided this trap because the semantics of the OCL used at the metalevel is given by an external mechanism,in our case by the semantics implemented by the QVT engine of Together Architect.The de-pendency of our semantics definition on a tool implementation might be seen as a drawback but for the purpose of our semantics–to help OCL users to deepen their knowledge on the peculiarities of OCL evaluation–this is not really an ing a tool as an’anchor’for our OCL semantics has also signifi-cant advantages such as automatic tool support(note that our OCL semantics is fully executable by QVT engines)andflexibility(users can easily adapt the OCL semantics to their needs).The rest of the paper is organized as follows.In Sect.2,we sketch our ap-proach and show,by way of illustration,a concrete application scenario for our semantics.The steps the evaluator actually has to perform are formalized as graphical QVT rules in Sect.3.Section4contains related work,while Sect.5 draws some conclusion and points to problems,which we plan to address in the near future.2Our Metamodel Based Approach for OCL Evaluation In this section we briefly review the technique and concepts our approach relies on and illustrate with a simple example the evaluation of OCL constraints.2.1Official Metamodels for UML/OCLWe base our semantics for OCL on the official metamodels for UML and OCL. We support the lastfinalized version of OCL2.0[4]but since this version still refers to UML1.5[6]we were forced to support UML1.5instead of UML2.0. Figures1and2show the parts of the UML and OCL metamodels that are relevant for this paper.Please note that Fig.1contains also in its upper part a metamodel of the semantic domain of class diagrams.In add of3). thethe, it possible to clearly distinguish a datatype object from its value.Fig.3.Changed Metamodel for OCL -SemanticsStock inv :.capacity>self .numOfItemsFig.4.Example -Class Diagram and Snapshot2.3We example.In Fig.4,a shown.The model numOfItems ,both of number of items it class Stockrequires be smaller than the satisfies the attached invariant because for each instance of Stock (class Stock has only one(a)(b)(c)(d)Fig.5.Evaluation of OCL expressions seen as an AST:(a)Initial AST (b)Leaf nodes evaluated (c)Middle nodes evaluated (d)Complete AST evaluatedthat in this example we were not concerned about concrete binding of the self variable.The problem of variable binding is discussed in Sect.2.4.The initial idea of our approach is that an OCL constraint can be analogously evaluated by annotating directly the OCL metamodel instance instead of the AST.SnapshotFig.6.OCL Constraint Before Evaluationfrom Fig.yetbecause The been finished state(Fig.6)(Op-,thetwo 7and 3,Fig.7.OCL Constraint After Evaluation in a Given Snapshot variables to current values.The binding of variables is realized in the OCL meta-model by the class NameValueBinding,which maps one free variable name to one value.Every OCL expression can have arbitrarily many bindings,the only restriction is the uniqueness of variable names within the set of linked NameVal-ueBinding instances.In the invariant of the Stock example we have used one free variable self. Although self is a predefined variable in OCL,it can be treated the same way as all other variables,which are introduced in Iterator Expressions.For example, the invariants e l f.c a p a c i t y>s e l f.numOfItemscan be rewritten asStock.a l l I n s t a n c e s−>f o r A l l(s e l f|s e l f.cap acity>s e l f.numOfItems)The binding of variables is done in a top-down approach.In other words, variable bindings are passed from an expression to all its sub-expressions.Some expressions do not only pass the current bindings,but also add/change bindings. An example for adding new value-name bindings will be explained in more details in Sect.3where the evaluation rules for forAll expressions are explained.Figure8shows the process of binding passing on a concrete example.In the upper part,the initial situation is given:The top-expression already has one binding nvb for variable self.In the lower part of thefigure,all subexpressions of the top-expression are bound to the same NameValueBinding as the top-expression.3Evaluation Rules Formalized in QVTThe previous section has shown the main idea of our approach:we annotate all intermediate results of a constraint evaluation directly to the instance of the OCL metamodel.What has not been specified yet are the evaluation steps themselves,Fig.8.Binding Passingfor example,that an AttributeCallExp is always evaluated to the attribute value on that object to which the source expression of AttributeCallExp evaluates.In this section,we specify these evaluation steps formally in form of QVT rules.These rules are minimal in the sense that they do not capture any opti-mization for an efficient evaluation nor impose any restrictions on the evaluation ordering,unless they are really necessary.3.1QVTQVT is a recent OMG standard for model transformations(see[8]for a detailed account on QVT’s semantics),which are described by a set of transformation rules.For our application scenario of QVT rules,source and target model are al-ways instances of the same metamodel;the metamodel for UML/OCL including the small changes we have proposed in Sect.2.Each QVT rule consists of two patterns(LHS,RHS),which are(incomplete)instantiations of the UML/OCL metamodel.When a QVT rule is applied on a given source model,a LHS match-ing sub model of the source model is searched.Then,the target model is obtained by rewriting the matching sub model by a new sub model that is derived from RHS under the same matching.If more than one QVT rule match on a given source model,one of them is non-deterministically applied.The model transfor-mation terminates as soon as none of the QVT rules is applicable on the current model.3.2A Catalog of RulesTo specify the evaluation process,we have to formalize for each non-abstract subclass of metaclass OclExpression one or more QVT rules.Due to space limit, only the most important rules can be presented in this subsection.In order to give a representative selection of our rules,we categorized them according to the kind of expression they target:Navigation Expressions,OCL PredefinedOperations ,Iterator Expressions ,and Atomic Expressions .For each category,we discuss one or two rules in detail.The main goal is to demonstrate that the evaluation of all kinds of OCL expressions can be formulated using QVT in an intuitive way.Navigation Expressions OCL expressions of this category are instances of AttributeCallExp and AssociationEndCallExp .Such expressions are evaluated by ’navigating’from the object,to which the source expression is evaluated,to that element in the object diagram,which is referenced by the attribute or asso-ciation end.Before the source expression can be evaluated,the current binding of variables has to be passed from the parent expression to the sub expression.We show in Fig.9how the binding rule is defined for AttributeCallExp .When applying this rule,the binding of the parent object ace (represented by a link from ace to the multiobject nvb in LHS)is passed to subexpression o (a link from o to nvb is established in RHS).Analogous rules exist for all other kinds of OCL expressions which have subexpressions.For the (subclasses of)LoopExp (see below)one needs also additional rules for handling the binding because the subexpressions are evaluated under a different binding than the parent expres-sion.Fig.9.Attribute Call Expression Bindings Passingrule d ,in two state on which the evaluation is performed.Since the evaluation of OCL rules does not have any side-effect on the system state,the lower parts of LHS and RHS will always coincide.AssociationEndCallExp We discuss here only the case of navigating to an unordered association end with multiplicity greater than 1(the case of multi-plicities equal to 1is very similar to AttributeCallExp ).The rule shown in Fig.11Fig.10.Attribute Call Expression Evaluationspecifies that the value of aece is a newly created object of type SetTypeValue whose elements refer to all objects o2that can be reached from object o via a link for ae .Again,object o is the evaluation of source expression oe .The rule shown in Fig.11contains at few locations the multiplicities 1-1at the link between two multiobjects,for example at the link between le2and l .This is an enrichment of the official QVT semantics on links between two multiobjects.Standard QVTinFig.11.Association End Call Expression Evaluation that Results in Set of ObjectsOCL Predefined Operations Expressions from this category are instances of the metaclass OperationCallExp but the called operation is a predefined one, such as+,=.These operations are declared and informally explained in the chapter on the OCL library in[4].As an example,we explain in the following theFig.13.Equal Operation Evaluation for IntegersFig.14.ForAll-Evaluation RulesIterator Expressions Iterator expressions are those in OCL which have as the main operator one from select,reject,forAll,iterate,exists,collect or isUnique.Since all these expressions can be expressed by macros based on iterate,it would be sufficient to refer for their semantics just to the semantics of iterate.We show here nevertheless a semantics for forAll,that is independent from the semantics of iterate.The rules describing the semantics of forAll are, compared with iterate,easier to understand,but contain already all mecha-nisms needed to describe iterate(see Fig.14).The rule ForAll-Initialisation makes a copy of evaluation of the source ex-pression,and assigns it under the role current to ie.Furthermore,the role intermediateResult is initialized with true and,for some technical reasons,the attribute freshBinding of ie is set to false and the evaluation of body expression oe is also initialized with true.The rule ForAll-IteratorBinding updates the binding on body expression oe for the iterator variable v with a new value vp.The element with the same value vp is chosen from the collection current and is removed afterwards from this collection.The attribute freshBinding is set to true and the evaluation of body expression oe is removed(note that the binding for oe has changed and the old evaluation of oe became obsolete).The rule ForAll-IntermediateEvaluation updates the intermediateResult of ie based on the new evaluation of oe.Furthermore,the value of attribute fresh-Binding isflipped.Thefinal rule ForAll-evaluation covers the case when the collection current of ie is empty.In this case the value of ie is set to that value which intermedi-ateResult currently has.Atomic Expressions This category consists of expressions such as LiteralExp and VariableExp that do not have any subexpressions.As an example we present rules for these two cases.In Fig.15,the evaluation of IntegerLiteralExp is shown. By applying this rule,a new IntegerValue is created that refers to the same integer as attribute integerSymbol in ie.Note,that this type of expressions does not need variable bindings because their evaluation does not depend on the evaluation of any variable.Figure16shows the evaluation rule for VariableExp. When this rule is applied,a new link is created between VariableExp and the value to which NameValueBinding,with the same name as VariableDeclaration, is connected.Fig.15.Integer Literal Expression EvaluationFig.16.Variable Expression Evaluation4Related WorkThe only paper we are aware of that shares similar interests in applying a graph-transformation based approach in order to deal with OCL constraints is[9].In this paper,a graphical visualization of OCL constraints is proposed.On top of this notation,simplification rules for OCL constraints are proposed,that implicitly also define a semantics for OCL.However,the semantics of OCL is not developed as systematically as in our approach,only the simplification rules for select are shown.Since[9]was published at a time where OCL did not have an official metamodel,the graph-transformation rules had to be based on another language definition.For a different kind of languages,behaviorial languages,Engels et al.define in[10]their dynamic semantics in form of graph-transformation rules,which are similar to our QVT rules.As an example,the semantics of UML statechart diagrams is presented.St¨a rk et al.define in[11]a formal semantics of Java.Even if they use a com-pletely different notation to specify an operational semantics,we see nevertheless a lot of striking similarities.St¨a rk et al.map the state space of a Java program to an Abstract State Machine(ASM)and describe possible state changes by a set of ASM rules that manipulate the Abstract Syntax Tree of a program.As shown in our motivating example,there are no principal differences between an AST and an instance of the metamodel.Also,ASM and QVT rules are based on the same mechanisms(pattern matching and rewriting).5Conclusions and Future WorkWe developed a metamodel-based,graphical definition of the semantics of OCL. Our semantics consists of a metamodel of the semantic domain(we slightly adapted existing metamodels from UML1.x)and a set of transformation rules written in QVT that specify formally the evaluation of an OCL constraint in a snapshot.To read our semantics,one does not need advanced skills in mathe-matics or even knowledge in formal logic;it is sufficient to have a basic under-standing of metamodeling and QVT.The most important advantage,however, is theflexibility our approach offers to adapt the semantics of OCL to domain-specific needs.Since the evaluation rules can directly be executed by any QVT compliant tool,it is now very easy to provide tool support for a new dialect of OCL.This is an important step forward to the OMG’s vision to treat OCL as a family of languages.We are currently investigating how an OCL semantics given in form of QVT rules can be used to argue on the semantical correctness of refactoring rules for UML/OCL,which we have defined as well in form of QVT rules.A refac-toring rule describes small changes on UML class diagrams with attached OCL constraints.A rule is considered to be syntactically correct if in all applicable situations the refactored UML/OCL model is syntactically well-formed.We call a rule semantically correct if in any given snapshot the evaluation of the originalOCL constraint and the refactored OCL constraint yields to the same result(in fact,this view is a simplified one since the snapshots are sometimes refactored as well).To argue on semantical correctness of refactoring rules,it has been very handy to have the OCL semantics specified in the same formalism as refactoring rules,in QVT.A more detailed description together with a complete argumen-tation on the semantical correctness of the MoveAttribute refactoring rule can be found in[12].Another branch of future activities is the description of the semantics of pro-gramming languages with graphical QVT rules.Our ultimate goal is to demon-strate that also the description of the semantics of a programming language can be given in an easily understandable,intuitive format.This mightfinally con-tribute to a new style of language definitions where the semantics of the language can be formally defined as easy and straightforward as it is today already the case with the syntax of languages.References1.Grady Booch,James Rumbaugh,and Ivar Jacobson.The Unified Modeling Lan-guage User Guide.Addison-Wesley,second edition,2005.2.Marjan Mernik,Jan Heering,and Anthony M.Sloane.When and how to developdomain-specific languages.ACM Computing Surveys,37(4):316–344,2005.3.Mark Richters.A precise approach to validating UML models and OCL con-straints.PhD thesis,Bremer Institut f¨u r Sichere Systeme,Universit¨a t Bremen, Logos-Verlag,Berlin,2001.4.OMG.UML2.0OCL Specification–OMG Final Adopted Specification.OMGDocument ptc/03-10-14,Oct2003.5.Achim D.Brucker and Burkhart Wolff.A proposal for a formal OCL semanticsin Isabelle/HOL.In Victor Carre˜n o,C´e sar Mu˜n oz,and Sofi`e ne Tashar,editors, TPHOLs,volume2410of LNCS,pages99–114.Springer,2002.6.OMG.UML1.5Specification.OMG Document formal/03-03-01,March2003.7.OMG.UML2.0Infrastructure Specification.OMG Document ptc/03-09-15,Sep2003.8.OMG.Meta object facility(MOF)2.0Query/View/Transformation Specification.OMG Document ptc/05-11-01,Nov2005.9.Paolo Bottoni,Manuel Koch,Francesco Parisi-Presicce,and Gabriele Taentzer.Consistency checking and visualization of OCL constraints.In UML2000,volume 1939of LNCS,pages294–308.Springer,2000.10.Gregor Engels,Jan Hendrik Hausmann,Reiko Heckel,and Stefan Sauer.Dynamicmeta modeling:A graphical approach to the operational semantics of behavioral diagrams in UML.In UML2000,volume1939of LNCS,pages323–337.Springer, 2000.11.Robert F.St¨a rk,Joachim Schmid,and Egon B¨o rger.Java and the Java VirtualMachine-Definition,Verification,Validation.Springer,2001.12.Thomas Baar and Slaviˇs a Markovi´c.A graphical approach to prove the semanticpreservation of UML/OCL refactoring rules.In Proceedings,Sixth International Andrei Ershov Memorial Conference,Perspectives of System Informatics(PSI), Novosibirsk,Russia,LNCS.Springer,July2006.To appear.。

semantics知识点总结Semantics is the study of meaning in language. It is concerned with how words and sentences are interpreted, how meaning is assigned to linguistic expressions, and how meaning is inferred from language. In this summary, we will explore some key concepts and topics in semantics, including the following:1. Meaning and reference2. Sense and reference3. Truth-conditional semantics4. Lexical semantics5. Compositional semantics6. Pragmatics and semantics7. Ambiguity and vagueness8. Semantic changeMeaning and referenceMeaning is a fundamental concept in semantics. It refers to the content or interpretation that is associated with a linguistic expression. The study of meaning in linguistics is concerned with understanding how meaning is established and conveyed in language. Reference, on the other hand, is the relationship between a linguistic expression and the real world entities to which it refers. For example, the word "dog" refers to the concept of a four-legged animal that is commonly kept as a pet. The study of reference in semantics is concerned with understanding how words and sentences refer to objects and entities in the world.Sense and referenceThe distinction between sense and reference is an important concept in semantics. Sense refers to the meaning or concept associated with a linguistic expression, while reference refers to the real world entities to which a linguistic expression refers. For example, the words "morning star" and "evening star" have the same reference - the planet Venus - but different senses, as they are used to describe the planet at different times of the day. Frege, a prominent philosopher of language, introduced this important distinction in his work on semantics.Truth-conditional semanticsTruth-conditional semantics is an approach to semantics that seeks to understand meaning in terms of truth conditions. According to this view, the meaning of a sentence isdetermined by the conditions under which it would be true or false. For example, the meaning of the sentence "The cat is on the mat" is determined by the conditions under which this statement would be true - i.e. if there is a cat on the mat. Truth-conditional semantics has been influential in the development of formal semantics, and it provides a formal framework for analyzing meaning in natural language.Lexical semanticsLexical semantics is the study of meaning at the level of words and lexical items. It is concerned with understanding the meanings of individual words, as well as the relationships between words in a language. Lexical semantics examines how words are related to each other in terms of synonymy, antonymy, hyponymy, and other semantic relationships. It also explores the different senses and meanings that a word can have, and how these meanings are related to each other. Lexical semantics plays a crucial role in understanding the meaning of sentences and discourse.Compositional semanticsCompositional semantics is the study of how the meanings of words and sentences are combined to create complex meanings. It seeks to understand how the meanings of individual words are combined in sentences to produce the overall meaning of a sentence or utterance. Compositional semantics is concerned with understanding the rules and principles that govern the composition of meaning in natural language. It also explores the relationship between syntax and semantics, and how the structure of sentences contributes to the interpretation of meaning.Pragmatics and semanticsPragmatics is the study of how language is used in context, and how meaning is influenced by the context of language use. Pragmatics is closely related to semantics, but it focuses on the use of language in communication, and how meaning is affected by factors such as the speaker's intentions, the hearer's inferences, and the context in which the language is used. While semantics is concerned with the literal meaning of linguistic expressions, pragmatics is concerned with the implied meaning that arises from the use of language in context.Ambiguity and vaguenessAmbiguity and vagueness are common phenomena in natural language, and they pose challenges for semantic analysis. Ambiguity refers to situations where a linguistic expression has multiple possible meanings, and it is unclear which meaning is intended. For example, the word "bank" can refer to a financial institution or the edge of a river. Vagueness, on the other hand, refers to situations where the boundaries of a linguistic expression are unclear or indistinct. For example, the word "tall" is vague because it is not always clear what height qualifies as "tall". Semantics seeks to understand how ambiguity and vagueness arise in language, and how they can be resolved or managed in communication.Semantic changeSemantic change refers to the process by which the meanings of words and linguistic expressions evolve over time. Over the course of history, languages undergo semantic change, as words acquire new meanings, lose old meanings, or change in their semantic associations. Semantic change can occur through processes such as metaphor, metonymy, broadening, narrowing, and generalization. Understanding semantic change is important for the study of historical linguistics and the diachronic analysis of language.ConclusionSemantics is a rich and complex area of study that plays a fundamental role in understanding the meaning of language. It encompasses a wide range of topics and concepts, and it has important implications for fields such as philosophy of language, cognitive science, and natural language processing. By exploring the key concepts and topics in semantics, we can gain valuable insights into how meaning is established and conveyed in language, and how we can analyze and understand the rich complexity of linguistic expressions.。