PLC的高速数据采集分析与记录工具 在工业现场,设备调试时经常遇到需要对PLC各种变量捕捉分析,优化控制时序,检查动作过程是否准确等情况;在设备运行时又需要对设备的运行状态进行全方位的监控和记录,方便设备故障后,故障过程的重现与故障原因的分析,尤其一些控制逻辑复杂的设备,这种需求更加突出。 在一般情况下,SCADA监控软件的趋势记录就可以满足需求,但是SCADA在趋势与记录上存在很大的劣势,比如,采集数据量大的系统(系统本身庞大,需要采集的数据点多),采集速度要求高的系统(系统本身运行快,要求最大程度复现控制器内逻辑与数据的处理过程,如西门子TDC等),这些情况下,单纯的依靠SCADA已经无法满足我们的需要,那么就需要专用的数据采集分析与记录工具帮我们完成。 下面是对PLC的一些数据采集与记录工具的介绍。 1)、iba公司的PDA 既然要说数据采集记录工具,首先要提的当然是强大的PDA,软件本身支持很多驱动,可以选择带硬件支持的版本,一般采用控制器连接iba公司的模块,模块通过光纤连接工控机的配置方法,能够最大限度提高速度,当然也有纯软件的版本,这个软件在钢铁行业应用的比较多,如轧制过程的数据采集记录。(不过,这个软件的价格我只能呵呵了),软件截图:

2)、AUTEM公司的PLC-ANALYZER pro 关于此软件,同样提供多种驱动。支持的PLC-Driver有Siemens SIMATIC S7 / C7 / M7, SAIA xx7, VIPA, SIMATIC S5, Siemens LOGO!, SINUMERIK, SIMOTION, BOSCH, CoDeSys, PILZ, Phoenix, Jetter, Allen-Bradley, GE Fanuc, HITACHI, OMRON, Mitsubishi, Schneider, AUTEM AD_USB-Box?, Beckhoff TwinCat等,对于西门子的PLC,支持 MPI/PROFIBUS/ETHERNET等,但是在软件的实际使用时你会发现,软件功能较PDA逊色不少。软件截图:

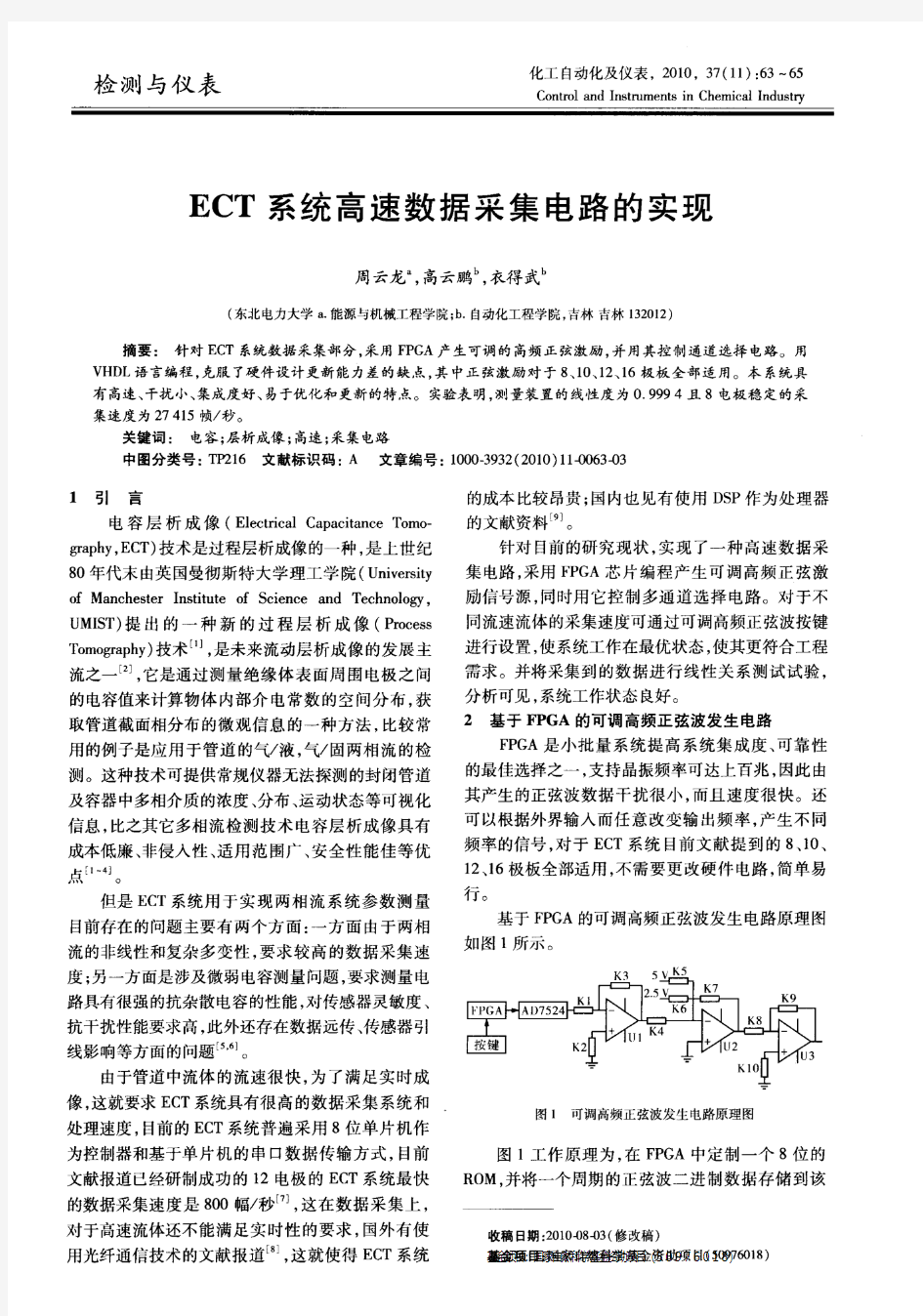

分类号:TP315 U D C:D10621-408-(2007)6203-0 密级:公开编号:2003032184 成都信息工程学院 学位论文 基于C51的数据采集电路PCB的设计与制作 论文作者姓名: 申请学位专业: 申请学位类别: 指导教师姓名(职称): 论文提交日期:

基于C51的数据采集电路PCB的设计与制作 摘要 “基于C51的数据采集电路PCB的设计与制作”是针对现代水利行业水情数据采集而设计制作的电路PCB。同时,也是为了响应国家提出的数字水利这样一个大背景下,把水利信息化尽快的实现、完善、壮大起来。本设计讲述了电子电路设计软件Protle99的基本功能,而后逐一介绍开发数据采集系统的步骤:需求分析、系统分析、系统设计、系统实现、系统维护。需求分析介绍了针对水利行业而进行了本系统的设计,在系统分析中分析了电子电路设计功能的各种元气件功能和各种连线要完成的功能,以及整个要完成的功能。在系统的设计中,详细的展现了系统的各个功能模块、原理图绘制、PCB的完成所需的准备步骤。在系统的实现中,给出了一个满足系统功能的完整PCB。通过反复的测试,我们得出结果,整个系统的设计是成功的,可以应用到所有的水利行业,进行数据的采集。 关键字:PCB;数据采集;电子电路;数字水利

The Design and Implementation of Data Acquisition Circuit Based on C51 Abstract “The design and implementation of data acquisition circuit based on C51” is the circuit PCB designed and implemented according to data of water situation of modern conservancy industry. At the same time, in order to response to the digital conservancy raised by our country, it makes the conservancy informationization implement, perfect and grow. This paper discusses the basic function of electronic circuit design software-Protle99. It takes this system for example to introduce the development steps of this system one by one: demand analysis, syst em analysis, system design, system implementation and system maintenance. Demand analysis introduces the design of this system focusing on conservancy industry. It analyses functions of various components and various connections of electronic circuit desig n in system analysis, as well as the function of completion. In the design of this system, it shows the preparing steps of every functional module, drawing of principle chart, and completion of PBC of this system. In the implementation of this system, it gives a complete PBC matched for the function of the system. After repeated tests, the result is that the design of this system is successful and it can be applied to all conservancy industries to collect data. Key word s:PCB; data collection; electronic circuit;digital conservancy

高速数据采集系统 设计

基于FPGA和SoC单片机的 高速数据采集系统设计 一.选题背景及意义 随着信息技术的飞速发展,各种数据的实时采集和处理在现代工业控制和科学研究中已成为必不可少的部分。高速数据采集系统在自动测试、生产控制、通信、信号处理等领域占有极其重要的地位。随着SoC单片机的快速发展,现在已经能够将采集多路模拟信号的A/D转换子系统和CPU核集成在一片芯片上,使整个数据采集系统几乎能够单芯片实现,从而使数据采集系统体积小,性价比高。FPGA为实现高速数据采集提供了一种理想的实现途径。利用FPGA高速性能和本身集成的几万个逻辑门和嵌入式存储器块,把数据采集系统中的数据缓存和控制电路全部集成在一片FPGA芯片中,大大减小了系统体积,提高了灵活性。FPGA 还具有系统编程功能以及功能强大的EDA软件支持,使得系统具有升级容易、开发周期短等优点。 二.设计要求 设计一高速数据采集系统,系统框图如图1-1所示。输入模拟信号为频率200KHz、Vpp=0.5V的正弦信号。采样频率设定为25MHz。经过按键启动一次数据采集,每次连续采集128点数据,单片机读取128点数据后在LCD模块上回放显示信号波形。

图1-1 高速数据采集原理框图 三.整体方案设计 高速数据采集系统采用如图3-1的设计方案。高速数据采集系统由单片机最小系统、FPGA最小系统和模拟量输入通道三部分组成。输入正弦信号经过调理电路后送高速A/D转换器,高速A/D 转换器以25MHz的频率采样模拟信号,输出的数字量依次存入FPGA内部的FIFO存储器中,并将128字节数据在LCD模块回放显示。 图3-1 高速数据采集系统设计方案 四.硬件电路设计 1.模拟量输入通道的设计 模拟量输入通道由高速A/D转换器和信号调理电路组成。信号调理电路将模拟信号放大、滤波、直流电平位移,以满足A/D转换器对模拟输入信号的要求。

激光雷达高速数据采集系统解决方案 0、引言 1、 当雷达探测到目标后, 可从回波中提取有关信息,如实现对目标的距离和空间角度定位,并由其距离和角度随时间变化的规律中得到目标位置的变化率,由此对目标实现跟踪; 雷达的测量如果能在一维或多维上有足够的分辨力, 则可得到目标尺寸和形状的信息; 采用不同的极化方法,可测量目标形状的对称性。雷达还可测定目标的表面粗糙度及介电特性等。接下来坤驰科技将为您具体介绍一下激光雷达在数据采集方面的研究。 1、雷达原理 目标标记: 目标在空间、陆地或海面上的位置, 可以用多种坐标系来表示。在雷达应用中, 测定目标坐标常采用极(球)坐标系统, 如图1.1所示。图中, 空间任一目标P所在位置可用下列三个坐标确定: 1、目标的斜距R; 2、方位角α;仰角β。 如需要知道目标的高度和水平距离, 那么利用圆柱坐标系统就比较方便。在这种系统中, 目标的位置由以下三个坐标来确定: 水平距离D,方位角α,高度H。 图1.1 用极(球)坐标系统表示目标位置

系统原理: 由雷达发射机产生的电磁能, 经收发开关后传输给天线, 再由天线将此电磁能定向辐射于大气中。电磁能在大气中以光速传播, 如果目标恰好位于定向天线的波束内, 则它将要截取一部分电磁能。目标将被截取的电磁能向各方向散射, 其中部分散射的能量朝向雷达接收方向。雷达天线搜集到这部分散射的电磁波后, 就经传输线和收发开关馈给接收机。接收机将这微弱信号放大并经信号处理后即可获取所需信息, 并将结果送至终端显示。 图1.2 雷达系统原理图 测量方法 1).目标斜距的测量 雷达工作时, 发射机经天线向空间发射一串重复周期一定的高频脉冲。如果在电磁波传播的途径上有目标存在, 那么雷达就可以接收到由目标反射回来的回波。由于回波信号往返于雷达与目标之间, 它将滞后于发射脉冲一个时间tr, 如图1.3所示。 我们知道电磁波的能量是以光速传播的, 设目标的距离为 R, 则传播的距离等于光速乘上时间间隔, 即2R=ct r 或 2 r ct R

高速数据采集卡250MSPS 14bit 250MSPS 14bit 8通道高速数据采集卡主要应用于雷达、通信、电子对抗、高能物理、质谱分析、超声等高科技领域。西安慕雷电子在高速数据采集卡研发及系统应用领域拥有十多年经验,2013年底发布了250MSPS 14bit 8通道高速数据采集卡MR-HA-250M,采集记录存储带宽高达3000MB/S。高速数据采集卡MR-HA-250M及记录存储系统的成功发布使得西安慕雷电子在高速数据采集卡及相关记录存储回放领域为国防及科研领域又提供了一套高性能解决方案。 图一高速数据采集卡MR-HA-250M 高速数据采集卡MR-HA-250M模块参数: ●输入接口: 连接器:SSMC; 输入方式:AC或DC耦合; 通道数量:8通道,可同步32通道 ●AFE模块: 高速数据采集卡中的信号调理模块一般采用衰减、滤波及程控增益放大器等对信号进行处理,高速数据采集卡MR-HA-250M采用信号直通AD模式,减少前端调理对高速数据采集卡动态性能影响。 图二高速数据采集卡MR-HA-250M

●ADC模块: 高速数据采集卡的ADC芯片采用Linear Tech LTC2157-14 (250 MSPS) 图三高速数据采集卡MR-HA-250M动态性能 ●时钟管理模块: 高速数据采集卡MR-HA-250M可选择外时钟、内时钟或参考时钟 ●FPGA模块: XILINX或ALTERA的FPGA芯片广泛用于高速数据采集卡中。FPGA模块开放编程是高速数据采集卡的必备能力。高速数据采集卡MR-HA-250M采用XILINX V6系列高性能FPGA。 ●DDR模块: 高速数据采集卡一般都会配有DDR缓存,存储采集过程中的数据。高速数据采集卡MR-HA-250M配置有4GB DDR2。 ●FIFO模式 高速数据采集卡将板载内存虚拟为FIFO,允许采集数据由缓冲后连续不断地通过总线传输到主机内存或硬盘中。该模式特点就是高速、大容量,使得高速数据采集卡记录时间达数小时。记录时间取决于存储介质的容量。 图四高速数据采集卡MR-HA-250M

技术创新 电子设计 您的论文得到两院院士关注 两千兆高速数据采集电路设计 The Design of an 2GSPS High Speed Data Acquizition System (中国石油大学北京) 桑泉柯式镇钱步仁 SANG Quan KE Shi-zhen QIAN Bu-ren 摘要:本文采用美国国家半导体公司的高速双通道模数转换器(ADC08D1000),以及Altera 公司CycloneII 系列的FPGA (EP2C70F896C8)实现对双路信号的高速采样,每片ADC 通过交叉采样对每路信号的采样率达到2GSPS 。本文着重介绍电路的设计,以及PCB 制版过程当中的技巧问题。关键词:高速采集;LVDS;阻抗匹配;电源分割中图分类号:TP274+.2文献标识码:B Abstract:In this paper,a high speed dual ADC(ADC08D1000)produced by National Semiconductor and an FPGA (EP2C70F896C8)in CycloneII series of Altera are used to sampling two signals in the same time ,and each converter is interleaved to increased the sample rate up to 2GSPS.Here our emphases are on some tips on design of the cirsuit and PCB board.Key words:High speed acuizition;LVDS;Impedance matching;Spliting on power board 文章编号:1008-0570(2010)04-2-0191-02 1高速ADC 芯片ADC08D1000 ADC08D1000是美国国家半导体公司(National Semiconduc - tor)于近年推出的双通道、 低功耗高速采样芯片,具有8位分辨率,单通道最高采样率达到1.3GHz 。双通道可以同时对两路信号同时采样,也可以同一信号进行交叉采样,这时采样率可以高达2GHz 。器件使用单一的1.9V 电压供电,整个器件的典型功率 消耗仅1.6W 。 当输入信号为500MHz,采样率为1GHz 的时,其独特的设计结构可以保证获得7.4位的有效采样位数,而位出错率仅只10-18。 ADC08D1000的输出数据采用了低电压差分传输信号(Low-Voltage Differential Signaling)。LVDS 的摆幅很小,典型值仅为350mA,这样一方面降低了系统的功率消耗,另外也使得高速的信号传输成为可能,并且由于高速差分先的成对出现,使得信号的完整性更好,当然,这个也需要适当的布线才能完成。在芯片当中每个通道有两路8位信号输出总线,这样,当每片ADC 对一路信号进行交叉采样后,共有4条信号输出总线将数据输出,即此时的数据输出速率为500MHz,通过这样的降速,使得接收器件的选择范围更大,也使避免使用专门的LVDS 接收器成为可能。 在本系统当中使用Altera 公司的CycloneII 系列的FPGA 接收采样数据,这是处于对产品成本和性能的综合考虑而来的。CycloneII 系列的FPGA 的LVDS 信号的接收速率达到805Mbps,发送可以达到640Mbps,完全可以满足接收ADC 的信号要求。另外在本设计当中,使用了两片ADC,要求对两路ADC 进行同时操作,即对ADC 采样开始时间、采样数据多少要保持一致,所以尽量使用一片控制芯片,能同时接收两片ADC 信号的输出采样数据,并且可以对两路ADC 进行控制。由于ADC 芯片输出为4条8位总线输出数据,这样每片ADC 的输出数据共有32对LVDS 线,同时ADC 芯片的输出数据的随路时钟信号 (DCLK)以及数据溢出标志位(OVR)同样是采用LVDS 信号,那么每片上面共有34对LVDS 线,所以要求FPGA 有接收68对LVDS 数据的能力,同时考虑到FPGA 的引脚的分配和全局时钟的位置安排,本系统选取了EP2C70F896C8作为数据接收及其他芯片的控制芯片。 2硬件电路设计 2.1ADC 外围电路设计 ADC 芯片的外围电路如下图所示: 对于输入被采样信号来说,使用差分信号要比单端信号更加可靠,如果经过前端放大电路后仍是单端信号,那么可以使用平衡-不平衡变压器(例如ADTL2-18)。 ADC 的控制方式有两种,一种是将控制一脚的电平直接处于高电位或者低电位,这种方式可以使用ADC 的大部分功能,但是不可更改;另外一种方式是基于SPI 口的扩展模式,在这种模式下可以使用ADC 的全部功能,本设计就使用了这种方式,在这种方式下,需要对控制信号的电平进行适当的分压,如图所示上图所示。 Rext 引脚必须外接一个高精度的3.3K 的电阻,可以降低偏 桑泉:硕士研究生

一种高速数据采集记录装置的设计 【摘要】文章介绍了一种基于Flash的高速数据采集记录装置的实现方案;文中采用了Flash高速存储技术与FPGA的二级缓冲技术,提高了存储速度,突破存储芯片的瓶颈,成功实现了数据存储速率与传输速率完美的匹配;同时通过设计合理的电路降低了存储模块的功耗,利用可靠的通信协议,有效保证了信号数据的可靠接收和存储。 【关键词】数据记录仪;Flash;高速存储 1.系统方案设计 本文设计的数据记录系统由以下几部分组成:两台完全相同的数据记录仪、一个地面综合测试台、上位机、配套软件以及配套电缆。主要用于记录由雷达系统产生的视频回波、图像及遥测三路LVDS高速信号。系统工作时,由雷达系统首先发来启动记录信号,使已处于采集状态的两台记录仪同时工作,二者互为备份。地面测试台产生的模拟信号供记录仪存储,同时可以控制记录仪进入不同的工作状态,通过内置的USB接口读取记录仪的数据;上位机通过USB电缆与地面测试台相接,对回读的数据进行分析,同时验证记录仪是否正常工作。 2.系统硬件设计 该系统采用隔离变压器隔离接收三路LVDS数据,使得隔离前后的电路没有电气连接特性,然后再将隔离后的信号传送给存储模块;经过存储模块的均衡、解串后传给FPGA中心控制器,最后存入两片Flash中。 遥测系统输出的三路数据都有各自的启动记录信号。当记录仪接收到启动控制信号,开始记录对应路的数据,并存储到相应的存储模块中。飞行试验完毕后,可以利用备用读数电缆,将各个存储模块中数据通过测试台上传至上位机中进行分析,以便对记录仪的存储功能进行验证。在飞行模式下记录仪的供电由雷达系统完成。 记录仪由三个存储模块和一个接口模块组成。存储模块主要接收遥测系统的视频回波、图像及遥测三路LVDS信号,并对其中的有效数据进行实时存储。该模块主要包括以下几个部分:中心逻辑控制芯片FPGA、配置芯片PROM、LVDS 电缆均衡器、LVDS解串芯片、存储芯片Flash、电源模块以及60MHz晶振等[1]。如图2.1所示: 接口模块主要包括LVDS高速读数接口、RS-422长线接口、视频及图像遥测雷达信号输入接口、各个存储模块的LVDS输入接口以及数据上传和指令下发接口。高速读数接口与地面测试台主控卡的相应接口连接,通过LVDS接口高速读取其中的数据;422长线接口通过双绞线电缆与地面测试台连接,主要实现记录仪与地面测试台之间的通信。

等间距采样的高速数据采集系统设计 郝亮,孟立凡,刘灿,高建中 (中北大学仪器科学与动态测试教育部重点实验室,太原030051) 摘要:简单介绍通过对窄脉冲等间距采样来测试电缆故障的基本原理,分析其脉冲的特点和处理要求;采用F PGA和MSP430F149作为主控芯片,设计了单路多次低速数据采集系统;利用Quartus II软件编写主控程序,并在Modelsim下进行仿真验证。实验结果表明,该系统方案切实可行,可有效解决电缆故障测距过程中的高精度数据采集问题。 关键词:等间距采样;数据采集;MSP430F149;F PGA 中图分类号:TN98文献标识码:B H igh2spe ed Data Acquisition System Based on Equidistance Sampling Hao Liang,Meng Lifan,Liu Can,Gao Jianzhong (Inst ruments Science and Dynamic Measurement Ministry of Education Key Laboratory, North University of China,T aiyuan030051,China) A bstract:T he basic principle of testing cable faults wit h narrow2pulse equidistance sampling is described.Pulse characteristics and pro2 cessing requirements are analyzed.The single2line repeated low2speed dat a acquisition system is designed with FPGA and MSP430F149 as main control chips.Main control procedures are programmed in Quartus II and simulated in Modelsim.Experimental result shows that t he system is practical,and the problem of high2precision data acquisition in the process of cable fault location is resolved effectively. K ey words:equidist ance sampling;data acquisit ion;MSP430F149;FPGA 引言 电缆故障是通信行业中的常见故障,而电缆测距是排除故障的前提条件。准确的电缆测距可以缩短发现故障点的时间,利于快速排除故障,减少损失。窄脉冲时域反射仪利用时域反射技术来测定电缆断点位置,可以同时检测出同轴传输系统中多个不连续点的位置、性质和大小。窄脉冲信号持续的时间非常短暂,为了能够有效地捕捉到窄脉冲信号,对A/D采样率和处理器速率提出了较高的要求,传统的数据采集已经不能满足系统设计需求。本文介绍的单路多次低速数据采集方案硬件结构简单,成本低,能够满足系统设计要求。 1系统设计理论依据 根据电磁波理论,电缆即传输线。假若在电缆的一端发送一探测脉冲,它就会沿着电缆进行传输,当电缆线路发生障碍时会造成阻抗不匹配,电磁波会在障碍点产生反射。在发射端,由测量仪器将发送脉冲和反射脉冲波形记录下来。实际测试中,具体障碍的波形有所差异:断线(开路)障碍时,反射脉冲与发射脉冲极性相同;而短路、混线障碍时,反射脉冲与发射脉冲极性相反。波形如图1所示。 图1发射脉冲与反射脉冲波形 设从发射窄脉冲开始到接收到反射脉冲波的时间为$t,则: l=v#$t 2 其中,v为脉冲波在电缆中的传输速度;l为电缆故障点与脉冲波送入端的距离。 由以上分析可知,在同一个固定障碍的线路上多次送入同一脉冲电压,其反射脉冲将同样地在同一位置多次出现。 要实现对反射窄脉冲的捕获和1m的测距分辨率(在波速为200m/L s的情况下),则$t= 2l v =2@1 200 =0.01L s =10ns。即要求抽样的时间分辨率为10ns,对应的数据采集系统频率高达100MHz。同时,最大测量范围是2km 时,要求发射脉冲的重复周期T= 2l v =2@2000 200 =20L s。

高速数据采集技术发展综述 摘要:高速数据采集系统广泛应用于军事、航天、航空、铁路、机械等诸多行业。区别于中速及低速数据采集系统,高速数据采集系统内部包含高速电路,电路系统1/3以上数字逻辑电路的时钟频率>=50MHz;对于并行采样系统,采样频率达到50MHz,并行8bit以上;对于串行采样系统,采样频率达到200MHz,目前广泛使用的高速数据采集系统采样频率一般在200KS/s~100MS/s,分辨率16bit~24bit。本篇文章主要简单介绍高速数据采集技术的发展,高速数据采集系统的结构、功能、原理、实现形式以及一些主要的应用。 关键词:高数数据采集系统、系统结构、系统原理、系统功能、实现形式、应用举例。 引言:高速数据采集技术在通信、航天、雷达等多个领域中广泛应用。随着软件无线电、通信技术、图像采集等技术的发展,对数据采集系统的要求越来越高,不仅要求较高的采集精度和采样速率,还要求采集设备便携化、网络化与智能化,并且需要将采集信息稳定的传输到计算机,进行显示与数据处理。同时,以太网协议已经成为当今局域网采用的最通用的通信协议标准。在嵌入式领域中,将以太网协议与数据采集系统相结合,形成局域网,实现方便可靠的数据传输与控制,是当前的研究热点。 1. 高速数据采集的发展 数据采集系统起始于20世纪50年代,由于数据采集测试系统具有高速性和~定的灵活性,可以满足众多传统方法不能完成的数据采集和测试任务,因而得到了初步的认可。到了70年代中后期,在数据采集系统发展过程中逐渐分为两类,一类是实验室数据采集系统,另一类是工业现场数据采集系统。就使用的总线而言,实验室数据采集系统多采用并行总线,工业现场数据采集系统多采用串行数据总线。随着微型机的发展,诞生了采集器、仪表等同计算机融为一体的数据采集系统。由于这种数据采集系统的性能优良,超过了传统的自动检测仪表和专用数据采集系统,因此获得了惊人的发展他3。随着计算机的普及应用,数据采集系统得到了极大的发展,基于标准总线并带有高速DSP的高速数据采集板卡产品也越来越多,技术先进、市场主流的厂商主要有Spectrum Signal Processing,SPEC,Signatec,Acquisition Logic,Blue Wave等公司 2001年Acquisition logic公司推出了基于PCI总线,采样率为500MS/s,1GS/s的8bit数据采集板卡AL500和AL51G,它的存储深度分别为64MB,256MB和1000MB三种。PCI 总线为主模式,数据宽度32bit,时钟频率33MHz,在突发模式下传输速率可达到133MB /s。两种板卡还同时具有数字信号处理功能:通过板卡上的现场可编程门阵列FPGA来实

多路数据采集系统设计毕业论文 第1章绪论 1.1 多路数据采集系统介绍 随着工、农业的发展,多路数据采集势必将得到越来越多的应用,为适应这一趋势,作这方面的研究就显得十分重要。在科学研究中,运用数据采集系统可获得大量的动态信息,也是获取科学数据和生成知识的重要手段之一。总之,不论在哪个应用领域中,数据采集与处理将直接影响工作效率和所取得的经济效益。 此外,计算机的发展对通信起了巨大的推动作用。算机和通信紧密结合构成了灵活多样的通信控制系统,也可以构成强有力的信息处理系统,这样对社会的发展产生了深远的影响。数据通信是计算机广泛应用的必然产物[2]。 数据采集系统,从严格的意义上来说,应该是用计算机控制的多路数据自动检测或巡回检测,并且能够对数据实行存储、处理、分析计算以及从检测的数据中提取可用的信息,供显示、记录、打印或描绘的系统。 数据采集系统一般由数据输入通道,数据存储与管理,数据处理,数据输出及显示这五个部分组成。输入通道要实现对被测对象的检测,采样和信号转换等

工作。数据存储与管理要用存储器把采集到的数据存储起来,建立相应的数据库,并进行管理和调用。数据处理就是从采集到的原始数据中,删除有关干扰噪声,无关信息和必要的信息,提取出反映被测对象特征的重要信息。另外,就是对数据进行统计分析,以便于检索;或者把数据恢复成原来物理量的形式,以可输出的形态在输出设备上输出,例如打印,显示,绘图等。数据输出及显示就是把数据以适当的形式进行输出和显示。 由于RS-232在微机通信接口中广泛采用,技术已相当成熟。在近端与远端通信过程中,采用串行RS-232标准,实现PC机与单片机间的数据传输。在本毕业设计中对多路数据采集系统作了初步的研究。本系统主要解决的是怎样进行数据采集以及怎样进行多路的数据采集,并将数据上传至计算机[2]。 1.2 设计思路 多路数据采集系统采用ADC0809模数转换器作为数据采集单元和AT89C51单片机来对它们进行控制,不仅具有控制方便、简单和灵活性大等优点,而且可以大幅度提高采集数据的灵敏度及指标。通过MAX232电平转换芯片实现单片机与PC 机的异步串行通信,设计中的HD7279实现了键盘控制与LED显示显示功能。本文设计了一种以AT89C51和ADC0809及RS232为核心的多路数据采集系统。 多路数据采集系统就是通过键盘控制选择通路,将采集到的电压模拟两转换成数字量实时的送到单片机里处理从而显示出采集电压和地址值,最终控制执行单片机与PC机的异步串行通信。 连接好硬件后,给ADC0809的三条输入通路通入直流电压。4-F键为功能键,4-E键为复位键,F键为确认键。1-3键为通道选择键,分别采集三个通道的数据值并实时显示出数值和地址值。结合单片机RS232串口功能还实现了与PC机的异

实验七数据采集电路PCB板设计 一、实验目的 (1)掌握电路原理图设计流程。 (2)掌握电路原理图层次设计。 (3)掌握由电路原理图到PCB设计的设计流程。 (4)掌握PCB设计流程。 二、基本要求 在自己的工程组的PCB工程文件中建立多个原理图文件,并建立一个PCB文件。按实验内容,设计出PCB板。 三、实验器材 P4计算机、Protel DXP软件 四、实验内容 绘制出下列电路原理图,进行层次设计,并进行PCB板设计。 图7-1 5V电源电路原理图 图7-2 串行通信电路原理图

图7-3 数据采集电路原理图 五、实验步骤 1. 建立原理图文件 (1) 运行Protel DXP,进入Protel DXP设计环境。 (2) 打开工程组文件:执行菜单命令【File】→【Open Project Group…】,在弹出的“Choose Project Group to Open”对话框中的【查找范围】中找到“我的工程组文件”所在的路径,并将该文件打开。 (3) 关闭当前的工程文件。 (4) 建立工程文件:执行菜单命令【File】→【New】→【PCB Project】,建立PCB Project1.PrjPCB工程文件。 执行菜单命令【File】→【Save Project】,在弹出的“Save [PCB Project1.PrjPCB] As…”对话框的文件名输入框中输入文件名(如输入:“数据采集电路PCB工程”),然后选择保存路径,再单击“保存”按钮。这样即可建立并更改工程文件名。 (5) 建立原理图文件:执行菜单命令【File】→【New】→【Schematic】,建立原理图文件Sheet1.SchDoc。 (6) 保存并更改原理图文件名:执行菜单命令【File】→【Save】,在弹出的“Save [Sheet1.SchDoc] As…”对话框的文件名输入框中输入文件名(如输入:“5V电源电路”),然后选择保存路径,再单击“保存”按钮。至此已建立好“5V电源电路”文件。按图7-1所示,绘制出5V电源电路原理图,并给元件编号。 (7) 向当前工程“数据采集电路PCB工程”中添加“串行通信电路原理图”文件:右键单击【Project】中的“数据采集电路PCB工程”工程文件名,在弹出的菜单中选择菜单命令【Add to Project…】,弹出“Choose Document to Add to Project [数据采集电路PCB工程.PRJPCB]”,选择打开文件“串行通信电路”。 (8) 继续建立原理图文件:执行菜单命令【File】→【New】→【Schematic】,建立原理图文件Sheet1.SchDoc。 (9) 保存并更改原理图文件名:执行菜单命令【File】→【Save】,在弹出的“Save [Sheet1.SchDoc] As…”对话框的文件名输入框中输入文件名(如输入:“数据采集电路”),然后选择保存路径,再单击“保存”按钮。至此已建立好“数据采集电路”文件。按图7-3所示,绘制出数据采集电路原理图,并给元件编号。 (10) 继续建立原理图文件:执行菜单命令【File】→【New】→【Schematic】,建立原理图文件Sheet1.SchDoc。 (11) 保存并更改原理图文件名:执行菜单命令【File】→【Save】,在弹出的“Save [Sheet1.SchDoc] As…”对话框的文件名输入框中输入文件名(如输入:“数据采集系统电路”),然后选择保存路径,再单击“保存”按钮。至此已建立好“数据采集系统电路”文件。

5 Gsps 高速数据采集系统的设计与实现 摘要:以某高速实时频谱仪为应用背景,论述了5 Gsps 采样率的高速数据采集系统的构成和设计要点,着重分析了采集系统的关键部分高速ADC(analog to digital,模数转换器)的设计、系统采样时钟设计、模数混合信号完整性设计、电磁兼容性设计和基于总线和接口标准(PCI Express)的数据传输和处理软件设计。在实现了系统硬件的基础上,采用Xilinx 公司ISE 软件的在线逻辑分析仪(ChipScope Pro)测试了ADC 和采样时钟的性能,实测表明整体指标达到设计要求。给出上位机对采集数据进行处理的结果,表明系统实现了数据的实时采集 存储功能。关键词:高速数据采集;高速ADC;FPGA;PCI Express 高速实时频谱仪是对实时采集的数据进行频谱分析,要达到这样的目的,对数据采集系 统的采样精度、采样率和存储量等指标提出了更高的要求。而在高速数据采集 系统中,ADC 在很大程度上决定了系统的整体性能,而它们的性能又受到时钟质量的影响。为满足系统对高速ADC 采样精度、采样率的要求,本设计中提 出一种新的解决方案,采用型号为EV8AQ160 的高速ADC 对数据进行采样;考虑到ADC 对高质量、低抖动、低相位噪声的采样时钟的要求,采用AD9520 为5 Gsps 数据采集系统提供采样时钟。为保证系统的稳定性,对模数混合信号完整性和电磁兼容性进行了分析。对ADC 和时钟性能进行测试,并给出上位 机数据显示结果,实测表明该系统实现了数据的高速采集、存储和实时后处理。 1 系统的构成高速数据采集系统主要包括模拟信号调理电路、高速ADC、高速时钟电路、大容量数据缓存、系统时序及控制逻辑电路和计算机接口电路等。图1 所示为5 Gsps 高速数据采集系统的原理框图。所用ADC 型号为EV8AQ160,8 bit 采样精度,内部集成4 路ADC,最高采样率达5 Gsps,可以工作在多种模式下。通过对ADC 工作模式进行配置,ADC 既可以工作在采样

高速数据采集系统信号调理电路的设计 上海交通大学电子信息与电气工程学院(200030) 乔 巍 杜爱玲 陈 春 叶 生摘 要 文章针对基于微控制器和PC 的高速数据采集系统,在讨论了信号调理电路功能及必要 性的基础上,给出了包括信号放大、衰减、隔离和滤波的设计方案,并对滤波电路的拓扑设计进行了研究。此外,针对广泛存在的电力信号采集与分析,以电能质量为分析、研究对象,给出了基于Sallen 2Key 和状态变量拓扑的滤波方案。对高速数据采集系统精度的提高和采集设备的保护具有实际意义。关键词 信号调理 高速数据采集 Sallen 2Key 拓扑 状态变量拓扑 目前,基于微控制器及基于PC 和内插板卡的数据采集系统在很大领域内得到了应用[1]。数据采集卡和微控制器前端的高速A/D 转换作为信号采集设备非常适合用来测量电压信号。但是,许多传感器和变送器输出的信号必须经过调理之后,才能进入数据采集卡、高速A/D 转换器或设备 ,以实现有效精确的测量。这种前端的预处理,一般就称为信号调理,包括信号放大衰减、滤波、电气隔离和多路技术。图1为基于PC 和内插板卡的数据采集系统框图[2]。 图1 基于PC 和内插板卡的数据采集系统框图 1 信号调理电路的组成 1.1 放大衰减电路 由于很多信号幅度比较小,所以需要通过放大器来提高测量的精度。放大器通过匹配信号电平和A/D 转换器的测量范围,来达到提高测量分辨率的目的。出于这个原因,现在许多数据采集卡都包括了板载放大器。同样情况,当需要数字化的电压超过了允许输入范围时,衰减就不可缺少了。1.2 隔离电路 数据采集系统中不合适的接地是造成测量问题和数据采集卡损坏的最普遍原因。对信号进行电气隔离可以防止这些问题的发生。隔离破坏了接地环路,避免了高的共模电压,并且保护了价格不菲的数据采集设备 。 通常的隔离方法有利用光耦、磁或者容性隔离器。磁或容性隔离器将信号从电压形式调制成频率形式。频率能够在转回成电压之前以非直接物理连接的方式通过变压器或者电容。当将被测信号的地和数据采集系统的地连起来的时候,会发现在两处输入的地之间存在一定的电势差,这个电压称为共模电压。如果我们用的是一个单端测量系统,如图2所示,测得的电压就会包括期望测试的电压V s 和共模电压V G 。如果采用差分输入为数据采集卡的输入方式,就能消除这些共模电压,一般说来,典型值能高达12V 。然而,高的地之间的电势差或者接地环路,都会损坏未经保护的数据采集设备。如果没有办法消除这种电势差,那么,就可以用信号隔离器来破坏接地环路以达到消除共模电压的作用。隔离器的另一个作用就是抑制一些来自电力线、闪电或者高压设备的浪涌高压。当存在这种高压的时候,一个浪涌往往能损坏设备。信号隔离器通过切断连接,建立了数据采集系统和这些高压浪涌之间的屏障。 图2 隔离原理 1.3 滤波电路 信号调理往往需要抑制一定频率范围内的噪 声,而噪声对于不同的系统有不同的含义。对于数据采集系统来说,通常有两种情况,一是来自于电力线或机器的频率在50Hz 或60Hz 的噪声,对于这种情况,大多数信号调理器的设计采用低通滤波器来实现最大程度的抑制[3]。 另一种常见的用法是用来防止信号混叠,这是由于采样率太低而引起的现象。奈奎斯特定理指出,如果对一种模拟信号进行采样,所有频率超过1/2采样率的信号都会以一种低频率信号的方式出现。我们只有在采样前把所有频率超过1/2采样率

第31卷第5期 唐山师范学院学报 2009年9月 Vol. 31 No. 5 Journal of Tangshan Teachers College Sep. 2009 ────────── 收稿日期:2008-12-12 作者简介:李洋(1982-),男,河北衡水人,唐山师范学院基础教育部教师。 -66- 一种高速数据采集系统的研究 李 洋,郭小松 (唐山师范学院 基础教育部,河北 唐山 063000) 摘 要:由于高速数据采集对信号完整性、信号干扰、高速布线及数据处理和高速实时存储要求极高,而其应用环境又往往非常复杂,所以在目前的实际应用中,很难实现一种既能进行长时间高速数据采集、又能进行大容量存储的数据采集系统。在此背景下,提出了一种高速数据采集及存储的解决方案,采用高速FPGA 加嵌入式微处理器作为中央处理器来进行高速数据传输和磁盘阵列数据存储,实现高速数据采集及大容量实时存储。 关键词:数据采集;模数转换;海量存储;RAID0 中图分类号: T N919.5 文献标识码:A 文章编号:1009-9115(2009)05-0066-03 Study of High-Speed Data Acquisition and Storage System LI Yang, GUO Xiao-song (Department of Foundation Education, Tangshan Teachers College, Tangshan Hebei 063000, China) Abstract: Because of the extreme requirements of signal integrity, noise jamming, high-speed layout, high-speed real-time storage and the complex application environments, it is very difficult to realize a high-speed data acquisition system which is suitable for long-time data acquisition and mass storage. Against this background, a solution of high-speed data acquisition and storage system is introduced in this thesis, which is using of high-speed FPGA and embedded microprocessors as the central processing device for high-speed data transfer and data storage of redundant array of inexpensive disks , realized on-time data acquisition and mass storage. Key words: data acquisition; A/D convert; mass storage; RAID 现代工业生产和科学研究对数据采集的要求日益提高,在雷达、声纳、软件无线电、瞬态信号测量等一些高速、高精度的测量中,需要进行高速数据采集。目前,数据采集系统在高速A/D 、D/A 器件发展的带动下,采集带宽在稳步提高,具有100MSPS 采集能力以上的高速数据采集系统产品己较成熟。然而国外厂商的高速采集系统往往都价格不菲,而且由于高速数据采集对信号完整性、信号干扰、高速布线及数据处理和高速实时存储要求极高,国内完全掌握这个技术的厂商并不多,所以在实际应用中,很难找到一种满足需要的高速采集系统。这种情况长期限制了高速数据采集技术在我国工业生产和科学研究中的应用。 在这样的背景下,本文提出一种高速数据采集与实时存储系统的解决方案,解决以往在高速技术、数据存储与传输技术等方面的几个技术难点,采用FPGA 作为核心器件,集成中央逻辑控制及硬盘接口,直接将高速数据存入有多块硬 盘组成的实时RAID 存储系统中,实现了高速采集和实时存储,并可脱机运行。这种方案成本低廉,能提高采集速度,增加系统可靠性,并大大提高可持续采集时间,具有较大的灵活性。 1 总体系统方案硬件设计 高速数据采集系统的主要目的是把采集到的模拟信号转化为数字信号,所以模拟信号进入数据采集系统的第一步就是通过AD 采集电路进行模数转换;采集到的数据为了以后研究调用,就需要存储到存储器中,所以系统的最后一步是使用高速海量存储器对数据进行存储;系统的启动、停止和数据传输的方式还需要使用中央逻辑控制电路,所以在AD 采集电路与高速海量存储器之间增加中央逻辑控制电路来作为AD 采集电路与高速海量存储器之间的桥梁;系统通过人机接口与PC 机连接,可以对数据采集系统进行调试,还方便调用存储数据进行研究测试,并实现