基于单片机设计的简易信号发生器

- 格式:doc

- 大小:179.50 KB

- 文档页数:18

基于单片机的信号发生器设计与实现摘要信号发生器是许多测试和实验中不可缺少的工具,在信息与通信、雷达信号处理、测量及控制、教学等领域应用十分广泛。

随着电子科学与技术的发展,对信号的频谱纯度、频率分辨率、频率的输出范围等提出的要求越来越高,然而用传统的频率合成方法研制的信号发生器在精度、功能等方面均存在较多的缺陷和不足,很大程度上不能够满足要求。

本文正是针对这一问题,设计并开发基于直接数字合成(Direct Digital Synthesis,DDS)技术的高性能、高精度的信号发生器。

用单片机控制DDS芯片完成信号的产生及控制,所产生的信号具有频率的分辨率较高、切换频率时的相位连续、频率的切换速度较快、输出相位的噪声很低等诸多优点。

本设计主要有以下几大模块构成:单片机及其接口模块、DDS模块、按键模块、液晶显示模块、幅度调节模块,能够实现通过键盘输入选择正弦波、方波、三角波三种波形,并通过液晶屏显示其频率值和示意波形等功能。

最后,应用单片机和DDS技术研制了一个现实可用的信号发生器,并给出了基于单片机和DDS技术的信号发生器的电路原理框图,PROTEL下的电路图,设计过程和软件流程图。

测试结果表明:本信号发生器达到了预期的设计要求,其性能和各种指标明显好于传统的信号发生器。

关键词:单片机DDS信号发生器Based on SCM Signal Generator Designand ImplementationAbstractSignal generator is an indispensable tool in many tests and experiments, and it has very extensive application in information and communication, radar signal processing, measurement and control, teaching, and other areas. As the electronic science and technology development, the spectrum of the signal frequency resolution, purity, the output of the frequency range of the demands of more and more high, but to use the traditional frequency synthesis method developed in precision, function signal generator which have many defects and the insufficiency, largely can't meet the requirements. This paper is to solve such a problem, design and develop high performance, high precision of the signal generator based on direct digital synthesis technologyWith single-chip microcomputer control chips signal is produced and control, the resulting signal has a higher frequency resolution, switching frequency of the phase of the continuous, frequency switching speed and output of the noise is low phase many advantages.This design basically has the following a few big blocks: SCM and its interface module, modules, key module, liquid crystal display module, amplitude adjustment module, can realize through the keyboard input choose sine wave, square wave, triangle wave three waveform, and through the LCD shows its frequency value and signal waveform etc. Function.Finally, the application of the single chip microcomputer and technology developed a reality of the available signal generator, and give the technology based on single chip microcomputer and the signal generator circuit principle diagram, the circuit diagram, design process under and software flow chart. Test results show that: the signal generator is expected to reach the design requirements of the performance and various indexes, significantly better with the traditional signal generator.Key words: Single-chip microcomputer;DDS;signal generator目录1引言 (4)2 系统简介 (5)2.1 方案论证与选择 (5)2.1.1信号发生模块的方案选择 (5)2.1.2单片机模块的方案选择 (5)2.1.3显示模块的方案选择 (5)2.1.4键盘模块的方案选择 (6)2.2 单片机介绍 (6)2.3 单片机的主要应用领域 (6)2.4 AT89S52单片机 (7)2.4.1 AT89S52单片机性能与特点 (7)2.4.2 AT89S52单片机引脚说明 (7)3 DDS技术介绍 (11)3.1直接数字式频率合成技术的原理 (11)3.2 DDS输出信号的的频谱特性 (12)3.2.1理想情况下DDS输出的频谱特性 (12)3.2.2非理想情况下DDS输出的频谱特性 (15)3.3 AD9833芯片简介 (16)3.3.1 AD9833的功能及特点 (16)3.3.2 AD9833的引脚及功能 (18)3.3.3 AD9833的内部寄存器功能 (18)4硬件电路的设计 (20)4.1 总体方案的设计 (20)4.2 电源电路的设计 (20)4.2.1 变压器的选择 (21)4.2.2 整流电路 (21)4.2.3 滤波电容的选择 (22)4.2.4 稳压电路 (23)4.3单片机电路的设计 (25)4.3.1振荡电路的设计 (25)4.3.2 复位电路的设计 (25)4.4 DDS电路的设计 (26)4.5按键电路的设计 (26)4.6幅度调节电路的设计 (27)4.6显示电路的设计 (28)5软件设计 (31)5.1 主程序 (31)5.2 DDS AD9833子程序 (31)5.3按键程序 (32)6电路的焊接和调试 (33)6.1电路的焊接 (33)6.2 DDS的调试 (36)6.3 放大器AD603的调试 (37)7 结论 (38)谢辞.............................................................................................. 错误!未定义书签。

目录引言 (2)一设计任务 (2)1设计内容 (2)2设计要求 (2)二芯片功能介绍 (2)三总体功能图和总原理图 (4)四程序流程图 (5)1 锯齿波程序流程图 (5)2 三角波程序流程图 (5)3 梯形波程序流程图 (6)4 方波程序流程图 (7)5 正弦波程序流程图 (8)6 整体程序流程图 (9)五程序设计 (10)六仿真测试 (13)七总结与体会 (16)八参考文献 (16)九致谢....................................................................... 错误!未定义书签。

引言信号发生器又称信号源或振荡器,在生产实践和科技领域中有着广泛的应用。

这次的设计分为五个模块:单片机控制及显示模块、数模转换模块、波形产生模块、输出显示模块、电源模块。

使用AT98C52作为主控台结合芯片DAC0832产生1HZ-10HZ频率可调的五种信号波(锯齿波、三角波、方波、梯形波、正弦波)。

这几种波形有几个开关控制,可以随意进行切换,十分方便。

另外,波形的频率和振幅也可以通过开关进行更改。

可以说这次的设计操作简单,内容丰富,而且电路快捷明了。

1设计任务1.1设计内容以单片机为基础,设计并开发能输出多种波形(正弦波、三角波、锯齿波、梯形波等),且频率、幅度可变的函数发生器。

1.2设计要求设计借口电路,将这些外设构成一个简单的单片机应用系统,画出接口的连接图和仿真图,并编写出控制波形的程序。

2芯片功能介绍2.1、DAC0832芯片介绍:DAC0832为一个8位D/A转换器,单电源供电,在+5~+15V范围内均可正常工作。

基准电压的范围为±10V,电流建立时间为1μs,CMOS工艺,低功耗20mW。

DAC0832的内部结构框图如下图所示。

图2.1 DAC0832的内部结构框图2.2 DAC0832的外部引脚及功能介绍图如下:图2.2 DAC0832介绍2.3 DAC0832的应用:DAC0832一是用作单极性电压输出,二是用作双极性电压输出,最后是用作程控放大器。

辽东学院信息技术学院《单片机原理与接口技术》课程设计报告函数发生器设计学生姓名:学号: 0915110602班级: B1106专业:电子信息工程指导教师:2014年07月【摘要】本设计是一个基于单片机的简易函数发生器,函数信号发生器的设计方法有多种,利用单片机设计的函数信号发生器具有编程灵活、显示清楚等优点。

它能产生方波、正弦波、锯齿波和三角波四种波形。

在编程语言上,此处选择了简单易行的C语言程序。

经过不断改进,现在已实现了所有与其目标。

关键词:单片机函数发生波形 C语言目录绪论......................................................... .1 1系统工作原理. (2)1.1 功能说明 (2)1.2基本原理 (2)2 硬件设计 (3)2.1 单片机最小系统单元 (3)2.2波形产生模块设计 (7)2.3 独立式键盘模块设计 (9)3 软件设计 (10)3.1 主程序流程图 (11)4 结论 (11)5.调试 (15)参考文献........................................ 错误!未定义书签。

附录A 源程序 (16)附录B 系统原理图 (22)绪论1、单片机概述随着大规模集成电路技术的发展,中央处理器(CPU)、随机存取存储器(RAM)、只读存储器(ROM)、(I/O)接口、定时器/计数器和串行通信接口,以及其他一些计算机外围电路等均可集成在一块芯片上构成单片微型计算机,简称为单片机。

单片机具有体积小、成本低,性能稳定、使用寿命长等特点。

其最明显的优势就是可以嵌入到各种仪器、设备中,这是其他计算机和网络都无法做到的。

2、信号发生器的分类信号发生器应用广泛,种类繁多,性能各异,分类也不尽一致。

按照频率范围分类可以分为:超低频信号发生器、低频信号发生器、视频信号发生器、高频波形发生器、甚高频波形发生器和超高频信号发生器。

开题报告,单片机实现一个简单的信号发生器第一篇:开题报告, 单片机实现一个简单的信号发生器单片机实现一个简单的信号发生器一、课题来源及研究的目的和意义1.1课题来源教师虚拟。

1.2研究的目的及意义本课题是基于单片机的信号发生器的设计。

研究本课题可以熟悉c 语言,MATLAB及相关电子器件的功能和用法。

通过对单片机硬件、软件的设计,及硬件与软件的联调后可以进一步熟悉相关的知识,提高利用所学知识解决实际问题的能力。

二、课题所涉及的问题在国内(外)研究现状分析单片微型计算机,简称单片机,是微型计算机的一个分支。

采用超大规模技术把具有数据处理能力(如算术运算、逻辑运算、数据传送、中断处理)的微处理器,随机存取数据存储器,只读程序存储器,输入输出电路等电路集成到一块单块芯片上,构成一个体积小,然而功能较完善的计算机系统。

这些电路能在软件的控制下准确、迅速、高效地完成程序设计者事先规定的任务。

单片机诞生20世纪70年代。

当时微电子技术正处于发展阶段,集成电路也属于中规模发展时期,各种新材料新工艺尚未成熟,单片机仍处在初级的发展阶段,元件集成规模还比较小,功能比较简单。

1976年INTEL公司推出了MCS-48单片机,这个时期的单片机才是真正的8位单片微型计算机,并推向市场。

到了80年代初,单片机已发展到了高性能阶段,像INTEL公司的MCS-51系列。

九十年代以后,单片机获得了飞速的发展,世界各大半导体公司相继开发了功能更为强大的单片机。

美国Microchip公司发布了一种完全不兼容MCS-51的新一代PIC系列单片机,引起了业界的广泛关注,特别它的产品只有33条精简指令集吸引了不少用户。

1990年美国INTEL公司推出了80960超级32位单片机引起了计算机界的轰动,产品相继投放市场,成为单片机发展史上又一个重要的里程碑。

我国的单片机应用始于80年代,虽然发展迅速,但相对于世界市场我国的占有率还很低。

到目前为止,由于我国的微电子技术和制造工艺都比较落后及国外单片机的竞争等原因,我国还没有设计生产出自己的单片机。

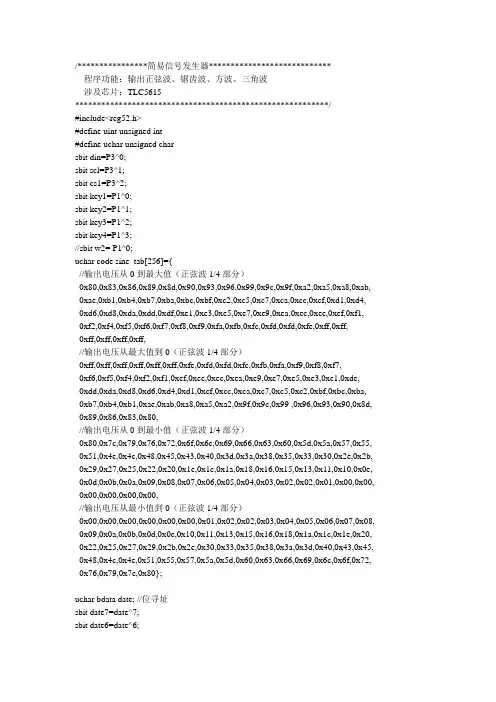

/****************简易信号发生器****************************程序功能:输出正弦波、锯齿波、方波、三角波涉及芯片:TLC5615**********************************************************/#include<reg52.h>#define uint unsigned int#define uchar unsigned charsbit din=P3^0;sbit scl=P3^1;sbit cs1=P3^2;sbit key1=P1^0;sbit key2=P1^1;sbit key3=P1^2;sbit key4=P1^3;//sbit w2= P1^0;uchar code sine_tab[256]={//输出电压从0到最大值(正弦波1/4部分)0x80,0x83,0x86,0x89,0x8d,0x90,0x93,0x96,0x99,0x9c,0x9f,0xa2,0xa5,0xa8,0xab, 0xae,0xb1,0xb4,0xb7,0xba,0xbc,0xbf,0xc2,0xc5,0xc7,0xca,0xcc,0xcf,0xd1,0xd4, 0xd6,0xd8,0xda,0xdd,0xdf,0xe1,0xe3,0xe5,0xe7,0xe9,0xea,0xec,0xee,0xef,0xf1,0xf2,0xf4,0xf5,0xf6,0xf7,0xf8,0xf9,0xfa,0xfb,0xfc,0xfd,0xfd,0xfe,0xff,0xff,0xff,0xff,0xff,0xff,//输出电压从最大值到0(正弦波1/4部分)0xff,0xff,0xff,0xff,0xff,0xff,0xfe,0xfd,0xfd,0xfc,0xfb,0xfa,0xf9,0xf8,0xf7,0xf6,0xf5,0xf4,0xf2,0xf1,0xef,0xee,0xec,0xea,0xe9,0xe7,0xe5,0xe3,0xe1,0xde,0xdd,0xda,0xd8,0xd6,0xd4,0xd1,0xcf,0xcc,0xca,0xc7,0xc5,0xc2,0xbf,0xbc,0xba, 0xb7,0xb4,0xb1,0xae,0xab,0xa8,0xa5,0xa2,0x9f,0x9c,0x99 ,0x96,0x93,0x90,0x8d, 0x89,0x86,0x83,0x80,//输出电压从0到最小值(正弦波1/4部分)0x80,0x7c,0x79,0x76,0x72,0x6f,0x6c,0x69,0x66,0x63,0x60,0x5d,0x5a,0x57,0x55, 0x51,0x4e,0x4c,0x48,0x45,0x43,0x40,0x3d,0x3a,0x38,0x35,0x33,0x30,0x2e,0x2b, 0x29,0x27,0x25,0x22,0x20,0x1e,0x1c,0x1a,0x18,0x16,0x15,0x13,0x11,0x10,0x0e, 0x0d,0x0b,0x0a,0x09,0x08,0x07,0x06,0x05,0x04,0x03,0x02,0x02,0x01,0x00,0x00, 0x00,0x00,0x00,0x00,//输出电压从最小值到0(正弦波1/4部分)0x00,0x00,0x00,0x00,0x00,0x00,0x01,0x02,0x02,0x03,0x04,0x05,0x06,0x07,0x08, 0x09,0x0a,0x0b,0x0d,0x0e,0x10,0x11,0x13,0x15,0x16,0x18,0x1a,0x1c,0x1e,0x20, 0x22,0x25,0x27,0x29,0x2b,0x2e,0x30,0x33,0x35,0x38,0x3a,0x3d,0x40,0x43,0x45, 0x48,0x4c,0x4e,0x51,0x55,0x57,0x5a,0x5d,0x60,0x63,0x66,0x69,0x6c,0x6f,0x72, 0x76,0x79,0x7c,0x80};uchar bdata date; //位寻址sbit date7=date^7;sbit date6=date^6;sbit date5=date^5;sbit date4=date^4;sbit date3=date^3;sbit date2=date^2;sbit date1=date^1;sbit date0=date^0;void delay(uint t){while(t--);}void write_sip5615(uchar k) {date=k;din=date7;scl=0;scl=1;din=date6;scl=0;scl=1;din=date5;scl=0;scl=1;din=date4;scl=0;scl=1;din=date3;scl=0;scl=1;din=date2;scl=0;scl=1;din=date1;scl=0;scl=1;din=date0;scl=0;}void write_5615(uint k){k<<=2;cs1=0;write_sip5615(k>>8);//送高八位write_sip5615(k);//送低八位cs1=1;}void main(){uint k1=0,k2=0,k3=0,k4=0,i=0,j=0,x=0,z,p;while(1){/* w2=0;delay(500);w2=1;delay(500); */if(key1==0)//按键1检测{k1=1;k2=0,k3=0,k4=0;while(!key1);}if(key2==0) //按键2检测{k2=1;k3=0,k1=0,k4=0;while(!key2);}if(key3==0)//按键3检测{k3=1;k1=0,k2=0,k4=0;while(!key1);}if(key4==0)//按键4检测{k4=1;k1=0,k2=0,k3=0;while(!key2);}if(k1==1)//正弦波write_5615(sine_tab[i]);i++;delay(100);if(i==256)i=0;}if(k2==1)//锯齿波{write_5615(j);j++;delay(100);if(j==250)j=0;}if(k3==1)//方波(次处用单片机的I/O效果更好){write_5615(10);delay(10000);write_5615(200);delay(10000);}if(k4==1)//三角波{for(z=0;z<301;z++){delay(50);write_5615(z);if(z==300){for(p=300;p>0;p--){if(p==0)break;write_5615(p);delay(50);}}}}}}。

基于单片机的智能信号发生器设计基于单片机的智能信号发生器设计摘要本文所设计的系统是利用AT89S52单片机和数模转换器件DAC0832产生所需不同信号的低频信号源,即采用AT89S52 单片机作为控制核心,而在外围采用数字/模拟转换电路(DAC0832)、运放电路(LM324)、按键和LED显示灯电路等,通过按键可控制产生方波、锯齿波、三角波、正弦波,同时用LED显示灯指示对应的波形输出。

文中简要介绍了DAC0832数模转换器的结构原理和使用方法,单片机AT89S52的基础理论,以及与电路设计有关的各种芯片,并着重介绍了利用单片机控制D/A 转换器产生上述信号的硬件电路设计和软件编程。

本文所设计的系统设计简单、性能优良、性价比高,可用于多种需要低频信号源的场所,具有一定的实用性。

关键词单片机信号发生器D/A转换运算放大基于单片机的智能信号发生器设计Design of intelligent signal generator based on single chipABSTRACTThis article by design of system is using AT89S52 single tablets machine and array die conversion devices DAC0832 produced by required different signal of low frequency signal source, is used AT89S52 single tablets machine as control core, and in perimeter used digital/simulation conversion circuit (DAC0832), and operational amplifiercircuit (LM324), and press and LED display lamp circuit,, by press can control produced square, and sawtooth wave, and triangle wave, and sine wave, while with LED display lamp indicates corresponds of waveform output.Brief introduction of DAC0832 in the text structure and the use method of digital-analog converter, basic theory of single-chip microcomputer AT89S52, and chip and circuit design, and focus on using d/a converter producing such signals on single chip microcomputer design of hardware circuit and software programming.This simple system designed by design, excellent performance, cost-effective, places with low frequency signal source can be used for a variety of needs, with a certain degree of practicality.Key words The single chip computer The signal generator D/ A conversion Operational amplifier基于单片机的智能信号发生器设计目录中文摘要 (I)英文摘要 (II)1 绪论 (1)2 系统设计 (3)2.1 系统方案的选择 (3)2.2 控制芯片的选择 (3)3 系统硬件设计 (4)3.1 基本原理 (4)3.2 单片机介绍及资源分配 (4)3.2.1 单片机的介绍 (4)3.2.2 资源分配 (9)3.3 各部分电路原理 (9)3.3.1 键盘电路原理 (9)3.3.2 LED显示电路原理 (11)3.3.3 DAC0832芯片原理 (12)3.3.4 LM324工作原理 (15)4 系统软件设计 (17)4.1 主程序流程图 (17)4.2 子程序流程图 (18)5 测试结果 (23)6 结论 (25)致谢 .................................................................................................. 错误!未定义书签。

单片机简易信号发生器课程设计

单片机简易信号发生器是一种基于单片机技术的电子设备,它可以产生各种不同的信号波形,如正弦波、方波、三角波等。

在电子工程领域中,信号发生器是一种非常重要的测试仪器,它可以用于测试各种电子设备的性能和参数,如放大器、滤波器、振荡器等。

在本次课程设计中,我们将使用单片机技术设计一款简易的信号发生器。

首先,我们需要选择一款适合的单片机芯片,如AT89C51、PIC16F877A等。

然后,我们需要编写相应的程序代码,实现信号波形的产生和输出。

在程序设计中,我们可以使用定时器和计数器来实现不同频率的信号波形产生。

例如,我们可以使用定时器产生一个固定频率的方波信号,然后通过改变计数器的值来改变方波的占空比。

同样地,我们也可以使用定时器和计数器来产生正弦波和三角波等不同形式的信号波形。

在硬件设计方面,我们需要选择适合的电路元件来实现信号波形的输出。

例如,我们可以使用DAC芯片来将数字信号转换为模拟信号,然后通过放大器和滤波器来输出信号波形。

当然,我们也可以选择其他的电路方案来实现信号波形的输出。

单片机简易信号发生器是一款非常有用的电子设备,它可以用于各种电子设备的测试和调试。

通过本次课程设计,我们可以学习到单

片机技术的应用和信号发生器的原理,提高我们的电子技术水平。

创新性实验研究报告实验项目名称_简易函数信号发生器四、实验内容1、运用keil软件对程序进行编写,运行程序,并进行程序修改。

2、运用protues软件进行硬件电路仿真设计。

3、将程序下载到仿真单片机中,并观测输出波形。

4、对程序进行修改,再次运行仿真软件,直到输出理想的波形。

5、仿照仿真软件进行硬件电路的焊接。

6、将程序下载到单片机,并用示波器测试输出波形。

7、对程序进行修改,直到输出满意的波形为止。

3、实验步骤1、首先打开keil软件.2、运用keil软件对程序进行编写,程序见附件。

3、打开protues软件.4、运用protues软件对硬件电路进行设计。

9C51单片机是该信号发生器的核心,具有2个定时器,32个并行I/O口,1个串行I/O口,5个中断源。

由于本设计功能简单,数据处理容易,数据存储空间也足够,因为我们采用了片选法选择芯片,进行芯片的选择和地址的译码。

在单片机最小最小系统中,单片机从P1口接收来自键盘的信号,并通过P0口输出控制信号,通过DA转换芯片最终由示波器显示输出波形。

单片机引脚分配如下:�XTAL1,XTAL2:外接晶振,产生时钟信号。

�RST:复位电路;�P2口:8位数字信号输出输出,外接DAC0832;�P3.6口和P3.7口:DAC0832的时钟信号;单片机模块单片机输出的是数字信号,因为要得到模拟信号的波形就必须对其进行数模转换。

我们采用了DAC0832数模转换器,该芯片具由8位输入锁存器、8位DAC寄存器、8位D/A转换器及转换控制电路四部分构成。

由于其输出为电流输出,因为外加运算放大器LM324使之转换为电压输出。

最后通过示波器显示输出的波形。

数模转换模块运放模块整体硬件电路图五、实验结果与分析1、实验现象、数据记录仿真波形2、对实验现象、数据及观察结果的分析与讨论:经过观察调试,再观察,再调试,最终输出的波形较为理想。

此次试验经过一系列的调试,最终输出的波形为正弦波、方波、三角波。

基于单片机的信号发生器设计

基于单片机的信号发生器是一种能够产生不同频率、幅度和波形的信号的设备。

它在电子实验、通信系统测试和音频设备调试中起到重要作用。

本文将介绍信号发生器的工作原理、设计要点以及一些应用案例。

信号发生器的核心部分是单片机,它是一种集成了处理器、存储器和输入输出接口的微型计算机。

单片机通过程序控制产生不同频率的脉冲信号,并通过数模转换器将数字信号转换为模拟信号输出。

为了保证信号的准确性和稳定性,还需要使用精密的时钟电路和滤波电路。

在设计信号发生器时,需要考虑以下几个要点。

首先是频率范围和分辨率的选择。

不同的应用场景需要不同的频率范围,而分辨率则决定了信号的精度。

其次是波形的选择和产生方式。

常见的波形有正弦波、方波、三角波等,可以通过查表、数学模拟或直接输出等方式产生。

此外,还需要考虑信号的幅度调节和输出阻抗匹配等问题。

信号发生器在实际应用中有着广泛的用途。

在电子实验中,它可以用来测试电路的频率响应、相位特性和失真情况。

在通信系统测试中,它可以模拟各种信号场景,用来验证系统的性能和稳定性。

在音频设备调试中,它可以生成各种音频信号,用来测试音响设备的音质和效果。

基于单片机的信号发生器是一种功能强大的设备,它能够产生多种频率、幅度和波形的信号,用于电子实验、通信系统测试和音频设备调试等领域。

通过合理的设计和实现,可以满足不同应用场景的需求,并提高工作效率和准确性。

希望本文对读者理解信号发生器的工作原理和设计要点有所帮助。

基于AT89S51单片机的数字信号发生器【摘要】智能仪器的出现,极大地扩充了传统仪器的应用范围。

智能仪器凭借其体积小、功能强、功耗低等优势,迅速地在家用电器、科研单位和工业企业中得到了广泛的应用。

本系统是基于AT89S51单片机设计的数字式波形发生器。

采用AT89S51作为系统的控制核心,外围电路采用数字/模拟转换电路(DAC0832),运放电路(MC1458),按键,ISP接口等。

通过按键控制切换产生正弦波,锯齿波,三角波,方波,各类型信号的频率统一为100HZ,而幅值在-5V~+5V范围内可调。

本设计电路原理简单,性能较好,具有一定的实用性和参考价值。

【关键词】单片机 ,波形发生器,D/A电路DIGITAL SIGNAL GENERATOR DESIGN BASED ON AT89S51【ABSTRACT】The emergence of intelligent machines, which greatly expanded the scope of application of traditional instruments. Intelligent instrument, with its small size, powerful, low-power advantages of home appliances quickly, research institutes and industrial enterprises has been widely used.The system is a digital waveform generator based on single chip computer. AT89S51 is used as a control core. The system is composed by digital/analog conversion (DAC0832),imply circuit (MC1458),button ISP inferface and LED lights. It can generate square triangle and sine wave,with LED display .The frequency of various types of signal unity of 100HZ, but the amplitude in the-5V ~ +5 V range adjustable. The circuit design is simple, better performance, has some practical and reference value.【KEY WORDS】the single chip computer , the signal generator , D/A conversion目录绪论 (9)1. 波形发生器现状 (9)2. 单片机在波形发生器中的运用 (9)第一章系统设计 (10)1. 系统要求 (11)2. 系统方案选择与论证 (11)3. 系统设计原理与思路 (11)第二章硬件电路的设计 (12)1. AT89S51的介绍 (12)2. 资源分配 (15)3. 最小单片机系统的设计 (15)4. 各模块电路的设计 (17)5. ISP接口 (23)第三章软件设计 (24)1. 主程序的设计 (25)2. 锯齿波程序的设计 (25)3. 三角波程序的设计 (26)4. 正弦波程序的设计 (27)5. 方波程序的设计 (28)第四章测试仿真 (29)1. 软件仿真 (29)2. 仿真结论分析 (30)3. 硬件测试结论分析 (31)绪论1.波形发生器现状波形发生器作为一种常用的应用电子仪器设备,传统的波形发生器可以完全用硬件电路搭建,如应用555振荡电路可以产生正弦波,三角波,方波等波形,传统的波形发生器多采用这种方式设计,这种方式不应用单片机,但是这种方式存在波形质量差,控制难,可调范围小,电路复杂和体积大等缺点,在科学研究和生产实践中,如工业过程控制,生物医学,地震模拟震动等领域往往需要低频信号源,而由硬件搭建的波形发生器效果往往达不到好的效果,而且低频信号源所需要的RC很大,大电阻,大电容在制作上有困难,参数的精度也难以保证,而且体积大,漏电,体积大是该类波形发生器的显著缺点。

引言信号发生器又称为信号源,其工作原理是利用频率合成技术提供各种频率、波形和输出电平电信号,常用作测试电子设备的仪器,广泛应用于通信、雷达、测控领域,电子以及现代化仪器仪表等领域,在电子参数的测量过程当中,信号发生器是必不可少的仪器。

目前大多数的波形信号发生器价格都较高,体积大,二次开发复杂,使用进口元器件较多。

单片机,由CPU、定时器和多接口等器件组成的自动化单片微型计算机。

其作为一种微型控制器,主要有体积小、低功耗、控制功能强,功能齐全和使用方便等优点。

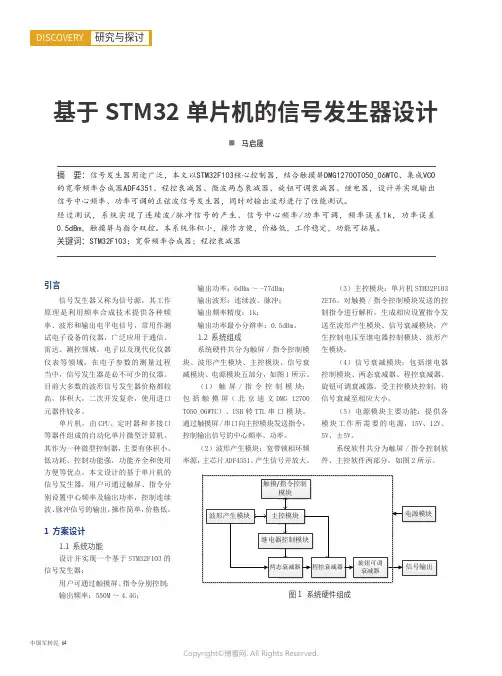

本文设计的基于单片机的信号发生器,用户可通过触屏、指令分别设置中心频率及输出功率,控制连续波、脉冲信号的输出,操作简单,价格低。

1 方案设计1.1 系统功能设计并实现一个基于STM32F103的信号发生器:用户可通过触摸屏、指令分别控制;输出频率:550M~4.4G;输出功率:6dBm~-77dBm;输出波形:连续波、脉冲;输出频率精度:1k;输出功率最小分辨率:0.5dBm。

1.2 系统组成系统硬件共分为触屏/指令控制模块、波形产生模块、主控模块、信号衰减模块、电源模块五部分,如图1所示。

(1)触屏/指令控制模块:包括触摸屏(北京迪文DMG 12700T050_06WTC)、USB转TTL串口模块。

通过触摸屏/串口向主控模块发送指令,控制输出信号的中心频率、功率。

(2)波形产生模块:宽带锁相环频率源,主芯片ADF4351。

产生信号并放大。

(3)主控模块:单片机STM32F103ZET6。

对触摸/指令控制模块发送的控制指令进行解析,生成相应设置指令发送至波形产生模块、信号衰减模块,产生控制电压至继电器控制模块、波形产生模块。

(4)信号衰减模块:包括继电器控制模块、两态衰减器、程控衰减器、旋钮可调衰减器。

受主控模块控制,将信号衰减至相应大小。

(5)电源模块主要功能:提供各模块工作所需要的电源,15V、12V、5V、±5V。

系统软件共分为触屏/指令控制软件、主控软件两部分,如图2所示。

基于单片机的函数信号发生器毕业设计完整版本毕业设计旨在设计一个基于单片机的函数信号发生器,以满足工程实践需求。

设计的信号发生器将具有以下特点:能够输出多种波形、具备可调频率和幅度的功能、具备稳定性和高精度等。

首先,信号发生器的硬件设计包括信号源、滤波电路、放大电路和输出电路。

信号源负责产生基本的信号波形,可以通过设置单片机的IO口电平高低来控制信号的波形。

滤波电路和放大电路主要负责对信号进行滤波和放大处理,以确保输出的波形质量和幅度稳定性。

输出电路则是将放大后的信号输出到外部设备上。

其次,信号发生器的软件设计主要是通过编程控制单片机的IO口来实现波形的生成和调节。

编程方面,可以使用C语言或者汇编语言来编写程序,实现波形的输出、频率和幅度的调节等功能。

在程序的运行过程中,需要通过控制IO口电平的高低来控制信号的形状。

同时,可以使用按键或旋钮等外部输入设备来实现对频率和幅度的调节,以满足用户的实际需求。

最后,在设计的过程中需要注意信号发生器的稳定性和精度。

稳定性主要包括信号的频率稳定性和幅度稳定性。

频率稳定性可以通过使用高精度的时钟源和精确的频率分频电路来实现。

幅度稳定性可以通过使用高精度的放大电路和自动增益控制电路来实现。

精度方面,则可以通过使用高精度的模拟数字转换芯片和时钟源来实现。

总的来说,基于单片机的函数信号发生器在工程实践中具有重要意义。

本设计旨在结合硬件和软件技术,实现一个功能完善、稳定性好、精度高的信号发生器。

通过合理的设计和优化,该信号发生器能够满足工程实践的需求,为相关领域的研究提供信号源支持。

第1章绪论1.1 信号发生器的现状与发展信号发生器是一种常用的信号源,广泛的应用于电子电路、自动控制和科学实验等领域。

它是一种为电子测量和计量工作提供符合严格技术要求的电信号设备。

因此,信号发生器和示波器、电压表、频率计等仪器一样是最普通、最基本的,也是应用最广泛的电子仪器之一,几乎所有的电参量的测量都需要用到信号发生器。

自六十年代以来,信号发生器就有了迅速的发展,出现了函数发生器、扫描信号发生器、合成信号发生器、控制信号发生器等种类。

各种信号发生器的主要性能指标也都有了大幅度的提高,同时在简化机械结构、小型化、多功能等各方面也有了显著的发展。

1.2 设计内容及方案的确定本课题要求以MCS-51系列单片机为核心,设计一个简易低频信号发生器。

要求能输出0.1~50HZ的正弦波、三角波和方波信号,能方便的用键盘选择不同的输出并在LED显示器上显示。

单片机通过查表的方法完成波形数据要求,输出的正弦波、三角波和方波信号频率在0.1~50HZ可调,系统有启动、调频和不同波形选择按键,转速显示要求至少4位。

根据要求我们组讨论如下:直接采用8位DA转换芯片,让单片机对8位DA芯片进行控制,从而输出波形。

第2章 基于单片机的简易低频信号发生器的设计2.1 总体设计框图图2.1.1总体设计框图如方框图所示根据要求我们组讨论如下:通过C 程序的编译,频率档位选择按键UP 、DOWN 以及波形选择按键SWITCH ,通过数码管显示频率档位和波形。

并且通过DAC0832实现数模转换,最后用示波器观察输出的结果。

2.2 单片机结构及系统工作原理数模转换器器工作原理就是模拟信号数字化的逆过程,模拟信号数字化通过采样、量化、编码完成,那么数字信号模拟化的过程读取二进制码、二进制码权值相加、输出一个总的电流或电压。

这其实就是一个模拟电子计数中的加法器。

量化电平个数相对于数模转换的分辨率,对于低频低成本的信号发生器,为了简化程序设计,所以直接采用8位DA转换芯片DAC0832,让单片机AT89C51对8位DA芯片进行控制,从而输出波形。

摘要本文以STC89C51单片机为核心设计了一个低频函数信号发生器。

信号发生器采用数字波形合成技术,通过硬件电路和软件程序相结合,可输出自定义波形,如正弦波、方波、三角波、三角波、梯形波及其他任意波形,波形的频率和幅度在一定范围内可任意改变。

波形和频率的改变通过软件控制,幅度的改变通过硬件实现。

介绍了波形的生成原理、硬件电路和软件部分的设计原理。

本系统可以产生最高频率798.6HZ的波形。

该信号发生器具有体积小、价格低、性能稳定、功能齐全的优点。

关键词:低频信号发生器;单片机;D /A转换;1设计选题及任务设计题目:基于单片机的信号发生器的设计与实现任务与要求:设计一个由单片机控制的信号发生器。

运用单片机系统控制产生多种波形,这些波形包括方波、三角波、锯齿波、正弦波等。

信号发生器所产生的波形的频率、幅度均可调节。

并可通过软件任意改变信号的波形。

基本要求:1. 产生三种以上波形。

如正弦波、三角波、矩形波等。

2.最大频率不低于 500Hz。

并且频率可按一定规律调节,如周期按1T,2T,3T,4T或1T,2T,4T,8T变化。

3.幅度可调,峰峰值在0——5V之间变化。

扩展要求:产生更多的频率和波形。

2系统概述2.1方案论证和比较2.1.1总体方案:方案一:采用模拟电路搭建函数信号发生器,它可以同时产生方波、三角波、正弦波。

但是这种模块产生的不能产生任意的波形(例如梯形波),并且频率调节很不方便。

方案二:采用锁相式频率合成器,利用锁相环,将压控振荡器(VCO)的输出频率锁定在所需频率上,该方案性能良好,但难以达到输出频率覆盖系数的要求,且电路复杂。

方案三:使用集成信号发生器发生芯片,例如AD9854,它可以生成最高几十MHZ的波形。

但是该方案也不能产生任意波形(例如梯形波),并且价格昂贵。

方案四:采用AT89C51单片机和DAC0832数模转换器生成波形,加上一个低通滤波器,生成的波形比较纯净。

它的特点是可产生任意波形,频率容易调节,频率能达到设计的500HZ以上。

简易信号发生器1引言信号发生器又称信号源或振荡器,在生产实践和科技领域中有着广泛的应用。

它能够产生多种波形,如三角波、锯齿波、矩形波(含方波)、正弦波等,在电路实验和设备检测中具有十分广泛的用途。

例如在通信、广播、电视系统中,都需要射频(高频)发射,这里的射频波就是载波,把音频(低频)、视频信号或脉冲信号运载出去,就需要能够产生高频的振荡器。

在工业、农业、生物医学等领域内,如高频感应加热、熔炼、淬火、超声诊断、核磁共振成像等,都需要功率或大或小、频率或高或低的信号发生器。

本设计采用FPGA来设计制作多功能信号发生器。

该信号发生器可以产生锯齿波、三角波、方波等波形。

2 FPGA简介FPGA(Field-Programmable Gate Array)即现场可编程门阵列,它是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物。

它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。

与传统们阵列和掩模可编程门阵列(MPGA)相比,FPGA具有很多的优点,传统门阵列可以用来设计任何电路,但是只能在工厂中一次性编程,而且还需要针对该电路的特定的掩模。

FPGA是标准通用器件。

使用其代替MPGA,可以将设计时间由几个月缩短至几小时,并且使设计更加简单,从而减少了错误修改和设计指标变更的花费。

FPGA器件在结构上,由逻辑功能块排列为阵列,它的结构可以分为三个部分:可编程快CLB(Configurable Logic Blocks)、可编程I/O模块IOB(Input Block)和可编程内部连线PI(Programmable Interconnect)。

CLB在器件中排列为阵列,周围有环形内部连线,IOB分布在四周的管脚上。

FPGA也存在缺点,FPGA中,每个可编程的点都有电阻和电容。

电阻和电容的使用减慢了信号的传输速度,所以FPGA的速度比传统门阵列要低,而且,FPGA中互联延迟是不可预测的。

基于单片机的信号发生器设计摘要在介绍MAX038 芯片特性的基础上,论述了采用MAX038 芯片设计数字函数信号发生器的原理以及整机的结构设计。

对其振荡频率控制、信号输出幅度控制以及频率和幅度数显的实现作了较详细的论述。

该函数信号发生器可输出三角波,方波和正弦波。

本文重点论述了整机通过D/A转换电路控制MAX038的实现过程,D/A转换电路采用了8位4通道的MAX505来实现。

在幅度的控制上采用数字电位器AD5171,该芯片是I²C总线方式控制,文中给出了I²C总线的读写控制程序。

系统支持按键操作和上位机操作两种模式。

关键词:函数信号;D/A ;单片机控制Design of Signal Generator System Based on SCMZisu zhou(College of Zhangjiajie, Jishou University, Jishou,Hunan 416000)AbstractBased on the introduction of MAX038 , we discussed the principle and the whole frame of the digital function signal generator. We described the control of the oscillatory frequent , amplitude and the digital display in detail. Thegenerator can output three kinds of waves : sine wave , square wave , triangle wave.This text has exposition the mirco-computer controls the D/A electric circuit of conversion realize the process. In D/A changing electric circuit adopt the 8 bit 4 channel come to realize. Porentiometer AD5171 is adopted in the control of length. This chip is that I²C bus control way. This system supports key-control or computer-control modes.Key words : function signal ;D/A ;single - chip microprocessor control ;目录绪论 (1)第一章系统概述和设计方案 (2)1.1论文的内容和组织 (2)1.2方案选择 (2)1.3信号发生芯片选择 (2)1.4方案框图设计及基本控制原理 (3)1.5.1 频段控制调整参数计算 (4)1.5.2频率控制细调参数计算 (5)1.5.3占空比的数字控制参数计算 (6)1.5.4幅度的数控参数实现 (6)第二章系统硬件设计 (8)2.1 系统总体设计 (8)2.2单片机介绍及外围电路 (8)2.3 D/A转换电路(频率,占空比控制电路) (10)2.3.1MAX505的引脚描述 (10)2.3.2MAX505的内部结构及原理 (11)2.3.3 D/A转换电路的电路说明 (13)2.4频段选择电路 (14)2.5 幅度控制电路 (15)2.6 键盘电路 (17)2.7电源电路 (18)第三章系统软件流程图设计 (20)3.1 主程序流程图 (20)3.2频段处理子程序 (21)3.3频率处理子程序 (21)3.4幅度处理子程序 (22)系统分析与总结 (23)参考文献 (24)附录 (25)绪论基于单片机的信号发生器设计,该课题的设计目的是充分运用大学期间所学的专业知识,考察现在正在使用的信号发生器的基本功能,完成一个基本的实际系统的设计全过程。

基于单片机的方波信号发生器设计为了实现方波信号的发生器,我们可以使用单片机来实现,单片机可以通过编程来控制方波信号的频率和占空比。

在这里,我将介绍一种基于单片机的方波信号发生器的设计。

首先,我们需要选择一个合适的单片机来作为我们的控制器。

常用的单片机有Arduino、STM32等。

在这里,我们选择使用Arduino Uno作为控制器。

Arduino Uno是一种开源的微控制器板,使用ATmega328P芯片,具有易用性和良好的稳定性。

接下来,我们需要连接一块电路板用于输出方波信号。

为了实现方波信号的生成,我们可以使用一个555定时器芯片来实现。

555定时器可以方便地产生方波信号。

我们将在Arduino Uno和555定时器之间进行串联连接,Arduino Uno将通过编程来控制555定时器的工作。

接下来,我们需要编写Arduino的程序来控制方波信号的频率和占空比。

我们可以使用Arduino的PWM输出功能来控制方波信号的频率。

通过调整PWM的占空比,我们可以控制方波信号的占空比。

以下是一个简单的Arduino程序示例:```c//定义信号输出引脚#define SIGNAL_PIN 9void setu//将信号输出引脚设为输出模式pinMode(SIGNAL_PIN, OUTPUT);void loo//设置PWM频率为1kHzint frequency = 1000;//设置PWM占空比为50%int dutyCycle = 50;//计算PWM周期//计算PWM高电平时间int highTime = period * dutyCycle / 100;while (true)//输出高电平digitalWrite(SIGNAL_PIN, HIGH);delayMicroseconds(highTime);//输出低电平digitalWrite(SIGNAL_PIN, LOW);delayMicroseconds(period - highTime);}```在这个示例程序中,我们定义了信号输出引脚为9号引脚,在setup 函数中将其设为输出模式。

辽东学院信息技术学院《可编程逻辑器件原理及应用》教学实习报告简易信号发生器学生姓名:杨刚学号: 0915110619班级: B1106专业:电子信息工程指导教师:张俊芳2014年07月简易信号发生器1引言信号发生器又称信号源或振荡器,在生产实践和科技领域中有着广泛的应用。

它能够产生多种波形,如三角波、锯齿波、矩形波(含方波)、正弦波等,在电路实验和设备检测中具有十分广泛的用途。

例如在通信、广播、电视系统中,都需要射频(高频)发射,这里的射频波就是载波,把音频(低频)、视频信号或脉冲信号运载出去,就需要能够产生高频的振荡器。

在工业、农业、生物医学等领域内,如高频感应加热、熔炼、淬火、超声诊断、核磁共振成像等,都需要功率或大或小、频率或高或低的信号发生器。

本设计采用FPGA来设计制作多功能信号发生器。

该信号发生器可以产生锯齿波、三角波、方波等波形。

2 FPGA简介FPGA(Field-Programmable Gate Array)即现场可编程门阵列,它是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物。

它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。

与传统们阵列和掩模可编程门阵列(MPGA)相比,FPGA具有很多的优点,传统门阵列可以用来设计任何电路,但是只能在工厂中一次性编程,而且还需要针对该电路的特定的掩模。

FPGA是标准通用器件。

使用其代替MPGA,可以将设计时间由几个月缩短至几小时,并且使设计更加简单,从而减少了错误修改和设计指标变更的花费。

FPGA器件在结构上,由逻辑功能块排列为阵列,它的结构可以分为三个部分:可编程快CLB(Configurable Logic Blocks)、可编程I/O模块IOB(Input Block)和可编程内部连线PI(Programmable Interconnect)。

CLB在器件中排列为阵列,周围有环形内部连线,IOB分布在四周的管脚上。

FPGA也存在缺点,FPGA中,每个可编程的点都有电阻和电容。

电阻和电容的使用减慢了信号的传输速度,所以FPGA的速度比传统门阵列要低,而且,FPGA中互联延迟是不可预测的。

FPGA的基本特点主要有:一、采用FPGA设计ASIC电路,用户不需要投片生产,就能得到合用的芯片。

二、FPGA可做其它全定制或半定制ASIC电路的中试样片。

三、FPGA内部有丰富的触发器和I/O引脚。

四、FPGA是ASIC电路中设计周期最短、开发费用最低、风险最小的器件之一。

五、FPGA采用高速CHMOS工艺,功耗低,可以与CMOS、TTL电平兼容。

使用FPGA时,可以根据不同的配置模式,采用不同的编程方式。

加电时,FPGA芯片将EPROM中数据读入片内编程RAM中,配置完成后,FPGA进入工作状态。

掉电后,FPGA恢复成白片,内部逻辑关系消失,因此,FPGA能够反复使用。

FPGA的编程无须专用的FPGA编程器,只须用通用的EPROM、PROM编程器即可。

当需要修改FPGA功能时,只需换一片EPROM即可。

这样,同一片FPGA,不同的编程数据,可以产生不同的电路功能。

因此,FPGA的使用非常灵活。

FPGA有多种配置模式:并行主模式为一片FPGA 加一片EPROM的方式;主从模式可以支持一片PROM编程多片FPGA;串行模式可以采用串行PROM编程FPGA;外设模式可以将FPGA作为微处理器的外设,由微处理器对其编程。

3 VHDL & Verilog简介VHDL(Very High Speed Integrated Circuit Hardware Description Language,超高速集成电路硬件描述语言)是一种用来描述数字系统行为和结构的硬件描述语言,被广泛的运用于描述和仿真各种数字系统,小到几个门,大到许多复杂集成电路相连的系统。

VHDL诞生于1982年,是由美国国防部开发的一种快速设计电路的工具,目前已经成为IEEE(The Institute of Electrical and Electronics Engineers)的一种工业标准硬件描述语言。

相比传统的电路系统的设计方法,VHDL具有多层次描述系统硬件功能的能力,支持自顶向下(Top to Down)和基于库(Library Based)的设计的特点,因此设计者可以不必了解硬件结构。

从系统设计入手,在顶层进行系统方框图的划分和结构设计,在方框图一级用VHDL对电路的行为进行描述,并进行仿真和纠错,然后在系统一级进行验证,最后再用逻辑综合优化工具生成具体的门级逻辑电路的网表,下载到具体的FPGA器件中去,从而实现可编程的专用集成电路(ASIC)的设计。

Verilog也是一种流行的硬件描述语言,他是由工业界开发的,1984年,Verilog作为一种私用的硬件描述语言,由Gateway Design Automation公司给出,1988年,Synopsis公司为Verilog开发了综合工具。

1995年,Verilog成为IEEE的一个标准。

Verilog 适合算法级,寄存器级,逻辑级,门级和版图级等各个层次的设计和描述。

VHDL的语法是基于ADA语言的,而Verilog的语法是基于C语言的。

由于是基于C 语言,所以它更容易掌握,但是VHDL语言在设计和描述大型系统时具有突出优势。

目前两种语言各占一半市场份额,两种语言都可以满足数字系统设计者的需求。

本设计中采用VHDL语言进行设计。

4 设计工具简介本次设计是基于Altera公司的QuartusII软件。

Quartus II 是Altera公司的综合性PLD开发软件,支持原理图、VHDL、VerilogHDL 以及AHDL(Altera Hardware Description Language)等多种设计输入形式,内嵌自有的综合器以及仿真器,可以完成从设计输入到硬件配置的完整PLD设计流程。

QuartusII支持Altera的IP核,包含了LPM/MegaFuction宏功能模块库,使用它,可以简化设计的复杂性,加快设计速度。

QuartusII平台支持一个工作组环境下的设计要求,其中包括支持基于Internet的协作设计。

此外,QuartusII通过和DSP Builder工具与Matlab/SIMULINK相结合,可以方便地实现各种DSP应用系统;支持Altera的片上可编程系统开发,集系统级设计、嵌入式软件设计、可编程逻辑设计于一体,是一种综性的开发平台。

5 系统设计基于VHDL语言设计一个多功能信号发生器,通过选择输入信号,可以输出递增锯齿波、递减锯齿波、三角波、方波等四种信号。

信号发生器的控制模块可以选用数据选择器实现,4种信号的数据选择可以使用4选1数据选择器实现。

5.1 VHDL程序语言基本设计一个VHDL语言的设计程序描述的是一个电路单元,这个电路单元可以是一个门电路,或者是一个计数器,也可以是一个CPU,一般情况下,一个完整的VHDL语言程序至少包括实体、结构体和程序包三个部分。

实体给出电路单元的外部输入输出接口信号和引用信息,结构体给出了电路单元的内部结构和信号的行为特点,程序包定义在设计结构体和实体中将用到的常数、数据类型、子程序和设计好的电路单元等。

第一部分是程序包,程序包是用VHDL语言编写的共享文件,定义在设计结构体和实体中将要用到的常数、数据类型、子程序和设计好的电路单元等,放在文件目录名称为IEEE的程序包库中。

library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;第二部分是程序的实体,定义电路单元的输入/输出引脚名称。

程序的实体名称可以任意取,但必须与VHDL程序的文件名称相同。

实体的标示符是ENTITY,实体以ENTITY 开头,以END结束。

ENTITY fulladder ISPORT(a,b,Ci:in std_logic;Co,s: out std_logic_vector(7 downto 0));END fulladder;其中,定义了a,b, Ci为输入信号引脚,定义Co,s为输出信号引脚。

第三部分是程序的结构体,具体描述电路的内部结构和逻辑功能。

结构体有三种描述方式,分别是行为(BEHA VIOR)描述方式、数据流(DATAFLOW)描述方式和结构描述方式。

其中数据流描述方式又被称为寄存器(RTL)描述方式。

结构体以表示ARCHITECHTURE开头,以END结尾。

结构体的名称可以任取。

architecture behav of fulladder isBEGINs<=a xor b xor Ci;Co<=(a and b)or(a and Ci)or(b and Ci);END fulladder上面程序段中结构体的描述方式属于程序流描述方式。

以上三段程序是一个完整的VHDL程序段,实现的功能是一位全加器。

5.2 波形发生器设计采用DDS技术可以很方便地产生各种高质量的波形。

DDS技术是从相位概念出发之结合成所需要波形的一种频率合成技术。

以正弦波为例,首先要按照一定的采样点数将正弦波形一个周期的数据信息存于ROM表中,表中包含着一个周期正弦波的数字幅度信息,每个地址对应正弦波中0到360度范围内的一个相位点的幅度值,查找表时即是把输入的地址相位信息映射成正弦波幅度的数字量信号,通过设置的输出端口输出。

在实物设计中,可以使用D/A接口来实现波形信号的输出。

为简化设计过程,本设计并未采用DDS技术,而是采用描点输出的方式,实现波形发生器的设计。

程序中设置一个波形的起始点,经过比较、计算得出波形的其他数值,将这些点依次连续输出,从而实现波形的仿真。

以递增锯齿波为例,首先定义初始点为tmp=“00000000”;在时钟上升沿到来时,执行tmp<=tmp+1;语句,同时将tmp输出,当tmp=“11111111”;时,将tmp值清零,执行下一个循环。

在本设计中,采用QuartusII软件仿真,所以可以通过波形文件直观的反映出输出的数字量的变化情况,以达到波形输出的仿真。

设计中分别对四种波形进行编程,编译无误后,封装生成模块文件,以供在后面的顶层电路设计中使用。

图5-1 四种波形封装图块本设计中设置了四种波形,分别是递增锯齿波、递减锯齿波、三角波、方波。

四种波形通过一个4选1数据选择器来实现选择性输出。

5.3 四选一数据选择器设计可以采用集成四选一数据选择器CT54153/CT74153,也可以使用软件编程生成模块的方式实现数据四选一的功能。