防火墙硬件ASIC、NP、X86、RISC、DSP 、ARM技术介绍

- 格式:doc

- 大小:16.50 KB

- 文档页数:2

ASIC(Application Specific Integrated Circuit)是专用集成电路。

目前,在集成电路界ASIC被认为是一种为专门目的而设计的集成电路。

是指应特定用户要求和特定电子系统的需要而设计、制造的集成电路。

ASIC的特点是面向特定用户的需求,ASIC在批量生产时与通用集成电路相比具有体积更小、功耗更低、可靠性提高、性能提高、保密性增强、成本降低等优点。

ASIC分为全定制和半定制。

全定制设计需要设计者完成所有电路的设计,因此需要大量人力物力,灵活性好但开发效率低下。

如果设计较为理想,全定制能够比半定制的ASIC芯片运行速度更快。

半定制使用库里的标准逻辑单元(Standard Cell),设计时可以从标准逻辑单元库中选择SSI(门电路)、MSI(如加法器、比较器等)、数据通路(如ALU、存储器、总线等)、存储器甚至系统级模块(如乘法器、微控制器等)和IP核,这些逻辑单元已经布局完毕,而且设计得较为可靠,设计者可以较方便地完成系统设计。

现代ASIC常包含整个32-bit处理器,类似ROM、RAM、EEPROM、Flash的存储单元和其他模块. 这样的ASIC常被称为SoC(片上系统)。

FPGA是ASIC的近亲,一般通过原理图、VHDL对数字系统建模,运用EDA软件仿真、综合,生成基于一些标准库的网络表,配置到芯片即可使用。

它与ASIC的区别是用户不需要介入芯片的布局布线和工艺问题,而且可以随时改变其逻辑功能,使用灵活。

NP(network process)网络处理器,是专门为处理数据包而设计的可编程处理器,能够直接完成网络数据处理的一般性任务。

硬件体系结构大多采用高速的接口技术和总线规范,具有较高的I/O能力,包处理能力得到了很大提升。

网络处理器一般具有以下特点:● 并行处理器: 采用多内核并行处理器结构。

片内处理器按任务大致分为核心处理器和转发引擎。

● 专用硬件协处理器: 对要求高速处理的通用功能模块采用专用硬件实现以提高系统性能。

深入了解DSP与ARM的区别与联系这些天正准备找工作的事,对于一些理论上的,或者说表面上的知识需要梳理下,所以有空整理了这篇简陋的比较,权当从另一个侧面理解下这两款主流处理器的特点了吧!DSP:DSP(digital singnal processor)是一种独特的微处理器,有自己的完整指令系统,是以数字信号来处理大量信息的器件。

一个数字信号处理器在一块不大的芯片内包括有控制单元、运算单元、各种寄存器以及一定数量的存储单元等等,在其外围还可以连接若干存储器,并可以与一定数量的外部设备互相通信,有软、硬件的全面功能,本身就是一个微型计算机。

DSP采用的是哈佛设计,即数据总线和地址总线分开,使程序和数据分别存储在两个分开的空间,允许取指令和执行指令完全重叠。

也就是说在执行上一条指令的同时就可取出下一条指令,并进行译码,这大大的提高了微处理器的速度。

另外还允许在程序空间和数据空间之间进行传输,因为增加了器件的灵活性。

其工作原理是接收模拟信号,转换为0或1的数字信号,再对数字信号进行修改、删除、强化,并在其他系统芯片中把数字数据解译回模拟数据或实际环境格式。

它不仅具有可编程性,而且其实时运行速度可达每秒数以千万条复杂指令程序,源源超过通用微处理器,是数字化电子世界中日益重要的电脑芯片。

它的强大数据处理能力和高运行速度,是最值得称道的两大特色。

DSP芯片,由于它运算能力很强,速度很快,体积很小,而且采用软件编程具有高度的灵活性,因此为从事各种复杂的应用提供了一条有效途径。

其主要应用是实时快速地实现各种数字信号处理算法。

根据数字信号处理的要求,DSP芯片一般具有如下主要特点:(1)在一个指令周期内可完成一次乘法和一次加法;(2)程序和数据空间分开,可以同时访问指令和数据;(3)片内具有快速RAM,通常可通过独立的数据总线在两块中同时访问;(4)具有低开销或无开销循环及跳转的硬件支持;(5)快速的中断处理和硬件I/O支持;(6)具有在单周期内操作的多个硬件地址产生器;(7)可以并行执行多个操作;(8)支持流水线操作,使取指、译码和执行等操作可以重叠执行。

ARM与DSP的区别?2007-03-15 18:08 加入收藏转发分享人人网开心网新浪微博搜狐博客百度收藏谷歌收藏qq书签豆瓣淘江湖Facebook Twitter DiggYahoo!Bookmarks我只知道arm是单片机,dsp是专用的做数字信号处理的芯片,由于是硬件处理。

所以速度很快,主要是用在通讯方面。

不过在网上看见这样的文章收益颇多一部分:DSP(digital singnal processor)是一种独特的微处理器,是以数字信号来处理大量信息的器件。

其工作原理是接收模拟信号,转换为0或1的数字信号,再对数字信号进行修改、删除、强化,并在其他系统芯片中把数字数据解译回模拟数据或实际环境格式。

它不仅具有可编程性,而且其实时运行速度可达每秒数以千万条复杂指令程序,源源超过通用微处理器,是数字化电子世界中日益重要的电脑芯片。

它的强大数据处理能力和高运行速度,是最值得称道的两大特色。

DSP芯片,也称数字信号处理器,是一种特别适合于进行数字信号处理运算的微处理器具,其主机应用是实时快速地实现各种数字信号处理算法。

根据数字信号处理的要求,DSP芯片一般具有如下主要特点:(1)在一个指令周期内可完成一次乘法和一次加法;(2)程序和数据空间分开,可以同时访问指令和数据;(3)片内具有快速RAM,通常可通过独立的数据总线在两块中同时访问;(4)具有低开销或无开销循环及跳转的硬件支持;(5)快速的中断处理和硬件I/O支持;(6)具有在单周期内操作的多个硬件地址产生器;(7)可以并行执行多个操作;(8)支持流水线操作,使取指、译码和执行等操作可以重叠执行。

当然,与通用微处理器相比,DSP芯片的其他通用功能相对较弱些。

ARM (Advanced RISC Machines ),既可以认为是一个公司的名字,也可以认为是对一类微处理器的通称,还可以认为是一种技术的名字。

1991 年ARM 公司成立于英国剑桥,主要出售芯片设计技术的授权。

ARM、DSP、FPGA的技术特点和区别在嵌入式开发领域,ARM是一款非常受欢迎的微处理器,其市场覆盖率极高,DSP和FPGA则是作为嵌入式开发的协处理器,协助微处理器更好的实现产品功能。

那三者的技术特点以及区别是什么呢?下文就此问题略做了总结。

ARM(Advanced RISC Machines)是微处理器行业的一家知名企业,设计了大量高性能、廉价、耗能低的RISC处理器、相关技术及软件。

ARM架构是面向低预算市场设计的第一款RISC微处理器,基本是32位单片机的行业标准,它提供一系列内核、体系扩展、微处理器和系统芯片方案,四个功能模块可供生产厂商根据不同用户的要求来配置生产。

由于所有产品均采用一个通用的软件体系,所以相同的软件可在所有产品中运行。

目前ARM在手持设备市场占有90以上的份额,可以有效地缩短应用程序开发与测试的时间,也降低了研发费用。

DSP(digital singnal processor)是一种独特的微处理器,有自己的完整指令系统,是以数字信号来处理大量信息的器件。

一个数字信号处理器在一块不大的芯片内包括有控制单元、运算单元、各种寄存器以及一定数量的存储单元等等,在其外围还可以连接若干存储器,并可以与一定数量的外部设备互相通信,有软、硬件的全面功能,本身就是一个微型计算机。

DSP采用的是哈佛设计,即数据总线和地址总线分开,使程序和数据分别存储在两个分开的空间,允许取指令和执行指令完全重叠。

也就是说在执行上一条指令的同时就可取出下一条指令,并进行译码,这大大的提高了微处理器的速度。

另外还允许在程序空间和数据空间之间进行传输,因为增加了器件的灵活性。

其工作原理是接收模拟信号,转换为0或1的数字信号,再对数字信号进行修改、删除、强化,并在其他系统芯片中把数字数据解译回模拟数据或实际环境格式。

它不仅具有可编程性,而且其实时运行速度可达每秒数以千万条复杂指令程序,远远超过通用微处理器,是数字化电子世界中日益重要的电脑芯片。

三分钟了解ARM、DSP及FPGA的区别ARM(Advanced RISC Machines)是微处理器行业的一家知名企业,设计了大量高性能、廉价、耗能低的RISC处理器、相关技术及软件。

ARM架构是面向低预算市场设计的第一款RISC微处理器,基本是32位单片机的行业标准,它提供一系列内核、体系扩展、微处理器和系统芯片方案,四个功能模块可供生产厂商根据不同用户的要求来配置生产。

由于所有产品均采用一个通用的软件体系,所以相同的软件可在所有产品中运行。

目前ARM在手持设备市场占有90以上的份额,可以有效地缩短应用程序开发与测试的时间,也降低了研发费用。

DSP(digital singnal processor)是一种独特的微处理器,有自己的完整指令系统,是以数字信号来处理大量信息的器件。

一个数字信号处理器在一块不大的芯片内包括有控制单元、运算单元、各种寄存器以及一定数量的存储单元等等,在其外围还可以连接若干存储器,并可以与一定数量的外部设备互相通信,有软、硬件的全面功能,本身就是一个微型计算机。

DSP采用的是哈佛设计,即数据总线和地址总线分开,使程序和数据分别存储在两个分开的空间,允许取指令和执行指令完全重叠。

也就是说在执行上一条指令的同时就可取出下一条指令,并进行译码,这大大的提高了微处理器的速度。

另外还允许在程序空间和数据空间之间进行传输,因为增加了器件的灵活性。

其工作原理是接收模拟信号,转换为0或1的数字信号,再对数字信号进行修改、删除、强化,并在其他系统芯片中把数字数据解译回模拟数据或实际环境格式。

它不仅具有可编程性,而且其实时运行速度可达每秒数以千万条复杂指令程序,远远超过通用微处理器,是数字化电子世界中日益重要的电脑芯片。

它的强大数据处理能力和高运行速度,是最值得称道的两大特色。

由于它运算能力很强,速度很快,体积很小,而且采用软件编程具有高度的灵活性,因此为从事各种复杂的应用提供了一条有效途径。

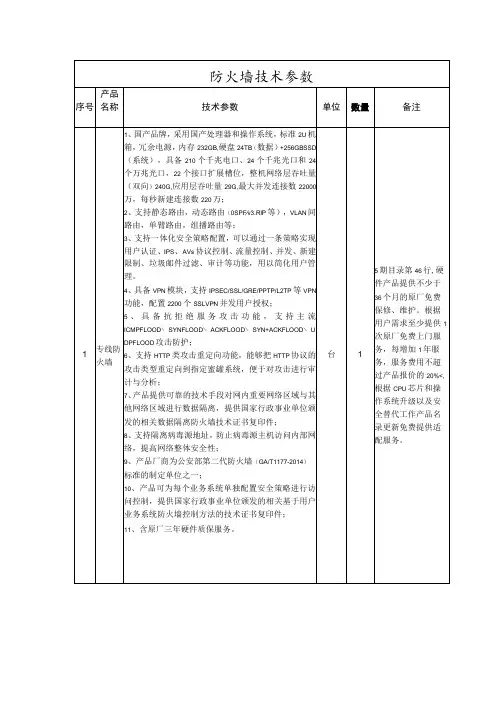

各系列产品概述:1.防火墙系列十几年来,天融信专注于信息安全,国内首家开发出自主知识产权的防火墙系统,率先提出TOPSEC联动技术体系,领先的TopASIC自主安全芯片,在不断的技术创新中网络卫士防火墙引领了包过滤、应用代理、核检测等突破性变革,目前已进入以自主安全操作系统TOS (Topsec Operating System) 为基础,以完全内容检测为标志的全新技术阶段,形成了适用于中小企业级到电信级各种网络应用需求的NGFW4000、NGFW4000-UF系列60多个型号的防火墙产品.网络卫士防火墙系统集成了防火墙、IPSEC VPN、SSL VPN、带宽管理、防病毒、入侵防御、内容过滤等多种安全功能;用户可根据实际需求灵活选择针对行业应用特点及不同性能的产品.目前天融信防火墙已在政府、金融、电信、教育、能源、交通等各行业普遍应用.据TOPSEC统计:遍布全国的29810多个网络和业务在其保护下平稳运行。

据权威数据机构IDC、CCID统计,天融信已连续十多年在网络安全硬件市场处于领先地位。

2。

网络卫士VPN系统作为国内最早从事信息安全产品研发生产的专业安全厂商,天融信自2000年开始向国内市场提供VPN产品,历经近十年的技术积累与市场考验,目前网络卫士VPN系统包括IPSEC VPN、VONE(IPSEC/SSL VPN多合一网关)两大系列,向用户提供成熟、完善的高性能VPN接入方案;拥有包括政府、金融、能源、物流、连锁服务等行业在内的两万余名用户.国家部委全球项目的实施、NPD产品开发流程及ISO9001质量体系的成功实践,验证着天融信VPN产品凭借卓越的品质与技术进入了国际领先行列。

自主知识产权的TOS (Topsec Operating System)系统平台,采用开放性系统架构及模块化设计,融合了数据加密、身份认证、访问控制等安全手段,使网络卫士VPN产品具有安全、高效、易于管理和扩展等特点.从2002年国内最早提出支持双边NAT穿越、第一个实现全动态组网;到2007年国内首发千兆线速VPN、首创全面支持分级可信接入VPN产品,2008年又在权威机构横向测评中,性能指标远远超越对手。

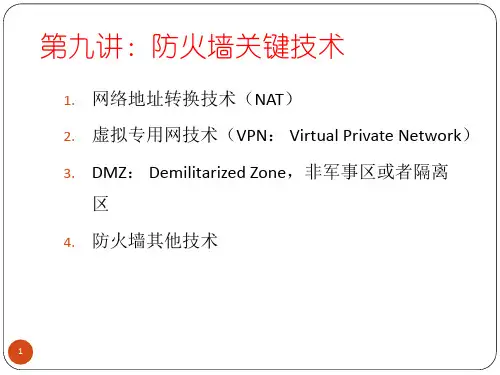

防火墙的基础知识大全什么是防火墙? 防火墙是使用一段"代码墙"把你的电脑和internet 分隔开。

它检查到达防火墙两端的所有数据包,无论是进入还是发出,从而决定该拦截这个包还是将其放行。

下面就让小编带你去看看关于防火墙的基础知识大全吧,希望能帮助到大家!都0202了,这些防火墙的知识你还不懂吗?硬件防火墙的原理软件防火墙及硬件防火墙中还有的其他功能,例如CF(内容过滤)IDS(入侵侦测)IPS(入侵防护)等等的功能。

也就是说硬件防火墙是指把防火墙程序做到芯片里面,由硬件执行这些功能,能减少CPU的负担,使路由更稳定。

硬件防火墙是保障内部网络安全的一道重要屏障。

它的安全和稳定,直接关系到整个内部网络的安全。

因此,日常例行的检查对于保证硬件防火墙的安全是非常重要的。

系统中存在的很多隐患和故障在暴发前都会出现这样或那样的苗头,例行检查的任务就是要发现这些安全隐患,并尽可能将问题定位,方便问题的解决。

4种类型(1)包过滤防火墙包过滤防火墙一般在路由器上实现,用以过滤用户定义的内容,如IP地址。

包过滤防火墙的工作原理是:系统在网络层检查数据包,与应用层无关。

这样系统就具有很好的传输性能,可扩展能力强。

但是,包过滤防火墙的安全性有一定的缺陷,因为系统对应用层信息无感知,也就是说,防火墙不理解通信的内容,所以可能被黑客所攻破。

(2)应用网关防火墙应用网关防火墙检查所有应用层的信息包,并将检查的内容信息放入决策过程,从而提高网络的安全性。

然而,应用网关防火墙是通过打破客户机/服务器模式实现的。

每个客户机/服务器通信需要两个连接:一个是从客户端到防火墙,另一个是从防火墙到服务器。

另外,每个代理需要一个不同的应用进程,或一个后台运行的服务程序,对每个新的应用必须添加针对此应用的服务程序,否则不能使用该服务。

所以,应用网关防火墙具有可伸缩性差的缺点。

(3)状态检测防火墙状态检测防火墙基本保持了简单包过滤防火墙的优点,性能比较好,同时对应用是透明的,在此基础上,对于安全性有了大幅提升。

防火墙x86架构和ASIC架构和NP架构的区别在众多的安全产品中,防火墙产品无疑是保障网络安全的第一道防线,很多企业为了保障自身服务器或数据安全都采用了防火墙。

随着Internet的迅速普及,全球范围内的计算机网络病毒、操作系统漏洞、垃圾邮件等网络安全问题也是层出不穷,网络安全产品和解决方案越来越成为各类网络用户和厂商们的聚焦点,在众多的安全产品中,防火墙产品无疑是保障网络安全的第一道防线,很多企业为了保障自身服务器或数据安全都采用了防火墙。

随着网络应用的增加,对网络带宽提出了更高的要求。

这意味着防火墙要能够以非常高的速率处理数据,于是千兆防火墙逐步崭露头角,频频被运用在金融、电信、教育、气象等大型的行业和机构,以及对安全要求极高的大型企业用户,其市场占有份额已经超过50%;下面就让我们来了解一下千兆防火墙的相关的产品、技术及选购方面的一些知识。

不同构架各具特色从百兆到千兆,最初只是量变。

千兆防火墙在2000年前后就进入了我国市场。

由于百兆网络接口与千兆网络接口的成本相差不大,早期的千兆防火墙仅仅是将百兆接口替换为千兆接口而已。

这种基于X86体系结构的千兆防火墙主体仍然是软件,其性能受到很大制约,无法达到千兆的处理速度。

因此,这些防火墙只是具有千兆接入能力的防火墙,而不是真正具有千兆处理能力的防火墙因此可以说是一种“换汤不换药”的形式改变。

随后几年,随着千兆网络在企业和行业用户中的不断普及,以及用户对性能需求的不断增加,千兆防火墙也逐发生了质变。

这种质的变化首先是人们把目光转移到了专用集成电路(ASIC)和网络处理器(NP)上。

相对于X86架构,基于这些架构的千兆防火墙才是真正的硬件解决方案,能够实现千兆处理速度。

在这里,我们不妨将X86架构、NP和ASIC放在一起进行技术比较,看看不同技术的优缺点。

X86架构最初的千兆防火墙是基于X86架构。

X86架构采用通用CPU和PCI总线接口,具有很高的灵活性和可扩展性,过去一直是防火墙开发的主要平台。

防火墙介绍黎狸1.什么是防火墙?防火墙的功能?防火墙是一种用来加强网络之间访问控制的特殊网络互连设备,是一种非常有效的网络安全模型。

功能:(本质特征为隔离内外网络和对进出信息流实施访问控制)①网络安全的屏障;②过滤不安全服务;③阻断特定的网络攻击;④部署NAT机制;⑤提供了监视局域网安全和预警的方便端点。

2.理解防火墙的四种体系结构,掌握分组过滤路由器、双宿主机、屏蔽主机、屏蔽子网四种不同结构的原理。

①个人防火墙:在操作系统之上运行的软件,安装在个人PC上,为个人计算机提供简单的防火功能。

②软件防火墙:网络防火墙的软件防火墙具有比个人防火墙更强的控制功能和更高的性能。

支持Windows,Unix或者Linux系统。

③一般硬件防火墙:嵌入式主机,配件可定制,功能全,性能一般。

④纯硬件防火墙:采用专用芯片,高性能,非常高的并发连接数和吞吐量;⑥分布式防火墙:上述几种均为边界防火墙。

防火墙的体系结构:①分组过滤路由器②双宿主机③屏蔽主机④屏蔽子网3.理解和掌握数据包过滤、代理服务器、NAT、状态监测技术,并解释对应名词:数据包过滤、代理服务器、NAT、DMZ数据包过滤:工作在网络层,在网络的适当位置来对数据包实施有选择的通过的技术。

代理服务器:是运行于连接内部网络与外部网络的主机(堡垒主机)上的一种应用,是一种比较高级的防火墙技术。

状态检测技术:4.数据包过滤和状态检测区别和联系?这两种防火墙的主要区别是,状态监测系统维护一复个状态表,让这些系统跟踪通过防火墙的全部开放的连接。

而数据包过滤防火墙就没有这个功能。

当通讯到达时,这个系统把这个通讯与状态表进行比较,确定这个通讯是不是一个已经建立起来的通讯的一部分。

现在市场上的防火墙、UTM产品从其架构上来说,大概分为三大类。

第一类是基于X86平台的,这种平台通常使用一颗或多颗主CPU来处理业务数据,网卡芯片和CPU 通过PCI总线来传输数据。

由于传统的32位PCI总线频率为33MHZ,所以,理论通讯速率为:132 MB Bytes/S即:1056 MBits/S.单从PCI通讯的速率上来说是可以满足千兆防火墙的需要,但实际上PCI总线在X86系统中是共享的,也就是说,如果有两个网卡同时传输数据,那么每个网卡所能获得的速率就只有66 MB Bytes/S,即:528 Mbits/S ,如果有四个网口同时传输数据,则每个网卡所能获得的速度只有16 MB Bytes/S,即128Mbit/S.从总线速度来看基于32位PCI总线的X86平台,做为百兆防火墙的方案是没有任何问题的。

但X86平台的防火墙方案,数据从网卡到CPU之间的传输机制是靠“中断”来实现的,中断机制导致在有大量数据包的需要处理的情况下(如:64 Bytes的小包,以下简称小包),X86平台的防火墙吞吐速率不高,大概在30%左右,并且CPU占用会很高。

这是所有基于X86平台的防火墙所共同存在的问题。

因此,基于32位PCI总线的X86平台是不能做为千兆防火墙使用的,因为32位PCI总线的通讯速率不能达到千兆防火墙的要求。

针对这个问题,Intel提出了解决方案,可以把32位的PCI总线升级到了PCI-E ,即:PCI-Express,这样,PCI-E 4X的总线的速度就可以达到2000MB Bytes/S,即:16Gbits/S,并且PCI-E各个PCI设备之间互相独立不共享总线带宽,每个基于PCI-E的网口可以使用的带宽为:2000MB Bytes/S,即:16Gbits/S,所以基于PCI-E 4X的X86从系统带宽上来说,做为千兆防火墙是没有任何问题的。

但是,基于PCI-E的防火墙数据从网卡到CPU之间传输同样使用“中断”机制来传输数据,所以小包(64 Bytes)的通过率仍然为:30-40%.第二类,基于ASIC架构的防火墙、UTM产品。

X86架构基础知识介绍X86架构是一种广泛应用于个人计算机和服务器的指令集架构。

它最初由英特尔公司于1978年推出,并成为个人计算机的主要架构之一、随着时间的推移,X86架构不断发展和演进,目前主要由英特尔和AMD等公司推动。

X86架构支持多种数据类型,包括整数、浮点数和向量数据等。

整数操作可处理不同大小的整数,如8位、16位、32位和64位。

浮点数操作支持单精度和双精度浮点数,以及一些高级浮点操作,如开根号和三角函数等。

向量数据操作允许同时处理多个数据,以提高计算效率。

X86架构采用一种被称为寄存器的特殊存储器件来存储和处理数据。

寄存器是内置在处理器中的高速存储器,可暂时存储和操作数据。

X86架构有多个通用寄存器和特殊寄存器,每个寄存器都有特定的用途和功能。

通用寄存器用于常规数据操作,如存储变量和计算中间结果等。

特殊寄存器用于保存程序状态和控制处理器行为。

X86架构还支持存储器层次结构,其中数据可以在不同层次的存储器之间移动。

处理器内部有多级高速缓存存储器,用于暂时存储数据和指令,以提高访问速度。

此外,X86架构还支持外部存储器,如随机存取存储器(RAM)和硬盘驱动器等,用于长期存储和备份数据。

X86架构的软件生态系统非常丰富,有大量的操作系统、开发工具和应用程序可供选择。

常见的操作系统包括Windows、Linux和macOS等,它们都提供对X86架构的良好支持。

开发工具包括编译器、调试器和性能分析工具等,开发者可以使用这些工具来创建和优化X86架构的软件。

应用程序涵盖了各个领域,包括办公软件、娱乐软件和科学计算等。

近年来,X86架构在能效和性能方面取得了很大进步。

先进的制造工艺和设计技术使得处理器能够提供更高的性能,并在较低的功耗下工作。

同时,X86架构还提供了一些高级功能,如虚拟化和安全保护等,以满足不同应用场景的需求。

总之,X86架构是一种广泛应用于个人计算机和服务器的指令集架构,它提供了一组丰富的指令集和寄存器,支持多种数据类型和存储器层次结构。

x86架构简介x86架构是一种广泛应用于个人电脑和服务器等计算机系统的微处理器架构。

它最早是由英特尔公司在1978年推出,而后被AMD、Cyrix等其他公司广泛采用和发展。

现在,x86架构已经成为PC市场的主导架构。

架构特点x86架构主要有以下几个特点:1.复杂指令集(CISC):x86架构具有复杂的指令集,即一条指令可以执行多个操作。

这使得x86架构的指令相对较长,且指令的执行时间相对较长。

然而,CISC架构的好处是可以通过一个指令实现更多的操作,从而减少指令数量和存储空间。

2.向后兼容性:x86架构不断发展演变,但同时保持了向后兼容性。

这意味着早期的x86指令集可以在最新的处理器上运行,而不需要进行修改或重新编译。

3.多功能性:x86架构允许在处理器上执行多种操作,并支持多任务处理。

这使得x86架构适用于各种应用场景,包括个人电脑、服务器、嵌入式系统等。

4.支持虚拟化技术:x86架构是虚拟化技术的主要支持平台之一。

通过虚拟化,可以在一台物理机上同时运行多个虚拟机实例,提高计算资源的利用率。

主要代表x86架构的主要代表是英特尔公司的处理器和AMD公司的处理器。

英特尔处理器英特尔公司是x86架构的主要推动者和开发者之一。

他们的处理器产品线包括酷睿系列、赛扬系列、至强系列等。

酷睿系列酷睿系列处理器是英特尔公司针对消费者市场推出的产品线。

它们具有较高的性能和能效,适用于个人电脑、笔记本电脑和智能设备等。

赛扬系列赛扬系列处理器是英特尔公司面向入门级市场推出的产品线。

它们具有较低的成本和能耗,并适用于低功耗设备和低端电脑。

至强系列至强系列处理器是英特尔公司为服务器和工作站等高性能计算场景设计的产品线。

它们具有更高的计算能力和可扩展性。

AMD处理器AMD公司也是x86架构的重要参与者。

他们的处理器产品线包括锐龙系列、锐速龙系列、EPYC系列等。

锐龙系列锐龙系列处理器是AMD公司面向消费者市场推出的产品线。

防火墙硬件ASIC、NP、X86、RISC、DSP 、ARM技术介绍

ASIC(Application Specific Integrated Circuit)是专用集成电路。

目前,在集成电路界ASIC被认为是一种为专门目的而设计的集成电路。

是指应特定用户要求和特定电子系统的需要而设计、制造的集成电路。

ASIC的特点是面向特定用户的需求,ASIC在批量生产时与通用集成电路相比具有体积更小、功耗更低、可靠性提高、性能提高、保密性增强、成本降低等优点。

ASIC分为全定制和半定制。

全定制设计需要设计者完成所有电路的设计,因此需要大量人力物力,灵活性好但开发效率低下。

如果设计较为理想,全定制能够比半定制的ASIC芯片运行速度更快。

半定制使用库里的标准逻辑单元(Standard Cell),设计时可以从标准逻辑单元库中选择SSI(门电路)、MSI(如加法器、比较器等)、数据通路(如ALU、存储器、总线等)、存储器甚至系统级模块(如乘法器、微控制器等)和IP核,这些逻辑单元已经布局完毕,而且设计得较为可靠,设计者可以较方便地完成系统设计。

现代ASIC常包含整个32-bit处理器,类似ROM、RAM、EEPROM、Flash的存储单元和其他模块. 这样的ASIC常被称为SoC(片上系统)。

FPGA是ASIC的近亲,一般通过原理图、VHDL对数字系统建模,运用EDA软件仿真、综合,生成基于一些标准库的网络表,配置到芯片即可使用。

它与ASIC的区别是用户不需要介入芯片的布局布线和工艺问题,而且可以随时改变其逻辑功能,使用灵活。

NP(network process)网络处理器,是专门为处理数据包而设计的可编程处理器,能够直接完成网络数据处理的一般性任务。

硬件体系结构大多采用高速的接口技术和总线规范,具有较高的I/O能力,包处理能力得到了很大提升。

网络处理器一般具有以下特点:

● 并行处理器: 采用多内核并行处理器结构。

片内处理器按任务大致分为核心处理器和转发引擎。

● 专用硬件协处理器: 对要求高速处理的通用功能模块采用专用硬件实现以提高系统性能。

● 专用指令集: 转发引擎通常采用专用的精简指令集,并针对网络协议处理特点优化。

● 分级存储器组织: NP存储器一般包含多种不同性能的存储结构,对数据进行分类存储以适应不同的应用目的。

● 高速I/O接口: NP具有丰富的高速I/O接口,包括物理链路接口、交换接口、存储器接口、PCI总线接口等。

通过内部高速总线连接在一起,提供很强的硬件并行处理能力。

● 可扩展性: 多个NP之间还可以互连,构成网络处理器簇,以支持更为大型高速的网络处理。

从网络处理器以上特点可以看出,与通用处理器相比,网络处理器在网络分组数据处理上具有明显的优势。

x86是一个intel通用计算机系列的标准编号缩写,也标识一套通用的计算机指令集合,X 与处理器没有任何关系,它是一个对所有*86系统的简单的通配符定义,例如:i386, 586,奔腾(pentium)。

由于早期intel的CPU编号都是如8086,80286来编号,由于这整个系列的CPU 都是指令兼容的,所以都用X86来标识所使用的指令集合如今的奔腾,P2,P4,赛扬系列都是支持X86指令系统的,所以都属于X86家族;

X86指令集是美国Intel公司为其第一块16位CPU(i8086)专门开发的,美国IBM公司1981年推出的世界第一台PC机中的CPU--i8088(i8086简化版)使用的也是X86指令,同时电脑中为提高浮点数据处理能力而增加的X87芯片系列数学协处理器则另外使用X87指令,以后就将X86指令集和X87指令集统称为X86指令集。

虽然随着CPU技术的不断发展,Intel陆续研制出更新型的i80386、i80486直到今天的Pentium 4(以下简为P4)系列,但为了保证电脑能继续运行以往开发的各类应用程序以保护和继承丰富的软件资源,所以Intel公司所生产的所有CPU仍然继续使用X86指令集,所以它的CPU仍属于X86系列。

RISC(reduced instruction set computer,精简指令集计算机)是一种执行较少类型计算机指令的微处理器,起源于80年代的MIPS主机(即RISC机),RISC机中采用的微处理器统称RISC处理器。

这样一来,它能够以更快的速度执行操作(每秒执行更多百万条指令,即MIPS)。

因为计算机执行每个指令类型都需要额外的晶体管和电路元件,计算机指令集越大就会使微处理器更复杂,执行操作也会更慢。

RISC主要特点:

RISC微处理器不仅精简了指令系统,采用超标量和超流水线结构;它们的指令数目只有几十条,却大大增强了并行处理能力。

如:1987年Sun Microsystem公司推出的SPARC芯片就是一种超标量结构的RISC处理器。

而SGI公司推出的MIPS处理器则采用超流水线结构,这些RISC处理器在构建并行精简指令系统多处理机中起着核心的作用。

RISC处理器是当今UNIX领域64位多处理机的主流芯片

性能特点一:由于指令集简化后,流水线以及常用指令均可用硬件执行;

性能特点二:采用大量的寄存器,使大部分指令操作都在寄存器之间进行,提高了处理速度;性能特点三:采用缓存—主机—外存三级存储结构,使取数与存数指令分开执行,使处理器可以完成尽可能多的工作,且不因从存储器存取信息而放慢处理速度。