赛灵思(Xilinx)FPGA设计约束的分类

赛灵思中文社区

本文主要通过一个实例具体介绍ISE中通过编辑UCF文件来对FPGA设计进行约束,主要涉及到的约束包括时钟约束、群组约束、逻辑管脚约束以及物理属性约束。

Xilinx定义了如下几种约束类型:

?“Attributes and Constraints”

?“CPLD Fitter”

?“Grouping Constraints”

?“Logical Constraints”

?“Physical Constraints”

?“Mapping Directives”

?“Placement Constraints”

?“Routing Directives”

?“Synthesis Constraints”

?“Timing Constraints”

?“Configuration Constraints”

通过编译UCF(user constraints file)文件可以完成上述的功能。

还是用实例来讲UCF的语法是如何的。

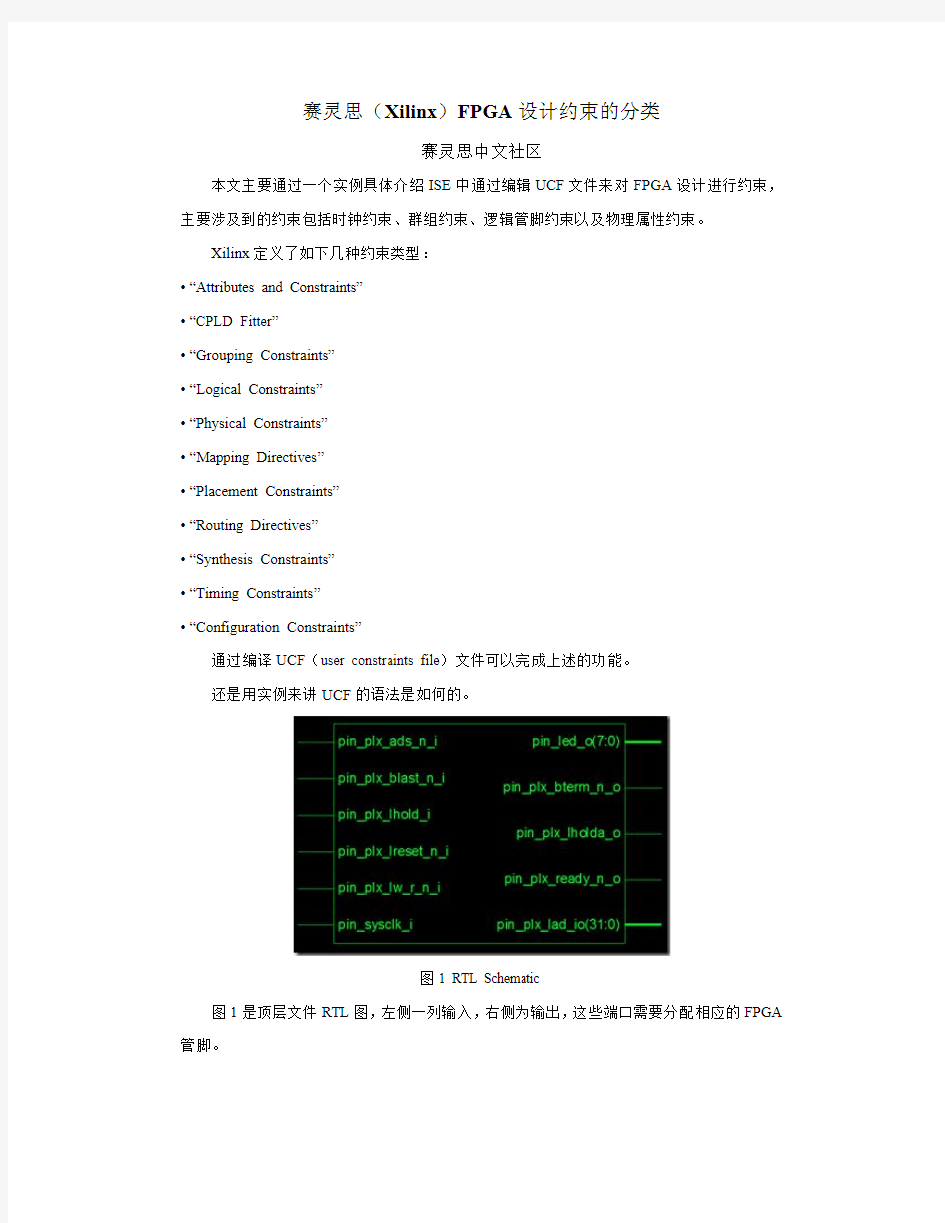

图1 RTL Schematic

图1是顶层文件RTL图,左侧一列输入,右侧为输出,这些端口需要分配相应的FPGA 管脚。

表1 UCF example对上面的UCF文件进行一些注释

该UCF文件主要是完成了管脚的约束、时钟的约束,以及组的约束。第一、二行:主要定义了时钟以及对应的物理管脚。

第一行,端口pin_sysclk_i 分配到FPGA管脚AD12,并放到了pin_sysclk_i group中。那如何得知是AD12的管脚呢,请看图2,FPGA管脚AD12是一个66MHz的外部时钟。FPGA的开发板肯定有电路原理图供你分配外部管脚。

图2电路原理图

图2,电路原理图第二行:时钟说明:周期15ns,占空比50%。关键词TIMESPEC(Timing Specifications),即时钟说明。一般的语法是:

TIMESPEC "TSidentifier"=PERIOD "timegroup_name" value [units];

其中TSidentifier用来指定TS(时钟说明)的唯一的名称。

第七行:pin_plx_lholda_o 连接至物理管脚D17,并配置该管脚电平变化的速率。关键词:SLEW,用来定义电平变化的速率的,一般语法是:

NET "top_level_port_name" SLEW="value";

其中value = {FAST|SLOW|QUIETIO}, QUIETIO仅用在Spartan-3A。

第十行:定义pin_plx_ads_n_i 输入跟时钟的关系。OFFSET IN和OFFSET OUT的约束。OFFSET IN 定义了数据输入的时间和接收数据时钟沿(capture Edge)的关系。一般的语法是:

OFFSET = IN value VALID value BEFORE clock

OFFSET = OUT value V ALID value AFTER clock

图3 时序图

图3 时序图(OFFSET IN)例子:

NET "SysCLk" TNM_NET = "SysClk";

TIMESPEC "TS_SysClk" = PERIOD "SysClk" 5 ns HIGH 50%;

OFFSET = IN 5 ns V ALID 5 ns BEFORE "SysClk";

上面的定义了基于SysClk的全局OFFSET IN的属性。时序可看图3。

图4 时序图

图4 时序图(OFFSET OUT)例子:

NET "ClkIn" TNM_NET = "ClkIn";

OFFSET = OUT 5 ns AFTER "ClkIn";

上面设置主要是定了了时钟跟数据的时间关系,时序图4。可以看到这时一种全局定义,Data1 和Data2输出时间都受到OFFSET = OUT 5 ns AFTER "ClkIn" 的约束。如果需要单独定义输出端口的OFFSET OUT的,需要制定相应的NET,可参考表1中的第57行。

第18至49行:pin_plx_lad_io<*> 被归到了名称为LAD的TMN(Timing name),这个可以说是GROUP的约束。这样往往给约束带来方便,不用一个一个的NET 或者INST进行约束。

第50至51行:对TIMEGRP 是LAD进行OFFSET IN和OUT的定义。

在时序约束中,在这里还未提及FROM TO的约束。FROM TO的约束主要是用来两个同步模块之间的时间关系的约束。在这里不做深入的讨论。

至此,基本上把一般的UCF文件的作用进行了注释。

注:一般的时间的约束需要通过静态的时序分析,然后再设定相应PERIOD,OFFSET IN 以及OFFEET OUT等的时间参数。

当然在例子中还没有涉及到区域的约束。下面会试图说一下。

ISE进行综合后会将设计代码生成相应的逻辑网表,然后经过translate过程,转换到Xilinx特定的底层结构和硬件原语,MAP过程就是将映射到具体型号的器件上,最后就是就是布线和布局的操作了。

区域的约束相当于将布局过程中指定特定型号的器件的位置,这完全可以通过FloorPlanner的GUI界面进行设置,用图形界面设置完后,配置信息会放到UCF中,这里只介绍UCF的使用。

例如:

INST "Done" LOC = "SLICE_X32Y163" ; #Done映射为一个寄存器,映射到SLICE_X32Y163的位置上。(32,163)相当于一个坐标,可以用FloorPlanner进行查看。INST"BRAM4/BU2/U0/blk_mem_generator/valid.cstr/ramloop[0].ram.r/v4_init.ram/TRUE_DP.S INGLE_PRIM.TDP"LOC = "RAMB16_X2Y22" ; #RAM16的一个映射。

又例如,X,Y,Z是对应的是寄存器。现在想把它们放在一个指定的区域中,我可以这样写,INST “X” AREA_GROUP = reg;

INST “X” AREA_GROUP = reg;

INST “X” AREA_GROUP = reg;

AREA_GROUP reg RANGE = SLICE_X1Y1 :SLICE_X1Y6;

注:如何查看INST中的名称呢?在ISE中Timing constraints editor中可以查看。

注:NET,LOC,TNM_NET,TIMESPEC,PERIOD,OFFSET,IN,OUT,SLEW,HIGH等都是关键字,UCF文件是大小敏感的,端口名称必须和源代码中的名字一致,且端口名字不能和关键字一样。但是关键字NET是不区分大小写的。

其实上述都是约束的入门的内容,如果要想深入的了解的话,请参考官方网站。

XilinxFPGA引脚功能详细介绍 注:技术交流用,希望对大家有所帮助。 IO_LXXY_# 用户IO引脚 XX代表某个Bank内唯一的一对引脚,Y=[P|N]代表对上升沿还是下降沿敏感,#代表bank号 2.IO_LXXY_ZZZ_# 多功能引脚 ZZZ代表在用户IO的基本上添加一个或多个以下功能。 Dn:I/O(在readback期间),在selectMAP或者BPI模式下,D[15:0]配置为数据口。在从SelectMAP读反馈期间,如果RDWR_B=1,则这些引脚变成输出口。配置完成后,这些引脚又作为普通用户引脚。 D0_DIN_MISO_MISO1:I,在并口模式(SelectMAP/BPI)下,D0是数据的最低位,在Bit-serial模式下,DIN是信号数据的输入;在SPI模式下,MISO是主输入或者从输出;在SPI*2或者SPI*4模式下,MISO1是SPI总线的第二位。 D1_MISO2,D2_MISO3:I,在并口模式下,D1和D2是数据总线的低位;在SPI*4模式下,MISO2和MISO3是SPI总线的MSBs。 An:O,A[25:0]为BPI模式的地址位。配置完成后,变为用户I/O口。 AW AKE:O,电源保存挂起模式的状态输出引脚。SUSPEND是一个专用引脚,AWAKE 是一个多功能引脚。除非SUSPEND模式被使能,AWAKE被用作用户I/O。 MOSI_CSI_B_MISO0:I/O,在SPI模式下,主输出或者从输入;在SelectMAP模式下,CSI_B是一个低电平有效的片选信号;在SPI*2或者SPI*4的模式下,MISO0是SPI总线的第一位数据。 FCS_B:O,BPI flash 的片选信号。 FOE_B:O,BPI flash的输出使能信号 FWE_B:O,BPI flash 的写使用信号 LDC:O,BPI模式配置期间为低电平 HDC:O,BPI模式配置期间为高电平 CSO_B:O,在并口模式下,工具链片选信号。在SPI模式下,为SPI flsah片选信号。 IRDY1/2,TRDY1/2:O,在PCI设计中,以LogiCORE IP方式使用。 DOUT_BUSY:O,在SelectMAP模式下,BUSY表示设备状态;在位串口模式下,DOUT 提供配置数据流。 RDWR_B_VREF:I,在SelectMAP模式下,这是一个低电平有效的写使能信号;配置完成后,如果需要,RDWR_B可以在BANK2中做为Vref。 HSW APEN:I,在配置之后和配置过程中,低电平使用上拉。 INIT_B:双向,开漏,低电平表示配置内存已经被清理;保持低电平,配置被延迟;在配置过程中,低电平表示配置数据错误已经发生;配置完成后,可以用来指示POST_CRC 状态。 SCPn:I,挂起控制引脚SCP[7:0],用于挂起多引脚唤醒特性。 CMPMOSI,CMPMISO,CMPCLK:N/A,保留。 M0,M1:I,配置模式选择。M0=并口(0)或者串口(1),M1=主机(0)或者从机(1)。 CCLK:I/O,配置时钟,主模式下输出,从模式下输入。 USERCCLK:I,主模式下,可行用户配置时钟。 GCLK:I,这些引脚连接到全局时钟缓存器,在不需要时钟的时候,这些引脚可以作为常规用户引脚。 VREF_#:N/A,这些是输入临界电压引脚。当外部的临界电压不必要时,他可以作为

DC综合全过程及使用的命令 DC的初始化文件.synopsys.dc.setup,该文件是隐藏文件,需要用ls –a显示 读取文件 DC支持多种硬件描述格式,.db .v .vhd等 对于dcsh工作模式来说,读取不同的文件格式需要不同的参数 Read -format Verilog[db\vhdl ect] file //dcsh工作模式 对于tcl工作模式来说,读取不同文件格式使用不同的命令。

Read_db file.db //tcl工作模式读取db格式 Read_verilog file.v //tcl工作模式读取verilog格式 Read_vhdl file.v //tcl工作模式读取vhdl格式 读取源程序的另外一种方式是配合使用analyzer命令和elaborate命令; Analyzer是分析HDL的源程序并将分析产生的中间文件存于work(用户可以自己指定)的目录下 Elaborate则在产生的中间文件中生成verilog的模块或者VHDL的实体 缺省情况下,elaborate读取的是work目录中的文件 当读取完所要综合的模块后,需要使用link命令将读到DC存储区中的模块或实体连接起来 注意:如果在使用link命令后,出现unresolved design reference的警告信息,需要重新读取该模块,或者在.synopsys_dc.setup 文件中添加link_library,告诉DC到库中去找这些模块,同时还要注意search_path中的路径是否指向该模块或单元电路所在的目录 Link命令执行后,DC就将模块按照RTL级或者门级的描述将电路连接起来,之后的各种限制条件就可以对该电路的顶层模块施加 DC限制条件施加的对象 针对以下电路成分:输入输出端口、模块、子模块的实例化、单元电路、连线及电路的引脚。在使用DC命令的时候,不要使用模糊的对象,例如,如下面的电路: Set_load 3 Clk 由于在电路中含有名称为CLK的pin、port和net,因此,DC无法知道该处的load是施加在哪个对象上,注意到一般连线会驱动负载,该命令就改为: Set_load 3 [get_nets Clk] TCL mode Set_load 3 find(net,”Clk”)dc_shell mode 路径的划分与合法路径 DC综合的时候是基于路径的优化,对于DC来说,合法的路径必须满足以下条件 路径的起点为输入端口或者是触发器的数据端 路径终点为输出端口或者是触发器的时钟端 DC设定的限制条件的值都是无单位的,这些单位都是由工艺库中给定的 可以用report_lib lib_name来查看所有在工艺库中设定的各个参数的单位 定义电路的工作环境和综合环境

5.1.6 SelectIO模块 Virtex-6每个I/O片(I/O Tile)包含两个IOB、两个ILOGIC、两个OLOGIC 和两个IODELAY,如图5-24 所示。 图5-24 I/O 片结构图 本小节就以下几个方面介绍Virtex-6 的SelectIO 资源。 (1) SelectIO 的电气特性。 (2) SelectIO 的逻辑资源——ILOGIC 资源和OLOGIC 资源。 (3) SelectIO 的高级逻辑资源——ISERDES 资源、OSERDES 资源和Bitslip。 一、SelectIO IO 的电气特性 所有的Virtex-6 FPGA 有高性能的可配置SelectIO 驱动器与接收器,支持非常广泛的接口标准。强大的功能SelectIO 包括输出强度和斜率的可编程控制以及使用数控阻抗(DCI)的片上终端。

IOB 包含输入、输出和三态SelectIO 驱动器。支持单端I/O 标准(LVCMOS、 HSTL、SSTL)和差分I/O 标准(LVDS、HT、LVPECL、BLVDS、差分HSTL 和SSTL)。 注意:差分输入和VREF 相关输入由VCCAUX 供电。 IOB、引脚及部逻辑的连接如图5-25 所示。 图5-25 IOB、引脚及部逻辑连接图 IOB 直接连接ILOGIC/OLOGIC 对,该逻辑对包含输入和输出逻辑资源,可实现数据和三态控制。ILOGIC和OLOGIC可分别配置为ISERDES和OSERDES。Xilinx软件库提供了大量与I/O相关的原语,在例化这些原语时,可以指定I/O 标准。与单端I/O相关的原语包括IBUF(输入缓冲器)、IBUFG(时钟输入缓冲器)、OBUF(输出缓冲器)、OBUFT(三态输出缓冲器)和IOBUF(输入/输出缓冲器)。与差分I/O相关的原语包括IBUFDS(输入缓冲器)、IBUFGDS (时钟输入缓冲器)、OBUFDS(输出缓冲器)、OBUFTDS(三态输出缓冲器)、IOBUFDS(输入/输出缓冲器)、IBUFDS_DIFF_OUT(输入缓冲器)和IOBUFDS_DIFF_OUT(输入/输出缓冲器)。 二、SelectIO的逻辑资源 SelectIO的逻辑资源主要是指ILOGIC和OLOGIC资源,它们完成了FPGA引脚到部逻辑的连接功能,包括组合输入/输出、三态输出控制、寄存器输入/输出、寄存器三态输出控制、DDR输入/输出、DDR输出三态控制、IODELAYE1高分辨率可调整延迟单元及其控制模块。 下面简要介绍ILOGIC和OLOGIC功能。

喾林原创 Synopsys DC10.03安装配置 1、需准备安装包: 1)、Synopsys DC(design compiler)安装包 2)、SCL 安装包(注:此包为synopsys license 管理)。 3)、Synopsys 图像安装工具:installer2.0及以上均可。 (注:图形安装操作简单,不易出错,故采用图形安装界面) 4)、Synopsys license 制作工具( EFA LicGen 0.4b 和Synopsys SSS Feature Keygen )。 2、开始安装DC : 1)、启动图形安装界面 于linux 系统下解压installer2.0包(在windows 下解压文件易损坏)。解压后运行setup.sh 得如图(一)所示界面。 图 (一)

喾林原创点击“start ”有如图(二)所示界面开始安装。在“Source ”栏选中DC 安装文件所在上层目录。“Done ”后“Next ”(此次“Next ”时间较长,耐心等待)。 图 (二) 之后可一直“NEXT ”到如图(三)所示。 图 (三)

在该界面勾选linux选项即可,继续下一步到如图(四)所示。选择安装路径后继续下一步直到结束。 喾林原创 图(四) 至此DC安装结束。 3、开始安装SCL: 此安装与DC安装步骤一直,几乎没有差别,唯一不同的就是安装路径不同。 4、license的制作: License的制作是在windows下制作的。

1)、打开EFA LicGen 0.4b文件夹运行LicGen.exe程序出现如图(五)所示界面。 喾林原创 图(五) 点击“OPEN”选择Synopsys.lpd文件,“打开”。回到图(五)所示界面。勾选上Custon、Use Daemon及最后一个Custon。

Spartan-3E Starter Kit Board User Guide

Chapter 1: Introduction and Overview Chapter 2: Switches, Buttons, and Knob Chapter 3: Clock Sources Chapter 4: FPGA Configuration Options Chapter 5: Character LCD Screen Chapter 6: VGA Display Port Chapter 7: RS-232 Serial Ports Chapter 8: PS/2 Mouse/Keyboard Port Chapter 9: Digital to Analog Converter (DAC) Chapter 10: Analog Capture Circuit Chapter 11: Intel StrataFlash Parallel NOR Flash PROM Chapter 12: SPI Serial Flash Chapter 13: DDR SDRAM Chapter 14: 10/100 Ethernet Physical Layer Interface Chapter 15: Expansion Connectors Chapter 16: XC2C64A CoolRunner-II CPLD Chapter 17: DS2432 1-Wire SHA-1 EEPROM

Chapter 1:Introduction and Overview Spartan-3E 入门实验板使设计人员能够即时利用Spartan-3E 系列的完整平台性能。 设备支持设备支持::Spartan-3E 、CoolRunner-II 关键特性关键特性::Xilinx 器件: Spartan-3E (50万门,XC3S500E-4FG320C), CoolRunner?-II (XC2C64A-5VQ44C)与Platform Flash (XCF04S-VO20C) 时钟时钟::50 MHz 晶体时钟振荡器 存储器: 128 Mbit 并行Flash, 16 Mbit SPI Flash, 64 MByte DDR SDRAM 连接器与接口: 以太网10/100 Phy, JTAG USB 下载,两个9管脚RS-232串行端口, PS/2类型鼠标/键盘端口, 带按钮的旋转编码器, 四个滑动开关,八个单独的LED 输出, 四个瞬时接触按钮, 100管脚hirose 扩展连接端口与三个6管脚扩展连接器 显示器: VGA 显示端口,16 字符- 2 线式 LCD 电源电源::Linear Technologies 电源供电,TPS75003三路电源管理IC 市场: 消费类, 电信/数据通信, 服务器, 存储器 应用: 可支持32位的RISC 处理器,可以采用Xilinx 的MicroBlaze 以及PicoBlaze 嵌入式开发系统;支持DDR 接口的应用;支持基于Ethernet 网络的应用;支持大容量I/O 扩展的应用。 Choose the Starter Kit Board for Your Needs Spartan-3E FPGA Features and Embedded Processing Functions Spartan3-E FPGA 入门实验板具有Spartan3-E FPGA 系列突出独特的特点和为嵌入式处理发展与应用提供了很大的方便。该板的特点如下: Spartan3-E 特有的特征:并行NOR Flash 配置;通过并行NOR Flash PROM 实现FPGA 的多种配置方式 嵌入式系统:MicroBlaze? 32-bit 嵌入RISC 处理器;PicoBlaze? 8-bit 嵌入控制器;DDR 存储器接口 Learning Xilinx FPGA, CPLD, and ISE Development Software Basics Spartan3-E FPGA 入门实验板比其他的入门实验板先进、复杂。它是学习FPGA 或CPLD 设计和怎样运用ISE 软件的基础。 Advanced Spartan-3 Generation Development Boards 入门实验板示范了MicroBlaze? 32-bit 嵌入式处理器和EDK 的基本运用。其更先进的地方

以.cshrc 及用户根目录下的.synopsys_vss.setup .synopsys_dc.setup 已经配置为前提)1.创建工作目录; 2.编写vhdl源程序; 3.编写.synopsys_vss.setup 和.synopsys_dc.setup文件; 4.编译vhdl源程序; 5.运行vhdldbx 仿真器; 6.运行synopsys的综合器; 7.完成综合后的门级仿真; 以一个一位加法器为例,进行具体说明(用户界面为CDE): 1)创建adder 目录: 可以在资源管理器中完成,也可以在unix环境下完成:mkdir adder; 2)在adder目录下创建work目录; 3)编写.synopsys_vss.setup文件并存入adder目录;.synopsys_vss.setup的内容如下:WORK >DEFAULT DEFAULT:work TIMEBASE = NS 4)编写一位加法器的源程序(adder1.vhd)并存入adder目录下: library ieee; use ieee.std_logic_1164.all; entity adder1 is port(din1 : in std_logic; din2 : in std_logic; cin : in std_logic; dout: out std_logic; cout: out std_logic); end adder1; architecture rtl of adder1 is begin dout <= din1 xor din2 xor cin; cout <= (din1 and din2) or (cin and (din1 xor din2)); end rtl; 5)编写一位加法器的测试基准(即test_bench)并存入adder目录下:(tb_adder1.vhd)library ieee; use ieee.std_logic_1164.all; entity tb_adder1 is end tb_adder1; architecture rtl of tb_adder1 is component adder1 is port(din1 : in std_logic; din2 : in std_logic; cin : in std_logic;

Xilinx FPGA配置的一些细节 2010年07月03日星期六 14:26 0 参考资料 (1) Xilinx: Development System Reference Guide. dev.pdf, v10.1 在Xilinx的doc目录下有。 (2) Xilinx: Virtex FPGA Series Configuration and Readback. XAPP138 (v2.8) March 11, 2005 在Xilinx网站上有,链接 (3)Xilinx: Using a Microprocessor to Configure Xilinx FPGAs via Slave Serial or SelectMAP Mode.XAPP502 (v1.5) December 3, 2007 在Xilinx网站上有,链接 注:此外xapp139和xapp151也是和配置相关的。 (4)Xilinx: Virtex-4 Configuration Guide. UG071 (v1.5) January 12, 2007 (5) Tell me about the .BIT . 链接: 1 Xilinx配置过程 主要讲一下Startup Sequence。 Startup Sequence由8个状态组成. 除了7是固定的之外,其它几个的顺序是用户可设置的,而且Wait for DCM和DCI是可选的。 其中默认顺序如下: 这些在ISE生成bit文件时通过属性页设定。 这几个状态的具体含义如下: Release_DONE : DONE信号变高 GWE : 使能CLB和IOB,FPGA的RAMs和FFs可以改变状态 GTS : 激活用户IO,之前都是高阻。

设置启动dc_shell-t工具的 .synopsys.setup文件 Author:周建伟 Company:西安邮电大学SOC组 Date:2013.10.30 摘要:若你在读不进你的库,即在你的运行报告中总是有:warning:Can?t read link_library file …your_library.db?,这边文档会对你有一定的帮助

逻辑综合环境 启动文件 启动文件用来指定综合工具所需要的一些初始化信息。DC使用名为“.synopsys_dc.setup”的启动文件(位置:inst_dir/admin/setup/.synopsys_dc.setup)。启动时,DC会以下述顺序搜索并装载相应目录下的启动文件: DC安装目录($DC_PATH/admin/setup) 用户主目录 工具启动目录 注意:后装载的启动文件中的设置将覆盖先装载的启动文件中的相同设置 本文档重在讲述怎么设置工具启动目录 1、把inst_dir/admin/setup/.synopsys_dc.setup文件拷贝到你DC脚本目录下(也就是和你 脚本在同个目录下) 2、在.synopsys_dc.setup文件的第92行,即set link_force_case “check_reference”命令下 修改内容如下: A、set lib_path /library/smic18/feview~2/version2.2(注:lib_path为你smic18库安装 目录,不同于DC安装目录) B、set link_library [list * $lib_path/STD/Synopsys/smic18_ss.db \ $lib_path/IO/Synopsys/smic18IO_line_ss.db \ $lib_path/IO/Synopsys/smic18IO_stagger_ss.db ] C、set search_path [list . ${synopsys_root}/libraries/syn ${synopsys_root}/dw/syn_ver \ ${synopsys_root}/dw/sim_ver \ $lib_path/STD/Synopsys $lib_path/IO/Synopsys ] D、set target_library [list $lib_path/STD/Synopsys/smic18_ss.db \ $lib_path/IO/Synopsys/smic18IO_line_ss.db \ $lib_path/IO/Synopsys/smic18IO_stagger_ss.db ] E、set synthetic_library “” set command_log_file “./command.log” set designer “zjw” set company “soc of xupt”

注:技术交流用,希望对大家有所帮助。 IO_LXXY_# 用户IO引脚 XX代表某个Bank内唯一的一对引脚,Y=[P|N]代表对上升沿还是下降沿敏感,#代表bank 号 2.IO_LXXY_ZZZ_# 多功能引脚 ZZZ代表在用户IO的基本上添加一个或多个以下功能。 Dn:I/O(在readback期间),在selectMAP或者BPI模式下,D[15:0]配置为数据口。在从SelectMAP读反馈期间,如果RDWR_B=1,则这些引脚变成输出口。配置完成后,这些引脚又作为普通用户引脚。 D0_DIN_MISO_MISO1:I,在并口模式(SelectMAP/BPI)下,D0是数据的最低位,在Bit-serial模式下,DIN是信号数据的输入;在SPI模式下,MISO是主输入或者从输出;在SPI*2或者SPI*4模式下,MISO1是SPI总线的第二位。 D1_MISO2,D2_MISO3:I,在并口模式下,D1和D2是数据总线的低位;在SPI*4模式下,MISO2和MISO3是SPI总线的MSBs。 An:O,A[25:0]为BPI模式的地址位。配置完成后,变为用户I/O口。 AWAKE:O,电源保存挂起模式的状态输出引脚。SUSPEND是一个专用引脚,AWAKE是一个多功能引脚。除非SUSPEND模式被使能,AWAKE被用作用户I/O。 MOSI_CSI_B_MISO0:I/O,在SPI模式下,主输出或者从输入;在SelectMAP模式下,CSI_B是一个低电平有效的片选信号;在SPI*2或者SPI*4的模式下,MISO0是SPI总线的第一位数据。 FCS_B:O,BPI flash 的片选信号。 FOE_B:O,BPI flash的输出使能信号 FWE_B:O,BPI flash 的写使用信号 LDC:O,BPI模式配置期间为低电平 HDC:O,BPI模式配置期间为高电平 CSO_B:O,在并口模式下,工具链片选信号。在SPI模式下,为SPI flsah片选信号。 IRDY1/2,TRDY1/2:O,在PCI设计中,以LogiCORE IP方式使用。

1.14. translation这一步是用什么DC命令来实现的? 我们知道,DC综合过程包括3个步骤:translation + logic optimization + mapping transition 对应命令为 read_verilog(read_vhdl等) logic optimization 和 mapping 对应于 compile 1.15. 逻辑优化和映射(logic optimization + mapping)又是用什么DC命令来实现的? logic optimization 和 mapping 均在compile命令完成,但是可以指定使用特殊的优化方法:structural 和flatten,建议大家在synthesis时同时生成structural 和flatten格式的netlist,然后打开看看到底有什么不同之处。 1.17. 基于路径的综合的意思是什么? 路径(path),是DC中的一个重要概念。它包括4种路径方式: 1 input到FF的D端。 2 FF的clk到另一个FF的D端。 3 FF的clk到输出Q。 4 input到output。 基于路径的综合就是对这四种路径进行加约束,综合电路以满足这些约束条件。 1.24 reference 是指什么? 和cell 有什么区别? 当存在一个模块被多次例化,那么该模块就称为reference 1.25 如何读入一个design? 使用analyze + elaborate 或者 read_verilog、read -f verilog、 read_vhdl、read_file 命令。 1.26 analyze+ elaborate 和 read 命令有什么区别? read_file 是可以读取任何synopsys支持格式的;analyze和eloborate 只支持verilog和VHDL两个格式,但是他们支持在中间过程中加入参数而且以便以后可以加快读取过程。

Encounter使用入门教程 本教程介绍一下自动布局布线工具Encounter的使用知识,开始以一个简单的十进制计数器版图的自动实现为例子,之后介绍包含block模块的复杂的版图自动实现。 在Designer Compiler使用入门教程中,笔者设计了一个十进制计数器,并经过Design Compiler对其进行综合后获得了门级综合网表文件counter.sv以及约束文件counter.sdc,根据这两个文件,我们就可以使用SOC Encounter实现十进制计数器的物理版图设计了。首先,我们要准备使用Encounter进行版图自动设计时所需要的数据: 时序库文件:fast.lib,slow.lib,tpz973gwc.lib,tpz973gbc.lib 物理库文件:tsmc18_6lm_cic.lef,tpz973g_5lm_cic.lef,tsmc18_6lm_antenna_cic.lef 门级网表文件:pad_counter.sv 时序约束文件:pad_counter.sdc IO位置放置文件:pad_counter.io //在设计导入Encounter中指定PAD的放置位置文件,不是必须文件 还有其它一些文件在后面用到时进行介绍。 一、网表中添加PAD、编写IO Assignment File 这里,pad_counter.sv是加入PAD后综合得到的门级网表。工程项目中设计制作完成后的芯片要进行封装,PAD就是芯片在封装时连接封装引线的地方。一般信号输入/输出PAD即I/O PAD要在综合前添加进入网表中,电源电压PAD 可以在综合时添加也可以在综合后添加。接下来就先介绍一下如何在网表中加入PAD,其实给网表加入PAD就是一般的module例化,和Verilog中一般的module 模块例化是一样的。 这里介绍在综合时给设计中加入I/O PAD。十进制计数器的Verilog源程序如下:module Cnt10(reset_n,clk,in_ena,cnt,carry_ena); input clk; input reset_n; input in_ena; output [3:0] cnt; output carry_ena; reg [3:0] cnt; reg carry_ena; always @(posedge clk or negedge reset_n) begin if(!reset_n) cnt<=4'b0; else if(in_ena && cnt==4'd10)

1.2.1 FPGA工作原理与简介 如前所述,FPGA是在PAL、GAL、EPLD、CPLD等可编程器件的基础上进一步发展的产物。它是作为ASIC领域中的一种半定制电路而出现的,即解决了定制电路的不足,又克服了原有可编程器件门电路有限的缺点。 由于FPGA需要被反复烧写,它实现组合逻辑的基本结构不可能像ASIC那样通过固定的与非门来完成,而只能采用一种易于反复配置的结构。查找表可以很好地满足这一要求,目前主流FPGA都采用了基于SRAM工艺的查找表结构,也有一些军品和宇航级FPGA采用Flash或者熔丝与反熔丝工艺的查找表结构。通过烧写文件改变查找表内容的方法来实现对FPGA的重复配置。 根据数字电路的基本知识可以知道,对于一个n输入的逻辑运算,不管是与或非运算还是异或运算等等,最多只可能存在2n种结果。所以如果事先将相应的结果存放于一个存贮单元,就相当于实现了与非门电路的功能。FPGA的原理也是如此,它通过烧写文件去配置查找表的内容,从而在相同的电路情况下实现了不同的逻辑功能。 查找表(Look-Up-Table)简称为LUT,LUT本质上就是一个RAM。目前FPGA中多使用4输入的LUT,所以每一个LUT可以看成一个有 4位地址线的的RAM。当用户通过原理图或HDL语言描述了一个逻辑电路以后,PLD/FPGA开发软件会自动计算逻辑电路的所有可能结果,并把真值表(即结果)事先写入 RAM,这样,每输入一个信号进行逻辑运算就等于输入一个地址进行查表,找出地址对应的内容,然后输出即可。 下面给出一个4与门电路的例子来说明LUT实现逻辑功能的原理。 例1-1:给出一个使用LUT实现4输入与门电路的真值表。 表1-1 4输入与门的真值表 从中可以看到,LUT具有和逻辑电路相同的功能。实际上,LUT具有更快的执行速度和更大的规模。 由于基于LUT的FPGA具有很高的集成度,其器件密度从数万门到数千万门不等,可以完成极其复杂的时序与逻辑组合逻辑电路功能,所以适用于高速、高密度的高端数字逻辑电路设计领域。其组成部分主要有可编程输入/输出单元、基本可

DC学习----第一章基本概念 作者:未知时间:2010-08-15 15:02:50 来自:网络转载 1.1 启动文件 启动文件用来指定综合工具所需要的一些初始化信息。DC使用名为“.synopsys_dc.setup”的启动文件,启动时,DC会以下述顺序搜索并装载相应目录下的启动文件: 1)、DC的安装目录; 2)、用户的home目录; 3)、当前启动目录。 注意:后装载的启动文件中的设置将覆盖先装载的启动文件中的相同设置。 下面是一个DC启动文件的实例,它包含了几乎所有重要的设置,下文将结合该实例解释启动文件中各项设置的具体含义。 例1-1(一个DC启动文件): search_path= search_path + {“.”, synopsys_root + “/dw/sim_ver” } search_path= search_path + { “~/risc32/synthesis/libraries” } target_library={ tcb773stc.db } synthetic_library={dw_foundation.sldb} link_library = { “*”, dw_foundation.sldb, tcb773stc.db } symbol_library = { tcb773s.sdb } synlib_wait_for_design_license = {"DesignWare-Foundation"} alias rt “report_timing” designer= XXXXX company= “ASIC Lab, Fudan Univ.” search_path指定了综合工具的搜索路径。 target_library为综合的目标库,它一般是由生产线提供的工艺相关的库。 synthetic_library是综合库,它包含了一些可综合的与工艺无关的IP。dw_foundation.sldb是Synopsys提供的名为Design Ware的综合库,它包含了基本的算术运算逻辑、控制逻辑、可综合存储器等IP,在综合是调用这些IP有助于提高电路性能和减少综合时间。 link_library是链接库,它是DC在解释综合后网表时用来参考的库。一般情况下,它和目标库相同;当使用综合库时,需要将该综合库加入链接库列表中。 symbol_library为指定的符号库。 synlib_wait_for_design_license用来获得DesignWare-Foudation的许可(license)。 alias语句与UNIX相似,它定义了命令的简称。 最后的designer和company项则表明了设计者和所在公司。 另外,在启动文件中用符号“/*” 和“*/” 进行注释。 1.2 设计实体 在DC中,总共有8种设计实体: λ设计(Design):一种能完成一定逻辑功能的电路。设计中可以包含下一层的子设计。 单元(Cell):设计中包含的子设计的实例。λ λ参考(Reference):单元的参考对象,即单元是参考的实例。 端口(Port):设计的基本输入输出口。λ λ管脚(Pin):单元的输入输出口。 连线(Net):端口间及管脚间的互连信号。λ λ时钟(Clock):作为时钟信号源的管脚或端口。

简谈Altera和Xilinx的FPGA区别 大家好,又到了每日学习的时间了,最近有很多人再问我学习FPGA到底是选择Altera的还是xilinx的呢,于是我就苦口婆心的说了一大堆,中心思想大概就是,学习FPGA一定要学习FPGA的设计思想以及设计原理,不要纠结于单一的实验平台或者操作软件,因为你想在这个行业越走越高的话,广度和深度都是要有所了解的,初期学习的时候尤其注重动手,选择一款操作平台以及操作软件是为了让你更好的去动手做,而不是让你在这款软件或者实验平台去做文章,因为不懂原理的话,换个环境你同样是什么都不明白。尤其是现在的科技公司产品更新升级换代还比较快,要学会去掌握最核心的知识点才是王道。下面,就我自己接触,咱们就来简单聊聊Altera和Xilinx的FPGA 区别,欢迎大家一起交流,三人行,必有我师,共同学习,共同进步。对于Altera和Xilinx 的FPGA,本人认为可以分为两个方面去比较一下,基本逻辑资源和内部基本架构。从目前企业中做开发使用的广泛性来说,Xilinx占得比重确实是大一些,但是从其他方面来说,比如价格,相对而言Altera的便宜些。对于两者的特点,Xilinx的短线资源非常丰富,这样在实现的时候,布线的成功率很高,尤其是逻辑做得比较满的时候。而Altera的FPGA 的短线资源经常不够用,经常要占用LE来充当布线资源,这也是为什么Altera的FPGA 可以便宜的原因,资源少些当然便宜,但是如果你是高手,也能把他的性能发挥得很好。另外就是关于块RAM,Xilinx的双口RAM是真的,Altera的没有双口RAM,如果你要实现真正的双口RAM,只能用两块RAM来背靠背地实现,这样你的RAM资源就少了一半,如果你的应用对片内双口RAM的需求很重要,用Altera的就划不来。下面咱们就从我刚才说的基本逻辑资源和内部基本架构这两个方面来聊聊。 1.基本逻辑资源基本的逻辑资源我建议大家可以去看看两家的芯片做个比较,今天时间有限就不给各位详谈了,通过比较你会发现我上面说的还是有点道理的。 2.内部基本架构从1985年Xilinx公司推出第一片FPGA到现在,FPGA的使用已经有近30年的历史了。目前主流市场的FPGA主要还是Xilinx和Altera两大系列,下面分别来介绍下它们各自的基本结构组成。 Xilinx的FPGA主要由以下单元结构组成:可配置

DC使用说明 文件说明:在进行下面的演示时需要用到两个文件,一个是example1.v,它是描述一个电路的verilog代码,我们的目标就是用DC综合这个代码得到满足约束条件的电路网表;另一个是dc.scr,它是综合example1.v的脚本文件。这两个文件都在/home/student1000目录下,大家把它们拷贝到自己的目录下,以备使用。DC既可使用图形界面,也可不使用图形界面而直接运行脚本来综合电路。 一、DC图形界面的使用。 1.DC图形界面的启动 1.1 打开一个终端窗口,写入命令dv –db_mode,敲入回车。 则DC图形界面启动,如下图所示

红框处是DC的命令输入框,以下在图形界面上的操作都可以在命令输入框中输入相应的命令来完成。 选择Help----- Man Pages可以查看DC的联机帮助。相应指令:man。例:man man表示 查看man命令的帮助。man create_clock表示查看creat_clock命令的帮助。

2.设置库文件 选择File---- Setup 需要设置以下库文件,如下图。 相应指令: set search_path [list /tools/lib/smic25/feview_s/version1/STD/Synopsys \ /tools/lib/smic25/feview_s/version1/STD/Symbol/synopsys] set target_library { smic25_tt.db } set link_library { smic25_tt.db } set symbol_library { smic25.sdb }

Step1 学习下载配置Xilinx 之FPGA 配合Mars-EDA 的Spartan2 核心板,用图文方式向大家详细讲述如何下载配置Xilinx 的FPGA。 FPGA 下载模式说明 S1 为 FPGA 下载模式选择跳线,M0,M1,M2 默认状态为通过 4.7K 电阻上拉到 3.3V,当用跳线帽短接 S1 的PIN3 和PIN6 将置 M0 为0,同理,短接 PIN2 和PIN5,PIN3 和PIN4 将置 M1,M2 为0。M0,M1,M2 的电平和 FPGA 下载之间的关系参见下图:(Boundary-scan mode)是调试最常用的 JTAG 模式。当采用板载 PROM 时,采用的跳线模式是 Master Serial Mode –短路 PIN1 和PIN6,PIN2 和PIN5 J2 为Slave Serial Mode 的接口。下载模式跳线 S1 短接PIN1 和PIN6,PIN2 和PIN5 即可。 J3 为 JTAG Mode 的接口。下载模式跳线短接 PIN1 和 PIN6 即可。

S2 跳线说明 1.通过 JTAG 方式烧录 FPGA:短接 PIN1 和PIN3。 2.通过 JTAG 方式烧录 PROM:短接 PIN3 和PIN5,PIN2 和PIN4. 3.通过菊花链下载 FPGA 和烧录 PROM:短接 PIN3 和PIN5,PIN4 和PIN6. 下面我们利用 Spartan2 核心板介绍一下通过 JTAG 菊花链方式下载 FPGA 和烧录 PROM. 硬件跳线选择: 1.跳线 S1: 此时要求 M0 M1 M2 = 100, 设置 FPGA 的下载方式为 Boundary-scan mode, 此时将 M1 和M2 的跳线安上。 跳线 S2 : 通过菊花链下载 FPGA 和烧录 PROM:短接 PIN3 和 PIN5,PIN4 和 PIN6. 2.将 Xilinx 下载线和核心板上 JTAG mode 接口 J3 相连,连接到计算机并口。核心板上电。

max_transition可以定义为上升或下降电阻和线网负载的乘积,除了工艺库中提供的,用户也可自己定义,而实际采用的是最严格的那个定义值。 相比较max——transition并不直接控制线网的实际电容,而max_capacitance作为直接控制电容的限制而提出的。但是其cost function是基于总的电容而不是瞬态时间。二者可以同时定义。没有违反约束的定义是:驱动pin或者是port的max capacitance大于或者是等于所有被驱动管的电容之和。 Max transition和max fanout 和max capacitance可以用来决定设计中的buffer个数。―――影响时间参数 优化约束―――对时间的约束优先于对面积的约束。在满足对面积的约束之前,会尽量的考虑满足对时间约束条件的满足。 对时间的约束―――-时序电路中通过对时钟的定义来达到,set input delay和set output delay。 ――――组合电路通过对set max delay和set min delay来设定点点之间的时间延迟,max delay通过设定set max delay和creat clock来达到; 而min delay通过设定set min delay和对保持时间的要求来达到。其中的使用set fix hold来固定保持时间。 优化的过程就是减少代价函数的过程――包括设计规则代价函数和优化代价函数。Max delay cost;min delay cost;max power cost;max area cost; 其中max delay cost是代价函数中具有最优权。 Max delay cost的计算:最差的违背和每个路径组的权重之积――worst violation;path group; 当设计不能满足时序单元的建立时间的要求的时候,违背就发生了。一般,把由一个时钟约束的路径组合成一个路径组,这样每个时钟都建立了一个单独的路径组,而剩余的路径组合成默认的路径组,如果在没有时钟的情况下,所有的路径都组合成一个默认的路径组。而综合总是针对路径进行的,所以很容易给每个路径定义其权重。如:max delay cost=1×1+1×2+1×3=6 min delay cost次重。与路径无关,是所有的最差的min delay违背之和,当实际的延迟时间小于设定的期望的延迟时间的时候,违背就发生了。如:min delay=1+2+3=6 max power是用于ECL电路中。 综合时候的时钟设定: 设定时钟树的时候,使用set dont touch network来设定时钟的dont touch参数值,防止 buffers。 Synopsys的STA不报告时序单元中针对时钟管脚的延迟(认为是理想状态-0)。如果时钟经过门单元的话,则不能认为时钟延迟是0,所以也要设定set clock skew-proagated选项来得到非零的时钟延迟,如果ASIC提供商已经定义了相对于时序单元管脚的潜在的时钟skew的上限的话,可以用set clock skew -uncertainty来定义skew。在设定完时钟之后,我们要使用set input delay和set output delay-option来设定输入输出端口的时间设定。用set multicycle path来设定复合时钟。