西安科技大学

高新学院

微电子专业实验报告

专业:微电子

班级:1001

:黄升

学号:1001050120

指导老师:王进军

设计软件:tanner软件

实验目的和要求:

1、掌握L-edit软件的基本设定和集成电路工艺和版图的图层关系。

2、根据性能和指标要求,明确设计要求和规则。

3、电路版图实现过程中电源线的走法。

4、掌握L-edit和S-edit仿真环境,完成异或门的仿真。

5、掌握LVS环境变量。

异或门版图的设计方法:

1、确定工艺规则。

2、绘制异或门版图。

3、加入工作电源进行分析。

4、与LVS比较仿真结果。

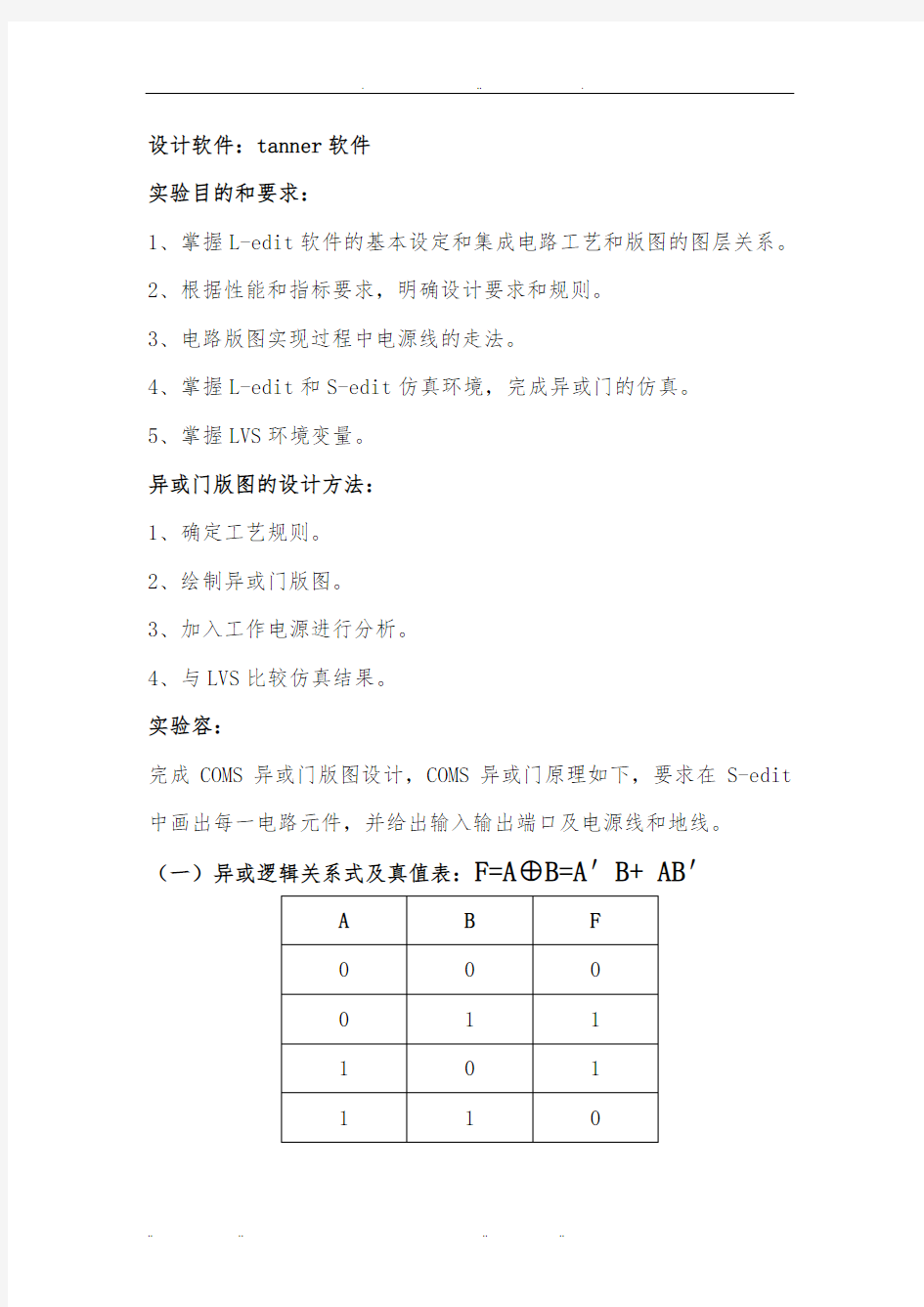

实验容:

完成COMS异或门版图设计,COMS异或门原理如下,要求在S-edit 中画出每一电路元件,并给出输入输出端口及电源线和地线。(一)异或逻辑关系式及真值表:F=A⊕B=A′B+ AB′

(二)原理图:

(三)版图:

(四)仿真分析:

Main circuit:Module0

.include“E:\ProgramFiles\tannerEDA\T-Spice10.1\models\m12_125.md M1 N3 A Gnd Gnd NMOS L=2u W=22u AD=66p PD=24u AS=66p PS=24u

M2 F B N3 Gnd NMOS L=2u W=22u AD=66p PD=24u AS=66p PS=24u

M3 F N3 B Gnd NMOS L=2u W=22u AD=66p PD=24u AS=66p PS=24u

M4 N3 A Vdd Vdd PMOS L=2u W=22u AD=66p PD=24u AS=66p PS=24u

M5 F B A Vdd Vdd PMOS L=2u W=22u AD=66p PD=24u AS=66p PS=24u

M6 F A B Vdd Vdd PMOS L=2u W=22u AD=66p PD=24u AS=66p PS=24u

v7 Vdd Gnd 5.0

v8 B Gnd pulse(0.05.00 In In 100n 200n)

v9 A Gnd pulse(0.05.00 In In 100n 400n)

.tran In 800n

.print tran v(A) v(B) v(F)

End of main circuit:Module0

上升沿下降沿均10n

v8 B Gnd pulse(0.05.00 10In 10In 100n 200n) v9 A Gnd pulse(0.05.00 10In 10In 100n 400n)

*NODE NAMEALASES

* 1=Gnd(10.5,-12)

* 2=Vdd(12,37)

* 4=B(15,12)

* 5=A(5,13)

* 6=F(72,13)

.include“E:\ProgramFiles\tannerEDA\T-Spice10.1\models\m12_125.md M1 F B A Vdd PMOS L=2u W=22u $(68.5 25 70.5 30)

M2 3 A Vdd Vdd PMOS L=2u W=22u $(44.5 25 46.5 30)

M3 F A M4 F B Gnd NMOS L=2u W=22u $(20.5 25 22.5 30)

M4 F B Gnd NMOS L=2u W=22u $(68.5 -3.5 70.5 1.5)

M5 3 A Gnd Gnd NMOS L=2u W=22u $(44.5 -3.5 46.5 1.5)

M6 F 3 B Gnd NMOS L=2u W=22u $(21 -3.5 23 1.5)

v5 Vdd Gnd 5.0

v6 B Gnd pulse(0.05.00 In In 100n 400n)

v7 A Gnd pulse(0.05.00 In In 100n 200n)

.tran In 800n

.print tran v(A) v(B) v(F)