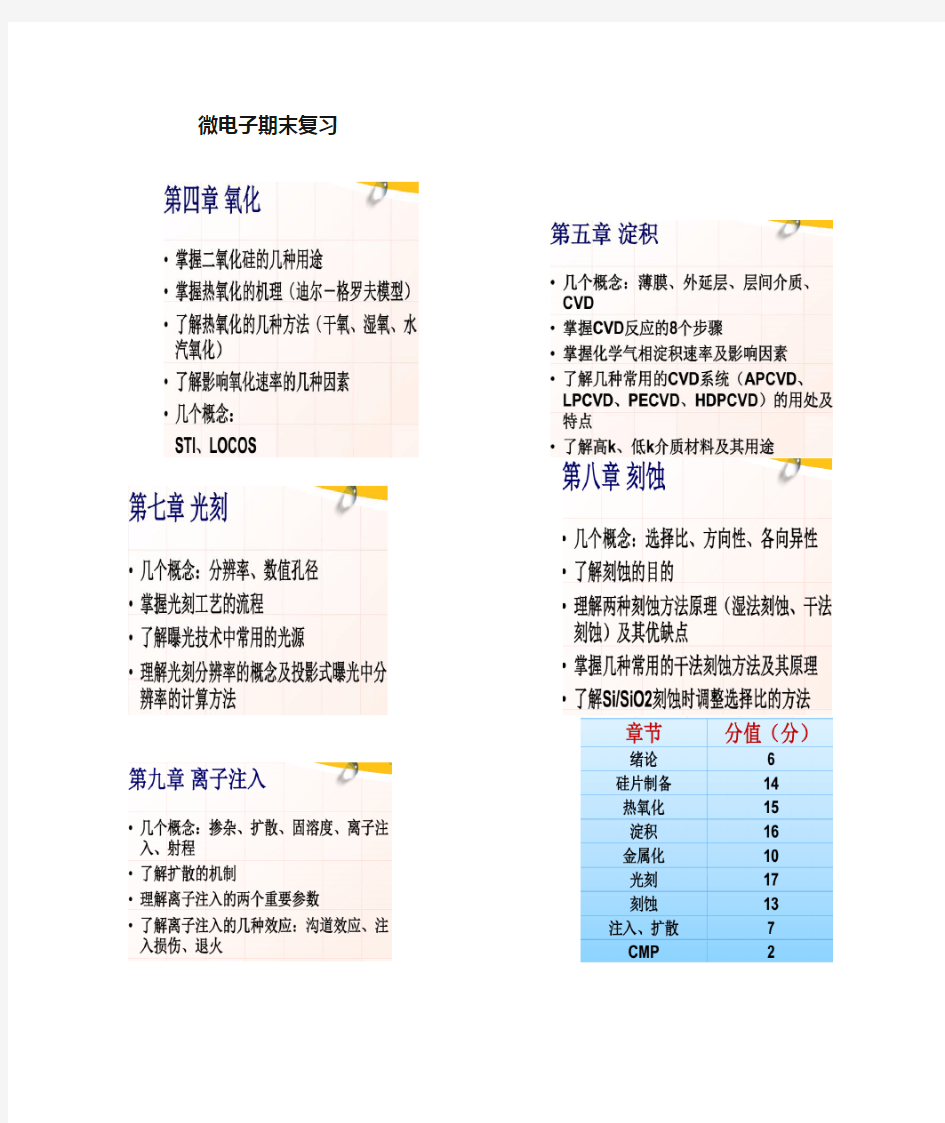

微电子期末复习

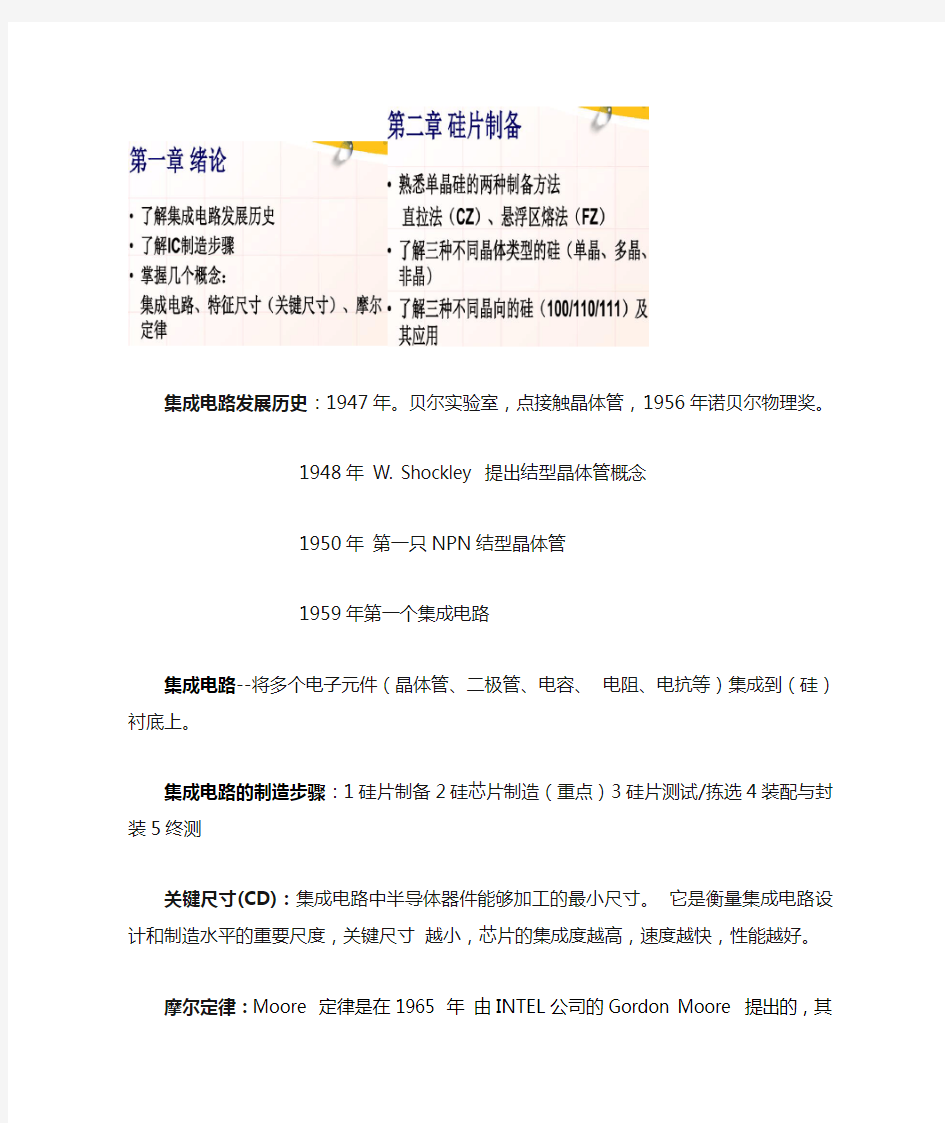

集成电路发展历史:1947年。贝尔实验室,点接触晶体管,1956年诺贝尔物理奖。

1948年 W. Shockley 提出结型晶体管概念

1950年第一只NPN结型晶体管

1959年第一个集成电路

集成电路--将多个电子元件(晶体管、二极管、电容、电阻、电抗等)集成到(硅)衬底上。

集成电路的制造步骤:1硅片制备2硅芯片制造(重点)3硅片测试/拣选4装配与

封装5终测

关键尺寸(CD):集成电路中半导体器件能够加工的最小尺寸。它是衡量集成

电路设计和制造水平的重要尺度,关键尺寸越小,芯片的集成度越高,速度越快,性能越好。

摩尔定律:Moore 定律是在1965 年由INTEL公司的Gordon Moore 提出的,

其内容是:硅集成电路按照4 年为一代,每代的芯片集成度要翻两番、工艺线宽约缩小30%,IC工作速度提高1.5倍等发展规律发展。

单晶硅:单晶硅,也称硅单晶,具有基本完整的点阵结构的晶体。不同的方向

具有不同的性质,是一种良好的半导材料。

1用高纯度的多晶硅在单晶炉内拉制而成

2纯度要求达到99.9999%,甚至达到99.9999999%以上。用于制造半导体器件、太阳能电池等

3半导体市场中95%以上的半导体器件及99%以上的集成电路用硅

多晶硅:1:多晶硅硬度介于锗和石英之间,室温下质脆,切割时易碎裂

2:主要用做半导体的原料,是制做单晶硅的主要原料,可作各种晶体管、整流二极管、可控硅、太阳能电池、集成电路、电子计算机芯片以及红外探测器等。非晶硅:非晶硅是一种直接能带半导体,它的结构内部有许多所谓的“悬键”,

也就是没有和周围的硅原子成键的电子,这些电子在电场作用下就可以产生电流,并不需要声子的帮助,因而非晶硅可以做得很薄,还有制作成本低的优点。

单晶硅的制备方法主要有:1:CZ法(直拉法)

2:悬浮区熔法(CF法)

其本质都是把熔融硅冷却成硅晶体

CZ法:

1:CZ法生长单晶硅把熔化的半导体级硅液体变成有正确晶向并且被掺杂成n或p型的固体硅锭,85%以上的单晶硅是采用CZ法生长,籽晶为所需晶向的单晶硅。

直拉法目的:实现均匀掺杂和复制籽晶结构,得到合适的硅锭直径,限制杂质

引入;

关键参数:拉伸速率和晶体旋转速度。

直拉法长单晶硅工艺过程:引晶,收颈,放肩,等径生长,收尾,冷却,晶

棒

直拉法(CZ法)生长单晶的特点:

优点:1:所生长的单晶的直径较大、成本相对较低

2:通过热场调整及晶转,埚转等工艺参数的优化,可较好控制电阻率径向均匀性

缺点:石英坩埚内壁被熔硅侵蚀及石墨保温加热元件的影响,易引入氧碳杂质,

不易生长高电阻率单晶。

改进直拉生长法-磁控直拉技术:原理:在CZ法生长单晶的基础上对坩埚

内的熔体施加磁场,由于半导体熔体是良导体,在磁场作用下受到与其运动方向相反作用力,于是熔体的热对流受到抑制。因而,除磁体外,主体设备如单晶炉等并无大的差别。

优点:1. 减少温度波动2. 减轻熔硅与坩埚作用3. 使粘滞层厚度增大;4. 降

低了缺陷密度和氧含量

硅单晶掺杂:

1. 在拉制单晶的过程中,在熔体中加入一定量的掺杂剂,就可以对单晶进行掺杂。对于硅来说,常用的P型掺杂剂是硼(B),而N型掺杂剂则是磷(P)。

2. 在掺杂过程中,晶体中的杂质浓度与熔体中的杂质浓度会有差异,用分凝系数(Segregation Coefficient)来表示k0=Cs/Cl,其中Cs和Cl分别是固

体和熔体中的杂质平衡浓度。

单晶生长中的杂质分布:由于分凝系数的存在,导致单晶生长过程中,熔体中的杂质 浓度会不断变化,进而导致单晶中的杂质浓度也会不断变化。 假设熔体中的杂质浓度是均匀的,则单晶中的杂质浓度可用下式表示:

Cs=k0C0(1-X)k0-1 其中:Cs 是单晶中的杂质浓度;C0是熔体中的初始杂质浓度; k0是分凝系数;X 是熔料中已结晶部分的重量比。

例:采用CZ 法生长的硅单晶顶端硼原子浓度为3×1015/CM3,那么当熔料90%已经结晶,剩下10%开始生长时,该处生长的硅单晶中硼浓度是多少?

根据公式C s =k 0C 0

(1-X)k0-1有: C s (x=0)=k 0C 0

=3×1015/cm 3 则C s (x=0.9)=k 0C 0×0.1-0.2=4.75×10

15/cm 3 硅中的晶体缺陷:缺陷密度-在每平方厘米硅片上产生的缺陷数目 点缺陷:原子层面的局部缺陷

位错:错位的晶胞

层错:晶体结构的缺陷

硅片定位边标识:

常用的硅片:CMOS 电路

P type (Boron doped )(100)晶向

电阻率:10~50Ω?cm

BJT (111)晶向

外延层:在单晶衬底上生长的薄层单晶层,其晶体结构与衬底一致,导电类型、

掺杂浓度和厚度可根据需要而定

外延从广义上讲时一种化学气相沉积,它是利用气(或液)态的硅化合物在加热的硅衬底上与氢气反应或自身分解反应,并以单晶形式淀积在硅衬底上的过程。

SiO2在IC中的应用:1:器件和电路的保护层或钝化膜

硅片表面生长一层二氧化硅膜可保护器件内部不受外界影响,提高器件稳定和可靠性。

钝化的前提是膜层质量要好,如果二氧化硅膜中含有大量离子或针孔,非但不能起到钝化作用,反而会造成器件不稳定。

2:某些器件的重要组成部分

(1)MOS管的绝缘栅材料

在MOS管中,常以二氧化硅膜作为栅极,这是因为二氧化硅的电阻率高,介电强度大,几乎不存在漏电流。

绝缘栅要求极高,因为Si-SiO2界面十分敏感(指电学性能),SiO2必须具有高质量。

(2)电容器的介质材料

SiO2介电常数为3~4,击穿电压较高,电容温度系数小,这些性能决定了它是一种优质的电容器介质材料,所以常用作集成电路中的电容器材料。

二氧化硅生长方法简单

3:用作阻挡杂质注入或扩散进入硅中的掩膜

二氧化硅膜起掩蔽作用的两个条件:

(1)厚度足够

(2)所选杂质在二氧化硅中的扩散系数要比在硅中的扩散系数小得多。随着温度升高、扩散时间延长,杂质有可能会扩散穿透二氧化硅膜层,使掩蔽作用失效

4:集成电路的隔离介质

5:用于电极引线和硅器件之间的绝缘介质

热氧化原理

生长机理

一般认为有两种模式:

(1)氧或水汽直接穿过氧表面层上的氧化膜

(2)在高温下,硅原子在二氧化硅界面处,不断夺取二氧化硅中的氧,生成新的氧化膜,使得表面处仍是硅与氧进行氧化,相当于氧原子进入硅中,或硅原子逐步扩散到表面

持前一观点的人多

热氧化经历步骤

(1)氧化剂从气体内部以扩散形式穿过附面层运动到气体与二氧化硅界面;(2)氧化剂以扩散方式穿过二氧化层,到达二氧化硅与硅界面;

(3)氧化剂在硅表面与硅反应生成二氧化硅

(4)反应副产物离开界面

热氧化生长速率——描述氧化物在硅片上生长的快慢

氧化物生长模型是由迪尔(Deal)和格罗夫(Grove)发展的线性-抛物线性模型:

SiO2的生长快慢将由氧化剂在二氧化硅的扩散速度以及与Si 反应速度中较慢的一个因素来决定。即由扩散控制和表面化学反应速率来决定.

当氧化时间很短时,氧化服从线性规律,此时SiO2的生长速率主要由表面化学反应来决定t

ox

=(B/A)t,B/A是线性速率系数

当氧化时间较长时,氧化服从抛物线型规律,此时SiO2的生长速率主要由氧化剂在SiO2中的扩散快慢来决定t ox=(Bt)^0.5,B是抛物线速率系数

影响氧化速率的因素:

压强对氧化速率的影响

晶向对氧化速率的影响

掺杂对氧化速率的影响

掺氯对氧化速率的影响

干氧氧化(Dryoxidation)Si(s)+O

2(g)=SiO

2

(s)

湿氧(Wet)/水汽氧化(Steamoxidation)Si(s)+2H

2O(g)=SiO

2

(s)+2H

2

(g)

这两种反应都在700oC~1200oC之间进行

水汽氧化比干氧氧化反应速率约高10倍

STI---浅沟道隔离工艺

LOCOS---硅的局部氧化技术

薄膜:指某一维度尺寸远小于另外两维上的尺寸的固体物质。与衬底相比,薄膜非常薄。

两种主要的淀积方式:

1)化学气相淀积(CVD):一种或数种物质的气体,以某种方式激活后,在衬底表面发生化学反应,并淀积出所需固体薄膜的生长技术。

例如:APCVD, LPCVD, PECVD, HDPCVD, MOCVD

2)物理气相淀积(PVD):利用某种物理过程实现物质的转移,即将原子或分子转移到衬底(硅)表面上,并淀积成薄膜的技术。

例如:蒸发 evaporation,溅射sputtering,分子束外延MBE

CVD反应的八个步骤:1)反应物的质量传输2)薄膜先驱物反应3)气体分子扩散4)先驱物的吸附5)先驱物扩散到衬底6)表面反应7)副产物的吸附作用8)副产物去除

化学气相淀积速率

1、质量传输限制淀积速率

淀积速率受反应物传输速度限制,即不能提供足够的反应物到衬底表面,速率对温度不敏感(如高压CVD)。

2、反应速度限制淀积速率

淀积速率受反应速度限制,这是由于反应温度或压力过低(传输速率快),提供驱动反应的能量不足,反应速率低于反应物传输速度

可以通过加温、加压提高反应速度

为了获得均匀的淀积速率(厚度),需保证反应区温度均匀分布

介质及其性能:

一、介电常数:介电常数指材料在电场作用下存储电势能的有效性,代表介质作为电容的能力。

(一)低K介质

遇到的问题: 芯片集成度提高,互连线宽和导线间距减小,电阻和寄生电容增大,导致RC信号延迟增加。

低k介质作为层间介质优点:减少相邻导线间的电耦合损失,提高导线的传输速率。

(二)高k介质

为什么要引入高k介质?

(1)在DRAM存储器中引入高k介质,以提高存储电荷(或能

量)密度,简化栅介质结构;

(2)特征尺寸缩小,使栅氧厚度减小到几nm,出现问题:

栅极漏电流增加

多晶硅内杂质扩散到栅氧甚至衬底

控制栅氧厚度在几纳米的难度较大。

金属化:在绝缘介质膜上淀积金属膜以及随后刻印图形以形成互连金属线和

集成电路的孔填充塞的过程。

互连:由导电材料制成的连线将电信号传输到芯片的不同部分,也被用于芯

片上器件和器件整个封装之间的金属连接。

接触:芯片内部的器件与第一金属层间在硅表面的连接。

通孔:穿过各种介质从某金属层到毗邻金属层形成电通路的开口。

填充薄膜:用金属薄膜填充通孔以便在两层金属间形成电连接。

铜大马士革结构

双大马士革方法:在双层介质间刻蚀通孔和槽,接着淀积铜,然后采用化学机械抛光形成图形,这样就同时形成了金属层以及金属层之间的通孔连接。

双大马士革方法的优点:1. 避免金属刻蚀;

2. 金属线间无需再淀积填充介质和介质平坦化,双大马士革方法减少工艺步骤的20% — 30%。

金属淀积系统(热蒸发、溅射)

真空蒸发镀膜:真空蒸发技术是对淀积薄膜的源材料施加热能或动能,使之分解为原子或原子的集合体,并输运到硅片表面后结合或凝聚在硅片表面而形成薄膜。

两种蒸发方式:电阻加热蒸发,电子束蒸发。

溅射:用高能粒子(经电场加速的正离子)冲击作为阴极的固态靶,靶原子与这些高能粒子交换能量后从表面飞出,淀积在作为阳极的硅片上,形成薄膜。离子溅射镀膜过程分为三步:

1. 真空中产生气体正氩离子,加速轰击负电的靶材。

2. 离子通过物理过程从靶上撞击出原子。

3. 溅射的原子迁移到硅片表面形成薄膜。

在硅片制造业中常用的金属及合金:

①互连线-----铝,铝铜合金,铜

②阻挡层金属-----钛钨(TiW)、氮化钛(TiN)等

③金属填充物-----钨(W)、铝(Al)等

光刻的定义:光刻是一种图形复印和化学腐蚀相结合的精密表面加工技术。

光刻工艺流程:1)清洗硅片2)预烘和打底胶3)涂胶4)前烘5)对准6)曝光7)后烘8)显影9)坚膜10)图形检测

分辨率R-表征光刻精度。光刻时所能得到的光刻图形的最小尺寸。

表示方法:每mm最多可容纳的线条数。(或最细线条尺寸)

若可分辨的最小线宽为L(线条间隔也L),则R=1/(2L)(mm -1

)或

R=Kλ/NA(μm)---投影式曝光

K1-系统常数, λ-波长, NA-数值孔径(凸镜收集衍射光的能力)

提高①光学曝光-紫外,深紫外

ⅰ)光源:

高压汞灯:紫外(UV),300-450nm;i线365nm,h线405nm,g线436nm。

准分子激光:深紫外(DUV),180nm~330nm。KrF:λ= 248nm; ArF:λ= 193nm;F2激光器:λ= 157nm。

曝光方式(曝光机)

①遮蔽式曝光:1)接触式:硅片与光刻版紧密接触

2)接近式:硅片与光刻版保持5-50μ m间距。

②投影式曝光:利用光学系统,将光刻版的图形投影在硅片上

下一代曝光方法

②电子束曝光:λ=几十---100?;

优点:分辨率高;

不需光刻版(直写式);

缺点:产量低(适于制备光刻版)

③X射线曝光:λ=2---40? ,软X射线;

X射线曝光的特点:分辨率高,产量大。

④极短紫外光(EUV):λ=10—14nm;

刻蚀工艺的种类

湿法刻蚀:采用化学溶液,借助化学反应腐蚀硅片中无光刻胶覆盖的部分,要求光刻胶有较强的抗蚀能力。

湿法腐蚀具有各向同性,造成侧向腐蚀。限制了器件尺寸向微细化发展,用于特征尺寸较大的刻蚀。

干法刻蚀:把硅片表面曝露于气态中产生的等离子体,等离子体通过光刻胶中开出的窗口,与硅片发生物理或化学反应(或这两种反应),从而去掉曝露的表面材料。

湿法腐蚀的缺点(1)湿法腐蚀是各向同性,干法可以是各向异性

(2)干法腐蚀能达到高的分辨率,湿法腐蚀较差

(3)湿法腐蚀需大量的腐蚀性化学试剂,对人体和环境有害

(4)湿法腐蚀需大量的化学试剂去冲洗腐蚀剂剩余物,不经济干法刻蚀:①化学刻蚀(各项同性,选择性好)——等离子体激活的化学反

应(等离子体刻蚀)

原理:a.产生等离子体:刻蚀气体经辉光放电后,成为具有很强化学活性的离子及游离基--等离子体。

b.等离子体活性基团与被刻蚀材料发生化学反应

②物理刻蚀(各向异性好,选择性差)——高能离子的轰击 (溅射刻蚀)

原理:a. 形成能量很高的等离子体;

b. 等离子体轰击被刻蚀的材料,使其被撞原子飞溅出来,形成刻蚀。

③离子增强刻蚀(各向异性,选择性较好)——反应离子刻蚀

原理:同时利用了溅射刻蚀和等离子刻蚀机制;物理性的离子轰击和化学反应相结合实现刻蚀。

各向异性:各向异性,亦称“非均质性”。物体的全部或部分物理、化学等性质随方向的不同而各自表现出一定的差异的特性。即在不同的方向所测得的性能数值不同。

掺杂:是将一定数量和种类的杂质掺入到半导体中,以改变其电学性质,并使掺入的杂质数量和分布情况都满足要求。

两种掺杂方式:①扩散:掺杂总量及浓度分布受扩散时间和温度影响;形成特征尺寸较大;扩散温度较高,需氧化物或氮化物作为掩膜。

②离子注入:杂质总量及浓度分布受注入剂式量、能量和推结时间及温度决定。

适于小特征尺寸的芯片。注入温度较低,常用光刻胶作为掩膜。

R:射程(range)--------离子在靶内的总路线长度

Rp:投影射程(projected range)---------R在入射方向上的投影

离子注入剂量:注入剂量是单位面积晶圆表面注入的离子数

扩散机制:扩散是粒子由浓度较高的地方向浓度较低的地方进行,从而使得

粒子的分布逐渐趋于均匀;浓度的差别越大,扩散越快;温度越高,扩散也越快。

1.间隙式和替位式杂质

离子注入:离化后的原子在强电场的加速作用下,注射进入靶材料的表层,

以改变这种材料表层的物理或化学性质。

离子注入的参数:(剂量,射程)

注入损伤:高能离子注入硅片后与靶原子发生一系列碰撞,可能使靶原子发生位移,被位移原子还可能把能量依次传给其它原子,结果产生一系列的空位-间隙原子对及其它类型晶格无序的分布。这种因为离子注入所引起的简单或复杂的缺陷统称为晶格损伤。

沟道效应:对晶体靶进行离子注入时,由于晶体排列的特性使得某些角度上有长距离的开口。假如注入离子运动方向与这些隧道般的开口相平行,这些注入的离子将不会与靶原子发生碰撞而深深地注入衬底之中。

高温退火原理:激活杂质(950℃),修复晶格损伤(500℃)

固溶度:溶质固溶于溶剂内所形成的饱和固溶体内溶质的浓度

离子注入的优点:1. 精确控制掺杂浓度2. 很好的杂质均匀性3. 对杂质深度很好控制4. 产生单一离子束5. 低温工艺6. 注入的离子能穿过薄膜7. 无固溶度极限

缺点:1.辐射损伤。高温退火修复。2.设备复杂(比扩散)

化学机械平坦化(CMP)的优缺点:优点:1平坦化2平坦化不同的材料3平坦化多层材料表面4减小严重的表面起伏5制作金属图形的另一种方法6改善金属台阶覆盖7增加IC的可靠性8减少缺陷9不使用危险气体

缺点:1新技术2引入新的缺陷3必须发展别的配套工艺技术4昂贵的设备费用

一、选择题。 1. 电离后向半导体提供空穴的杂质是( A ),电离后向半导体 提供电子的杂质是( B )。 A. 受主杂质 B. 施主杂质 C. 中性杂质 2. 在室温下,半导体Si 中掺入浓度为31410-cm 的磷杂质后,半导体中 多数载流子是( C ),多子浓度为( D ),费米能级的位置( G );一段时间后,再一次向半导体中掺入浓度为 315101.1-?cm 的硼杂质,半导体中多数载流子是( B ),多子浓度为( E ),费米能级的位置( H );如果,此时温度从室温升高至K 550,则杂质半导体费米能级的位置( I )。(已知:室温下,31010-=cm n i ;K 550时,31710-=cm n i ) A. 电子和空穴 B. 空穴 C. 电子 D. 31410-cm E. 31510-cm F. 315101.1-?cm G. 高于i E H. 低于i E I. 等于i E 3. 在室温下,对于n 型硅材料,如果掺杂浓度增加,将导致禁带宽 度( B ),电子浓度和空穴浓度的乘积00p n ( D )2i n ,功函数( C )。如果有光注入的情况下,电子浓度和空穴浓度的乘积np ( E )2i n 。 A. 增加 B. 不变 C. 减小 D. 等于 E. 不等于 F. 不确定 4. 导带底的电子是( C )。

A. 带正电的有效质量为正的粒子 B. 带正电的有效质量为负的准粒子 C. 带负电的有效质量为正的粒子 D. 带负电的有效质量为负的准粒子 5. P 型半导体MIS 结构中发生少子反型时,表面的导电类型与体材 料的类型( B )。在如图所示MIS 结构的C-V 特性图中,代表去强反型的( G )。 A. 相同 B. 不同 C. 无关 D. AB 段 E. CD 段 F. DE 段 G. EF 和GH 段 6. P 型半导体发生强反型的条件( B )。 A. ???? ??= i A S n N q T k V ln 0 B. ???? ??≥i A S n N q T k V ln 20 C. ???? ??=i D S n N q T k V ln 0 D. ??? ? ??≥i D S n N q T k V ln 20 7. 由于载流子存在浓度梯度而产生的电流是( B )电流,由 于载流子在一定电场力的作用下而产生电流是( A )电流。 A. 漂移 B. 扩散 C. 热运动 8. 对于掺杂的硅材料,其电阻率与掺杂浓度和温度的关系如图所示, 其中,AB 段电阻率随温度升高而下降的原因是( A )。 A. 杂质电离和电离杂质散射 B. 本征激发和晶格散射

半导体基础知识和半导体器件工艺 第一章半导体基础知识 通常物质根据其导电性能不同可分成三类。第一类为导体,它可以很好的传导电流,如:金属类,铜、银、铝、金等;电解液类:NaCl水溶液,血液,普通水等以及其它一些物体。第二类为绝缘体,电流不能通过,如橡胶、玻璃、陶瓷、木板等。第三类为半导体,其导电能力介于导体和绝缘体之间,如四族元素Ge锗、Si硅等,三、五族元素的化合物GaAs砷化镓等,二、六族元素的化合物氧化物、硫化物等。 物体的导电能力可以用电阻率来表示。电阻率定义为长1厘米、截面积为1平方厘米的物质的电阻值,单位为欧姆*厘米。电阻率越小说明该物质的导电性能越好。通常导体的电阻率在10-4欧姆*厘米以下,绝缘体的电阻率在109欧姆*厘米以上。 半导体的性质既不象一般的导体,也不同于普通的绝缘体,同时也不仅仅由于它的导电能力介于导体和绝缘体之间,而是由于半导体具有以下的特殊性质: (1) 温度的变化能显著的改变半导体的导电能力。当温度升高时,电阻率会降低。比如Si在200℃时电阻率比室温时的电阻率低几千倍。可以利用半导体的这个特性制成自动控制用的热敏组件(如热敏电阻等),但是由于半导体的这一特性,容易引起热不稳定性,在制作半导体器件时需要考虑器件自身产生的热量,需要考虑器件使用环境的温度等,考虑如何散热,否则将导致器件失效、报废。 (2) 半导体在受到外界光照的作用是导电能力大大提高。如硫化镉受到光照后导电能力可提高几十到几百倍,利用这一特点,可制成光敏三极管、光敏电阻等。 (3) 在纯净的半导体中加入微量(千万分之一)的其它元素(这个过程我们称为掺杂),可使他的导电能力提高百万倍。这是半导体的最初的特征。例如在原子密度为5*1022/cm3的硅中掺进大约5X1015/cm3磷原子,比例为10-7(即千万分之一),硅的导电能力提高了几十万倍。 物质是由原子构成的,而原子是由原子核和围绕它运动的电子组成的。电子很轻、很小,带负电,在一定的轨道上运转;原子核带正电,电荷量与电子的总电荷量相同,两者相互吸引。当原子的外层电子缺少后,整个原子呈现正电,缺少电子的地方产生一个空位,带正电,成为电洞。物体导电通常是由电子和电洞导电。 前面提到掺杂其它元素能改变半导体的导电能力,而参与导电的又分为电子和电洞,这样掺杂的元素(即杂质)可分为两种:施主杂质与受主杂质。 将施主杂质加到硅半导体中后,他与邻近的4个硅原子作用,产生许多自由电子参与导电,而杂质本身失去电子形成正离子,但不是电洞,不能接受电子。这时的半导体叫N型半导体。施主杂质主要为五族元素:锑、磷、砷等。 将施主杂质加到半导体中后,他与邻近的4个硅原子作用,产生许多电洞参与导电,这时的半导体叫p型半导体。受主杂质主要为三族元素:铝、镓、铟、硼等。 电洞和电子都是载子,在相同大小的电场作用下,电子导电的速度比电洞

电子科技大学二零零六至二零零七学年第一学期期末考试半导体物理课程考试题卷( 120分钟)考试形式:闭卷考试日期200 7年 1 月 14日 注:1、本试卷满分70分,平时成绩满分15分,实验成绩满分15分; 2.、本课程总成绩=试卷分数+平时成绩+实验成绩。 课程成绩构成:平时分,期中分,实验分,期末分 一、选择填空(含多选题)(2×20=40分) 1、锗的晶格结构和能带结构分别是( C )。 A. 金刚石型和直接禁带型 B. 闪锌矿型和直接禁带型 C. 金刚石型和间接禁带型 D. 闪锌矿型和间接禁带型 2、简并半导体是指( A )的半导体。 A、(E C -E F )或(E F -E V )≤0 B、(E C -E F )或(E F -E V )≥0 C、能使用玻耳兹曼近似计算载流子浓度 D、导带底和价带顶能容纳多个状态相同的电子 3、在某半导体掺入硼的浓度为1014cm-3, 磷为1015cm-3,则该半导体为( B )半导体;其有效杂质浓度约为( E )。 A. 本征, B. n型, C. p型, D. 1.1×1015cm-3, E. 9×1014cm-3 4、当半导体材料处于热平衡时,其电子浓度与空穴浓度的乘积为( B ),并且该乘积和(E、F )有关,而与( C、D )无关。 A、变化量; B、常数; C、杂质浓度; D、杂质类型; E、禁带宽度; F、温度 5、在一定温度下,对一非简并n型半导体材料,减少掺杂浓度,会使得( C )靠近中间能级E i ;如果增加掺杂浓度,有可能使得( C )进入( A ),实现重掺杂成为简并半导

体。 A 、E c ; B 、E v ; C 、E F ; D 、 E g ; E 、E i 。 67、如果温度升高,半导体中的电离杂质散射概率和晶格振动散射概率的变化分别是(C )。 A 、变大,变大 B 、变小,变小 C 、变小,变大 D 、变大,变小 8、最有效的复合中心能级的位置在(D )附近,最有利于陷阱作用的能级位置位于(C )附近,并且常见的是( E )陷阱。 A 、E A ; B 、E B ; C 、E F ; D 、 E i ; E 、少子; F 、多子。 9、一块半导体寿命τ=15μs ,光照在材料中会产生非平衡载流子,光照突然停止30μs 后,其中非平衡载流子将衰减到原来的( C )。 A 、1/4 B 、1/e C 、1/e 2 D 、1/2 10、半导体中载流子的扩散系数决定于该材料中的( A )。 A 、散射机构; B 、复合机构; C 、杂质浓度梯度; C 、表面复合速度。 11、下图是金属和n 型半导体接触能带图,图中半导体靠近金属的表面形成了(D )。 A 、n 型阻挡层 B 、p 型阻挡层 C 、p 型反阻挡层 D 、n 型反阻挡层 12、欧姆接触是指( D )的金属-半导体接触。 A 、W ms =0 B 、W ms <0 C 、W ms >0 D 、阻值较小并且有对称而线性的伏-安特性 13、MOS 器件中SiO 2层中的固定表面电荷主要是( B ),它能引起半导体表面层中的能带( C )弯曲,要恢复平带,必须在金属与半导体间加( F )。 A .钠离子; B 硅离子.;C.向下;D.向上;E. 正电压;F. 负电压 二、证明题:(8分) 由金属-SiO 2-P 型硅组成的MOS 结构,当外加的电压使得半导体表面载流子浓度n s 与内部多数载流子浓度P p0相等时作为临界强反型层条件,试证明:此时半导体的表面势为: 证明:设半导体的表面势为V S ,则表面的电子浓度为: 200exp()exp()S i S s p p qV n qV n n KT p KT == (2分) 当n s =p p0时,有:20exp( ),S p i qV p n KT = (1分)

---------------------------------------------------------------最新资料推荐------------------------------------------------------ 2015半导体物理器件期末考试试题(全) 半导体物理器件原理(期末试题大纲)指导老师:陈建萍一、简答题(共 6 题,每题 4 分)。 代表试卷已出的题目1、耗尽区:半导体内部净正电荷与净负电荷区域,因为它不存在任何可动的电荷,为耗尽区(空间电荷区的另一种称呼)。 2、势垒电容:由于耗尽区内的正负电荷在空间上分离而具有的电容充放电效应,即反偏 Fpn 结的电容。 3、Pn 结击穿:在特定的反偏电压下,反偏电流迅速增大的现象。 4、欧姆接触:金属半导体接触电阻很低,且在结两边都能形成电流的接触。 5、饱和电压:栅结耗尽层在漏端刚好夹断时所加的漏源电压。 6、阈值电压:达到阈值反型点所需的栅压。 7、基区宽度调制效应:随 C-E 结电压或 C-B 结电压的变化,中性基区宽度的变化。 8、截止频率:共发射极电流增益的幅值为 1 时的频率。 9、厄利效应:基带宽度调制的另一种称呼(晶体管有效基区宽度随集电结偏置电压的变化而变化的一种现象) 10、隧道效应:粒子穿透薄层势垒的量子力学现象。 11、爱因斯坦关系:扩散系数和迁移率的关系: 12、扩散电容:正偏 pn 结内由于少子的存储效应而形成的电容。 1/ 11

13、空间电荷区:冶金结两侧由于 n 区内施主电离和 p 区内受主电离

---------------------------------------------------------------最新资料推荐------------------------------------------------------ 而形成的带净正电荷与净负电荷的区域。 14、单边突变结:冶金结的一侧的掺杂浓度远大于另一侧的掺杂浓度的 pn 结。 15、界面态:氧化层--半导体界面处禁带宽度中允许的电子能态。 16、平带电压:平带条件发生时所加的栅压,此时在氧化层下面的半导体中没有空间电荷区。 17、阈值反型点:反型电荷密度等于掺杂浓度时的情形。 18、表面散射:当载流子在源极和源漏极漂移时,氧化层--半导体界面处载流子的电场吸引作用和库伦排斥作用。 19、雪崩击穿:由雪崩倍增效应引起的反向电流的急剧增大,称为雪崩击穿。 20、内建电场:n 区和 p 区的净正电荷和负电荷在冶金结附近感生出的电场叫内建电场,方向由正电荷区指向负电荷区,就是由 n 区指向 p 区。 21、齐纳击穿:在重掺杂 pn 结内,反偏条件下结两侧的导带与价带离得非常近,以至于电子可以由 p 区的价带直接隧穿到 n 区的导带的现象。 22、大注入效应:大注入下,晶体管内产生三种物理现象,既三个效应,分别称为:(1)基区电导调制效应;(2)有效基区扩展效应; (3)发射结电流集边效应。 它们都将造成晶体管电流放大系数的下降。 3/ 11

《半导体物体复习资料》 1、本征半导体是指(A )的半导体。 A. 不含杂质和晶格缺陷 B. 电阻率最高 C. 电子密度和空穴密度相等 D. 电子密度与本征载流子密度相等 2、如果一半导体的导带中发现电子的几率为零,那么该半导体必定( D )。 A. 不含施主杂质 B. 不含受主杂质 C. 不含任何杂质 D. 处于绝对零度 3、对于只含一种杂质的非简并n型半导体,费米能级E F随温度上升而( D )。 A. 单调上升 B. 单调下降 C. 经过一个极小值趋近Ei D. 经过一个极大值趋近Ei 4、如某材料电阻率随温度上升而先下降后上升,该材料为( C )。 A. 金属 B. 本征半导体 C. 掺杂半导体 D. 高纯化合物半导体 5、公式中的是半导体载流子的( C )。 A. 迁移时间 B. 寿命 C. 平均自由时间 D. 扩散时间 6、下面情况下的材料中,室温时功函数最大的是( A ) A. 含硼1×1015cm-3的硅 B. 含磷1×1016cm-3的硅 C. 含硼1×1015cm-3,磷1×1016cm-3的硅 D. 纯净的硅 7、室温下,如在半导体Si中,同时掺有1×1014cm-3的硼和1.1×1015cm-3的磷,则电子浓度约为( B ),空穴浓度为( D ),费米能级为( G )。将该半导体由室温度升至570K,则多子浓度约为( F ),少子浓度为( F ),费米能级为( I )。(已知:室温下, n i≈1.5×1010cm-3;570K时,n i≈2×1017cm-3) A、1×1014cm-3 B、1×1015cm-3 C、1.1×1015cm-3 D、2.25×105cm-3 E、1.2×1015cm-3 F、2×1017cm-3 G、高于Ei H、低于Ei I、等于Ei 8、最有效的复合中心能级位置在( D )附近;最有利陷阱作用的能级位置在( C )附近,常见的是( E )陷阱。 A、E A B、E D C、E F D、Ei E、少子 F、多子 10、对大注入条件下,在一定的温度下,非平衡载流子的寿命与( D )。

半导体技术期末复习集团文件发布号:(9816-UATWW-MWUB-WUNN-INNUL-DQQTY-

1.20世纪上半叶对半导体产业发展做出贡献的4种不同产业。P2 答:真空管电子学、无线电通信、机械制表机、固体物理 2.列出5个集成时代,指出每个时代的时间段,并给出每个时代每个芯片上的元件数。P4 小规模集成电路 20世纪60年代前期 2-50个芯片 中规模集成电路 20世纪60年代到70年代前期 20-5000个芯片 大规模集成电路 20世纪70年代前期到70年代后期 5000-100000个芯片 超大规模集成电路20世纪70年代后期到80年代后期个芯片 甚大规模集成电路 20世纪90年代后期至今大于1000000个芯片 3.列出提高微芯片制造技术相关的三个重要趋势,简要描述每个趋势。P8 1、提高芯片性能:提高速度和降低功耗。1)、器件做的越小,芯片上的器件就越多,芯片的速度就提高;2)、使用材料,通过芯片表面的电路和器件来提高电信号的传输。 2、提高芯片可靠性 3、降低芯片成本 原因:根本原因是得益于CD尺存的减小;半导体产品市场的大幅度增长。 4.什么是芯片的关键尺寸?这种尺寸为何重要?P9 芯片的物理尺寸特征被称为特征尺寸,最小的特征尺寸称为关键尺寸。

将CD作为定义制造复杂性水平的标准,也就是如果你拥有在硅片上制造某种CD的能力,那你就能加工其他所有特征尺寸,由于这些尺寸更大,因此更容易生产。例如,如果芯片上的最小尺寸是0.18um,那么这个尺寸就是CD。半导体产业使用“技术节点”这一术语描述在硅片制造中使用的可应用CD . 5.什么是摩尔定律?它预测了什么?这个定律正确吗?P10 1964年摩尔预言在一块芯片上的晶体管数大约每隔一年翻一番(后来在1975年被修正为预计每18个月翻一番)。摩尔定律惊人的准确! 6.以B掺入Si中为例,说明什么是受主杂质、受主杂质电离过程和P型半导体。 在硅晶体中掺入硼,硼是Ⅲ族元素,硼替代原有硅原子位置,由于Ⅲ族元素最外层只有3个价电子,与周围硅原子产生共价键时,产生一个空穴,而本身接受一个电子称为带负电的离子,通常我们称这种杂质为受主杂质。这种半导体主要依靠受主提供的空穴导电,这种依靠空穴导电的半导体称为p型半导体。 7.以As掺入Ge中为例,说明什么是施主杂质、施主杂质电离过程和N 型半导体。 在As中掺入Ge , Ge 是V族元素杂质, Ge杂质会替代原来硅原子的位置,与周围的硅原子形成共价键,多余的一个电子便成了能够导电的自由电子,本身变成带正电的离子,通常我们称这种杂质为施主杂质。这种半导体依靠施主提供的电子导电,这种依靠电子导电的半导体称为n型半导体。

一、填空题 1.纯净半导体Si 中掺V 族元素的杂质,当杂质电离时释放 电子 。这种杂质称 施主 杂质;相应的半导体称 N 型半导体。 2.当半导体中载流子浓度的分布不均匀时,载流子将做 扩散 运动;在半导体存在外加电压情况下,载流子将做 漂移 运动。 3.n o p o =n i 2标志着半导体处于 平衡 状态,当半导体掺入的杂质含量改变时,乘积n o p o 改变否? 不变 ;当温度变化时,n o p o 改变否? 改变 。 4.非平衡载流子通过 复合作用 而消失, 非平衡载流子的平均生存时间 叫做寿命τ,寿命τ与 复合中心 在 禁带 中的位置密切相关,对于强p 型和 强n 型材料,小注入时寿命τn 为 ,寿命τp 为 . 5. 迁移率 是反映载流子在电场作用下运动难易程度的物理量, 扩散系数 是反映有浓度梯度时载流子运动难易程度的物理量,联系两者的关系式是 q n n 0=μ ,称为 爱因斯坦 关系式。 6.半导体中的载流子主要受到两种散射,它们分别是电离杂质散射 和 晶格振动散射 。前者在 电离施主或电离受主形成的库伦势场 下起主要作用,后者在 温度高 下起主要作用。 7.半导体中浅能级杂质的主要作用是 影响半导体中载流子浓度和导电类型 ;深能级杂质所起的主要作用 对载流子进行复合作用 。 8、有3个硅样品,其掺杂情况分别是:甲 含铝1015cm -3 乙. 含硼和磷各1017 cm -3 丙 含镓1017 cm -3 室温下,这些样品的电阻率由高到低的顺序是 乙 甲 丙 。样品的电子迁移率由高到低的顺序是甲丙乙 。费米能级由高到低的顺序是 乙> 甲> 丙 。 9.对n 型半导体,如果以E F 和E C 的相对位置作为衡量简并化与非简并化的标准,那么 T k E E F C 02>- 为非简并条件; T k E E F C 020≤-< 为弱简并条件; 0≤-F C E E 为简并条件。 10.当P-N 结施加反向偏压增大到某一数值时,反向电流密度突然开始迅速增大的现象称为 PN 结击穿 ,其种类为: 雪崩击穿 、和 齐纳击穿(或隧道击穿) 。 11.指出下图各表示的是什么类型半导体? 12. 以长声学波为主要散射机构时,电子迁移率μn 与温度的 -3/2 次方成正比 13 半导体中载流子的扩散系数决定于其中的 载流子的浓度梯度 。 14 电子在晶体中的共有化运动指的是 电子不再完全局限在某一个原子上,而是可以从晶胞中某一点自由地运动到其他晶胞内的对应点,因而电子可以在整个晶体中运动 。 二、选择题 1根据费米分布函数,电子占据(E F +kT )能级的几率 B 。 A .等于空穴占据(E F +kT )能级的几率 B .等于空穴占据(E F -kT )能级的几率 C .大于电子占据E F 的几率 D .大于空穴占据 E F 的几率 2有效陷阱中心的位置靠近 D 。 A. 导带底 B.禁带中线 C .价带顶 D .费米能级 3对于只含一种杂质的非简并n 型半导体,费米能级E f 随温度上升而 D 。 A. 单调上升 B. 单调下降 C .经过一极小值趋近E i D .经过一极大值趋近E i 7若某半导体导带中发现电子的几率为零,则该半导体必定_D _。 A .不含施主杂质 B .不含受主杂质 C .不含任何杂质 D .处于绝对零度

电子科技大学二零零 七 至二零零 八 学年第 一 学期期 末 考试 一、选择填空(22分) 1、在硅和锗的能带结构中,在布里渊中心存在两个极大值重合的价带,外面的能带( B ), 对应的有效质量( C ),称该能带中的空穴为( E )。 A. 曲率大; B. 曲率小; C. 大; D. 小; E. 重空穴; F. 轻空穴 2、如果杂质既有施主的作用又有受主的作用,则这种杂质称为( F )。 A. 施主 B. 受主 C.复合中心 D.陷阱 F. 两性杂质 3、在通常情况下,GaN 呈( A )型结构,具有( C ),它是( F )半导体材料。 A. 纤锌矿型; B. 闪锌矿型; C. 六方对称性; D. 立方对称性; E.间接带隙; F. 直接带隙。 4、同一种施主杂质掺入甲、乙两种半导体,如果甲的相对介电常数εr 是乙的3/4, m n */m 0值是乙的2倍,那么用类氢模型计算结果是( D )。 A.甲的施主杂质电离能是乙的8/3,弱束缚电子基态轨道半径为乙的3/4 B.甲的施主杂质电离能是乙的3/2,弱束缚电子基态轨道半径为乙的32/9 C.甲的施主杂质电离能是乙的16/3,弱束缚电子基态轨道半径为乙的8/3 D.甲的施主杂质电离能是乙的32/9,的弱束缚电子基态轨道半径为乙的3/8 5、.一块半导体寿命τ=15μs ,光照在材料中会产生非平衡载流子,光照突然停止30μs 后,其中非平衡载流子将衰减到原来的( C )。 A.1/4 ; B.1/e ; C.1/e 2 ; D.1/2 6、对于同时存在一种施主杂质和一种受主杂质的均匀掺杂的非简并半导体,在温度足够高、n i >> /N D -N A / 时,半导体具有 ( B ) 半导体的导电特性。 A. 非本征 B.本征 7、在室温下,非简并Si 中电子扩散系数D n与ND有如下图 (C ) 所示的最恰当的依赖关系: Dn Dn Dn Dn A B C D 8、在纯的半导体硅中掺入硼,在一定的温度下,当掺入的浓度增加时,费米能级向( A )移动;当掺 ND ND ND ND

实验一半导体材料的缺陷显示及观察

实验一半导体材料的缺陷显示及观察 实验目的 1.掌握半导体的缺陷显示技术、金相观察技术; 2.了解缺陷显示原理,位错的各晶面上的腐蚀图象的几何特性; 3.了解层错和位错的测试方法。 一、实验原理 半导体晶体在其生长过程或器件制作过程中都会产生许多晶体结构缺陷,缺陷的存在直接影响着晶体的物理性质及电学性能,晶体缺陷的研究在半导体技术上有着重要的意义。 半导体晶体的缺陷可以分为宏观缺陷和微观缺陷,微观缺陷又分点缺陷、线缺陷和面缺陷。位错是半导体中的主要缺陷,属于线缺陷;层错是面缺陷。 在晶体中,由于部分原子滑移的结果造成晶格排列的“错乱”,因而产生位错。所谓“位错线”,就是晶体中的滑移区与未滑移区的交界线,但并不是几何学上定义的线,而近乎是有一定宽度的“管道”。位错线只能终止在晶体表面或晶粒间界上,不能终止在晶粒内部。位错的存在意味着晶体的晶格受到破坏,晶体中原子的排列在位错处已失去原有的周期性,其平均能量比其它区域的原子能量大,原子不再是稳定的,所以在位错线附近不仅是高应力区,同时也是杂质的富集区。因而,位错区就较晶格完整区对化学腐蚀剂的作用灵敏些,也就是说位错区的腐蚀速度大于非位错区的腐蚀速度,这样我们就可以通过腐蚀坑的图象来显示位错。 位错的显示一般都是利用校验过的化学显示腐蚀剂来完成。腐蚀剂按其用途来分,可分为化学抛光剂与缺陷显示剂,缺陷显示剂就其腐蚀出图样的特点又可分为择优的和非择优的。 位错腐蚀坑的形状与腐蚀表面的晶向有关,与腐蚀剂的成分,腐蚀条件有关,与样品的性质也有关,影响腐蚀的因素相当繁杂,需要实践和熟悉的过程,以硅为例,表1列出硅中位错在各种界面上的腐蚀图象。 二、位错蚀坑的形状 仅供学习与交流,如有侵权请联系网站删除谢谢2

电子科技大学二零一零至二零一一学年第一学期期末考试 1.对于大注入下的直接辐射复合,非平衡载流子的寿命与(D ) A. 平衡载流子浓度成正比 B. 非平衡载流子浓度成正比 C. 平衡载流子浓度成反比 D. 非平衡载流子浓度成反比 2.有3个硅样品,其掺杂情况分别是: 甲.含铝1×10-15cm-3乙.含硼和磷各1×10-17cm-3丙.含镓1×10-17cm-3 室温下,这些样品的电阻率由高到低的顺序是(C ) A.甲乙丙 B. 甲丙乙 C. 乙甲丙 D. 丙甲乙 3.题2中样品的电子迁移率由高到低的顺序是( B ) 4.题2中费米能级由高到低的顺序是( C ) 5. 欧姆接触是指( D )的金属一半导体接触 A. W ms = 0 B. W ms < 0 C. W ms > 0 D. 阻值较小且具有对称而线性的伏安特性 6.有效复合中心的能级必靠近( A ) A.禁带中部 B.导带 C.价带 D.费米能级 7.当一种n型半导体的少子寿命由直接辐射复合决定时,其小注入下的少子寿命正比于(C ) A.1/n0 B.1/△n C.1/p0 D.1/△p 8.半导体中载流子的扩散系数决定于其中的( A ) A.散射机构 B. 复合机构 C.杂质浓变梯度 D.表面复合速度 9.MOS 器件绝缘层中的可动电荷是( C ) A. 电子 B. 空穴 C. 钠离子 D. 硅离子 10.以下4种半导体中最适合于制作高温器件的是( D ) A. Si B. Ge C. GaAs D. GaN 二、解释并区别下列术语的物理意义(30 分,7+7+8+8,共4 题) 1. 有效质量、纵向有效质量与横向有效质量(7 分) 答:有效质量:由于半导体中载流子既受到外场力作用,又受到半导体内部周期性势场作用。有效概括了半导体内部周期性势场的作用,使外场力和载流子加速度直接联系起来。在直接由实验测得的有效质量后,可以很方便的解决电子的运动规律。(3分) 纵向有效质量、横向有效质量:由于k空间等能面是椭球面,有效质量各向异性,在回旋共振实验中,当磁感应强度相对晶轴有不同取向时,可以得到为数不等的吸收峰。我们引入纵向有效质量跟横向有效质量表示旋转椭球等能面纵向有效质量和横向有效质量。(4分) 2. 扩散长度、牵引长度与德拜长度(7 分) 答:扩散长度:指的是非平衡载流子在复合前所能扩散深入样品的平均距离。由扩散系数

半导体测试技术实践总结报告 一、实践目的 半导体测试技术及仪器集中学习是在课堂结束之后在实习地集中的实践性教学,是各项课间的综合应用,是巩固和深化课堂所学知识的必要环节。学习半导体器件与集成电路性能参数的测试原理、测试方法,掌握现代测试设备的结构原理、操作方法与测试结果的分析方法,并学以致用、理论联系实际,巩固和理解所学的理论知识。同时了解测试技术的发展现状、趋势以及本专业的发展现状,把握科技前进脉搏,拓宽专业知识面,开阔专业视野,从而巩固专业思想,明确努力方向。另外,培养在实际测试过程中发现问题、分析问题、解决问题和独立工作的能力,增强综合实践能力,建立劳动观念、实践观念和创新意识,树立实事求是、严肃认真的科学态度,提高综合素质。 二、实践安排(含时间、地点、内容等) 实践地点:西安西谷微电子有限责任公司 实践时间:2014年8月5日—2014年8月15日 实践内容:对分立器件,集成电路等进行性能测试并判定是否失效 三、实践过程和具体内容 西安西谷微电子有限责任公司专业从事集成电路测试、筛选、测试软硬件开发及相关技术配套服务,测试筛选使用标准主要为GJB548、GJB528、GJB360等。 1、认识半导体及测试设备

在一个器件封装之后,需要经过生产流程中的再次测试。这次测试称为“Final test”(即我们常说的FT测试)或“Package test”。在电路的特性要求界限方面,FT测试通常执行比CP测试更为严格的标准。芯片也许会在多组温度条件下进行多次测试以确保那些对温度敏感的特征参数。商业用途(民品)芯片通常会经过0℃、25℃和75℃条件下的测试,而军事用途(军品)芯片则需要经过-55℃、25℃和125℃。 芯片可以封装成不同的封装形式,图4显示了其中的一些样例。一些常用的封装形式如下表: DIP: Dual Inline Package (dual indicates the package has pins on two sides) 双列直插式 CerDIP:Ceramic Dual Inline Package 陶瓷 PDIP: Plastic Dual Inline Package 塑料 PGA: Pin Grid Array 管脚阵列

第一章: 基本概念与名词解释 1、光子学说的几个基本概念:相格、光子简并度等; 2、微观粒子的四个统计分布规律:麦克斯韦速率分布率、波耳兹曼分布率、费米分布率、玻色分布率; 3、原子、分子的微观结构,固体的能带; 4、热辐射和黑体辐射的几个概念:热辐射、朗伯体、视见函数、普朗克公式; 5、简述辐射跃迁的三种过程:自发辐射、受激吸收、受激辐射; 6、谱线加宽的类型及定义:均匀加宽、非均匀加宽、碰撞加宽;

第二章: 基本概念与名词解释 1、一般概念:激发态能级寿命、亚稳态能级、粒子数反转、 负温度、激活介质、增益饱和; 2、三能级系统、四能级系统的粒子数反转的形成过程; 3、关于介质中的烧孔效应、气体激光器中的烧孔效应的论述。理论推导与证明 1、粒子数密度的差值(式2-1-17,2-1-22); 2、均匀加宽与非均匀加宽的小信号增益系数(式2-2-14,2-2-15); 3、均匀加宽与非均匀加宽情况下的大信号反转粒子数密度、烧孔面积(式2-3-3,2-3-7); 4、均匀加宽与非均匀加宽情况下的大信号增益系数(式2-3-10,2-3-17);

第三章: 基本概念与名词解释 1、激光的几个特性:包括时间相干性、空间相干性、相干时间、相干长度、相干面积、相干体积、光子简并度; 2、有关谐振腔的基本概念:谐振腔、稳定腔、不稳定腔、介稳腔; 3、激光振荡的几个现象和过程:纵模、横模、模的竞争、空间 烧孔、兰姆凹陷、频率牵引、高斯光束、激光器最佳透过率。 理论推导与证明 1、普通光源相干时间与相干面积(式3-1-5,3-1-12); 2、激光产生的阈值条件(式3-3-11); 3、粒子数密度的差值的阈值(式3-3-18); 4、均匀加宽情况单模激光器的输出功率与最佳透过率(式3-6-9) 5、非均匀加宽情况单模激光器的输出功率(式3-6-18)。

一、填空题 1.纯净半导体Si 中掺错误!未找到引用源。族元素的杂质,当杂质电离时释放 电子 。这种杂质称 施主 杂质;相应的半导体称 N 型半导体。 2.当半导体中载流子浓度的分布不均匀时,载流子将做 扩散 运动;在半导体存在外加电压情况下,载流子将做 漂移 运动。 3.n o p o =n i 2标志着半导体处于 平衡 状态,当半导体掺入的杂质含量改变时,乘积n o p o 改变否? 不变 ;当温度变化时,n o p o 改变否? 改变 。 4.非平衡载流子通过 复合作用 而消失, 非平衡载流子的平均生存时间 叫做寿命τ,寿命τ与 复合中心 在 禁带 中的位置密切相关,对于强p 型和 强n 型材料,小注入时寿命τn 为 ,寿命τp 为 . 5. 迁移率 是反映载流子在电场作用下运动难易程度的物理量, 扩散系数 是反映有浓度梯度时载 q n n 0=μ ,称为 爱因斯坦 关系式。 6.半导体中的载流子主要受到两种散射,它们分别是电离杂质散射 和 晶格振动散射 。前者在 电离施主或电离受主形成的库伦势场 下起主要作用,后者在 温度高 下起主要作用。 7.半导体中浅能级杂质的主要作用是 影响半导体中载流子浓度和导电类型 ;深能级杂质所起的主要作用 对载流子进行复合作用 。 8、有3个硅样品,其掺杂情况分别是:甲 含铝1015cm -3 乙. 含硼和磷各1017 cm -3 丙 含镓1017 cm -3 室温下,这些样品的电阻率由高到低的顺序是 乙 甲 丙 。样品的电子迁移率由高到低的顺序是甲丙乙 。费米能级由高到低的顺序是 乙> 甲> 丙 。 9.对n 型半导体,如果以E F 和E C 的相对位置作为衡量简并化与非简并化的标准,那么 T k E E F C 02>- 为非简并条件; T k E E F C 020≤-< 为弱简并条件; 0≤-F C E E 为简并条件。 10.当P-N 结施加反向偏压增大到某一数值时,反向电流密度突然开始迅速增大的现象称为 PN 结击穿 ,其种类为: 雪崩击穿 、和 齐纳击穿(或隧道击穿) 。 11.指出下图各表示的是什么类型半导体? 12. 以长声学波为主要散射机构时,电子迁移率μn 与温度的 -3/2 次方成正比 13 半导体中载流子的扩散系数决定于其中的 载流子的浓度梯度 。 14 电子在晶体中的共有化运动指的是 电子不再完全局限在某一个原子上,而是可以从晶胞中某一点自由地运动到其他晶胞内的对应点,因而电子可以在整个晶体中运动 。 二、选择题 1根据费米分布函数,电子占据(E F +kT )能级的几率 B 。 A .等于空穴占据(E F +kT )能级的几率 B .等于空穴占据(E F -kT )能级的几率 C .大于电子占据E F 的几率 D .大于空穴占据 E F 的几率 2有效陷阱中心的位置靠近 D 。 A. 导带底 B.禁带中线 C .价带顶 D .费米能级 3对于只含一种杂质的非简并n 型半导体,费米能级E f 随温度上升而 D 。 A. 单调上升 B. 单调下降 C .经过一极小值趋近E i D .经过一极大值趋近E i 7若某半导体导带中发现电子的几率为零,则该半导体必定_D _。 A .不含施主杂质 B .不含受主杂质 C .不含任何杂质 D .处于绝对零度

1.与绝缘体相比,半导体的价带电子激发到导带所需要的能量 ( B )。 A. 比绝缘体的大 B.比绝缘体的小 C. 和绝缘体的相同 2.受主杂质电离后向半导体提供( B ),施主杂质电离后向半 导体提供( C ),本征激发向半导体提供( A )。 A. 电子和空穴 B.空穴 C. 电子 3.对于一定的N型半导体材料,在温度一定时,减小掺杂浓度,费 米能级会( B )。 A.上移 B.下移 C.不变 4.在热平衡状态时,P型半导体中的电子浓度和空穴浓度的乘积为 常数,它和( B )有关 A.杂质浓度和温度 B.温度和禁带宽度 C.杂质浓度和禁带宽度 D.杂质类型和温度 5.MIS结构发生多子积累时,表面的导电类型与体材料的类型 ( B )。 A.相同 B.不同 C.无关 6.空穴是( B )。 A.带正电的质量为正的粒子 B.带正电的质量为正的准粒子 C.带正电的质量为负的准粒子 D.带负电的质量为负的准粒子 7.砷化稼的能带结构是( A )能隙结构。 A. 直接 B.间接 8.将Si掺杂入GaAs中,若Si取代Ga则起( A )杂质作

用,若Si 取代As 则起( B )杂质作用。 A. 施主 B. 受主 C. 陷阱 D. 复合中心 9. 在热力学温度零度时,能量比F E 小的量子态被电子占据的概率为 ( D ),当温度大于热力学温度零度时,能量比F E 小的 量子态被电子占据的概率为( A )。 A. 大于1/2 B. 小于1/2 C. 等于1/2 D. 等于1 E. 等于0 10. 如图所示的P 型半导体MIS 结构 的C-V 特性图中,AB 段代表 ( A ),CD 段代表(B )。 A. 多子积累 B. 多子耗尽 C. 少子反型 D. 平带状态 11. P 型半导体发生强反型的条件( B )。 A. ???? ??=i A S n N q T k V ln 0 B. ??? ? ??≥i A S n N q T k V ln 20 C. ???? ??=i D S n N q T k V ln 0 D. ??? ? ??≥i D S n N q T k V ln 20 12. 金属和半导体接触分为:( B )。 A. 整流的肖特基接触和整流的欧姆接触 B. 整流的肖特基接触和非整流的欧姆接触 C. 非整流的肖特基接触和整流的欧姆接触 D. 非整流的肖特基接触和非整流的欧姆接触 13. 一块半导体材料,光照在材料中会产生非平衡载流子,若光照

大三下:半导体物理期末复习考点整理 重要:15年6月底期末考试原卷(除了计算题改成了书上的原题,其他题目完全一样),书上的计算题难度和这上面的难度一样,是基础计算共30分强烈建议考前翻翻这篇pdf附近有关的推广链接,有这类题型的且不难的卷子.(我就是考前看了看这个链接,考试就是原题); 计算题只用关心一两步公式就能做出来的书上作业基础原题; 简答概念 ●典型面心结构有银铜铝汞 ●金刚石/ZnS是两个彼此错开的面心结构.砷化镓结构和其类似 ●本征半导体:完全不含杂质且无晶格缺陷的 ●把价带中空着的状态看成带正电的粒子空穴 ●导带上的电子与价带空穴参与导电 ●杂质影响半导体性质原因:破坏周期性势场,导致禁带产生能级,打破 了原有的Eg大小 ●电子共有化:能量相近的电子由于壳层交叠不再局限于单个原子 ●简并度:拥有相同能量的状态个数 ●肖特基缺陷特点:晶体体积增大晶格常数变化,克尔缺陷仅错位体积晶 格常数不变

● ●←计算必考 ●这种↓题型必考计算 ● ●(计算题必考,代入计算一步出答案)●;(简答必考) ●电流密度方程 ●[了解]负微分电导现象是由非等效能谷间的电子转移引起的;n型GaAs中的 强电场输运与硅不同,其漂移速度达到一最大值后,随着电场的进一步增加

反而会减小 ●[了解]碰撞离化:当半导体中的电场增加到某个阈值以上时,载流子将得到 足够的动能,可以通过雪崩过程(avalanche process)产生电子-空穴对 ●位于禁带中央附近的深能级是最有效的复合中心。 ●载流子从高能级向低能级跃迁,发生电子-空穴复合时,把多余的能 量传给另一个载流子,使这个载流子被激发到能量更高的能级上去,当它重新跃迁回低能级时,多余的能量常以声子形式放出,这种复合称为俄歇复合。 ●(深能级)积累非平衡载流子的作用称为陷阱效应,在费米能级附近 时,最有利于陷阱效应 ● (必考简答题,p改成n就是电子对应的方程) ●金半接触的能带弯曲图会画,并能理解;很重要 ●PN结中得势垒宽度高度: 势垒高度V D=kT μln?(N D n i ); 势垒宽度X D=√kT q (1 n A +1 n D )V D;

半导体材料复习资料 绪论 1.半导体的基本特性? ①电阻率大体在10-3~109Ω?范围 ②整流效应 ③负电阻温度系数 ④光电导效应 ⑤光生伏特效应 ⑥霍尔效应 2.为什么说有一天,硅微电子技术可能会走到尽头? ①功耗的问题 存储器工作靠的是成千上万的电子充放电实现记忆的,当芯 片集成度越来越高耗电量也会越来越大,如何解决散热的问 题? ②掺杂原子均匀性的问题 一个平方厘米有一亿到十亿个器件,掺杂原子只有几十个, 怎么保证在每一个期间的杂质原子的分布式一模一样的 呢?是硅微电子技术发展遇到的又一个难题 ③2层量子隧穿漏电的问题 随着器件尺寸的减小,绝缘介质2的厚度也在减小,当减小到 几个纳米的时候,及时很小的电压,也有可能使器件击穿或 漏电。量子隧穿漏电时硅微电子技术所遇到的另一个问题。 ④量子效应的问题 如果硅的尺寸达到几个纳米时,那么量子效应就不能忽略了,现有的集成电路的工作原理就可能不再适用 第一章 ⒈比较3氢还原法和硅烷法制备高纯硅的优缺点? ⑴三氯氢硅还原法 优点:产率大,质量高,成本低,是目前国内外制备高纯硅的主要方法。 缺点:基硼、基磷量较大。

⑵硅烷法 优点 ①除硼效果好;(硼以复盐形式留在液相中) ②无腐蚀,降低污染;(无卤素及卤化氢产生) ③无需还原剂,分解效率高; ④制备多晶硅金属杂质含量低(4的沸点低) 缺点:安全性问题 相图 写出合金Ⅳ由0经1-2-3的变化过程 第二章 ⒈什么是分凝现象?平衡分凝系数?有效分凝系数? 答:⑴分凝现象:含有杂质的晶态物质溶化后再结晶时,杂质在结晶的固体和未结晶的液体中浓度不同,这种现象较分凝现象。 ⑵平衡分凝系数:固液两相达到平衡时,固相中的杂质浓度和液相中的杂质浓度是不同的,把它们的比值称为平衡分凝系数,用K0表示。 K0

半导体物理2010-2011学年(2011.1.5) 一、简答题(8*6’=48’) 1.请填写下表中的数据: 解理面 材料晶格结构布拉伐格子直接/间接 带隙 Si GaAs 2.什么是本征半导体?什么是杂质半导体?示意画出掺杂浓度为Nd的N型半导体样品电子浓度n和本征载流子浓度ni随T变化曲线。 3.“纯净的半导体中,掺入百万分之一的杂质,可以减小电阻率达1百万倍,”是估算说明之。 4.一块杂志补偿的半导体,受主杂质和施主杂质浓度相等。设杂质全部电离,判断当杂质浓度分别为 (a) Na=Nd=1014cm-3(b) Na=Nd=1018cm-3 时,哪种情况的电导率大?简述分析理由。 5.什么是载流子的平均自由时间τ?有两块Si半导体材料1和2,其中τ1>τ2,迁移率哪个大? 如果同一块半导体中,有两种机理的平均自由时间τ1和τ2,其总迁移率如何确定? 6.写出以n型样品为例少子空穴的连续性方程。 由连续性方程写出:不考虑电场的作用、无产生、稳态载流子扩散方程; 7.什么是PN结的势垒电容?定性说明掺杂浓度对势垒电容有何影响。 8.一个p-N异质结接触前能带图见图1。画出平衡状态下能带图。

电阻率为7Ω·cm的p型硅,T=300K。 ⑴试计算室温时多数载流子和少子浓度(可查图)。 ⑵计算该半导体的功函数。 ⑶不考虑界面态,在金属铝(功函数W Al=4.20eV)和金属铂(功函数W Pi=5.3eV)中选择制备肖特基二极管的金属,给出选择理由。 ⑷求金属一侧势垒高度的理论值qΦms和半导体一侧势垒高度qV D 。 三、(16’) 室温下,一个Si的N-P结,N区一侧掺杂浓度为1017cm-3,P区为1015cm-3 ⑴求该N-P结的接触电势差。 ⑵画出平衡PN结、正向偏置PN结、反向偏置PN结空间电荷区中及边界处的载流子分布示意图。 ⑶根据正向和反向少子分布情况,解释PN结正向导通,反向截止的饱和特性。 ⑷写出理想PN结电流-电压关系公式,在对数坐标下,定性画出理想和实际I-V特性示意图。 四、(15’) 一理想的MOS结构的高频测量的C-V曲线如图2. (1)判断该结构中,半导体的导电类型。 (2)说明图中1,2,3,4,5点的半导体一侧的状态,并示意画出每点半导体一侧的能带形状,以及金属和半导体一侧的电荷分布。