altera常用扩展名介绍(自创)

- 格式:doc

- 大小:1.19 MB

- 文档页数:35

Quartus®II简介®Altera Corporation101 Innovation DriveSan Jose, CA 95134 USA(408) 544-7000Quartus II 简介3.0 版第 1 次修订2003 年 6 月P25-09235-00Altera、Altera 徽标、FastTrack、MAX、MAX+PLUS、MAX+PLUS II、MegaCore、MegaWizard、NativeLink、Nios、OpenCore、Quartus、Quartus II、Quartus II 徽标和 SignalTap 是 Altera Corporation 在美国和其它国家(或地区)的注册商标。

ByteBlaster、ByteBlasterMV、Excalibur、HardCopy、IP MegaStore、Jam、LogicLock、MasterBlaster、MegaLAB、PowerFit 和 SignalProbe 是 Altera Corporation 在美国和其它国家(或地区)的商标和/或服务标志。

Altera Corporation 使用的产品设计元素和助记键受版权法和/或商标法的保护。

Altera Corporation 承认本文档提及的其它组织的产品或服务商标和/或服务标志,特别是:Mentor Graphics 和 ModelSim 是 Mentor Graphics Corporation 的注册商标,ModelTechnology 是 Mentor Graphics Corporation 的商标。

Altera 保留更改本文档中所述设备或设备规范的权利,恕不另行通知。

Altera 建议客户在下订单之前要取得设备规范的最新版本,以确认客户所依赖的信息是最新的。

Altera 保证自己的半导体产品的性能与 Altera 的标准担保一致,符合当前规范。

Altera(现在是英特尔(Intel)的 Quartus Prime)工程文件通常包括多个文件,如

项目文件(.qpf)、映射文件(.qsf)、原理图文件、VHDL/Verilog 文件等。

这些

文件之间的相对路径通常是相对于项目文件所在的目录而言的。

以下是一些常见的 Altera 文件及其相对路径的例子:

1.项目文件(.qpf):

▪位于项目根目录下,通常包括工程的设置信息,例如项目名称、文件列表等。

▪相对路径:./project.qpf

2.映射文件(.qsf):

▪位于项目根目录下,包含了关于逻辑映射的详细信息。

▪相对路径:./project.qsf

3.VHDL/Verilog 文件:

▪位于项目文件夹的子目录中,例如src或hdl。

▪相对路径:./src/my_module.vhd或./hdl/my_module.v

4.约束文件(.sdc):

▪通常位于项目文件夹的子目录,例如constraints。

▪相对路径:./constraints/my_constraints.sdc

在使用相对路径时,确保路径是相对于项目文件(.qpf 文件)所在的目录的。

这有

助于确保项目文件能够正确引用其他文件,避免路径错误导致文件无法找到的问题。

注意:如果使用相对路径,要确保在文件的相对路径中不使用不同平台上的目录分隔符。

在大多数系统中,使用斜杠/作为目录分隔符是通用的做法。

Altera公司是一家知名的半导体公司,致力于生产和销售可编程逻辑器件(PLD)和现场可编程门阵列(FPGA)等产品。

下面将列举Altera公司旗下的CPLD和FPGA产品,帮助大家更好地了解这家公司的产品线。

一、CPLD产品线1. MAX 7000系列MAX 7000系列是Altera公司推出的一款CPLD产品,具有低功耗、高性能和可编程性强的特点。

该系列产品广泛应用于通信、工业控制、汽车电子等领域,为客户提供了稳定可靠的解决方案。

2. MAX 9000系列MAX 9000系列是Altera公司的另一款CPLD产品,采用了先进的CMOS工艺和可编程逻辑单元,具有高密度、可靠性高的特点。

该系列产品在航空航天、国防安全、医疗设备等领域有着广泛的应用。

二、FPGA产品线1. Stratix系列Stratix系列是Altera公司旗下最为知名的FPGA产品之一,拥有高速、高密度、低功耗等特点,适用于需要大规模数据处理和高性能计算的应用场景。

该系列产品常用于人工智能、云计算、数据中心等领域。

2. Cyclone系列Cyclone系列是Altera公司针对中小规模应用市场推出的FPGA产品,具有低成本、低功耗、高性能等特点。

该系列产品在嵌入式系统、工业自动化、网络通信等领域有着广泛的应用。

3. Arria系列Arria系列是Altera公司旗下的高性能FPGA产品,具有高速、低功耗、灵活性强等特点,适用于需要高性能和灵活性的应用场景。

该系列产品在无线通信、高性能计算、高清视频等领域有着广泛的应用。

通过以上列举,我们可以看到Altera公司在CPLD和FPGA领域拥有丰富的产品线,为不同领域的客户提供了多样化的解决方案。

期待Altera在未来能够持续推出更多高性能、低功耗的PLD和FPGA产品,满足客户不断增长的需求。

Altera公司作为半导体行业的领军企业,一直以来致力于为全球各行业提供高性能、低功耗的可编程逻辑器件(PLD)和现场可编程门阵列(FPGA)产品。

目录1概述 6 2基于块的设计方法 6 3STRATIX系列器件介绍7 3.1STRATIX系列器件所具有的新特性:7 3.2STRATIX系列器件内部结构7 3.3内部连线8 3.4内部存储单元8 3.5内置DSP单元10 3.6I/O接口12 3.7时钟系统12 3.8远程升级功能13 3.9其他13 4STRATIX器件家族及封装13表目录表1 STRATIX内部存储单元特性9 表2 STRATIX器件内部存储单元容量及最大带宽9 表3 STRATIX系列器件乘法器列表12 表4 STRATIX系列器件I/O端口支持标准12 表5 STRATIX器件家族14 表6 STRATIX系列器件封装14图目录图1可编程逻辑设计方法演进趋势 6图2基于STRATIX系列器件的设计流程7图3 STRATIX系列器件内部结构8图4 STRATIX系列器件内部存储单元9图5 DSP单元内部结构10图6 DSP单元实现四组2输入乘法器10图7 DSP单元实现两组2输入乘法累加器11图8 DSP单元实现两组4输入乘加器11图9 DSP单元实现一组8输入乘加器11ALTERA公司STRATIX系列可编程逻辑器件技术交流报告关键词: ALTERA,STRATIX,可编程逻辑,器件摘要:本文主要对ALTERA公司STRATIX系列器件及其Block-Based的设计方法进行了简要介绍。

缩略语清单:PLL:Phase Locked Loop 锁相环MegaRAM:STRATIX器件容量为512K的内部存储单元1概述STRATIX系列可编程逻辑器件是ALTEREA公司即将于年内推出的一款高性能可编程逻辑器件。

该系列器件采用1.5V,0.13um工艺,可同时提供最多114,140个LE和10MbitsRAM空间。

STRATIX系列器件可提供包含多达224个9bit*9bit内置乘法器的28个DSP功能块,其经过优化的结构可以有效实现高性能滤波器和乘法器。

Altera FPGA/CPLD 学习笔记Xilinx,Altera,Lattice是可编程器件的主要三个生产厂家。

最近领导安排叫我学习Altera的FPGA,以前主要接触的Xilinx的东西多一些。

所以一上手感觉生疏,特别是QuartusII软件。

QuartusII是Altera公司新一代的FPGA/CPLD开发环境。

前一代Max+plusII开发环境Altera公司已经不再提供新的版本。

所以今后学习还是应用尽可能使用QuartusII。

以前Max+plusII的工程文件也可以导入QuartusII中。

熟悉MaxplusII的也可以将QuartusII的界面转换成MaxplusII。

一.基础知识1. FPGA/CPLD的区别与联系表1-12.逻辑电路概念① 组合逻辑电路的输出信号只与该时刻的输入信号有关,而与电路原来所处的状态无关。

② 时序逻辑任何一个时刻的输出状态不仅取决于当时的输入信号,还与电路的原状态有关。

时序电路的特点是具有记忆元件(最常见的是触发器),具有反馈通道。

包括各类触发器、寄存器、各类计数器和顺序脉冲发生器,各类存储器。

二. Quartus II安装破解这里以Quartus II5.1为例。

QuartusII对PC机硬件要求较高,尽可能采用高配置的PC机。

安装一路next就可以了。

主要是破解,一般的配套光盘都有license文件,但需要自己修改HOSTID,也就是你的网卡的物理地址,介绍一下流程。

1.安装完毕QuartusII后,将sys_cpy.dll文件复制copy到C:\altera\quartus50\bin,将原来的文件覆盖。

2.在C盘新建文件夹flexlm,将光盘中的license.dat拷贝到c:\flexlm中。

同时将只读属性去掉。

3.打开“开始”->运行输入cmd 进入dos模式。

然后输入ipconfig/all 然后记下physical address,也就是hostid。

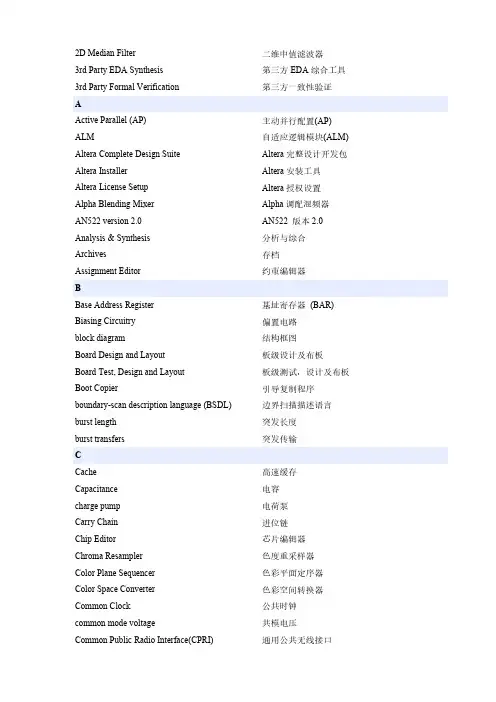

author: liu xiao ping date: 2007.01.8各扩展名的顺序没安排好,以后有时间再改正欢迎补充与改正,可联系qq:53579621参考quartus helpQuartus II是一款功能强大的EDA软件。

在这个集成开发环境中,PLD使用者可以完成编辑、编译、仿真、综合、布局布线、时序分析、生成编程文件、编程等全套PLD开发流程。

Quartus II以工程(Project)为单位管理文件。

保证了设计文件的独立性和完整性。

由于Quartus II功能众多,每一项功能都对应一个甚至多个文件类型。

在使用中,如果需要转移或备份某一工程对应的文件,对众多文件的取舍成了一个令人头痛的问题。

类似问题,在使用Maxplus II的过程中也很常见。

使用Quartus II自带的工程文件压缩功能可以省去取舍文件的麻烦。

但是.qar文件把众多文件压缩成一个文件,只有解压缩才能获取具体文件的信息。

如果使用版本控制工具(如CVS)的话,对.qar 文件无法进行版本比较。

甚至当.qar文件受损时,部分甚至全部文件都无法恢复了。

而且,缺省配置的.qar文件也包含了一些非关键文件,存在一定的冗余。

解决这一问题的关键在于弄清文件扩展名的意义,明明白白地控制文件的取舍。

The following file types are available for use in the Quartus II software:上面这些文件可以分为五类:1. 编译必需的文件:设计文件(.gdf、.bdf、EDIF输入文件、.tdf、verilog设计文件、.vqm、.vt、VHDL设计文件、.vht)、存储器初始化文件(.mif、.rif、.hex)、配置文件(.qsf、.tcl)、工程文件(.qpf)。

2. 编译过程中生成的中间文件(.eqn文件和db目录下的所有文件)3. 编译结束后生成的报告文件(.rpt、.qsmg等)4. 根据个人使用习惯生成的界面配置文件(.qws等)5. 编程文件(.sof、.pof、.ttf等)1).vqm V erilog Quartus Mapping FileSynplicity Synplify 软件或Quartus II 软件生成的Verilog HDL 格式网表文件。

一.SDRAM工作原理和控制方法在基于FPGA的图象处理系统中,常常需要用到大容量、高速度的存储器。

而在各种随机存储器件中,SDRAM的价格低、体积小、速度快、容量大,是比较理想的器件。

但SDRAM的控制逻辑比较复杂,对时序要求也十分严格,使用很不方便,这就要求有一个专门的控制器,使系统用户能很方便地操作SDRAM。

l SDRAM简介SDRAM器件的管脚分为控制信号、地址和数据三类。

通常一个SDRAM中包含几个BANK,每个BANK的存储单元是按行和列寻址的。

由于这种特殊的存储结构,SDRAM有以下几个工作特性。

● SDRAM的初始化--- SDRAM在上电100~200μs后,必须由一个初始化进程来配置SDRAM的模式寄存器,模式寄存器的值决定着SDRAM的工作模式。

●访问存储单元--- 为减少I/O引脚数量,SDRAM复用地址线,所以在读写SDRAM时,先由ACTIVE 命令激活要读写的BANK,并锁存行地址,然后在读写指令有效时锁存列地址。

一旦BANK被激活后只有执行一次预充命令后才能再次激活同一BANK。

●刷新和预充--- SDRAM的存储单元可以理解为一个电容,总是倾向于放电,因此必须有定时的刷新周期以避免数据丢失。

刷新周期可由(最小刷新周期÷时钟周期)计算获得。

对BANK预充电或者关闭已激活的BANK,可预充特定BANK也可同时作用于所有BANK,A10、BA0和BA1用于选择BANK。

●操作控制--- SDRAM的具体控制命令由一些专用控制引脚和地址线辅助完成。

CS、RAS、CAS 和WR在时钟上升沿的状态决定具体操作动作,地址线和BANK选择控制线在部分操作动作中作为辅助参数输入。

由于特殊的存储结构,SDRAM操作指令比较多,不像SRAM一样只有简单的读写。

二.SDRAM 控制器的设计实现 2.1 SDRAM 控制器的设计实现 ● 总体设计框图和外部接口信号SDRAM 控制器与外部的接口示意图由上图给出,控制器右端接口信号均为直接与SDRAM 对应管脚相连的信号,此处不做介绍。

Quartus II工程文件的后缀含义上面这些文件可以分为五类:1. 编译必需的文件:设计文件(.gdf、.bdf、EDIF输入文件、.tdf、verilog设计文件、.vqm、.vt、VHDL设计文件、. vht)、存储器初始化文件(.mif、.rif、.he x)、配置文件(.qsf、.tcl)、工程文件(.qpf)。

2. 编译过程中生成的中间文件(.eqn文件和db目录下的所有文件)3. 编译结束后生成的报告文件(.rpt、.qsmg等)4. 根据个人使用习惯生成的界面配置文件(.qws等)5. 编程文件(.sof、.pof、.ttf等)上面分类中的第一类文件是一定要保留的;第二类文件在编译过程中会根据第一类文件生成,不需要保留;第三类文件会根据第一类文件的改变而变化,反映了编译后的结果,可以视需要保留;第四类文件保存了个人使用偏好,也可以视需要保留;第五类文件是编译的结果,一定要保留。

在使用版本控制工具时,我通常保留第一类、第三类和第五类文件。

但是第三类文件通常很少被反复使用。

所以,为了维护一个最小工程,第一类和第五类文件是一定要保留的。

此外,当一个项目的设置内容需要转移给另一个项目时,例如引脚分配信息,需要转移.tcl文件而不是.qsf文件。

.tcl文件与.qsf文件的关系以及如何生成.tcl文件我会在以后的日志中给出。

CyClone III C25 原版资料下载关于CPLD/FPGA一些问题1、PLD,CPLD,FPGA有何不同?答:不同厂家的叫法不尽相同,PLD是可编程逻辑器件的总称,早期多EEPROM工艺,基于乘积项结构。

FPGA是指现场可编程门阵列,最早由Xilinx公司发明。

多为SRAM工艺,基于查找表结构,要外挂配置用的EPROM。

Xilinx把SRAM工艺,要外挂配置用的EPROM的PLD叫FPGA,把Flash工艺、乘积项结构的PLD叫CPLD;Altera把自己的PLD产品:MAX系列,FLEX/ACEX/ APEX系列都叫作CPLD,即复杂PLD,由于FLEX/ACEX/APEX系列也是SRA M工艺,要外挂配置用的EPROM,用法和Xilinx的FPGA一样,所以很多人把Altera的FELX/ACEX/APEX系列产品也叫做FPGA.2、NiosII嵌入式处理器是一个什么样的处理器?与其他相比具有哪些功能? 答:1)Nios II嵌入式处理器是一个用户可配置的通用RISC嵌入式处理器。

author: liu xiao ping date: 2007.01.8各扩展名的顺序没安排好,以后有时间再改正欢迎补充与改正,可联系qq:53579621参考quartus helpQuartus II是一款功能强大的EDA软件。

在这个集成开发环境中,PLD使用者可以完成编辑、编译、仿真、综合、布局布线、时序分析、生成编程文件、编程等全套PLD开发流程。

Quartus II以工程(Project)为单位管理文件。

保证了设计文件的独立性和完整性。

由于Quartus II功能众多,每一项功能都对应一个甚至多个文件类型。

在使用中,如果需要转移或备份某一工程对应的文件,对众多文件的取舍成了一个令人头痛的问题。

类似问题,在使用Maxplus II的过程中也很常见。

使用Quartus II自带的工程文件压缩功能可以省去取舍文件的麻烦。

但是.qar文件把众多文件压缩成一个文件,只有解压缩才能获取具体文件的信息。

如果使用版本控制工具(如CVS)的话,对.qar 文件无法进行版本比较。

甚至当.qar文件受损时,部分甚至全部文件都无法恢复了。

而且,缺省配置的.qar文件也包含了一些非关键文件,存在一定的冗余。

解决这一问题的关键在于弄清文件扩展名的意义,明明白白地控制文件的取舍。

The following file types are available for use in the Quartus II software:上面这些文件可以分为五类:1. 编译必需的文件:设计文件(.gdf、.bdf、EDIF输入文件、.tdf、verilog设计文件、.vqm、.vt、VHDL设计文件、.vht)、存储器初始化文件(.mif、.rif、.hex)、配置文件(.qsf、.tcl)、工程文件(.qpf)。

2. 编译过程中生成的中间文件(.eqn文件和db目录下的所有文件)3. 编译结束后生成的报告文件(.rpt、.qsmg等)4. 根据个人使用习惯生成的界面配置文件(.qws等)5. 编程文件(.sof、.pof、.ttf等)1).vqm V erilog Quartus Mapping FileSynplicity Synplify 软件或Quartus II 软件生成的Verilog HDL 格式网表文件。

*.vqm 主要应该是用来做布局布线用A VQM File is an atom-based V erilog HDL netlist file that defines all logic for a Synplify design or for a particular top-level design entity when used as a part of an incremental compilation, using a subset of V erilog HDL constructs在quartus中产生 vqm file有三种方法the VQM File is placed in the <project directory>\atom_netlists\ directory∙Turn on Save a node-level netlist in the Compilation Process S ettings page in the S ettings dialog box, and then compile the design.∙Turn on Save a node-level netlist in the Back-Annotate Assignments dialog box and back-annotate a design.∙Click Start VQM W riter.联系与区别.vhm 和 .vm 分别为 VHDL 和verilog 源码被synplify综合后为了做综合后仿真所生成的文件;vqm是synplify等软件为quartus 所生成的网表文件,synplify会根据不同的器件生成不同后缀的网表文件的,举例:对于apex生成.vqm文件,对于vertex会生成.edf网表vqm(synplify输出)和vo(Quartus II输出)都是Verilog的网表,两者内容比较相似,*.vo比*.vqm 更具体一点。

但是区别比较大。

vqm只能由于在Quartus II中Fit,不能用于仿真。

vo是Quaruts II在synthesis或者fit以后产生的门级仿真模型,可以用于ModelSim仿真。

vo可以和sdo(延时文件)一起做时序仿真2).vo verilog output files由Quartus II Compiler 产生,主要用于专业仿真工具如modelsim等进行综合后仿真的网表文件。

不能被quartus II compiler 编译The V erilog Output File contains properties of all entities within the top-level project.类似有.vho文件vhdl output filesA Very High Speed Integrated Circuit (VHSIC) Hardware Description Language (VHDL) standard netlist file (with the extension .vho) that is generated by the Quartus II Compiler.The VHDL Output File is a VHDL version 1987 standard netlist file that can be imported into an industry-standard VHDL simulation or timing analysis tool. A VHDL Output File cannot be compiled with the Quartus II Compiler3).edif EDIF Input File 用于布局布线An EDIF version 2 0 0 netlist file (with the extension (.edf), generated by any standard EDIF netlist writer. The Quartus II software also supports EDIF Input files with the extensions (.edif) or (.edn).When you compile an EDIF Input File, the Compiler uses one or more Library Mapping Files (.lmf) to map cells in an EDIF Input File to corresponding Quartus II logic functions, including Library of Parameterized Modules (LPM) functions, as well as to user-defined functions.4).inc AHDL Include FileAhdl语言的头文件An ASCII text file (with the extension .inc) that can be imported into a Text Design File (.tdf) by an AHDL Include Statement. The AHDL Include File replaces the Include Statement that calls it. INC Files can contain Function Prototype, Define, Parameters, or Constant Statements.一般咱们接触到的地方就是在用MegaWizard Plug-In Manager时宏功能模块封装文件中模块的AHDL Include 文件5).sdo Standard Delay Format Output File主要用于modelsim仿真,sdo可以和 vo一起做时序仿真SDF Output Files are automatically generated when you compile a design.Y ou can also generate an SDF Output File by using the Start > Start EDA Netlist Writer command (Processing menu). SDF Output Files contain timing delay information that allow you to perform back-annotation for simulation with VHDL simulators that use simulation libraries that are compliant with VITAL version 2.2b and version 3.0 (VITAL 95); back-annotation for simulation in V erilog HDL simulators; and timing analysis and physical synthesis with EDIF simulation and synthesis tools.6).tcl Tcl Script File可以采用多种方法在Quartus II 软件中使用Tcl 脚本。

可以使用针对Tcl 的 Quartus II API 命令建立Tcl 脚本。

应将Tcl 脚本另存为Tcl Script File(.tcl)。

A Tcl Script File contains a single Tcl script, which is composed of Tcl commands and Quartus II Application Programming Interface (API) functions used as commands. Y ou can use the Quartus II Text Editor to create and edit Tcl Script Files.如:7).bsf Block Symbol FileBlock Editor 中使用的宏功能模块符号A symbol file (with the extension .bsf) created with the Quartus II Symbol Editor. Y ou can read and edit a symbol, which represents a macrofunction, primitive, megafunction, or design file, in a BSF, and add the symbol to a Block Design File (.bdf) with the Symbol Editor8).bdf Block Design File使用Quartus II Block Editor 建立的原理图设计文件A schematic design file (with the extension .bdf) created with the Quartus II Block Editor. BDFs may contain block diagrams, symbols, and schematics that represent logic in a design. Y ou can read and edit BDFs in the Block Editor.9).qpf Quartus II Project File指定用来建立工程和与工程相关修订的Quartus II 软件版本。