Developing a PWM Interface using LabVIEW FPGA

- 格式:pdf

- 大小:111.77 KB

- 文档页数:5

用C 语言和M A TLAB 构造PWM 控制仿真模型的一种方法华中理工大学 董玮 秦忆 摘要:文章介绍了一种将C 语言与M A TLAB 结合起来进行构造PWM 仿真模型的方法,这种方法不用编程,简单直观,使用方便,易于模块化。

关键词:PWM 控制 M A TLAB S I M UL I N KA Si m ula tion M ethod to P WM Con trol with C and M AT LABDong W ei Q in Y iAbstract :A m ethod to construct PWM si m ulati on model w ith C and M A TLAB has been introduced in the paper .T he m ethod is si m p le and intuiti onal w ithout any p rogram .It is convenient to use and m ake modulariza 2ti on .Keywords :PWM contro l M A TLAB S I M UL I N K1 前言PWM 控制是通过对每周期内输出脉冲个数和每个脉冲宽度的控制来改善逆变器的输出电压、电流波形[1]。

它是现代交流变频调速的一种重要的控制方式。

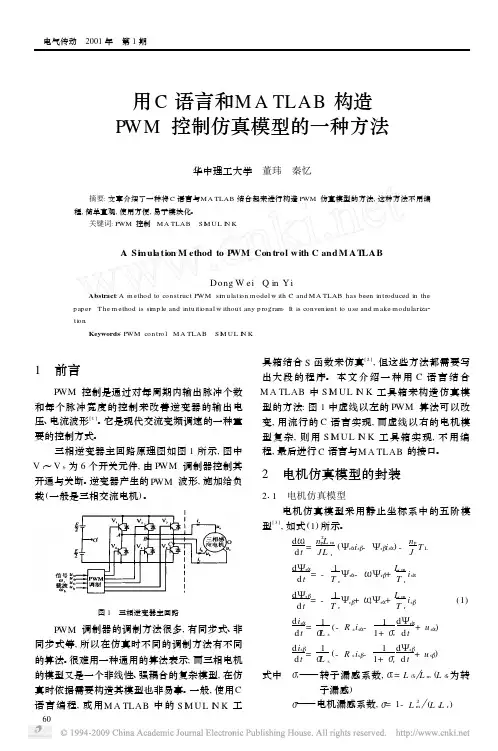

三相逆变器主回路原理图如图1所示,图中V 1~V 6为6个开关元件,由PWM 调制器控制其开通与关断。

逆变器产生的PWM 波形,施加给负载(一般是三相交流电机)。

图1 三相逆变器主回路PWM 调制器的调制方法很多,有同步式、非同步式等,所以在仿真时不同的调制方法有不同的算法。

很难用一种通用的算法表示;而三相电机的模型又是一个非线性、强耦合的复杂模型,在仿真时依据需要构造其模型也非易事。

一般,使用C 语言编程,或用M A TLAB 中的S I M UL I N K 工具箱结合S 函数来仿真[2],但这些方法都需要写出大段的程序。

华为突破技术封锁自主研发芯片英语作文Huawei Breaks Through Technology Blockade withSelf-developed ChipsWith the advancement of technology and the increasing competition in the global market, the issue of technological blockade has become more prominent. In recent years, Huawei, a leading global provider of information and communications technology (ICT) infrastructure and smart devices, has continuously faced technological challenges and restrictions. However, Huawei has successfully broken through the technology blockade by developing its own chips.In the face of the technology blockade, Huawei has invested heavily in research and development to develop its own chips. The company has established a strong research and development team comprised of experts in various fields, including chip design, semiconductor technology, and artificial intelligence. Through their collaborative efforts, Huawei has successfully developed a series of cutting-edge chips that have not only improved the performance of its products but also reduced its dependence on foreign suppliers.One of the key achievements of Huawei in breaking through the technology blockade is the development of its Kirin series of chips. The Kirin chips are designed to provide superior performance, energy efficiency, and security for Huawei's smartphones, tablets, and other devices. By using its own chips, Huawei has been able to optimize the performance of its devices and deliver a better user experience to its customers.In addition to the Kirin chips, Huawei has also developed its own Kunpeng and Ascend series of chips for its server and artificial intelligence products. The Kunpeng chips are designed to provide high-performance computing capabilities for Huawei's server products, while the Ascend chips are designed to provide advanced AI processing capabilities for Huawei's AI products. By developing its own chips, Huawei has been able to expand its product offerings and compete more effectively in the global market.Overall, Huawei's success in breaking through the technology blockade with its self-developed chips is a testament to the company's innovation and determination. By investing in research and development and fostering a culture of continuous improvement, Huawei has been able to overcome the technological challenges it faces and emerge as a global leaderin the ICT industry. As Huawei continues to develop new technologies and products, it is poised to further strengthen its position in the global market and drive innovation in the ICT industry.。

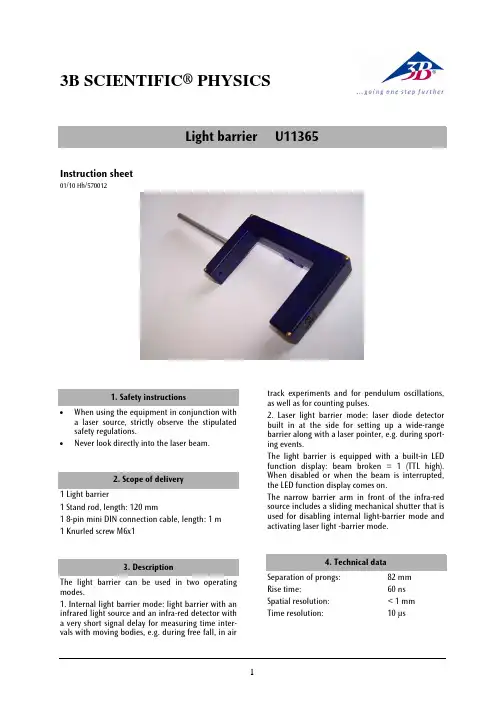

3B SCIENTIFIC ®PHYSICS1Light barrier U11365Instruction sheet01/10 Hh/5700121. Safety instructions•When using the equipment in conjunction with a laser source, strictly observe the stipulated safety regulations.•Never look directly into the laser beam.2. Scope of delivery1 Light barrier1 Stand rod, length: 120 mm1 8-pin mini DIN connection cable, length: 1 m 1 Knurled screw M6x13. DescriptionThe light barrier can be used in two operating modes.1. Internal light barrier mode: light barrier with an infrared light source and an infra-red detector with a very short signal delay for measuring time inter-vals with moving bodies, e.g. during free fall, in airtrack experiments and for pendulum oscillations, as well as for counting pulses.2. Laser light barrier mode: laser diode detector built in at the side for setting up a wide-range barrier along with a laser pointer, e.g. during sport-ing events.The light barrier is equipped with a built-in LED function display: beam broken = 1 (TTL high). When disabled or when the beam is interrupted, the LED function display comes on.The narrow barrier arm in front of the infra-red source includes a sliding mechanical shutter that is used for disabling internal light-barrier mode and activating laser light -barrier mode.4. Technical dataSeparation of prongs: 82 mm Rise time: 60 ns Spatial resolution: < 1 mm Time resolution:10 µs3B Scientific GmbH • Rudorffweg 8 • 21031 Hamburg • Germany • Subject to technical amendments© Copyright 2010 3B Scientific GmbH5. Operation•Screw onto the stand rod using the arm at-tached to the thinner of the two prongs of the barrier and the M6 nut provided for this pur-pose.•Insert the mini DIN cable into the mini DIN connector on the broader prong of the barrier and connect it to the 3B NET log TM interface U11300 or to digital counter U210051.•Activate internal light barrier mode by opening the mechanical shutter. Subsequently, mount and focus the device for the intended applica-tion.•Activate laser light barrier mode by closing the mechanical shutter and (roughly) focus the la-ser light source onto the opening at the side of the light barrier. To achieve this, mirrors may be used to deflect the laser beam. Make fine adjustments to the light barrier.6. ApplicationsDetermining the position, velocity and acceleration of moving bodiesDetermining the acceleration due to gravity g in free fall experimentsMeasuring periods of oscillating bodies7. Sample experimentDetermining acceleration due to gravity g using picket fence U11366 Required apparatus:1 3B NET log TMU11300 1 Light barrier U11365 1 Picket fence U11366 1 Stand base U13270 1 Steel rod, length: 750 mm U15003 1 Universal clamp U13255 (1 Foam rubber sheet, approx. 20 x 20 cm)• Use the stand apparatus to fix the light barrierat a suitable height above ground level or at the edge of a table. If necessary, place a cush-ioning surface (e.g. foam rubber sheet) along the point of impact.• Select the digital input of the 3B NET log TMinter-face and load the free-fall experiment (tem-plate) from the 3B NET labTM software. All thenecessary settings required for evaluation are provided by this software.•Conduct the experiment and analyse yourresults.Fig. 1: Measuring free fallFig. 2: Distance against timeFig. 3: Fall velocity against time。

Evaluates: MAX20754 and MAX20790MAX20754EVKIT8Evaluation KitOne Analog Way, Wilmington, MA 01887 U.S.A. | Tel: 781.329.4700 | © 2021 Analog Devices, Inc. All rights reserved.© 2021 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners.Click here to ask an associate for production status of specific part numbers.General DescriptionThis MAX20754EVKIT8 evaluation kit (EV kit) demon-strates the MAX20754 PMBus™-compatible dual-output multiphase power-supply controller. The controller gener-ates six pulse-width modulated (PWM) control signals, or “phases.” The MAX20754EVKIT8 EV kit is a single-output design, with all six phases assigned to one output. The output uses coupled inductor topologies. Coupled induc-tors reduce the effective inductor value and size without excessive ripple current, reducing required output capaci-tance, and improving transient response.The EV kit also demonstrates the MAX20790 power-stage device; there are six MAX20790 devices, one per phase.Features●Optimized for Single +10V to +16V Supply• Onboard +3.3V Regulator (MAX17501) ●Generates One Output• Output: 6-Phase, 1V, 225A ●500kHz Switching Frequency ●Enable Switch●PMBus Configuration and Control• Compatible with Maxim’s PowerTool™ GUI • Easy Connection to PC Using MAXPOW-ERTOOL002 USB-to-SMBus Interface (order separately) ●Status LEDs• Power-Good• Power-Stage Fault • SMBus Alert ●Proven PCB Layout●Compensation Scheme Optimized for HighBandwidth ●Fully Tested and Assembled319-100863; Rev 0; 12/21Ordering Information appears at end of data sheet.PMBus is a trademark of SMIF , Inc.PowerTool is a trademark of Maxim Integrated Products, Inc.MAX20754EVKIT8 BoardEvaluation KitQuick StartRequired Equipment●12V DC power supply capable of delivering 300W atthe desired input voltage●Windows PC with a spare USB port●MAXPOWERTOOL002 USB-to-SMBus Interface(order separately)●Maxim Digital PowerTool GUI softwareOptional Equipment●AC/DC “wall adapter” for convenient low-power eval-uation, connecting to J5 on the EV kit. For example:• CUI p/n ETSA120500UC-P5P-SZ (12V, 5A, 60Wmax)• CUI p/n EMSA120300-P5P-SZ (12V, 3A, 40W max)●300MHz four-channel oscilloscope●BNC-to-SMB cables for convenient, low-noise oscil-loscope connection to the input and output voltagesense points. For example: CD International Tech-nology p/n BSB-174TPR-3.●Electronic load capable of sinking 240A at 1V• Ask about the Maxim MINILOAD device●Digital multimeter (DMM)ProcedureNote: In the following sections, text in bold refers to items directly from the EV kit software.The EV kit is fully assembled and tested. Follow the steps below to verify board operation.Caution: Do not turn on the power supply until all connections are completed.1) Visit the Maxim Integrated website to download andinstall the latest version of the Digital PowerToolsoftware.2) Connect the USB cable from the PC to the MAX-POWERTOOL002 interface adapter.3) Connect the adapter ribbon cable to the matchingheader J13 on the EV kit, ensuring that J13-Pin 1 isadjacent to the red wire on the ribbon cable.4) Connect the DC power supply positive lead to J6 andthe negative lead to J7 (or use an AC-DC adapterthrough J5 using a center-positive 2.1mm I.D. x5.5mm O.D. plug).5) If available, connect the electronic load(s) to theoutputs at screw terminals ST1, ST2, ST3, and ST4, being careful to observe the VOUT and GND polarity indicated by the silkscreen labels.6) If available, connect the oscilloscope to the EV kit forwaveform analysis. Coaxial SMB cable connections J8, and J9 allow low-noise measurement of the input and output ripple waveforms. (Note that the inputvoltage signal at J8 is resistively attenuated 20:1 toprotect oscilloscope inputs.)7) Ensure that jumpers JP1 and JP2 have shuntsinstalled.8) Enable the external 12V supply.9) Enable the onboard MAX17501 12V-to-3.3V sup-ply circuit with switch S5. This supplies 3.3V to theMAX20754, which in turn generates 1.8V power forthe MAX20790 power-stage devices.10) Start the GUI software. The “Dashboard” windowshould appear as shown in Figure 1.11) Enable the MAX20754 output by operating switch S2on the EV kit, or by setting the OPERATION and ON_ OFF_CONFIG commands in the PowerT ool GUI.Evaluation KitDetailed Description of SoftwareThe PowerT ool software presents system-level information on the Dashboard tab. This view collects basic information for all Maxim PMBus devices found on the bus. This tab configures sequencing and output voltage levels and pres-ents an overview of the system status. Clicking the Stop Communication button stops all PMBus transactions from the PowerT ool GUI. T o force detection of all active devices on the bus, click the Search for Devices button.For detailed information on a particular device, click on the sub-tab for that device’s slave address. This opens a view with a set of further sub-tabs specific to that device as shown in Figure 2. The sub-tabs available vary depending on the GUI version and the connected device’s capability, but typically include Configuration, Monitor, Faults Set, and PMBus Command.The Configuration tab presents the most commonly used PMBus command data in human-readable form. The device status is updated by continuous polling of these commands. Configuration settings for an individual device can be saved to or restored from an external file. The PMBus command settings can be saved to or restored from the device’s internal nonvolatile memory as well.The Monitor tab shows continuously updated telemetry data from the device. Rolling plots of output voltage, input voltage, output current, and temperature data are shown, including indication of fault limits relative to the operating point.Figure 1. Maxim PowerTool Graphical User Interface Software Dashboard WindowEvaluation KitThe Faults Set tab allows the user to configure andmonitor the status of most protection and warning func-tions. The fault levels and fault response commands areconfigured from this tab. The full contents of the STATUS_register commands are available by clicking the ViewFault/Warning bit by bit button. Fault and warning flags are cleared by clicking the Clear Fault/Warning button,which sends the CLEAR_FAULTS PMBus command tothe device.The PMBus Command tab shows all supported PMBus commands in a series of sub-tabs, allowing detailed con-figuration and analysis of the command values. The user can view the command values in a hexadecimal or deci-mal format by checking or clearing the Force Hex check-box. The Use PEC checkbox enables or disables Packet Error Checking for all GUI communications. Note that the command data is continuously updated by polling; typing a new value into the text boxes causes the new value to be sent to the device.Figure 2. Detailed View for One Device; Configuration Sub-TabEvaluation KitDetailed Description of HardwareThe MAX20754EVKIT8 demonstrates a single-output step-down power supply solution, with one six-phase output, which makes use of the coupled inductors. This solution provides high output-current with high efficiency, fast load-transient response, and low ripple and noise.The MAX20754 controller automatically interleaves all PWM outputs assigned to a given output at even inter-vals. The output is six-phase resulting in 60° timing. Each PWM signal is connected to one MAX20790 power-stage device, operating in parallel configuration. This configura -tion is capable of supplying up to 37.5A per phase. Each power-stage is in turn connected to one winding of a coupled inductor.The MAX20754 controller evenly shares the load current between phases in a given output. The EV kit is con-figured to operate both outputs at 500kHz fundamental switching frequency, but can be modified to operate anywhere from 300kHz to 800kHz with appropriate com -pensation network changes. The output is set to supply 1V. The maximum output current for the output is 225A.The output voltage, output rise-time and fall-time, switch -ing frequency, PMBus address, slope compensation, and maximum output current are set using only five external resistors, allowing simple setup and application configura -tion that does not require PMBus commands. Refer to the MAX20754 and MAX20790 integrated circuit data sheets for complete details on design and component selection.Table 1. Jumper JP1Table 2. Jumper JP2Table 3. Connector ListSHUNT POSITIONDESCRIPTIONInstalled MAX17501 +3.3V output connected to MAX20754 V DD3P3 input.Not installedMAX20754 can be powered by an external +3.3V supply at TP35.SHUNT POSITIONDESCRIPTIONInstalled MAX17501 +3.3V output connected to AUX3P3 rail (ENx debounce and status LED logic, etc.).Not installedThe AUX3P3 rail can be powered by an external +3.3V supply at Pin 2 of JP2.REFERENCE DESIGNATORDESCRIPTIONJ6Input supply positive voltage (+5V to +16V)J7Input supply groundST1Rail 1 output positive voltage ST2Rail 1 output ground ST3Rail 1 output positive voltage ST4Rail 1 output groundJ13Header for connection to MAXPOWERTOOL002 USB-to-SMBus interface.Pin 1: SCL Pin 3: SDA Pin 7: ALERTEven-numbered pins: GroundJ8SMB jack for input supply monitoring. This connection has a 1/20 resistive divider with 50Ω back-impedance. Connect to an oscilloscope with 20x scaling and ≥1MΩ input resistance.J9SMB jack for Rail 1 output voltage monitoring. This connection has 50Ω back-impedance. Connect to an oscilloscope with 1x scaling and ≥1MΩ input resistance.J5Alternate input supply barrel connector, 2.1mm I.D. x 5.5mm O.D. barrel jack, center-positive. Do not exceed 5A current.Evaluation KitTable 4. SwitchesTable 5. Test PointsREFERENCE DESIGNATORFUNCTIONS5SPDT toggle switch. Enable MAX17501 +3.3V buck regulator to supply V DD3P3Green light: output enabledS4Momentary tactile switch; no function on MAX20754S2SPDT toggle switch. Enable Rail 1 output regulation.Green light: PGOOD1 pin highAmber light: ALERT pin asserted lowRed light: FAULT pin asserted low (power stage fault detected)REFERENCE DESIGNATORDESCRIPTIONTP21ALERT signal (open-drain)TP20FAULT signal (open-drain)TP36SDA signal (open-drain)TP37SCL signal (open-drain)TP17EN1 signal (open-drain)TP7Input supply positive voltage TP8Input supply groundTP19Input voltage sense point for efficiency measurements TP22Input ground sense point for efficiency measurements TP18PGOOD1 signal (open-drain)TP6PWM0 signal (Rail 1)TP5PWM1 signal (Rail 1)TP4PWM2 signal (Rail 1)TP3PWM3 signal (Rail 1)TP2PWM4 signal (Rail 1)TP1PWM5 signal (Rail 1)TP13Rail 1 loop-response (Bode plot) measurement positive injection point (see MAX20754 EV Kit Schematic )TP23Rail 1 loop-response (Bode plot) measurement negative injection point (see MAX20754 EV Kit Schematic )TP25Rail 1 output voltage efficiency measurement point TP26Rail 1 output ground efficiency measurement pointTP9Rail 1 output voltage feedback sense point (for line/load regulation accuracy measurement with DMM)TP10Rail 1 output ground feedback sense point (for line/load regulation accuracy measurement with DMM)TP34V DDS supply; +1.8V power to MAX20790 power stage, from MAX20754 integrated switcher output TP35V DD3P3 supply; +3.3V power to MAX20754 integrated switcher TP29, TP30, TP31, TP32,TP33, TP39GroundEvaluation Kit#Denotes RoHS compliance.PARTTYPE MAX20754EVKIT8#MAX20754 EV Kit MAXPOWERTOOL002#USB-to-SMBus Interface5.0mV/div(AC-COUPLED)V OUT(V = 1V, I = 0A, f = 500kHz)PHASE MARGIN = 62.24BANDWIDTH = 68.75kHz50mV/div(AC-COUPLED)50A/divOrdering InformationEvaluation KitMAX20754 EV Kit Bill of MaterialsEvaluation KitMAX20754 EV Kit Bill of Materials (continued)0 0Evaluation KitMAX20754 EV Kit SchematicP W M 2R A T I O = 0.068238 T O M A T C H V I N _S C A L E _M O N I T O R D E F A U L TN O D R O O PR I N TZ 12 2 16 2 5 4 13 0 <----P H A S E S F I R I N G O R D E R 1 2P W M 5P W M 0O U T P U T #1V O U T 1:R 1R D E SZ 25 2 4 1 3 04 2 4 1 33 2 1 3R L DP W M 3P W M 1P W M 4O U T P U T #1C O M P E N S A T I O N N E T W O R K S C H E M E 9AC 2R 2C L DC I N TT O N _R I S E , T O F F _F A L L : 0.5M SO C P = 257AA D D R E S S : 0X 5A M R A M P : M H (0X 25, 37 D E C .)F R E Q U E N C Y _S W I T C H : 500K H Z V O U T _C O M M A N D : 1.0V T P 33T P 30T P 29T P 23T P 13T P 34R 58R 47R 21R 38R 37R 20R 34C 37R 27R 33C 29R 24C 25C 28R 16R 17C 90000U 1C 11C 12C 13C 14C 15C 16C 6C 2R 6R 5R 4R 3R 1C 5C 1C 4C 3L 1T P 6T P 5T P 4T P 3T P 2T P 1R 8R 7C 7C 47R 9R 111R 2R 113R 57R 36R 35R 19R 18R 46R 15C 1068P F A 1_O U T 1A 2B _O U T 1P G M C0.47B L U EV D DB L AC KB L AC KB L AC KS N S N 1A P A D A P A D 22U F22U FA P A D A P A D A P A D A P A D 1.2U HA 3_O U T 1A 3_I N 1499S N S P 14992.49K100P FR R E FA 1_O U T 1A 2_I N 1A 2_O U T 1A 2B _O U T 1C S 4M S C L SD AF A U L T _NP G O O D 1P G M DP G M CP G M BP G M AC S 0ME N 1A L E R T _N B P A DB P A D0.50%0.1U F68P F68P F 68P F 034K1K101000P F1K 1K1654994994021K1K1K332806C S 1M C S 2MV D D V I N _E F F _NP W M 1C S 5SA 3_I N 1P W M 5U V _I N C S 0S C S 1S C S 2S C S 3S C S 4S C S 5S C S 3M P W M 4P W M 3T S 1SP W M 2P W M 0P G M AC S 4SC S 3SC S 1SC S 0S4990.1U FA 2_O U T 1V D DC S 5M 0.1U FV D D 3P 322U FV D D S20K 22U FA 3_O U T 1787100P F49968P FD N I D N ID N I D N I D N ID N ID N I D N IC S 2S68P F D N I220P F0.015U F D N I1200P FP G M D 4.64K6495.76K P G M BA 2_I N 10.015U F 6040V I N _E F F _P00Evaluation KitMAX20754 EV Kit Schematic (continued)M A X 20790M A X 20790D N IR 120R 119P W M 0R 122C 244121U 24700P F 4700P F C 164P W M 4R 123D N I D N IR 1144700P F U 37123114700P F C 55C 165C 89C 103C 166C 167C 119C 120C 24C 39C 117C 118C 186C 187C 129C 130C 230C 231C 232C 184C 185C 26R 1211210987654C 19R 10C 17C 21C 131C 132C 133C 50C 51111098654324321L 2C 148C 147C 146C 53R 50V I N10U F10U F 10U F10U F47U F 0.22U F10U F10U F10U F 47U F1000P F4.7A V D D 0V I N10U FD N ID N I D N I D N I D N ID N ID N I100U F100U F 100U FA V D D 40.1U FC L 1208-2-100T R -R L X 0V D D SV D D SL X 4V O U T 1C S 4ST S 1S V O U T 1T S 1SC S 0S0.22U F0.1U F4700P F1.0U F47U F47U F 101.0U F 1.0U F1U F 00100U F100U F100U F1.0U F4.71000P F01U F104700P F B II NI NB II NI NEvaluation KitMAX20754 EV Kit Schematic (continued)M A X 20790M A X 20790451U F C 33C L 1208-2-100T R -RC 2274700P F U 4D N I6L X 2P W M 1C 107C 174C 175C 123C 124C 106C 38C 45C 172C 173C 23C 108C 109C 178C 179C 125C 126C 153C 224C 176C 177C 142C 141R 26121110987321R 117R 125C 242C 30R 25121110987654321U 5R 115C 8R 128R 126R 127C 139C 138C 1404321L 3C 36C 137C 35C 31C 3210U F10U F10U F10U F47U F 4.74.7D N I C S 2S1000P F1.0U FD N ID N ID N ID N ID N I D N ID N ID N I100U FV O U T 1C S 1S1000P FL X 10.22U F0.1U FA V D D 1V D D SV D D SV I NV I NA V D D 2T S 1SP W M 2T S 1SV O U T 10.1U F1047U F 47U F 4700P F 4700P F 1.0U F 4700P F 10U F 10U F 10U F100U F100U F01U F00100U F100U F10U F100.22U F4700P F4700P F 47U F1.0U F100U F1.0U FI NI NB II NI NB IEvaluation KitEvaluation KitMAX20754 EV Kit Schematic (continued)E F F I C I E N C Y M E A S U R E M E N T P O I N T - C O N N E C T W I T H L E A D S T O T P 26V I N S E N S E P O I N T F O R E F F I C I E N C Y M E A S U R E M E N T(A L S O F E E D S U V _I N )E F F I C I E N C Y M E A S U R E M E N T P O I N T - C O N N E C T W I T H L E A D S T O T P 25V O U T 1 S M BV I N S M B (D I V I D E B Y 20)T P 10T P 8T P 7T P 9S T 4S T 3C 218C 241C 219C 220C 221C 222C 235C 234C 238C 237C 240C 236C 239C 217C 216C 215C 214C 213C 195C 194C 193C 192C 191C 190C 223C 159C 158C 67C 157C 66C 156C 155C 154J 8J 9J 5C 210C 211C 196C 197C 91C 92C 93C 94C 203C 198C 199C 200C 201C 202C 204C 205C 206C 207C 208C 209C 84C 85C 86C 87C 88C 95C 96C 97C 98C 99C 100C 101C 188C 189D 2T P 26T P 25C 83C 82C 81C 80C 79C 76C 77C 78C 75C 65C 63C 62C 56C 212C 74C 73C 71C 72C 70C 69R 66S T 2S T 1R 67R 64C 68R 65D 1C 152C 151C 150C 149C 61C 60C 59C 58C 57J 7J 6R 63R 60T P 22T P 19R 61R 62A P A DA P A DR E D A P A D 0V I N _E F F _NB L AC K100U F B L A C K100U F 100U F 0.01U F 0.01U F A P A D V I N _E F F _P78081000.01U F 330U F108-0740-001R E D100U FM B R S 540T 3D N I D N I D N ID N ID N ID N I100U F100U F100U F100U F100U F 100U F 100U F 100U F 100U F D N ID N I 100U F D N I D N ID N ID N ID N ID N I 0V O U T 1V O U T 1V I NV O U T 1V O U T 1V O U T 1V O U T 10.01U F 0.01U F0.01U F 100U F 100U F100U F100U F 100U F100U F100U F 100U F 100U F 100U F 0.01U F 0.01U F 100U F 100U F 100U F100U F100U F100U F100U F100U F100U F100U F100U F100U F100U F100U F100U F100U F100U F 100U F100U F 100U F100U F 0.01U F 100U F 100U F0.01U F 100U F100U F100U F 0.01U F 100U F 100U F100U F 100U F100U F100U F100U FM B R S 540T 3100U F100U F0.01U F 100U F330U F 100U F 100U F 100U F 100U F 7808100U F 100U F 100U F 0.01U F 100U F100U F 100U F 100U F S N S N 17808100P FS N S P 1131-3701-266131-3701-2661K 52.3V I NV O U T 10V O U T 1330U F108-0740-001V O U T 149.97808P J -102A HEvaluation KitMAX20754 EV Kit Schematic (continued)T P 35J 4J 3J 20J 13T P 37T P 36R 102R 99R 98Q 1R 40S 5R 59R 48R 39S 5R 23C 225J P 2J P 1C 113L 5C 41U 8C 40C 112C 27R E S E T _NV D D 3P 3R E G 3P 3A L E R T _NP C C 02S A A NA U X 3P 3S C LA P A DS D AA P A D10033U HP C C 02S A A NV I NT S W -108-07-L -DS C LS D A100K2N 7002150V I N100KV O U T 1V O U T 1V O U T 1E N 3P 3R E G 3P 3A U X 3P 337.4KU P S -08-01-01-L -R AG 12J P C F U P S -08-01-01-L -R AU P S -08-01-01-L -R A100K100K100K1.0U FG 12J P C F47U F 1.0U F3300P F10U F10U FR E DM A X 17501E A T B +Evaluation KitEvaluation KitMAX20754 EV Kit PCB Layout—Top SilkscreenMAX20754 EV Kit PCB Layout—Internal Layer 2 GND MAX20754 EV Kit PCB Layout—Top LayerMAX20754 EV Kit PCB Layout—Internal Layer 3 SignalEvaluation KitMAX20754 EV Kit PCB Layout—Internal Layer 4 Signal MAX20754 EV Kit PCB Layout—Bottom Layer MAX20754 EV Kit PCB Layout—Internal Layer 5 GND MAX20754 EV Kit PCB Layout—Bottom SilkscreenEvaluation KitInformation furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use.Specifications subject to change without notice. No license is granted by implicationor otherwise under any patent or patent rights of Analog Devices. Trademarks andregistered trademarks are the property of their respective owners.REVISION NUMBERREVISION DATE DESCRIPTIONPAGES CHANGED12/21Initial release—Revision History。

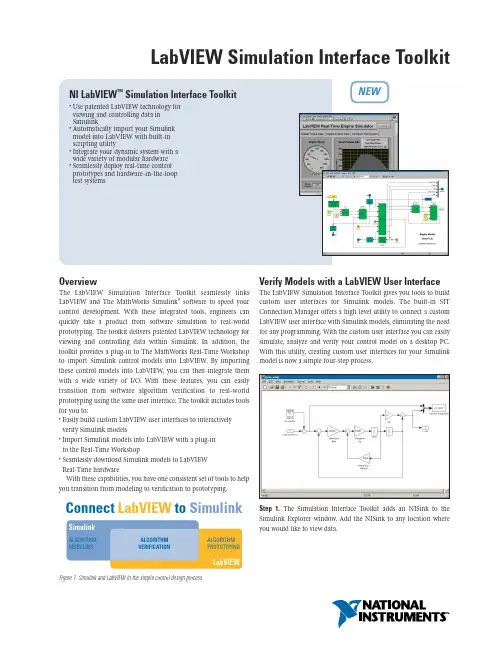

OverviewThe LabVIEW Simulation Interface Toolkit seamlessly links LabVIEW and The MathWorks Simulink ®software to speed your control development.With these integrated tools,engineers can quickly take a product from software simulation to real-world prototyping.The toolkit delivers patented LabVIEW technology for viewing and controlling data within Simulink.In addition,the toolkit provides a plug-in to The MathWorks Real-Time Workshop to import Simulink control models into LabVIEW.By importing these control models into LabVIEW,you can then integrate them with a wide variety of I/O.With these features,you can easily transition from software algorithm verification to real-world prototyping using the same user interface.The toolkit includes tools for you to:•Easily build custom LabVIEW user interfaces to interactively verify Simulink models•Import Simulink models into LabVIEW with a plug-in to the Real-Time Workshop•Seamlessly download Simulink models to LabVIEW Real-Time hardwareWith these capabilities,you have one consistent set of tools to help you transition from modeling to verification to prototyping.Figure 1. Simulink and LabVIEW in the simple control design processVerify Models with a LabVIEW User InterfaceThe LabVIEW Simulation Interface Toolkit gives you tools to build custom user interfaces for Simulink models.The built-in SIT Connection Manager offers a high level utility to connect a custom LabVIEW user interface with Simulink models,eliminating the need for any programming.With the custom user interface you can easily simulate,analyze and verify your control model on a desktop PC.With this utility,creating custom user interfaces for your Simulink model is now a simple four-step process.Step 1.The Simulation Interface Toolkit adds an NISink to the Simulink Explorer window.Add the NISink to any location where you would like to view data.LabVIEW Simulation Interface Toolkit•Use patented LabVIEW technology for viewing and controlling data in Simulink•Automatically import your Simulink model into LabVIEW with built-in scripting utility•Integrate your dynamic system with a wide variety of modular hardware •Seamlessly deploy real-time control prototypes and hardware-in-the-loop test systemsNI LabVIEW ™Simulation Interface ToolkitNEWConnect LabVIEW to SimulinkSimulinkLabVIEWALGORITHM MODELINGALGORITHM PROTOTYPINGALGORITHM VERIFICATIONStep 2.Next,you create a custom LabVIEW user interface using the extensive library of built-in controls and indicators available in LabVIEW.Step ing the SIT Connection Manager,you connect the control and indicators on the LabVIEW user interface to the parameters and NISinks of the Simulink block diagram.Step 4.Run the LabVIEW application and analyze the behavior of the model.Advanced Features for Model VerificationThe SIT Connection Manager works seamlessly over the networkso you can connect a LabVIEW user interface to Simulink models running on a different machine.This allows you to keep all Simulink models on one desktop PC or to easily verify multiple Simulink models from one user-interface location.Users can also access the SIT User Interface API directly to easily automate custom batch test sequences.For instance,you can create a batch simulator that automatically runs a Simulink model with various parameters and records the response.With the hundreds of analysis functions in LabVIEW,you can generate complex input signals for the model and analyze the results of the batch simulation.This capability dramatically reduces the amount of manual testing required during the algorithm verification stage.Figure 2. LabVIEW interfaces to Simulink over the networkImporting Simulink Models into LabVIEWYou can also import the control system model into the LabVIEW environment with the LabVIEW Simulation Interface Toolkit.The toolkit includes a plug-in for Real-Time Workshop that automatically compiles the Simulink model into a DLL and builds several LabVIEW examples of how to interface with the DLL.The example VIs built by the toolkit are specific to the Simulink model and speed development time by providing basic interfaces to data acquisition hardware.You can modify the interfaces to data acquisition hardware and replace them with interfaces to CAN I/O or motion control.With a variety of built-in libraries to interface to I/O,you can start with the examples and make minimal modifications to build your custom application.Deploying to Real-Time HardwareWith the architecture of the LabVIEW Simulation Interface Toolkit,you can seamlessly go from desktop verification of the Simulink model to real-world prototyping.By simply selecting a menu option to target a real-time system,you automatically download the necessary files for running the model while maintaining the custom LabVIEW user interface you previously created.This seamless transition preserves the work used to create the user interface while providing a solid real-time architecture for your system.Choose from a variety of LabVIEW Real-Time targets to download the Simulink model to.Build stand-alone systems with real-time PXI systems or distributed CompactFieldPoint systems.You can also integrate a real-time system into your desktop with the PCI-7041/6040E plug-in board.With the model running real-time hardware,you can easily create control prototypes and hardware-in-the-loop test systems.LabVIEW Simulation Interface Toolkit2National Instruments • Tel: (800) 433-3488•Fax: (512) 683-9300•***********•3National Instruments • Tel: (800) 433-3488•Fax: (512) 683-9300•***********•System RequirementsThe LabVIEW Simulation Interface Toolkit requires that you have a proper license for the following products:•MATLAB® version 6.0 or later •Simulink version 4.0 or later•Real-Time Workshop® version 4.0 or later •Microsoft Visual C++ version 6.0 and •LabVIEW version 7.0 or laterLabVIEW Simulation Interface ToolkitLabVIEW Simulation Interface Toolkit ......................778552-03Upgrade,from version 1.0....................................850552A-03LabVIEW Development SystemProfessional ..............................................................776678-03Full ............................................................................776670-03LabVIEW Real-Time Module ......................................777844-03BUY ONLINE!Visit /info and enter lvsit.Ordering InformationGlobal Services and SupportNI has the services and support to meet your needs around the globe and through the application life cycle – from planning and development through deployment and ongoing maintenance – and tailored for customer requirements in research,design,validation,and manufacturing.We have direct operations in more than 37 countries and distributors in another 12 locations.Our local sales and support representatives are degreed engineers,ready to partner with you to find solutions that best fit your needs.Local Sales and Technical SupportIn offices around the globe,our staff is local to the country so that you have access to field engineers who speak your language and are available to consult on your unique needs.We also have a worldwide support organization staffed with Applications Engineers trained to quickly provide superior technical e our online Request Support interface (/support) to define your question,then speak to or e-mail an Applications Engineer,or access more than 14,000 worldwide measurement and automation professionals within NI Developer Exchange Discussion /support also provides immediate answers to your questions through self-help troubleshooting,product reference,and application development resources.For advanced technical support and software maintenance services,sign up for Premier Support,a program that provides expanded hours of(typically four business hours).Training andCertificationcontribute to your success.variety of training alternatives,paced tutorials and interactive CDs,hands-on courses taught by experienced instructors – all designed so that you can choose how to learn about our products.Further,NI offers certifications acknowledging individual expertise in working with NI products and technologies.Visit /training for more information.Professional ServicesOur Professional Services team consists of National Instruments Applications Engineers,NI Consulting Services,and the worldwide National Instruments Alliance Partner Program (a network of600 independent consultants and integrators).Our Professional Services team can offer services ranging from basic start-up assistance and collaborative development withyour engineers,to turnkeysystem integration andmaintenance of your system.In addition to our NI Alliance Partners,we have developed global relationships with many industry partners that range from computer software and hardware companies,such as Microsoft,Dell,Siemens, and Tektronix.By collaborating with these companies,you receive a complete spectrum of solutions – from components to turnkey systems.Find the Alliance partner directory at /allianceProduct ServicesNI GPIB products are warranted against defects in workmanship and material for one year from the date of shipment.To help you meet project life-cycle requirements,NI offers extended warranties for an additional charge.NI provides complete repair services for our products.Express repair and advanced replacement services are also available.Or,order your software and hardware installed in PXI and PXI/SCXI™ systems with NI Factory Installation Services.Ordering Made EasyVisit /products to browse product specifications,make comparisons,or access technical representatives via online chat or telephone.Worldwide customers can use a purchase order or credit card to buy in local currency and receive direct shipments from local NI offices.Our North American Customer Service Representatives are available Monday through Friday between 7 a.m.and 7 p.m. Central Time.Outside North America,please contact the NI office in your country.Order Status and Service RequestsNational Instruments brings you real-time status on current orders at /status Similarly,find out the status of open technical support incidents or hardware repair requests at /support/servicereqNational Instruments • Tel: (512) 683-0100•Fax: (512) 683-9300•*********** • (800) 433-3488© 2004 National Instruments Corporation. All rights reserved. Product and company names listed are trademarks or trade names of their respective companies.。

基于Lab V IE W 的数据采集与信号处理系统的设计杜 娟1,邱晓晖1,赵 阳2,颜 伟2,缪 飞1(1.南京邮电大学通信与信息工程学院,江苏南京210003;2.南京师范大学电气与自动化工程学院,江苏南京210042)[摘要] 介绍了虚拟仪器领域中最具代表性的图形化编程开发平台LabV I EW,并对基于LabV I EW 编程环境实现数据采集进行了研究,设计实现了一种基于LabV I EW 8 5环境,以E M I 噪声分析仪为下位机的数据采集与信号处理系统的设计方法.该设计方法主要实现了以RS232为代表的串口通讯,数组转换及频谱分析等功能,结果表明应用该设计方法设计出的系统具有简洁友好的人机界面,可直接在前面板上完成各种操作与观测.该设计方案较之目前大多数的设计方法相比有效地降低了程序的运算量,节省了运算时间,成功实现了实时无差错的采集到由下位机发来的完整数据.[关键词] LabV I EW,串口通讯,数组转换[中图分类号]TM 461;TN 713+.7 [文献标识码]A [文章编号]1672-1292(2010)03-0007-04Data A cquisiti on and Signal Processi ng Syste m Based on Lab V IE WDu Juan 1,Q iu X iaohui 1,Zhao Yang 2,YanW ei 2,M iao Fei 1(1.Co ll ege of Co mmun ication and In f or m ati on Engi n eeri ng ,Nan ji ng U n i vers it y ofPost and Co mmun ications ,Nan ji ng 210003,Ch i na ;2.School of E l ectri cal and Au to m ati on Engi n eeri ng ,Nan ji ng Nor malU n i vers it y ,N an ji ng 210042,C h i na)Abstrac t :L ab V IE W is i ntroduced i n t h is pape r as a k i nd of mo st representative g raph i ca l prog ramm i ng platf o r m s i n V ir -t ua l instru m ent fi e l d ,and rea lizi ng data acqu i sition based on L ab V I E W prog ra mm i ng env ironment is st udied ,then a de -s ire m et hod o f D ata acqu i s i tion and Signa l processing system used E M I no i se analyze r as the next b itm achi ne based onlabv i ew 8.5is introduced .T he system realized R S232ser i a l co mm un ica ti on ,array conversi on and spectral analysisfuncti ons .The result show s t hat the system designed by th i s m ethod has a s i m p l e and friendly i nterface ,and tha t userscan do every operati on and observa tion i n t he front pane l d irectly .T his sche m e reduces the calcu lati on procedure e ffec -ti ve l y and save ti m e ,achieves the rea-l ti m e and error -free co llected the data i ntegr itily .K ey word s :labv i ew ,serial communicati on ,a rray conversi on收稿日期:2010-06-02.基金项目:中国博士后基金(20080431126)、毫米波国家重点实验室开放基金(K200903)、江苏省博士后基金(0702033B )、江苏省自然科学基金(BK2008429).通讯联系人:邱晓晖,博士,副教授,研究方向:现代信号处理.E-m ai:l qi uxh @n j upt .edu .c nLabV I E W (Labo ratory V irtual I nstr um ent Eng i n eering W orkbench)是基于图形编译G (G raph ics)语言的虚拟仪器软件开发平台,具有数据采集、数据分析、信号发生、信号处理、输入输出控制等功能,是公认的标准数据采集和仪器控制软件.在Labv ie w 环境下开发的应用程序称为V I(V irtua l Instrum ent).一个完整的LabV I E W 程序主要由前面板、程序框图和图标/连接端口3部分组成[1],前面板是交互式图形化用户界面,用于设置输入数值和观察输出量;程序框图是定义V I 功能的图形化源代码,包括前面板上没有但编程必须有的对象,如函数、结构和连线等,利用图形语言对前面板的控制量和指示量进行控制;图标/连接端口是用于把程序定义成一个子程序,以便在其他程序中加以调用.LabV I E W 中自带450多个内置函数,专门用于从采集到的数据中挖掘有用的信息,用于分析测量数据及处理信号.1 系统硬件结构部分传导电磁干扰综合测量与分析系统可以对被测设备进行噪声诊断与抑制,包括硬件部分和软件部分[2,3].硬件部分的原理图如图1所示.系统硬件又分为模拟部分和数字部分,模拟部分由中心控制模块、第10卷第3期2010年9月 南京师范大学学报(工程技术版)J OURNAL OF NAN JI NG NORMAL UNI VERS I TY(ENG I NEER I NG AND TECHNOLOGY ED I T I ON) V o.l 10No .3Sep,t 2010信号类型选择模块、放大倍数选择模块、滤波器模块构成.其中,中心控制模块为C ylone 公司的EP1C3T 144FPGA 芯片,负责控制信号类型、放大倍数的选择,并控制采样、数据存储及传输;信号类型选择模块由新型噪声分离网络将输入信号分为共模/差模信号,并由FPGA 芯片控制G6S-2F 型继电器K,选通共模/差模或直通信号的其中一路;噪声放大模块由TH S4271DGK 运算放大器完成信号20dB 放大;串口数据传输模块由FPGA 控制RS232串口,用于向计算机传输数据并接收计算机发送的命令.2 软件设计部分软件部分具有噪声测量结果显示、噪声分析功能,各个功能分别在相应的软件界面上实现.本系统采用模块化的软件设计思想来编写,Lab V I E W 程序框图可以分为3部分:串口数据采集模块、数组转换模块、波形显示模块.上位机程序的流程图如图2所示.2 1 串口数据采集模块2 1 1 V ISA 概述虚拟仪器软件架构V I SA (V irtua l I nstru m ents So ft w are A r -ch itecture)是应用于仪器编程的标准I/O 应用程序接口,是工业界通用的仪器驱动器标准API(应用程序接口).它采用面向对象编程,具有很好的兼容性、扩展性和独立性.通过V ISA,用户能与大多数仪器总线连接,包括GPI B 、USB 、串口、PX I 、VX I和以太网.无论底层是何种硬件接口,用户只需要面对统一的编程接口,即V I SA.V ISA 的另一个显著优点是平台可移植性,任何使用V ISA函数的程序可以很容易地移植到其他平台上.V I SA 定义了自己的数据类型,就避免了在移植程序时由于数据类型大小不一导致的问题.2 1 2 系统组成(1)串口参数设置[4].LabV I E W 的串口通讯V I 位于I nstru m ent I/O Platte 的Serial 中,此部分程序用到了LabV I E W 中串口操作的配置节点设置串口通讯的波特率、校验方式、数据位数、停止位数等参数.(2)写模块.包括两部分:前一部分用于发射同步时钟,用于与下位机的时钟同步;后一部分为命令发送部分,用于向下位机取任意时间的数据.南京师范大学学报(工程技术版) 第10卷第3期(2010年)(3)读模块.在接收数据之前需要使用V I SA Bytes at seria l port 查询当前串口接收缓冲区中的数据字节数.如果V I SA read 要读取的字节数大于缓冲区中的数据字节数,V IS A read 操作将一直等待,直至缓冲区中的数据字节数达到要求的字节数[5].在这部分的操作过程中,要注意延迟时间的设定,过长会增加等待时间,过短会收不到完整的数据[6].经过多次试验,本程序的延迟时间为2m s ,利用读串口节点读取串口缓冲区中的字符串,这部分的程序框图如图3所示:2 2 数组转换与实时显示模块2 2 1 数组转换下位机传送的数据格式为十六进制ASCII 形式,需要将其转换为十进制数字形式后才能保存并显示.具体的操作方法是:首先判断收到的字符串是否是完整的,如果收到了完整的8K 个字节,则对字符串接收区连接至 字符串至数组的转换 控件.由前面关于硬件部分的介绍可以得出下位机输出的噪声信号分为总信号、共模信号、差模信号,并都有0db ,20db 的两种输出,所以共6组数据,因此本设计采用了事件结构,设置8个分支分别负责控制发送6组代表不同信号的数据和保存数据,鼠标按下即可自动发送.2 2.2 数据保存与实时显示(1)数据保存是把采集来的数据保存到M ySQL 数据库里,首先进行的是数据库的选择以及数据库表格的建立,然后用LabSQL 工具包将采集的数据按照一定的时间间隔保存到数据库的表格里.(2)历史数据查询.因为已经把采集的数据保存在数据库里了,所以历史数据的查询只需要从数据库里按照一定的条件检索出来就行了[7].这样就涉及到检索条件的问题.而保存数据的表格的主键已设为保存时刻.每个数据在时间上是唯一的,因此检索条件确定为保存数据的时间段.这一模块的程序图如图4所示.杜 娟,等:基于Lab V IE W 的数据采集与信号处理系统的设计南京师范大学学报(工程技术版) 第10卷第3期(2010年)2 3 波形显示与FFT处理模块经过上述的数组转换后,可以直接对一维数组进行快速傅里叶变换,本设计主要观察峰值信息,所以在显示波形模块中,设定属性时,选择所选测量 幅度(峰值).图5为曲线建立了一个游标,拖动游标中心点可以在波形图上自动搜索临近的峰值坐标[8].GB9254Vo ltage on QP下方曲线为标准线,此波形为在没有信号源输入时采集到的差模0DB噪声信号.由图可以看到现在游标采集到的峰值坐标为(8 976608,22 5189).3 结语本文研究了利用LabV I E W开发平台、串口通讯及虚拟仪器技术成功的实现了对下位机进行数据采集、显示及信号处理等功能.结果表明,LabV I E W比其它文本语言更加简单直观可靠,且该系统具有良好的可移植性,通过扩展采集卡通道及重新编程,可以满足对不同数据的采集要求.[参考文献](References)[1]孟武胜,朱剑波,黄鸿,等.基于L abV IE W数据采集系统的设计[J].电子测量技术,2008,31(11):63-65.M eng W usheng,Zhu J i anbo,Huang H ong,e t a.l Da ta acqu i sition syste m based on L ab V I E W[J].E l ec tron i c M easure m ent T echno l ogy,2008,31(11):63-65.(i n Ch i nese)[2]赵阳,李世锦,孟照娟,等.传导性E M I噪声的模态分离与噪声抑制问题探讨[J].南京师范大学学报:工程技术版,2004,4(4):1-4.Zhao Y ang,L i Shiji n,M eng Zhao j uan,et a.l T echn i que o f conducted E M I no i se separati on and no ise suppression[J].Journal o f N an jing N orma lU n i ve rsity:Eng ineer i ng and T echno l ogy Ed iti on,2004,4(4):1-4.(in Ch i nese)[3]Zhao Y,See K Y.Performance study of C M/DM d i scri m i nation ne t w ork f o r conduc ted E M I diagnosis[J].Chinese J of E lec-tron ics,2003,12(4):536-538.[4]乔芳,林小玲,余渊,等.基于L abV IE W实时数据采集系统的设计[J].中国市政工程,2009(2):24-25.Q iao F ang,L i n X iao li ng,Y u Y uan,e t a.l O n desi gn of rea-l ti m e data acquisition syste m based on Lab V I E W[J].Ch i naM u-n i c i pa l Eng i neering,2009(2):24-25.(i n Ch i nese)[5]陈金平,王生泽,吴文英.基于Lab V I E W的串口通信数据校验和的实现方法[J].自动化仪表,2008,29(3):32-34.Chen Ji nping,W ang Shengze,W uW eny i ng.I m ple m enti ng m ethod o f ser i a l communicati on data checksum based on L abV IE W [J].Process A utom ati on Instrumentation,2008,29(3):32-34.(i n Ch i nese)[6]X iang X J,X ia P,Y ang S,et a.l R ea-l ti m e d i g ita l si m ulati on o f contro l syste m w ith L ab V I E W si m ulati on interface too lkit[J].P roceedi ngs o f the26th Chi nese Contro l Conference July26-31,2007:318-322.[7]林爽,杨风.基于L abV IE W的多通道数据采集系统的研究[J].山西电子技术,2009(3):18-20.L i n Shuang,Y ang Feng.T he research of m ultichanne l DAQ system based on L ab V IE W[J].Shanx i E lectron ic T echno logy, 2009(3):18-20.(i n Chinese)[8]孙秋野,刘昂,王云爽.L ab V IE W8 5快速入门与提高[M].西安:西安交通大学出版社,2009:135-157.Sun Q i uye,L i u A ng,W ang Y unshuang.L abV IE W8.5Q u i ck Start and I m prove[M].X i an:X i an J i aotong U n i versity P ress,2009:135-157.(i n Chi nese)[责任编辑:刘 健]。

电气自动化专业外语翻译作业A High Performance Interleaved Discontinuous PWM Strategy for TwoParalleled Three-Phase Inverter(双并联三相逆变器的高性能交错间断PWM控制策略)Abstract—This article aims to obtain the optimal combination of the switching loss, maximum zero-sequence circulating current (ZSCC), and line current ripple, which benefits most of the applications. The analysis shows that the interleaved discontinues pulsewidth modulation (IDPWM) maintains the minimum switching loss and line current ripples, but it introduces a larger ZSCC.Therefore, to obtain the optimal combination of the switching loss,maximum ZSCC peak, and line current ripple, it is essential to retain the minimum switching times and the optimal line current ripple of IDPWM but further reducing its overly large ZSCC. Further analysis reveals that IDPWM includes the vector combinations with medium ZSCC change rates, resulting in the larger ZSCC.Given the redundancies of the vector combinations, this article proposes a simple matrix to modify the original modulation signals of IDPWM, eliminating the medium ZSCC change rates. The proposed PWM scheme retains the minimum line current ripple and switching times as those of IDPWM while further reducing its overly large ZSCC, as validated by analytical results as well as experimental results. Since the proposed method obtains the optimal combination among switching loss, line current ripple, and maximum ZSCC peak, we name the proposed PWM scheme a high-performance DPWM.译文:摘要——本文旨在获得开关损耗、最大零序环流(ZSCC)和线路电流纹波的最佳组合,从而使大多数应用受益。

New FeatureApplying additional Signals during VI Process2015Introduction•VI•Using additional signals–Input channels–Not updated by VI–From beginning or additional to last drive•Process integrated and automatedin FEMFAT LAB vi•Software release end of 2015 Example:VI of 4 posterusing additionalWFT signalsNew folder•Additional evaluation •No change in function of other foldersData of additional signals •Different file formats possible•Usually measured dataData of additional signals •If activated, these signals will be applied to adm-file for next simulation •Select channels of data file which should be used additionallyInformation of additional input channels•Sequence defined by selection•Spline ID has to be defined corresponding to adm-file •Gain–Default is 1, i.e. same data as in data file–Can be changed, e.g. for using different wheel loadFilter response channels •Automatic filtering of response files•Trend will be computed with filtered signals•Filter applied by filter fileTrend monitoring•Only location changed •From folder Iteration to folder Additional evaluationExample•VI of full vehicle using WFT signals (“4 Poster with WFT signals”)•Iteration of vertical displacements (4 poster)•Apply additional channels to vertical displacements–FX, FY, TX, TZ–At all 4 wheel centers•Additional channels can be applied –From first iteration on–To last drive•7th iteration of 4 poster•Spring displacements and wheelcenter acceleration very accurate•Additional WFT signals applied Spring displacement front leftblack…measurementred…...simulation•Selection of desired file which includes also WFT signals•Selection of WFT channels•Channel description of data file is shown•Spline ID has to be selected for each additional input channel•Gain factor 1•Simulate–Additional channels will beapplied additionally–adm-file includes iterated vertical displacements (4-poster) andmeasured additional WFTsignals (FX, FY, TX, TZ)Results•WFT torque front left about Z axis(steering torque) black…measurementred…... result of 4-poster(no steering torqueapplied)green.. 4-poster includingadditional WFTsignals。

Measurement and controlling with Windows™Flexible confi guration of user interfaces and displays Easy generation of protocol and presentation sheetsCompatible with DAQ hardware of most manufacturersExpandable with individually de-fi ned functionsOnline Data Acquisition and AnalysisDASYLab WindowFive easy solutions <for convincing results>... one module for adata logger ...... two modules for achart recorder ...... four modules for a storage oscilloscopewith individual scaling ..... three modules for afrequency analyser... fi ve modules for acquisition,display, frequency analysis andstatistics of your dataDialogsAlso here you don’t need any programming! Confi gure modules easily using the Module Properties di-alog boxes. Easily specify the capability of each function block, the number of channels and the parameter settings.LayoutsUse the layout view to create the operator inter-face to work with your application and to defi ne the structure and content of professional reports. For each application you have 200 pages to display your data and results.WorksheetThe worksheet is where you create the data fl ow logic for the application. Select and combine the desired function modules and connect them with wires that represent the data fl ow.The browser window displays a tree structure con-taining all available function modules as well as any saved block boxes. It also contains a navigator to quickly fi nd specifi c modules in a worksheet.The console window displays graphical and numeri-cal information about content and structure of the data fl ow.DisplaysSignal AnalysisFunction ModulesNo programming required! Confi gure your experiment setup easily using the drag’n’drop capability of DASYLab. Pick up the required Function Module from your favorite Modules of the module bar or use the tree of the browser window.DASYLab Display OptionsDisplaysUse the different displays in DASYLab to repre-sent your data online. Interactively zoom and view cursor measurements on or off-line..DASYLab FeaturesYou can choose between four different DASYLab Versions to get exactly the features that you need. The light version contains the basic func-tions for PC-based data acquisition and representation. The basic version comes with additional mathematical and statistical functions as well as basic control modules. The full version comes with additional blocks for automation of measurement and analysis tasks. The professional version contains the network functionality, frequency and Rainfl ow analysis as well as a setpoint generator module.Layouts and ReportsUse the DASYLab VI-Tool to create a clear and informative presenta-tion of your data and results. Represent your data in scope displays, numerical listings, chart recorders or bar graphs, just by placing the cor-responding objects in the layout and connecting them to the worksheet modules. Use text or graphical elements to enhance the clarity and use-ability of your application.F u n c t i o n a lG r o u pL i t e B a s i c F u l l P r oTrigger FunctionsPre/Post Trigger z z z zStart/Stop Trigger z z z z Combi Trigger z z z z Sample Triggerz z z z Trigger on Demand z z z zRelayz z z zMathematicsFormula Module z z z zArithmetic z z z z Comparator z z z zTrigonometry z z z zScalingz z z zDifferentiation/Integrationz z z z Logical Operations z z z z Bit Logic z z z z FlipFlop z z z z Gray Code z z z z Slope Limitation z z z z Reference Curvez z z zStatisticsStatical Values z z z z Position in Signal z z z z Histogram z z z z Rainfl owz z z Two Channel Counting z z z Regression z z z z Counter z z z z PWM Analysis z z z z Min/Max z z z z Sort Channels z z z z Check Reference Curvez z z zSignal AnalysisFilter z z z z Correlation z z z z Data Window z z z z FFTz z z z Polar/Carthesian z z z z FFT Filter z z z FFT Maximumz z zF u n c t i o n a lG r o u pL i t eB a s i c F u l l P r on-Harmonic z z z Elektricz z z z Harmonic Distortion z z z z Period Check z z z z Third Analysisz zzControlSequence Generator z zzGenerator z z z zSwitch z z z z Slider z z z z Coded Switch z z z z PID Control z z z z Two-Point Control z z z z Time Delay z z z z Latch z z z z Signal Router z z z z TTL Pulse Generator z z z z Stopzz z zGlobal Variable Read z z z z Global Variable Set z z z z Blocktime Infoz z z zDisplayY/t Graph z z z zX/Y Graph zz z zChart Recorder z z z zPolar-Plot zz z zAnalog Meter z z z z Digital Meter z z z z Bar Graph z z z z Status Lamp z z z z Diagramz z z z List Displayz z z zFilesRead Data z z z z Write Data z z z zBackup Data z z z z ODBC Input z z z z ODBC Outputz zz zF u n c t i o n a lG r o u pL i t eB a s i c F u l l P r o Data ReductionAveragez z z z Block Average /Peak Hold z z z zSeparate z z z z Merge/Expand zz z zShift Register z z z zCut Out z z z z Time Slice zz z z Circular Bufferz zz zNetworkNet Input z z ¤z Net Output z z ¤z Message Input z z ¤z Message Output z z ¤zData-Socket Import z z z z Data-Socket Exportzz z zSpecialNew Black Box z z z z Black Box Export/Import zz z z Action z z z z Message z z z z Send E-mail z z z zTime Base z z z z Signal Adaptionzz z zAdd-on ModulesConvolution z z z Weight z z z Transfer z z z Universal Filter z z z Save Universal File z zzISO 8041 Module z z Sound Level Meter z z Sound Power Meterz zProgram OptionsSequencerz z z zNumber on VI-Tool pages11200200DASYLab Lite Version is restricted to 64 data channelsLegendIncluded in this versionzNot included in this versionzAvailable as part of Analysis Toolkit AddonAvailable as individual Add-on moduleOnly available in Net version¤Input ModulesUse the different function modules to create in Layout Windows or on the worksheet screen sliders, switches, or other interactive elements to allow the user changing parameters and values while experiment is running.DASYLab InterfacesDASYLab supports a wide variety of differ-ent data acquisition devices using any kindof available interface to the PC. Whetheryou have stationary, mobile or in-vehicle ap-plication, DASYLab will support the appro-priate sources.DASYLab ExtensionsAnalysis ToolkitThe analysis toolkit contains a group of modules to analyse a signal in thefrequency domain: Octave and third octave analysis, transfer functions,different kinds of fi lters as well as signal energy calculation.Sequence GeneratorThe Sequence generator module gives you the tools to easily create setpointsignals for control applications. Curves and ramps of different shapes can becombined to create custom waveforms.Vibration Impact on Human BodyExtension ToolkitNeed a custom function? Use the extension toolkit to add modules toDASYLab using Microsoft C. Use the working examples as the basis foryour modules.Driver ToolkitHave your own hardware? The driver toolkit allows you to include anykind of data source in DASYLab. It contains the complete API to developyour own drivers using Microsoft C.DAP MicrostarPCIPXI/Compact-PCIUSBPC-CardCANEthernet InterfaceIEEE InterfaceRS232-InterfaceSPS Simatic S7 Interface Net OptionThe network communication modules allow fast data and informationtransfer between different DASYLab applications via TCP/IP.This extension contains the complete analysis and weighting for vibrationimpact on the human body generated by machines according to ISO 8041.AcousticsSound level and sound power calculation according to the appropriateISO norms are the central analysis modules of this extension.Software InterfacesAnalog InputAnalog Input MultispeedAnalog OutputAnalog Output MultispeedDigital InputDigital Input MultispeedDigital OutputDigital Output MultispeedCounter InputFrequency OutputDataSocket ImportDataSocket ExportDDEDDE InputDDE OutputRS232RS232 InputRS232 OutputIComICom Input (TCP/IP)ICom Output (TCP/IP)IEEE 488ieee488 Inputieee488 OutputModBusAnalog InputAnalog OutputDigital InputDigital OutputDistributor。

APPLICATION NOTEUSING ST7 PWM SIGNAL TO GENERATEANALOG OUTPUT (SINUSOID)by Microcontroller Division Application TeamINTRODUCTIONThe purpose of this note is to present how to use the ST7 PWM/BRM for the generation of a 50Hz sinusoïd tunable in average and amplitude. Our application has been done with a ST72511R4.1 ST7 PWM/BRM GENERATORIn this part the main PWM/BRM features of the ST7 are pointed out. Please refer to the ST7 datasheet for more details.The ST7 PWM/BRM includes a 6-bit Pulse Width Modulator (PWM) and a 4-bit Binary Rate Multiplier (BRM) Generator. It allows the digital to analog conversion (DAC) when used with external filtering.PWM GENERATIONThe counter increments continuously, clocked at internal CPU clock. Whenever the 6 least significant bits of the PWM counter overflow, the output level for all active channel (only PWM0 in this application) is set.When a match occurs between the PWM counter and the PWM binary weight, the corre-sponding output level is reset. (see Figure 1).This PWM signal must be filtered with an external RC network selected for the filtering level re-quired.Dedicated pins for the PWM/BRM are connected to a 1k serial resistor which must be taken into account to calculate the RC filter time.(see Figure 2).In any case, the RC filter time must be higher than T cpu x64 (= 8µs here because f cpu=8MHz). In this application, no additional external resistor is used; the value of C ext used is 1µF.The RC filter time is then equal to 1ms (it has to be higher T cpu x64).AN1041/10981/121ST7 PWM/BRM GENERATOR2/12Figure 1. PWM GenerationFigure 2. Typical PWM Output FilterBRM GENERATIONThe BRM bits allow the addition of a pulse to widen a standard PWM pulse (with duration of T cpu ) for specific PWM cycles. This has the effect of “fine-tuning” the PWM Duty cycle (without modifying the base duty cycle), thus, with the external filtering, providing additional fine voltage steps (see Figure 3).The PWM intervals which are added to are specified in the 4-bit BRM register and are en-coded as shown in the following table. The BRM values shown may be combined together to provide a summation of the incremental pulse intervals specified (see Figure 4).COUNTER63COMPARE VALUEOVERFLOWOVERFLOWOVERFLOW000tPWM OUTPUTtT CPU x 641K (max)C extOUTPUT VOLTAGE STAGER intOUTPUT R ext3/12ST7 PWM/BRM GENERATORTable 1. Bit BRM Added Pulse Intervals (Interval #0 not selected).Figure 3. BRM pulse addition (PWM > 0)Figure 4. Precision for PWM/BRM Tuning (after filtering).BRM 4 - Bit DataIncremental Pulse Intervals0000none 0001i = 80010i = 4,120100i = 2,6,10,141000i = 1,3,5,7,9,11,13,15T CPU x 64T CPU x 64T CPU x 64T CPU x 64 incrementm = 1 m = 0m = 2T CPU x 64m = 15ST7 PWM/BRM GENERATORREGISTER DESCRIPTIONThe 10 bits are separated into two data registers:PULSE BINARY WEIGHT REGISTER701POL P5P4P3P2P1P0Channel 2 Pulse Binary Weight Register (PWM2)Channel 3 Pulse Binary Weight Register (PWM3)Bit 7 = Reserved(Forced by hardware to “1”)Bit 6 = POL Polarity Bit for channel i.0: The channel i outputs is a “1” level during the binary pulse and a “0” level after.1: The channel i outputs is a “0” level during the binary pulse and a “1” level after.Bit 5:0 = P[5:0] PWM Pulse Binary Weight for channel i.This register contains the binary value of the pulse.BRM REGISTERS70B7B6B5B4B3B2B1B0Channels 3+2 BRM Register (BRM32)Bit 7:4 = B[7:4]BRM Bits (channel i+1).Bit 3:0 = B[3:0] BRM Bits (channel i)This register defining the intervals where an incremental pulse is added to the beginning of the original PWM pulse. Two BRM channel values share the same register.From the programmer's point of view, the PWM and BRM registers can be regarded as being combined to give one data value.For example :1POL P P P P P P+B B B B Effective (with external RC filtering) DAC value1POL P P P P P P B B B B4/12A 50HZ SINUSOID2 A 50HZ SINUSOIDThe goal of this application is to generate a 50Hz sinusoïd. The use of the BRM allows us to have a better precision thanks to the sub steps it creates (Vdd/1024).In this application, there are two ways to obtain these values:- you can call the function calc() at the beginning of the main program (this function calculates the 64 desired values one time and stores them into a table called value[] in RAM).- you can also use the table value[] declared in ROM with all the 64 values, calculated before running the application. If you change the amplitude or the offset of the signal, take care to change values into the table (file table.c).According to the way you choose, you have to include the files function.c and function.h or table.c and table.h (please, refer to the listing of the program: the unchosen way is in com-ment).These values are words (16 bit-long). The four least significant bits are put in BRM and the fol-lowing six bits are put in PWM. Effectively,the biggest value is 3FF (got for cos(0) recentered in [0..1023]), the six upper bits are then unused because at zero.We use an hardware Watchdog, active just after reset; for this reason, it has to be refreshed every 98ms (or less).To describe a sinusoïd between 0 and 2 π, we used 64 values with steps of 2π/64 radians.FREQUENCYTo have the desired frequency (50Hz here), a real time base is created using a 16 bit timer output compare interrupt (see AN974). The period is 20ms, and then 625 counts timer (dec-imal value) are needed (fcpu/4=2MHz, and there are 64 points to describe the sinusoïd). During interrupts, a value is put into the BRM and the PWM registers and the OC1R counter is updated.5/12A 50HZ SINUSOID6/12Here follows a table giving different values of the counter for different frequencies:OCCUPATION TIMEDuring an interrupt and for this program running at fcpu=8MHz, the CPU is used at 11.76%(36.75µs) by loop of 20ms/64 (because the frequency considered is 50Hz). That means that 88.24% of the CPU are free to do anything else.OFFSET AND AMPLITUDEThe function calc() calculates the sinusoïd values with the expression:where Am represents the amplitude of the sinusoïd and offset the way to change the average value. As the sinusoïd has to be between 0 and 1023 (0 and 5 Volts) for an efficient use of the 10 bit DAC (210=1024), initial values for Am and offset in this application are 511 and 512 (to have the maximum amplitude).These values can be changed but there are the following constraints:f(Hz)5060708090100Counter value625521446391347313offset+Am ≤1023offset-Am ≥0Am*cos(X)+offset7/12FLOWCHARTS3 FLOWCHARTSHere follows the flowchart of the main program using the function calc():Figure 5. Main Program Flowchartcall calc()values calculated?noyesfilling of BRM with value[i] and $0Ffilling of PWM with value[i]>>4 and $3F or $C0watchdog refreshedinterrupt?yesnocounter updatedFLOWCHARTS8/12Figure 6. Function Flowchartvalue[k]=cos(2πκ/64)*Am+offsetwatchdog refreshed every ten calculationsk++i++≥yes noENDi 63SOFTWARE4 SOFTWAREThe assembly code given below is for guidance only. For missing label declaration please refer to the register label description of the datasheet or the ST web software library (“map7250 .c” file...).main.c:// Include files#include “map7250.h” // ST7250 memory and registers mapping#include “variable.h” // Define your global variables here#include “function.h” // All functions used in the application can be definedgoodmanagement.projecta/herefor“table.h”//#include//-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-main(void)void{PWMBRMregisters.andPWM2=0x80; //InitializationofBRM32=0x00;calc();thesinusoïdvalues.calculatingtheCalloffunction//usetothetablebettervaluestime,This//it’stakesalongfile(seetable.c).//ROMlocatedin{asmallinterrupts.Disablesim //}comparevalueOC1R.inLoadtheTAOC1HR=(delta>>8); //delta;=TAOC1LRtimeratFFFC.theResetTACLR=0; //nowithotherset.CompareOLV1interrupt, 0x41; //OutputTACR1Timer=inAmodewith16MHzquartz.normalainclock=fcpu/4->0.5µsTACR2=Timer0x80; //{asminterrupts.Enablerim //}while(1)thereset98ms).ofeveryWatchdog(becauseRefresh{WDGCR=0x7F;} //theof}OFFILE***/END(c)/*********************1998STMicroelectronics9/12SOFTWAREitpwmb.c: (interrupt routine)-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-DESCRIPTION : Main Interrupt Service RoutinesThis file can be used to describe all the interrupt subroutinesthat may occur within your application.As the routines’ names are declared in the .prm file, when an interrupthappens, the software will branch automaticly to the corresponding routineaccording to the interrupt vector loaded in the PC register.For now, the routines are all empty as nothing special may occur inthe example’s main program.It’s better to create as many interrupt functions as necessary, ie for eachinterrupt vector even if the routine is empty (iret). By doing this, youwill prevent your software from branching to an undesired interrupt routine.-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-MODIFICATIONS :******************************************************************************/#include “map7250.h”#include “variable.h”#include “lib_bits.h”#pragma TRAP_PROC SAVE_REGS/*-----------------------------------------------------------------------------ROUTINE NAME : tima_rtINPUT/OUTPUT : NoneDESCRIPTION : timer Interrupt Service RoutineCOMMENTS :-----------------------------------------------------------------------------*/void tima_rt(void){#pragma DATA_SEG _ZEROPAGEstatic unsigned char index=0;unsigned int total;#pragma DATA_SEG DEFAULTif( ValBit(TASR,6) ) // First step to clear OCF1. Test if the IT is generated by OCF1.{BRM32 = value[index] & 0xF; // The four least significant bits are put in the BRM register.PWM2=((value[index] >> 4) & 0x3F) | 0x80; // Bit 7=1 (unused), POL=0.10/12SOFTWARE// The six upper bits of the table value are put in PWM0(counter).if(index==63) index=0; // If it’s the end of the table, jump to its begin.total=(TAOC1HR<<8)+TAOC1LR; // Total of the counter (16 bits). Second step to clear the OCF1 flag.total+=delta; // Update of the counter.TAOC1HR=(total>>8); // Update of TAOC1HR.TAOC1LR=total; // Update of TAOC1LR.index++; // Next value.}else{TAOC2LR=0x0; // Second step to clear the OCF2 flag.}/*** (c) 1998 STMicroelectronics ****************** END OF FILE ***/11/12SOFTWARE"THE PRESENT NOTE WHICH IS FOR GUIDANCE ONLY AIMS AT PROVIDING CUSTOMERS WITH INFORMATION REGARDING THEIR PRODUCTS IN ORDER FOR THEM TO SAVE TIME. AS A RESULT, STMICROELECTRONICS SHALL NOT BE HELD LIABLE FOR ANY DIRECT, INDIRECT OR CONSEQUENTIAL DAMAGES WITH RESPECT TO ANY CLAIMS ARISING FROM THE CONTENT OF SUCH A NOTE AND/OR THE USE MADE BY CUSTOMERS OF THE INFORMATION CONTAINED HEREIN IN CONNEXION WITH THEIR PRODUCTS."Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without the express written approval of STMicroelectronics.The ST logo is a registered trademark of STMicroelectronics©1998 STMicroelectronics - All Rights Reserved.Purchase of I2C Components by STMicroelectronics conveys a license under the Philips I2C Patent. Rights to use these components in an I2C system is granted provided that the system conforms to the I2C Standard Specification as defined by Philips.STMicroelectronics Group of CompaniesAustralia - Brazil - Canada - China - France - Germany - Italy - Japan - Korea - Malaysia - Malta - Mexico - Morocco - The Netherlands - Singapore - Spain - Sweden - Switzerland - Taiwan - Thailand - United Kingdom - U.S.A.12/12。