参赛注意事项

(1)2003年9月15日8:00竞赛正式开始,每支参赛队限定在提供的A、B、C、D、E、F题中任选一题;认真填写《登记表》各栏目内容,填写好的《登记表》由赛场巡视员暂时保存。

(2)参赛者必须是有正式学籍的全日制在校本、专科学生,应出示能够证明参赛者学生身份的有效证件(如学生证)随时备查。

(3)每队严格限制3人,开赛后不得中途更换队员。

(4)竞赛期间,可使用各种图书资料和网络资源,但不得在学校指定竞赛场地外进行设计制作,不得以任何方式与他人交流,包括教师在内的非参赛队员必须迴避,对违纪参赛队取消评审资格。

简易逻辑分析仪(D题)

一、任务

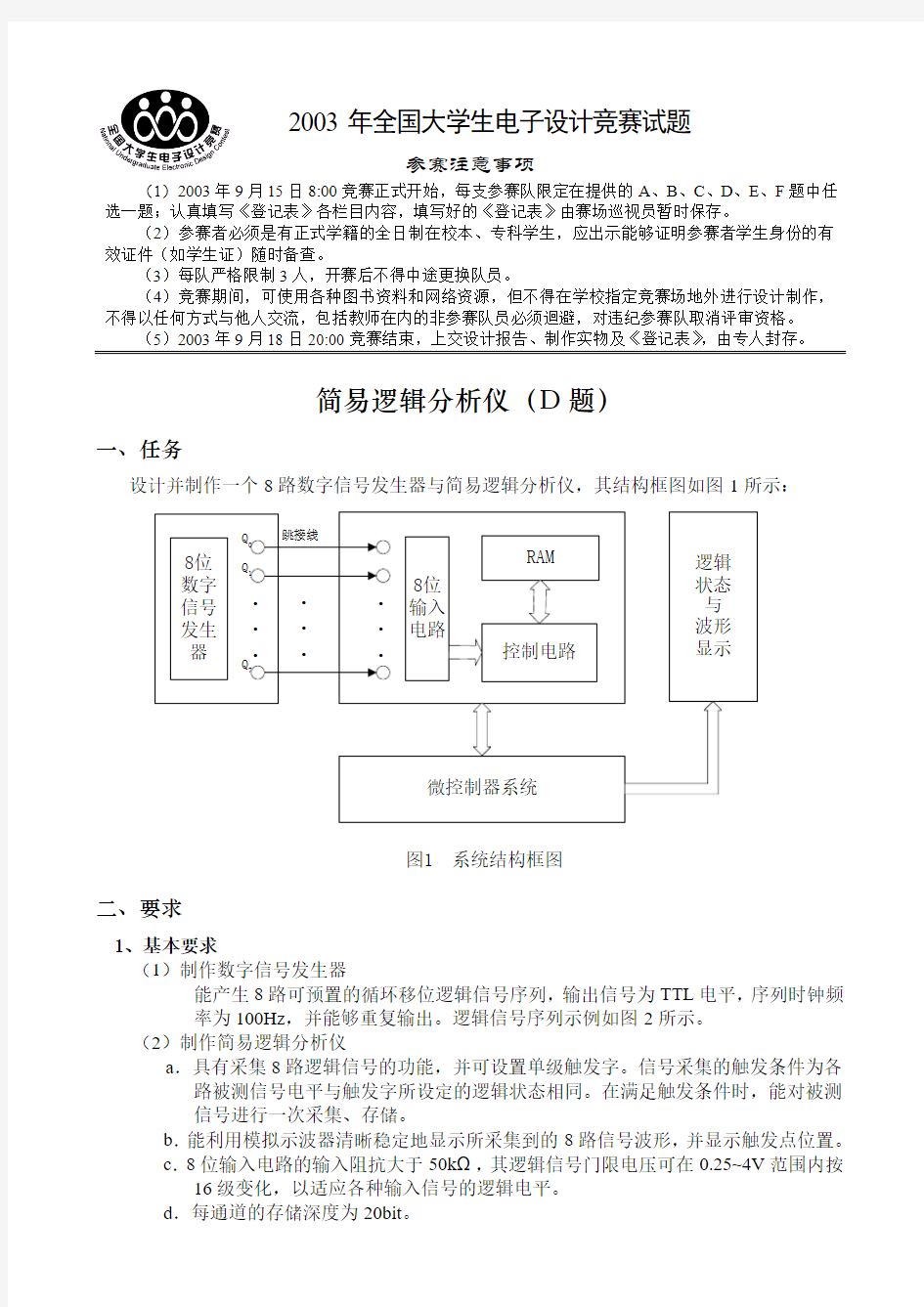

设计并制作一个8路数字信号发生器与简易逻辑分析仪,其结构框图如图1所示:

图1 系统结构框图

二、要求

1、基本要求

(1)制作数字信号发生器

能产生8路可预置的循环移位逻辑信号序列,输出信号为TTL电平,序列时钟频

率为100Hz,并能够重复输出。逻辑信号序列示例如图2所示。

(2)制作简易逻辑分析仪

a.具有采集8路逻辑信号的功能,并可设置单级触发字。信号采集的触发条件为各路被测信号电平与触发字所设定的逻辑状态相同。在满足触发条件时,能对被测

信号进行一次采集、存储。

b.能利用模拟示波器清晰稳定地显示所采集到的8路信号波形,并显示触发点位置。

c.8位输入电路的输入阻抗大于50kΩ,其逻辑信号门限电压可在0.25~4V范围内按16级变化,以适应各种输入信号的逻辑电平。

d.每通道的存储深度为20bit。

Q 0Q 1Q 7Q 6Q 5Q 4Q 3Q 2

clock

2.发挥部分

(1)能在示波器上显示可移动的时间标志线,并采用LED 或其它方式显示时间标志线

所对应时刻的8路输入信号逻辑状态。

(2)简易逻辑分析仪应具备3级逻辑状态分析触发功能,即当连续依次捕捉到设定的3

个触发字时,开始对被测信号进行一次采集、存储与显示,并显示触发点位置。3级触发字可任意设定(例如:在8路信号中指定连续依次捕捉到两路信号11、01、00作为三级触发状态字)。

(3)触发位置可调(即可选择显示触发前、后所保存的逻辑状态字数)。 (4)其它(如增加存储深度后分页显示等)。

三、评分标准

四、说明

1、系统结构框图中的跳接线必须采取可灵活改变的接插方式。

2、数字信号的采集时钟可采用来自数字信号发生器的时钟脉冲clock 。

3、测试开始后,参赛者不能对示波器进行任何调整操作。

4、题中涉及的“字”均为多位逻辑状态。如图2中纵向第一个字为一个8位逻辑状态字(00000101),而发挥部分中的3级触发字为2位逻辑状态。

图2 重复输出循环移位逻辑序列00000101

第六届全国大学生结构设计竞赛赛题 1.命题背景 吊脚楼是我国传统山地民居中的典型形式。这种建筑依山就势,因地制宜,在今天仍然具有极强的适应性和顽强的生命力。这些建筑既是我中华民族久远历史文化传承的象征,也是我们的先辈们巧夺天工的聪明智慧和经验技能的充分体现。 重庆地区位于三峡库区,旧式民居中吊脚楼建筑比比皆是。近年来的工程实践和科学研究表明,这类建筑易于遭受到地震、大雨诱发泥石流、滑坡等地质灾害而发生破坏。自然灾害是这种建筑的天敌。 相对于地震、火灾等灾害而言,重庆地区由于地形地貌特征的影响,出现泥石流、滑坡等地质灾害的频率更大。因此,如何提高吊脚楼建筑抵抗这些地质灾害的能力,是工程师们应该想方设法去解决的问题。本次结构设计竞赛以吊脚楼建筑抵抗泥石流、滑坡等地质灾害为题目,具有重要的现实意义和工程针对性。 2.赛题概述 本次竞赛的题目考虑到可操作性,以质量球模拟泥石流或山体滑坡,撞击一个四层的吊脚楼框架结构模型的一层楼面,如图2.1所示。四层吊脚楼框架结构模型由参赛各队在规定的时间内现场完成。模型各层楼面系统承受的竖向荷载由附加配重钢板实现。主办方提供器材将模型与加载装置连接固定(加载台座倾角均为o 30θ=),并提供统一的测量工具对模型的性能进行测试。 图2.1.第六届全国大学生结构设计竞赛赛题简图 配重1M 配重2M 配重2M 后固定板 前撞击板 螺杆 钢底座 钢架A 钢架B 不锈钢半圆滑槽 模型部分(含部分加载装置) 加载台座 θ θ 加速度传感器 螺杆 硬橡胶

3.模型要求 图3.1.模型要求示意图 图 3.1模型设计参数取值表 q o 30 0L 20cm > —— H 1cm 99± L < 24cm —— q 配重1M 配重2M 配重2M 前撞击板 后固定板 底板 模型平面尺寸要求示意图 要求平整,且与前撞击板端头有效接触面积不小于22cm 要求平整,且与后固定板端头有效接触面积不小于22cm 底板示意图 允许固定区域 硬橡胶

第二届“中联杯”全国大学生建筑设计方案竞赛获奖结果公告为了繁荣建筑创作,提高建筑专业大学生的设计能力和综合素质,促进青年人才的成长,中国建筑学会与全国高等学校建筑学专业指导委员会、中国联合工程公司在去年成功举办第一届“中联一等奖 杯”全国大学生建筑设计方案竞赛的基础上,今年举办的第二届“中联杯”全国大学生建筑设计方案竞赛又创出佳绩。本次竞赛至2010年10月20日截稿之日,共收到包括香港地区在内的全国26个省、自治区、直辖市100多所高校报送的746项作品,创近年来新高。 第二届中联杯评选工作于2010年12月23日在杭州进行,评审委员会由中国工程院院士何镜堂,全国建筑设计大师韩光宗、何玉如、郭明卓,中国建筑学会秘书长周畅,全国高校建筑学科专业指导委员会主任仲德崑,以及清华大学、同济大学、哈尔滨工业大学、天津大学、重庆大学、西安建筑科技大学等著名院校建筑学院的院长、副院长等十三位专家组成,何镜堂院士任评审工作委员会主任。评审工作自始至终坚持“公开、公正和公平”的评选原则,通过评委会多轮的投票筛选,共选出107项入围作品,其中包括一等奖2项,二等奖5项,三等奖10项以及优秀奖90项。对于此次参赛作品的综合水平,评委们给予了极高的评价,不论是从参赛数量还是作品质量,相对于去年都有了一个较大的提升。以“我的城市,我的明天”为主题的746份作品,以不同的创作手段,不同的表现方式,体现出年轻设计者对中国城市发展中的焦点问题的关注,同时也具有一定的探索未来的意义。对于今年部分作品中体现的环保与绿色建筑的思想,也反映了我国建筑教育的一大进步。对于“中联杯”的两次成功举办,评委们给予了很高的肯定与期望,希望它能成为建筑学大学生的一个“品牌”,成为学生放飞思想、释放创意的一个良好平台,为推动建筑学的发展做出贡献。 获奖人员及项目名单详见附件。 附件:第二届“中联杯”全国大学生建筑设计方案竞赛获奖结果 中国建筑学会 中国联合工程公司011年1月30日

数学与统计学院 第三届计算机程序设计竞赛题 竞赛需知: 1、答案必须写在答题纸上。 2、程序采用C/JAVA/VB/VFP语言实现均可。 3、考虑到各种因素,程序的键盘输入和结果输出可以用伪代码或者自然语言表示。但是必 须说明输入变量和输出变量。 4、题目最好能用完整、正确的语言程序来解决问题,如确实无法编写完整语言程序的,可 以写出程序主要框架和流程,必要时可以用伪代码或者自然语言描述算法(程序)。 一、玫瑰花数(20分) 如果一个四位数等于它的每一位数的4次方之和,则称为玫瑰花数。例如: + + 1634+ =, 4^4 4^3 4^6 4^1 编程输出所有的玫瑰花数。 #include

int i,j,k; int n; scanf("%d",&n); for(i=0;i Scratch现场赛试题(小学组)小学生Scratch现场编程比赛 试题 小学生Scratch现场编程比赛试题 (小学组制作时间:3个小时) 说明:D盘下有两个文件夹,分别是“机号”和“参考和素材”,请选手把“机号”文件夹名改为自己的机号,如:你的机号是12号,你就把此文件夹改名为“12号”。比赛结束时上传此文件夹到指定位置,确定上传成功后方可离开。 一、试题 (一)基础部分(20分) 说明:打开试题,根据如下要求,继续编写脚本并直接保存试题。(可打开“参考和素材”文件夹,查看四个可执行文件,浏览编写成功后的运行结果。) 第1题:当按下空格键时,小球自动出现在海星身上,然后小球向螃蟹飞去,直到碰到螃蟹时,小球停止运动。 第2题:当“计算”按钮被单击时,能够计算长方形的面积,并把结果显示在舞台上。 第3题:当“上一张”按钮被单击时,背景图片切换到上一张。当“下一张”按钮被单击时,背景图片切换到下一张。 第4题:当绿旗被点击时,角色“鱼”在舞台上从左边向右边游动并自动不断循环。 (二)创作部分(80分) 选手从下述3个主题中任选一个主题 ....进行创作,每个主题都提供相应的图片素材供选择。创作类别可选动画、故事、演示类、互动、游戏类中任何一种。如果时间有余,选手可以完成其它主题创作,酌情加分。(图片素材在“参考和素材”文件夹中) 主题1:寓言故事《乌鸦喝水》 主题2:遵守交通规则 主题3:保护野生动物 2.作品保存 作品完成后,在机号文件夹中以“机号+主题号”保存,如:你的机号是12号,你要保存主题2的作品,以“12号2”为文件名保存,扩展名默认。再根据自己的创作,填写“12号”文件夹中的“作品说明文档”并直接进行保存。 二、评价指标 ●思想性: 简易逻辑分析仪 摘要 本系统是由单片机作为主控制器、可编程器件作为辅助控制单元来实现数字信号产生、逻辑信号采集和示波器显示。 由单片机为核心的信号发生器,实现了大范围可控频率、预设码型的信号输出;数据采集模块的输入电路中的程控迟滞比较器,提高了输入信道的抗干扰能力。可编程器件高密度特点在本系统中的应用,大大减少了外围器件,增强了系统的可靠性。带有LCD显示模块为用户控制提供友好的人机界面,实现了设置掉电保护功能,并支持鼠标操作和图形打印。 关键词逻辑分析仪单片机可编程器件程控迟滞比较器一、方案论证及选择 方案一: 利用普通的74系列移位计数器构成数字信号发生器,纯单片机方式实现逻辑分析仪。 图 1-1 方案一结构框图 如图1-1所示,数字信号发生器部分,利用74系列的移位计数器的基本功能,通过拨码开关向置数端预置循环序列,通过TTL 驱动输出数字信号。逻辑分析仪部分的门限电压由电位器控制。这种方法单片机除了完成基本的数据分析外,还需要完成对逻辑数据的采集、存储、显示等大量控制工作。 方案二: 由单片机产生数字信号序列,由另外两片单片机构成逻辑分析仪。 射随器 门限 比较器 电位器 调压电路 单 片 机 Z Y X D/A D/A 预 置 拨码开关 序列 输出 数字信号发生器 简易逻辑分析 100Hz 时钟 键盘 级联74 移位计数器 数码管 图 1-2 方案二结构框图 如图1-2所示,相比方案一在信号产生上方案二采用了单片机方案,数码管显示循环序列码状态,本方案用软件可以实现不同频率、更加复杂数字信号的输出。在逻辑分析仪部分,部分的特点是双单片机结构,二者通过串口通信,下位机单片机3只负责显示,上位机单片机2通过D/A 输出程控的门限电平。本方案解决了显示与数据采集处理不能同时工作的矛盾, 方案三 利用FPGA/CPLD 的高速特点,实现系统并行工作,这是本方案相比于方案二的特色之一。用可编程器件可以高速完成单一功能模块。FPGA/CPLD 的使用弥补了单片机在高速采集和实时显示的弱点,使整个系统的处理能力远超过当前微控制器的水平,这使设计十分具有发挥的空间。而且通过合理地划分软硬件的工作量,将使软件控制和软件编写变得容易。 单 片 机 2 单 片 机 3 单 片 机 1 输出级TTL 驱动 射随器 D/A 门限 比较器 串口 通信 Z Y X D/A D/A 数码管 键盘 数字信号发生简易逻辑分析 键盘 数码管 第十届全国大学生结构设计竞赛赛题 大跨度屋盖结构 随着国民经济的高速发展和综合国力的提高,我国大跨度结构的技术水平也得到了长足的进步,正在赶超国际先进水平。改革开放以来,大跨度结构的社会 需求和工程应用逐年增加,在各种大型体育场馆、剧院、会议展览中心、机场候机楼、铁路旅客站及各类工业厂房等建筑中得到了广泛的应用。借北京成功举办2008奥运会、申办2022冬奥会等国家重大活动的契机,我国已经或即将建成一大 批高标准、高规格的体育场馆、会议展览馆、机场航站楼等社会公共建筑,这给我国大跨度结构的进一步发展带来了良好的契机,同时也对我国大跨度结构技术水平提出了更高的要求。 2总体模型 总体模型由承台板、支承结构、屋盖三部分组成(图-1) 加载区域 图-1模型三维透视示意简图 2.1承台板 承台板采用优质竹集成板材,标准尺寸1200mm>800mm,厚度16mm,柱 底平面轴网尺寸为900mm>600mm,板面刻设各限定尺寸的界限: (1)内框线:平面净尺寸界限,850mr> 550mm; (2) 中框线:柱底平面轴网(屋盖最小边界投影)尺寸, (3) 外框线:屋盖最大边界投影尺寸, 1050mm X750mm 承台板板面标高定义为土 0.00。 2.2支承结构 仅允许在4个柱位处设柱(图-2中阴影区域),其余位置不得设柱。柱的任 何部分(包括柱脚、肋等)必须在平面净尺寸(850mmx 550mm )之外,且满足 空间检测要求。(即要求柱设置于四角175mm 125mm 范围内。) 柱顶标高不超过+0.425 (允许误差+5mm ),柱轴线间范围内+0.300标高以 下不能设置支撑,柱脚与承台板的连接采用胶水粘结。 2.3屋盖结构 屋盖结构的具体形式不限,屋盖结构的总高度不大于 125mm (允许误差 +5mm ),即其最低处标高不得低于0.300m ,最高处标高不超过0.425m (允许误 差 +5mm )。 平面净尺寸范围(850mmx 550mm )内屋盖净空不低于300mm ,屋盖结构 覆盖面积(水平投影面积)不小于900X300mm ,也不大于1050X750mm ,见图-3。 不需制作屋面。 屋盖结 构覆盖面积(水平投 影面积)不小于900>600mm ,也不大于 1050X750m m 。但不限定屋盖平面尺寸是矩形,也不限定边界是直线。 屋盖结构中心点(轴网900X300mm 的中心)为挠度测量点。 2.4剖面尺寸要求 模型高度方向的尺寸以承台板面标高为基准,尺寸详见图 -4、5。 900mm >600mm ; (I ; ② 图-2承台板平面尺寸图 、柱脚内界 口 g □ Trfrii?尺寸范应 (85Gi550} 〔柱脚不睜进入谀范 柱位 12UW 基于单片机的简易逻辑分析仪 目录 第1节引言 (3) 1.1系统概述 (3) 1.1.1系统的特点 (4) 1.1.2系统的功能 (4) 第2节系统主要硬件电路设计 (5) 2.1 系统结构框图 (5) 2.2 主体控制模块 (5) 2.3 系统硬件的主体实现 (7) 2.3.1 数字信号发生器模块的电路设计与实现 (7) 2.3.2 主控系统模块的电路设计与实现 (8) 2.3.3 LED显示模块的电路设计与实现 (10) 2.3.4 硬件的抗干扰措施 (12) 第3节系统软件设计 (13) 3.1 系统软件流程 (13) 3.2 中断服务子程序 (15) 3.3 AT24C04程序设计 (15) 第4节结束语 (19) 参考文献 (20) 基于单片机的简易逻辑分析仪 第1节引言 信息时代是数字化的时代,数字技术的高速发展,出现了以高性能计算机为核心的数字通信、数字测量的数字系统。在研究这些数字系统产品的应用性能的同时也必须研究在设计、生产和维修他们的过程中,如何验证数字电路设计的合理性、如何协调硬件及其驱动应用软件的工作、如何测量其技术指标以及如何评价其性能。逻辑分析仪的出现,为解决这些问题提供了可能。 随着数字系统复杂程序的增加,尤其是微处理器的高速发展,用示波器测试己显得有些无能为力。1973年在美国应运而生的逻辑分析仪(Logic Analyzer),能满足数字域测试的各种要求。它属于总线分析仪一类的数据域测试仪器*主要用于查找总线(或多线)相关故障.同时对于数据有很强的选择能力和跟踪能力,因此,逻辑分析汉在数字系统的测试中获得了广泛的应用。 逻辑分析仪(Logic Analyzer)是以逻辑信号为分析对象的测量仪器。是一种数据域仪器,其作用相当于时域测量中的示波器。正如在模拟电路错误分析中需要示波器一样,在数字电路故障分析中也需要一种仪器,它适应了数字化技术的要求,是数字、逻辑电路、仪器、设备的设计、分析及故障诊断工作中不可按少的工具。在测试数字电路、研制和维修电子计算机、微处理器以及各种集成化数字仪表和装置中具有广泛的用途;还是数字系统设计、侦错、软件开发和仿真的必备仪器;作为硬件设计中必不可少的检测工具,还可将其引入实验教学中,建立直观感性的印象,提升学生的硬件设计能力,可以全面提高教学质量;随着科技的发展,LA在多通道、大存储量、高采样速率、多触发功能方面得到更快的发展,在航天、军事、通信等数字系统领域得到越来越广泛的应用。 我们从上面可以看出逻辑分析仪在各个领域的广泛应用。那么我们在学习、应用的同时设计并制作一个简易的逻辑分析仪就显的意义重大了,这样这个过程既可以让我们更加深入理解其原理,又可以提高动手设计并制作整个系统电路的能力,还可以将其作为简易仪器应用于以后的实验中。 1.1系统概述 因在本节中,我们将对简易逻辑分析仪的应用进行分析。给出它的特点,能实现的功能以及系统的简单操作 1.1.1 系统的特点 逻辑分析仪也称逻辑示波器,它是用来分析数字系统逻辑关系的一种仪器。逻辑分析仪的主要作用有二个:一是用于观察的形式显示出数字系统的运行情况,相当于扩展了人们的视野,起一个逻辑显示器的作用;二是对系统运行进行分析和故障诊断。 第五届全国大学生结构设计竞赛总结 (技术版) 黄祖慰20080537 5th国赛的作品,是总结了4th国赛的失败教训,以降低模型量为重点的模型设计和制作成果。我们通过不懈努力,终于到达了目标。在这次比赛中,我们研究出了一些先进的模型设计和制作技巧和积累了更多的设计和制作的经验。在此,我将通过模型从无到有的整个过程进行具体的介绍。 一、研读赛题 读懂题目在结构设计竞赛中是一个最基本的要求,要做到对赛题的点点滴滴熟记于心,并且从规则中发掘模型设计的切入点。 要想获得大奖,就要对题目认真分析;努力寻找漏洞显得相当重要,是一条迈向成功的捷径。在本次结构设计竞赛模型中,整体铁块,虚悬挑梁等都是针对题目漏洞而设计的,为模型重量的减轻做出了重要贡献。 二、准备制作工具 所谓公欲善其事必先利其器,要想做好一个模型,一套好的工具是必须的。在制作模型初期,选手可以采用非比赛指定工具来制作模型。虽然赛题中已经明确规定了制作工具,但是由于提供工具的局限性,有些很好的想法不能够在模型上做出来。我的建议是,先使用的工具,把想法尽可能表现出来,等到模型初步定型后,再使用比赛指定工具,寻求达到同样效果的模型的制作 方法。为了提高制作精度,画线笔可采用0.38mm的水笔。 三、研究材料特性 所谓知自知彼方能百战不殆,在制作模型之前,必须先对材料进行分析,了解材料的特性,由此得知材料的实际力学性质和可加工性质。下面我就罗列我对本次比赛的复压竹皮、竹制底板和502胶水的性质研究的一些心得: 1、复压竹皮在顺纹路方向存在连续纤维,利于受拉。但是顺 纹容易被撕裂。 2、规格为0.2mm的竹皮为单层竹皮,应注意竹皮上存在的 竹节的薄弱点,应尽量避开;此种竹皮,一面为光面,一面为 毛面,粘贴时,光面的粘接速度要快于毛面,但是最终粘接紧 密性毛面为优。使用单层竹皮作为拉杆,存在风险,北京交通 第七届北京市大学生建筑结构设计竞赛 B组赛组(桥梁方向) 一.题目 北京市自行车专用路跨京藏高速高架桥设计 二.设计资料 (一)工程概况 1.具体交通需求 为解决回龙观地区非机动车出行不便问题,北京市拟建一条自行车专用路。该专用路与京藏高速相交,采用立体交叉形式上跨京藏高速。在京藏高速东西两侧辅路设有人行梯道,保障拟建自行车专用路与现况京藏高速辅路非机动车系统及行人道实现交通跨越。 沿着京藏高速路纵向240米范围内,共有5座跨京藏高速路的高架桥(2座已建,2座待建,1座本桥),跨京藏高架桥作为此区域从北向进京的第一座桥,形成标志。 图2-1-1 拟建高架桥平面图 图2-1-2 拟建高架桥道路纵断面 2.跨越线路需求-京藏高速 京藏高速主路按高速公路标准建设,计算车速为100km/h,双幅路形式,三上三下六车道,中间分隔带宽度2.5m,西侧主路横断面形式为:0.5m路缘带+3×3.75m车行道+3m硬路肩(含0.5m路缘带)+0.75m土路肩,宽度为15.5m。京藏高速辅路在主路两侧布置,为单向3车道,横断面形式为1.0m检修步道+0.25m路缘带+3×3.25m机动车道+2.5m非机动车道 +1.5m人行道。 道路等级、规划红线、规划断面、节点形式等见下表: 图2 拟跨越线路具体情况 (二)拟建场地工程地质条件 1 地形、地貌及地物概述 本工程场地地貌属温榆河冲洪积扇的中部。地形较平坦,钻孔地面标高在 42.64~44.88m 之间。 根据本次钻探野外描述、原位测试及室内土工试验成果,按土的岩性及工程特性将地层划分为 11 大层,其中①层土为人工填土层,②~?层土为第四纪沉积土层。 现自上而下分述如下: 2.2.1 人工填土层 a.素填土①:黄褐色,稍湿~湿,稍密,具中压缩性。主要成分为粉质黏土、粉土,含少量砖渣、碎石。本层厚度为 0.70~4.00m,层底标高为 40.71~43.21m。 b.杂填土①1:杂色,稍湿,松散~稍密。主要由砖块、灰渣、碎石等组成。本层厚度为 0.30~4.00m。 2.2.2 第四纪沉积土层 a.粉土②:褐黄色,稍湿~湿,中密~密实。含云母片、氧化铁条纹,夹粉质黏土②1、黏土②2 薄层或透镜体。本层厚度为 2.00~6.20m,层底标高为 36.57~ 39.89m。 b.粉质黏土②1:褐黄色,可塑,具中压缩性~高压缩性。含氧化铁条纹。本层厚度为 0.40~2.70m。 c.黏土②2:褐黄色,可塑,局部软塑,具中压缩性~高压缩性。含氧化铁条纹。本层厚 本科生毕业设计报告学院物理与电子工程学院专业电子信息工程 设计题目:基于51单片机的 简易逻辑分析仪设计 学生姓名 指导教师 (姓名及职称) 班级 学号 完成日期:年月 基于51单片机的简易逻辑分析仪设计 物理与电子工程学院电子信息工程 [摘要]本设计完成了一种能进行数字电路中多路数据测试的简易逻辑分析仪。它以51单片机控制核心,数模转换器为逻辑信号门限电平控制电路,用按键和 12864LCD作为人机交互界面,采用C51进行模块化编程,实现了四路信号的测试,具有成本低,使用方便等特点。 [关键词]数字电路单片机数模转换器逻辑分析仪 1 设计任务与要求 本设计的主要任务及参数指标是:数据位数4位,存储深度80字;数据速率最高1kHz;输入阻抗大于50kΩ;逻辑信号门限电平在1.0V~4.0V 范围内按8级任意设定。 2 设计方案 本系统采用51单片机为控制核心,系统由单片机系统、逻辑电平控制、按键、LCD显示、系统电源等模块构成。被测数据输入到逻辑电平控制模块,然后进行单片机进行测试,按键用于控制逻辑信号门限电平的大小,系统电源为各模块供电,各模块的供电电压为5V。 图1 系统框图 3 设计原理分析 3.1 单片机系统电路设计 图2 单片机系统电路 单片机系统为逻辑分析仪的核心,负责控制逻辑分析仪的逻辑电平、检测按键并驱动LCD 进行显示。单片机系统电路如图2所示,由晶体振荡器Y1、电容C3和C4构成振荡器电路,为单片机提供时钟信号。电容C1、电阻R2和R1、按键KEY1构成单片机复位电路,高电平复位,当按键KEY1按下的时间超过2个机器周期以上时,单片机就执行复位操作。EA 接高电平,单片机首先访问内部程序存储器。J1为1KΩ的排阻,作为P0口的外部上拉电阻。在硬件制作时为了方便单片机的测试和功能的扩展,把所有的I/O 口均通过排针引出。 EA/VP 31X119X218RESET 9 RD 17WR 16 INT012INT113T014T115P101P112P123P134P145P156P167P178P0039P0138P0237P0336P0435P0534P0633P0732P2021P2122P2223P2324P2425P2526P2627P27 28 PSEN 29 ALE/P 30TXD 11RXD 10U18051 P10 P11P12P13P14P15P16P17P00P01P02P03P04P05P06P07P20P21P22P23P24P25P26P27 123456789J1 1K +5 Y112M +5 RXD TXD RD WR T0T1INT0INT1C3 22p F C4 22p F R28.2K C110u F +5 12J6CON2 KEY1SW2 R1100 . . 安阳工学院电子信息与电气工程学院 《EDA技术》课程大作业 题目:简易逻辑分析仪 班级: 2011级电子信息工程一班 评分标准: 1、题目难易度。 10% 2、设计和结论正确,分析清晰合理。 40% 3、大作业报告阐述清晰,格式规范。 20% 4、陈述清晰,回答问题正确。 30% 大作业成绩 总成绩=T+J*40%+(J+J*(X-1/N))*30% T为回答问题成绩,J为教师成绩,X为学生自评分值,N为小组人数 简易逻辑分析仪 1. 设计任务 逻辑分析仪可以将数字系统中的脉冲信号、逻辑控制信号、总线数据甚至毛刺脉冲都能同步高速的采集进该仪中的高速RAM中暂存,以备显示和分析。我们所设计的简易逻辑分析仪是一个8通道的逻辑数据采集电路,它可以将输入到RAM中的计数结果通过输出线完整地按地址输出出来,其中CLK(时钟信号),CLK_EN(时钟使能信号),CLR(清零端),WREN(写入允许控制)和DIN(7..0)(写入允许控制),OUTPUT(八位数据输出)。预期可以将输入到简易逻辑分析仪中的数据可以完整的读取出来。 2.设计方案 我们所设计的简易逻辑分析仪主要有三个功能模块构成:一个8位LMP_RAM0,存储1024个字节,有十根地址线;一个十位计数器LMP_COUNTER和一个锁存器74244。设计思路框图如下图一: 图一设计思路框图 3. 方案实施 3.1、LPM计数器模块的设计 首先打开一个原理图编辑窗,存盘取名为 eda1,然后建成工程,在进入本工程的原理图,单击Mega Wizard Plug-In Manger 管理器按钮,然后进入如图二所示的窗口,选择LPM-COUNTER模块,再选择CycloneⅢ和VHDL;文件名为CONT10B。 Problem A: 序列的混乱程度 Time limit:1s Memory limit:128MB Description 有一个长度为n的正整数序列,一个序列的混乱程度定义为这个序列的最大值和最小值之差。请编写一个程序,计算一个序列的混乱程度。 Input 输入的第一行为一个正整数T(T<=1000),表示一共有T组测试数据。 每组测试数据的第一行为一个正整数n(1<=n<=1000),代表这个序列的长度。第二行为n 个正整数,代表这个序列。序列中元素的大小不会超过1000。 Output 对于每个测试数据,输出一行包含一个正整数,代表对应序列的混乱程度。 Sample Input 2 5 1 2 3 4 5 5 1 9 2 4 8 Sample Output 4 8 Problem B: 随机数 Time limit:1s Memory limit:128MB Description 有一个rand(n)的函数,它的作用是产生一个在[0,n)的随机整数。现在有另外一个函数,它的代码如下: int random(int n,int m) { return rand(n)+m; } 显而易见的是函数random(n,m)可以产生任意范围的随机数。现在问题来了,如果我想要产生范围在[a,b)内的一个随机数,那么对应的n,m分别为多少? Input 输入的第一行为一个正整数T(T<=1000),表示一共有T组测试数据。 对于每组测试数据包含两个整数a,b(a<=b)。 Output 对于每组测试数据,输出一行包含两个整数n和m,两个整数中间有一个空格分隔。 Sample Input 2 0 5 1 4 Sample Output 5 0 3 1 简易逻辑分析仪 一、方案论证及选择 1、系统总体框图如下: 整个系统由信号发生器部分、信号调理部分、ARM软件控制部分以及输出显示部分组成。 2、数字信号发生器模块 方案一:采用555定时器和可预置移位寄存器。用两片74LS194A接成8位可预置循环移位寄存器,方波发生器提供一时钟信号给移位寄存器,预置数用8个按键接入(即循环序列),此方案简单可靠。 方案二:用PC 通过软件编程可以从并行口输出信号波形,不需要硬件电路,且设计灵活,但是不适合电子设计竞赛,并且PC体积大,携带不方便。 方案三:采用中规模FPGA,使用VHDL语言设计移位寄存器。此方案可以实现精确定时产生信号,且信号频率可调,体积小, 但其显示电路占用资源多,这样设计出来的电路系统将大且复杂。 方案四:采用一片AT89C2051单片产生波形序列。用单片机产生数字信号,设计简单,设置灵活,频率调节方便。 综合分析上述各方案,比较其优缺点,本系统有其固定的频率要求,故选用最简单的方案一。 3、门限电压分级部分 方案一、采用单片机软件控制分级输出不同的电压值,给到比较器的反相端。该方案简单、且输出电压精确。 方案二、用单片机产生一路PWM波,再经过两级RC低通滤波可得到直流电压,通过控制PWM波的占空比来改变电压值,达到分级效果。该方案RC滤波得到的电压不稳定,且有纹波。 方案三、直流电源供5V电压,采用电阻、电位器进行一级一级的分压,以实现分级效果。该方案电路复杂,且电位器调节比较难。 方案四、采用数字式电位器,由单片机结合相应的外围电路进行控制,以实现分压。采用程控方式,得到的电压精确且稳定。 鉴于本系统软件程序较多,ARM内部仅两个DA,故选择方案四以避免使用单片机内部DA。 二、硬件部分单元电路 1、数字信号发生器电路 该部分采用了555定时器产生一定频率的时钟信号,通过改变滑动变阻器阻值可实现频率在一定范围内可变,定时器后接一个非门以增强后级驱动能力。定时器产生的方波信号作为双向移位寄存器74LS194的输入时钟,利用74LS194的两个控制端(S0,S1)来产生八路可预置的循环移位逻辑信号序列。当按键SW2按下时,74LS194将按键的逻辑状态输入移位寄存器,送入移位寄存器的这组数值便在时钟的控制下循环移位。 2、信号调理部分 由移位寄存器产生的逻辑信号经过电压比较器LM339,与一可调门限电压进行比较,并输出TTL逻辑电平。这些电平信号输入到单片机与用户自己设置的触发状态字进行比较进而输出题目要求采集的信号。由于LM339输出的信号电平为5V,而单片机可承受的电压最大为3.3V,故需在LM339后进行光耦隔离以防止外部设备给过大的电流给单片机,同时也达到降压的效果。 word文档整理分享 本科生毕业设计报告学院物理与电子工程学院专业电子信息工程 设计题目:基于51单片机的 简易逻辑分析仪设计 学生姓名 指导教师 (姓名及职称) 班级 学号 完成日期:年月 基于51单片机的简易逻辑分析仪设计 物理与电子工程学院电子信息工程 [摘要]本设计完成了一种能进行数字电路中多路数据测试的简易逻辑分析仪。它以51单片机控制核心,数模转换器为逻辑信号门限电平控制电路,用按键和 12864LCD作为人机交互界面,采用C51进行模块化编程,实现了四路信号的测试,具有成本低,使用方便等特点。 [关键词]数字电路单片机数模转换器逻辑分析仪 1 设计任务与要求 本设计的主要任务及参数指标是:数据位数4位,存储深度80字;数据速率最高1kHz;输入阻抗大于50kΩ;逻辑信号门限电平在1.0V~4.0V 范围内按8级任意设定。 2 设计方案 本系统采用51单片机为控制核心,系统由单片机系统、逻辑电平控制、按键、LCD显示、系统电源等模块构成。被测数据输入到逻辑电平控制模块,然后进行单片机进行测试,按键用于控制逻辑信号门限电平的大小,系统电源为各模块供电,各模块的供电电压为5V。 图1 系统框图 3 设计原理分析 3.1 单片机系统电路设计 图2 单片机系统电路 单片机系统为逻辑分析仪的核心,负责控制逻辑分析仪的逻辑电平、检测按键并驱动LCD 进行显示。单片机系统电路如图2所示,由晶体振荡器Y1、电容C3和C4构成振荡器电路,为单片机提供时钟信号。电容C1、电阻R2和R1、按键KEY1构成单片机复位电路,高电平复位,当按键KEY1按下的时间超过2个机器周期以上时,单片机就执行复位操作。EA 接高电平,单片机首先访问内部程序存储器。J1为1KΩ的排阻,作为P0口的外部上拉电阻。在硬件制作时为了方便单片机的测试和功能的扩展,把所有的I/O 口均通过排针引出。 EA/VP 31X119X218RESET 9 RD 17WR 16 INT012INT113T014T115P101P112P123P134P145P156P167P178P0039P0138P0237P0336P0435P0534P0633P0732P2021P2122P2223P2324P2425P2526P2627P27 28 PSEN 29 ALE/P 30TXD 11RXD 10U18051 P10 P11P12P13P14P15P16P17P00P01P02P03P04P05P06P07P20P21P22P23P24P25P26P27 123456789J1 1K +5 Y112M +5 RXD TXD RD WR T0T1INT0INT1C3 22p F C4 22p F R28.2K C110u F +5 12J6CON2 KEY1SW2 R1100 . . 2019年大学生程序设计大赛策划书 一、活动名主题 “华为”杯程序设计大赛 二、举办单位 策划主办单位:华为技术有限公司 协办单位:(排名不分先后)华中科技大学、武汉大学、武汉理工大学 三、活动时间 20xx年x月x日-x月xx日 四、参赛资格 ●本次大赛面向武汉三所目标高校在校全日制本科及以上学历学生(毕业时间在20xx年x月xx日之后)。 ●初赛以个人为单位,性别、专业不限;预计800人; ●在华为官方的网站注册报名,报名成功后获得参赛资格,只有在报名期间进行网上注册后才能参与比赛。 五、竞赛流程 第一阶段:报名参赛(5月10日—5月24日) l参赛选手阅读参赛注意事项,确认协议内容,在华为官方的 网站上注册简历,获得参赛资格的选手以个人身份参赛。 第二阶段:初赛(6月1日8:00—6月1日12:00) l网吧集中测试(集中招聘机试流程) 1.5月30日18:00前,通过邮件、短信和电话的形式通知通过简历筛选的学生初赛场地、机试场次、时间、所需证件及注意事项; 2.1日当天,学生凭身份证刷卡签到,并获取自己的登录账号 与密码。 3.学生按安排的批次进行入座考试,机试全程为30分钟,逾时将视为不及格。全程考试属封闭式测试,不得翻阅网页及手机,完全独立完成整个测试过程。一旦发现翻阅行为,一律视为作弊,将会被取消参赛资格。 4.考试成绩按照答案正确率与用时两个维度进行评价,在追求准确的同时对学生们的编程效率也作出了要求。 第三阶段:软件训练营(6月2日9:00—6月2日16:00) l1日晚将通过邮件、短信与电话的形式,邀请通过初赛的18 位学生参加为期6个小时的软件训练营-敏捷开发的训练课程,本课程主要是针对学生编程思维进行的引导式更新,课程内容比较灵活多变,动手环节较多,较有吸引力。 l中午学生将统一在华为A2食堂进行就餐。 l完成培训的学生将会收到华为武研所办法的“敏捷技能拥有者”的荣誉证书和决赛工具包(题目+小贴士+输出文件)。 l培训后,同学将会自主组成6个三人组进行接下来的决赛。每两个三人组将会由一位导师(业务部门提供的业务骨干)进行指导, 基于单片机的简易逻辑分析仪毕业设计论文 目录 第1节引言 (3) 1.1系统概述 (3) 1.1.1系统的特点 (4) 1.1.2系统的功能 (4) 第2节系统主要硬件电路设计 (5) 2.1 系统结构框图 (5) 2.2 主体控制模块 (5) 2.3 系统硬件的主体实现 (7) 2.3.1 数字信号发生器模块的电路设计与实现 (7) 2.3.2 主控系统模块的电路设计与实现 (8) 2.3.3 LED显示模块的电路设计与实现 (10) 2.3.4 硬件的抗干扰措施 (12) 第3节系统软件设计 (13) 3.1 系统软件流程 (13) 3.2 中断服务子程序 (15) 3.3 AT24C04程序设计 (15) 第4节结束语 (19) 参考文献 (20) 基于单片机的简易逻辑分析仪 第1节引言 信息时代是数字化的时代,数字技术的高速发展,出现了以高性能计算机为核心的数字通信、数字测量的数字系统。在研究这些数字系统产品的应用性能的同时也必须研究在设计、生产和维修他们的过程中,如何验证数字电路设计的合理性、如何协调硬件及其驱动应用软件的工作、如何测量其技术指标以及如何评价其性能。逻辑分析仪的出现,为解决这些问题提供了可能。 随着数字系统复杂程序的增加,尤其是微处理器的高速发展,用示波器测试己显得有些无能为力。1973年在美国应运而生的逻辑分析仪(Logic Analyzer),能满足数字域测试的各种要求。它属于总线分析仪一类的数据域测试仪器*主要用于查找总线(或多线)相关故障.同时对于数据有很强的选择能力和跟踪能力,因此,逻辑分析汉在数字系统的测试中获得了广泛的应用。 逻辑分析仪(Logic Analyzer)是以逻辑信号为分析对象的测量仪器。是一种数据域仪器,其作用相当于时域测量中的示波器。正如在模拟电路错误分析中需要示波器一样,在数字电路故障分析中也需要一种仪器,它适应了数字化技术的要求,是数字、逻辑电路、仪器、设备的设计、分析及故障诊断工作中不可按少的工具。在测试数字电路、研制和维修电子计算机、微处理器以及各种集成化数字仪表和装置中具有广泛的用途;还是数字系统设计、侦错、软件开发和仿真的必备仪器;作为硬件设计中必不可少的检测工具,还可将其引入实验教学中,建立直观感性的印象,提升学生的硬件设计能力,可以全面提高教学质量;随着科技的发展,LA在多通道、大存储量、高采样速率、多触发功能方面得到更快的发展,在航天、军事、通信等数字系统领域得到越来越广泛的应用。 我们从上面可以看出逻辑分析仪在各个领域的广泛应用。那么我们在学习、应用的同时设计并制作一个简易的逻辑分析仪就显的意义重大了,这样这个过程既可以让我们更加深入理解其原理,又可以提高动手设计并制作整个系统电路的能力,还可以将其作为简易仪器应用于以后的实验中。 1.1系统概述 因在本节中,我们将对简易逻辑分析仪的应用进行分析。给出它的特点,能实现的功能以及系统的简单操作 1.1.1 系统的特点 逻辑分析仪也称逻辑示波器,它是用来分析数字系统逻辑关系的一种仪器。逻辑 第三届全国大学生结构设计竞赛 赛题 第三届全国大学生结构设计竞赛委员会 2009.9.24 一、竞赛模型 定向木结构风力发电塔(如图),塔身高800mm,叶片(数量不限)组成的 A A-A 二、模型介绍 1.塔身 塔身为竞赛主结构,需满足以下要求: (1)塔身高800mm,顶点高度实际误差不大于±3mm。塔身外形不影响叶轮运转,塔身水平截面的外轮廓为正多边形或圆形; (2)具有足够的承载能力; (3)具有规定的刚度; (4)与塔顶标准发电机底座连接可靠; (5)与塔底标准底座连接可靠。 2.叶片和叶轮 安装完成后,叶轮外轮廓直径不得大于800mm。 三、装置说明 1.发电机 发电机采用CFX-03型标准发电机,质量4470g,底板及立面详见附图。2.风叶连接件 连接件质量300g,详见附图。 3.发电功率测量系统 发电功率测量系统由导线、负载、功率计组成。导线所受风力不能传递到塔身,由支架承受。 4.鼓风机 相关参数见下表 名称新型节能低噪声轴流风机 型号SF7-4 厂家上海金蓝机电设备成套有限公司 功率3kW 转速1400n/min 风量2500m3/h 风速23m/s 全压力340Pa 经实测,风叶连接件(距鼓风机1m处)的风速参考值如下: 档位风速(m/s) W1 4.0 W2 6.8 W3 9.0 5.塔架安装底盘详见附图。 6.塔脚与安装底盘连接螺栓:重量2g/套。 四、材料及制作工具 1.木材 (1)尺寸:长度1000mm,截面有50mm×1mm、2mm×2mm、2mm×6mm、6mm×6mm; (2)性能参考值:顺纹弹性模量1.0×104MPa,顺纹抗拉强度30MPa。2.胶水:502。 简易逻辑分析仪 摘要 本系统基于逻辑分析仪原理,以AT89C系列单片机为核心,设计制作完成了简易逻辑分析仪。本系统主要由数字信号发生器模块、采集存储和示波器显示模块、人机交互模块三部分组成。基于题目要求,本系统对触发方式、信号采集存储、示波器显示波形和时间标志线、友好的人机界面等功能进行了重点设计。经测试,各项指标均满足基本部分和发挥部分的要求,并且有些指标超出题目要求。 关键字:逻辑分析仪;单片机;液晶 Abstract: Keywords: Signal Oscilloscope;MCU;LCM 1、 总体方案设计 1. 方案比较和选择 方案一:纯FPGA/CPLD(可带IP核)或FPGA/CPLD与单片机结合方式。即由FPGA/CPLD产生数字序列信号,判断单、三级触发信号,设定门限电压,采集、存储、显示被测信号;由IP核实现人机交互及信号测量分析等功能;或由单片机完成IP核实现的功能。此方案优点是速度快、精度高。缺点是软硬件复杂、调试困难、程序不易控制、性价比极低;而且体现不出本方案的优势。 方案二:纯单片机方式。即由多片单片机分别完成数字序列发生器,判断触发信号、数据采集、存储、显示,人机交互、门限电压设定 等功能。优点是操作方便、软件结构清晰、控制灵活、调试容易、性价比较高。本系统对速度的要求不是很高,所以单片机完全能够胜任。 2. 系统设计方案 本系统以三片单片机AT89C51为核心,将设计任务分解为数字信号发生器模块、采集存储和示波器显示模块、人机交互模块三部分。其中核心和关键部分是采集存储和示波器显示模块,另外两个模块起辅助作用。总体系统框图如图1所示。 图1 2、 电路设计与分析 1.可预置的8路数字信号发生器 本模块用于产生8路可预置的重复循环移位逻辑信号序列,输出信号为TTL电平,序列时钟频率为100Hz。输出数字信号如图2示例所示。Scratch现场赛精彩试题(小学组)小学生教育Scratch现场编程比赛

简易逻辑分析仪报告

第十届全国大学生结构设计竞赛赛题

基于单片机的简易逻辑分析仪毕业设计论文

黄祖慰-第五届全国大学生结构设计竞赛总结(技术版)

北京大学生建筑结构设计竞赛

基于51单片机的简易逻辑分析仪设计

简易逻辑分析仪

首届全国中医药院校大学生程序设计竞赛试题

简易逻辑分析仪

基于51单片机的简易逻辑分析仪设计说明书

2019年大学生程序设计大赛策划书

基于单片机的简易逻辑分析仪的毕业设计论文

第三届全国大学生结构设计竞赛

简易逻辑分析仪