EDA技术与VHDL考试试题(可编辑修改word版)

- 格式:docx

- 大小:19.10 KB

- 文档页数:7

EDA技术EDA技术试卷(练习题库)1、个项目的输入输出端口是定义在()。

2、描述项目具有逻辑功能的是()。

3、关键字ARCHITECTURE定义的是。

4、M AXP1USII中编译VHD1源程序时要求()。

5、1987标准的VHD1语言对大小写是()。

6、关于1987标准的VHD1语言中,标识符描述正确的是()。

7、符合1987VHD1标准的标识符是()。

8、VHD1语言中变量定义的位置是()。

9、VHD1语言中信号定义的位置是()。

10、变量是局部量可以写在()。

11、变量和信号的描述正确的是()。

12、关于VHD1数据类型,正确的是()。

13、下面数据中属于实数的是()。

14、下面数据中属于位矢量的是()。

15、可以不必声明而直接引用的数据类型是()。

16、STD_10GIG_1164中定义的高阻是字符()。

17、STD_10GIG」164中字符H定义的是()。

18、使用STD_1OG1G」164使用的数据类型时()。

19、VHD1运算符优先级的说法正确的是()。

20、如果a=1,b=0,则逻辑表达式(aANDb)OR(NOTbANDa)的值是()。

21、不属于顺序语句的是()。

22、正确给变量X赋值的语句是()。

23、EDA的中文含义是()。

24、EPF10K20TC144-4具有多少个管脚()。

25、如果a=1,b=1,则逻辑表达式(aXORb)OR(NOTbANDa)的值是()。

26、MAX+P1USII的,数据类型为std_1ogic_vector,试指出下面那个30、在一个VHD1,数据类型为integer,数据范围0to127,下面哪个赋31、下列那个流程是正确的基于EDA软件的FPGA/CP1D和变量的说法,哪一个是不正确的:()。

33、下列语句中,不属于并行语句的是:()。

34、O在EDA工具中,能将硬件描述语言转换为硬件电路的重要工具软件称为。

35、不是操作符号它只相当与作用〃target=Zb1ank〃>在VHD1的CASE语句中,条件句中的“二>”不是操作符号,它只相当与O作用。

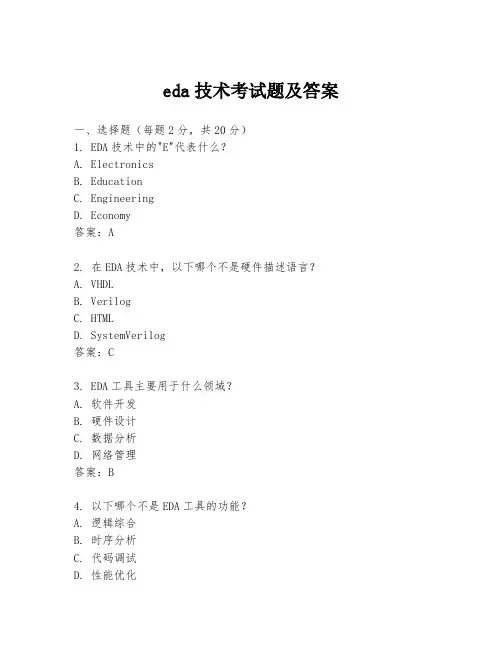

EDA考试题目及答案一、单项选择题(每题2分,共10题)1. EDA技术中,用于描述数字电路的硬件描述语言是:A. VHDLB. VerilogC. C语言D. Python答案:A2. 在VHDL中,用于定义信号的关键字是:A. variableB. constantC. signalD. type答案:C3. 下列哪个不是Verilog中的测试平台(testbench)组件?A. initial块B. always块C. moduleD. function答案:D4. 在EDA设计中,用于模拟电路行为的软件工具是:A. 仿真器B. 编译器C. 综合器D. 布局器答案:A5. 以下哪个选项不是EDA工具的主要功能?A. 电路设计B. 电路仿真C. 电路测试D. 电路维修答案:D6. 在VHDL中,用于实现组合逻辑的构造块是:A. processB. if语句C. case语句D. all of the above答案:D7. Verilog中,用于描述时序逻辑的关键字是:A. alwaysB. initialC. moduleD. assign答案:A8. 在EDA设计流程中,电路综合通常发生在哪个阶段之后?A. 电路设计B. 电路仿真C. 电路测试D. 电路验证答案:B9. 下列哪个不是VHDL中的并发语句?A. ifB. caseC. loopD. procedure答案:D10. 在Verilog中,用于描述模块间连接的关键字是:A. inputB. outputC. wireD. module答案:C二、多项选择题(每题3分,共5题)1. EDA技术可以应用于以下哪些领域?A. 集成电路设计B. 软件工程C. 电子系统设计D. 机械工程答案:A, C2. VHDL中的哪些构造可以用来描述时序逻辑?A. processB. ifC. whileD. after答案:A, D3. 在Verilog中,哪些关键字用于定义模块的端口?A. inputB. outputC. inoutD. module答案:A, B, C4. EDA工具在设计流程中可以提供哪些辅助功能?A. 设计验证B. 设计优化C. 设计转换D. 设计维护答案:A, B, C5. 在EDA设计中,哪些因素会影响电路的性能?A. 电路复杂度B. 电源电压C. 温度变化D. 材料特性答案:A, B, C, D三、简答题(每题5分,共2题)1. 描述一下在EDA设计中,为什么需要进行电路仿真?答案:在EDA设计中,电路仿真是为了在实际制造电路之前,通过软件模拟电路的行为和性能。

一、单项选择题:(20分)1.IP核在EDA技术和开发中具有十分重要的地位;提供用VHDL等硬件描述语言描述的功能块,但不涉及实现该功能块的具体电路的IP核为D 。

A .瘦IP B.固IP C.胖IP D.都不是2.综合是EDA设计流程的关键步骤,在下面对综合的描述中,_________是错误的。

DA.综合就是把抽象设计层次中的一种表示转化成另一种表示的过程;B.综合就是将电路的高级语言转化成低级的,可与FPGA / CPLD的基本结构相映射的网表文件;C.为实现系统的速度、面积、性能的要求,需要对综合加以约束,称为综合约束;D.综合可理解为一种映射过程,并且这种映射关系是唯一的,即综合结果是唯一的。

3.大规模可编程器件主要有FPGA、CPLD两类,下列对FPGA结构与工作原理的描述中,正确的是__C__。

A. FPGA全称为复杂可编程逻辑器件;B. FPGA是基于乘积项结构的可编程逻辑器件;C. 基于SRAM的FPGA器件,在每次上电后必须进行一次配置;D. 在Altera公司生产的器件中,MAX7000系列属FPGA结构。

4.进程中的信号赋值语句,其信号更新是___C____。

A. 按顺序完成;B.比变量更快完成;C.在进程的最后完成;5.VHDL语言是一种结构化设计语言;一个设计实体(电路模块)包括实体与结构体两部分,结构体描述BA.器件外部特性;B. 器件的内部功能;C.器件的综合约束;D.器件外部特性与内部功能。

6.不完整的IF语句,其综合结果可实现AA. 时序逻辑电路B.组合逻辑电C. 双向电路D. 三态控制电路7.子系统设计优化,主要考虑提高资源利用率减少功耗(即面积优化),以及提高运行速度(即速度优化);指出下列哪些方法是面积优化B①流水线设计②资源共享③逻辑优化④串行化⑤寄存器配平⑥关键路径法A. ①③⑤B. ②③④C. ②⑤⑥D. ①④⑥8.下列标识符中,__________是不合法的标识符。

杭州电子科技大学 2005 年 EDA 技术与 VHDL 考试试题1. 大规模可编程器件主要有 FPGA 、CPLD 两类,下列对 CPLD 结构与工作原理的 描述中,正确的是 ________ 。

A. CPLD 是基于 查找表结构的可编程逻辑器件;B. CPLD 即是现场可编程逻辑器件的英文简称;C. 早期的 CPLD 是从 GAL 的结构扩展而来;D. 在 Xilinx 公司生产的器件中, XC9500 系列属 CPLD 结构;2. 综合是 EDA 设计流程的关键步骤,综合就是把抽象设计层次中的一种表示转化 成另一种表示的过程;在下面对综合的描述中, ______________ 是正确的。

A. 综合就是将电路的高级语言转化成低级的,可与 FPGA / CPLD 的基本结构相映射 的网表文件;B. 综合是纯软件的转换过程,与器件硬件结构无关;C. 为实现系统的速度、面积、性能的要求,需要对综合加以约束,称为强制综合。

D.综合可理解为, 将软件描述与给定的硬件结构用电路网表文件表示的映射过程,并且这种映射关系是唯一的; 3. IP 核在EDA 技术和开发中具有十分重要的地位,IP 分软IP 、固IP 、硬IP ;下列所描述的 IP 核中,对于硬 IP 的正确描述为 ____________ 。

A. 提供用 VHDL 等硬件描述语言描述的功能块, 但不涉及实现该功能块的具体电路;B. 提供设计的最总产品 --- 模型库;C. 以网表文件的形式提交用户,完成了综合的功能块;D. 都不是。

4.基于EDA 软件的FPGA / CPLD 设计流程为:原理图/HDL 文本输入 宀 ______________ 宀综合T 适配T ___________ 严 编程下载T 硬件测试。

① 功能仿真 ②时序仿真③逻辑综合 ④配置⑤引脚锁定A . ③ ①B. ⑤ ②C. ④ ⑤D. ①② 5. 下面对利用原理图输入设计方法进行数字电路系统设计,那一种说法是不正确的 ______ 。

1.面向FPGA的开发流程,EDA图形设计输入方法,使EDA工具的设计输入的两种类型?状态图/波形/原理输入;图形输入和硬件描述语言文本输入2.PLD的发展历程?(1)20世纪70年代,熔丝编程的PROM和PLA器件是最早的可编程逻辑器件。

(2)20世纪70年代末,对PLA进行了改进,AMD公司推出了PAL器件。

(3)20世纪80年代初 ,Lattice公司发明电可擦写的,比PAL使用更灵活的GAL器件。

(4)20世纪80年代中期Xilinx公司提出现场可编程概念,同时生产出了世界上第一片FPGA器件。

同一时期,Altera公司推出EPLD器件,较GAL器件有更高的集成度,可以用紫外线或电擦除。

(5)20世纪80年代末,Lattice公司推出EPLD器件,将可编程逻辑器件的性能和应用技术推向了一个全新的高度(6)进入20世纪90年代后,可编程逻辑集成电路技术进入飞速发展时期。

器件的可用逻辑门数超过了百万,并出现了内嵌发杂功能模块3.PLD的分类?(1)按集成度:低/高集成度芯片(2)结构上:乘积项/查找表结构器件(3)编成工艺:熔丝/反熔丝/EPROM/EEPROM/SRAM/FLASH型4.熔丝和反熔丝编程的区别?熔丝(Fuse)早期的PROM器件的使用结构,根据设计熔丝图文件来烧断对应的熔丝编程反熔丝(Anti-fuse)编程时通过击穿漏层是两点导通,与熔丝烧断获得开路正好相反5.CPLD的MAX7000系列器件的组成?逻辑阵列块,宏单元,扩展乘积项,可编程连线阵列和I/O控制块6.Altera的Cyclone系列器件的组成?逻辑阵列块,嵌入式存储器块,I/O单元和PLL等模块构成7.STD-LOGIC定义了哪九种数据?‘U’未初始化的‘X’强未知的‘0’强逻辑0‘1’强逻辑1‘Z’高阻态‘W’弱未知的‘L’弱逻辑0‘H’弱逻辑1‘—’表示忽略8.检测时钟上升沿可用哪些语句?CLK'EVENT' AND (CLK='1') AND (CLK 'LAST VALUE='0'');Rising_edge();wait until clk='1';9.信号与变量的异同点?同:初始值的设置不是必需的,语句的格式相似,赋值都可以多次。

eda技术与vhdl设计答案【篇一:eda技术与vhdl复习练习题】/p> 一、填空题1、pld的中文含义是:________。

2、asic的中文含义是:________。

3、“与-或”结构的可编程逻辑器件主要由四部分构成:________、________、____________和____________。

4、可编程逻辑器件结构图中一般用“x”表示此编程单元为________。

6、可编程逻辑器件结构图中无任何标记表示此编程单元为________。

7、可编程逻辑器件按规模的大小一般分为________和_________。

8、低密度可编程逻辑器件的主要有________和_________。

9、gal器件________取代全部pal器件。

10、pal器件只能________次编程。

11、gal器件能________次编程。

12、gal器件________取代ttl器件。

13、gal器件采用________擦除。

14、pal和gal器件________在系统编程。

15、pal和gal器件需要使用________编程。

二、选择题1、可编程逻辑器件pld的基本结构形式是_______:a:与——与b:与——或c:或——与d:或——或2、可以多次编程的器件是_______:a:prom b:plac:pal d:gal3、pld器件未编程时_______:a:有逻辑功能 b:没有逻辑功能c:pal器件有逻辑功能d:gal器件有逻辑功能 4、gal器件可以用擦除:a:普通光 b:紫外线c:红外线 d:电5、gal16v8器件的输出引脚最多有______:a:16b:4 c:8 d:206、pal16v8器件的输入引脚最多有_______:a:16 b:4 c:8 d:207、gal16v8不能取代_________:a:pal16v b:74ls138c:74ls373 d:isplsi1032e-70plcc848、gal16v8的_______不可编程:a:与阵列 b:或阵列c:输出逻辑宏单元olmc d:a、b都三、判断题 1、gal器件的输出逻辑宏单元olmc不能实现pal器件的所有输出形式。

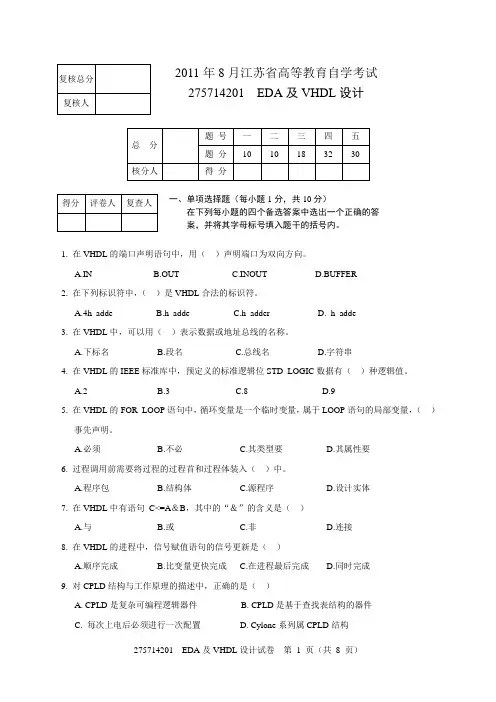

1. 在VHDL 的端口声明语句中,用( )声明端口为双向方向。

A.INB.OUTC.INOUTD.BUFFER 2. 在下列标识符中,( )是VHDL 合法的标识符。

A.4h_addeB.h_adde_C.h_adderD._h_adde 3. 在VHDL 中,可以用( )表示数据或地址总线的名称。

A.下标名B.段名C.总线名D.字符串4. 在VHDL 的IEEE 标准库中,预定义的标准逻辑位STD_LOGIC 数据有( )种逻辑值。

A.2 B.3 C.8 D.95. 在VHDL 的FOR_LOOP 语句中,循环变量是一个临时变量,属于LOOP 语句的局部变量,( )事先声明。

A.必须B.不必C.其类型要D.其属性要 6. 过程调用前需要将过程的过程首和过程体装入( )中。

A.程序包B.结构体C.源程序D.设计实体 7. 在VHDL 中有语句 C<=A &B ,其中的“&”的含义是( )A.与B.或C.非D.连接 8. 在VHDL 的进程中,信号赋值语句的信号更新是( )A.顺序完成B.比变量更快完成C.在进程最后完成D.同时完成 9. 对CPLD 结构与工作原理的描述中,正确的是( )A. CPLD 是复杂可编程逻辑器件B. CPLD 是基于查找表结构的器件C. 每次上电后必须进行一次配置D. Cylone 系列属CPLD 结构2011年8月江苏省高等教育自学考试 275714201 EDA 及VHDL 设计一、单项选择题(每小题1分,共10分)在下列每小题的四个备选答案中选出一个正确的答 案,并将其字母标号填入题干的括号内。

10. Quartus Ⅱ的VHDL 语言文本设计文件类型是( )A. .vwfB. .bdfC. .vhdD. .v11. 功能仿真是在设计输入完成后,选择具体器件进行编译之前进行的逻辑功能验证,因此又称为 。

12. VHDL 设计实体的基本结构由 、程序包、实体、结构体和配置等部分构成。

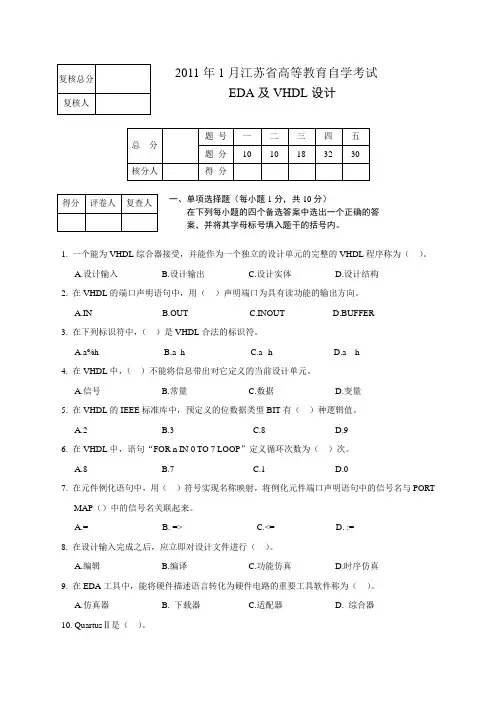

1. 一个能为VHDL 综合器接受,并能作为一个独立的设计单元的完整的VHDL 程序称为( )。

A.设计输入 B.设计输出 C.设计实体 D.设计结构2. 在VHDL 的端口声明语句中,用( )声明端口为具有读功能的输出方向。

A.IN B.OUT C.INOUT D.BUFFER3. 在下列标识符中,( )是VHDL 合法的标识符。

A.a%hB.a_hC.a--hD.a__h 4. 在VHDL 中,( )不能将信息带出对它定义的当前设计单元。

A.信号B.常量C.数据D.变量 5. 在VHDL 的IEEE 标准库中,预定义的位数据类型BIT 有( )种逻辑值。

A.2 B.3 C.8 D.9 6. 在VHDL 中,语句“FOR n IN 0 TO 7 LOOP ”定义循环次数为( )次。

A.8 B.7 C.1 D.07. 在元件例化语句中,用( )符号实现名称映射,将例化元件端口声明语句中的信号名与PORT MAP ()中的信号名关联起来。

A.=B. =>C.<=D. := 8. 在设计输入完成之后,应立即对设计文件进行( )。

A.编辑B.编译C.功能仿真D.时序仿真 9. 在EDA 工具中,能将硬件描述语言转化为硬件电路的重要工具软件称为( )。

A.仿真器 B. 下载器 C.适配器 D. 综合器 10. Quartus Ⅱ是( )。

2011年1月江苏省高等教育自学考试EDA 及VHDL 设计一、单项选择题(每小题1分,共10分)在下列每小题的四个备选答案中选出一个正确的答 案,并将其字母标号填入题干的括号内。

2A.高级语言B.硬件描述语言C.EDA 工具软件D.综合软件11. 一般将EDA 技术的发展分为CAD 、 、和EDA 三个阶段。

12. 时序仿真是在选择了具体器件并完成布局、布线之后进行的时序关系仿真,因此又称为 。

13. VHDL 设计实体的基本结构由库、程序包、实体、结构体和 等部分构成。

eda技术考试题及答案一、选择题(每题2分,共20分)1. EDA技术中的"E"代表什么?A. ElectronicsB. EducationC. EngineeringD. Economy答案:A2. 在EDA技术中,以下哪个不是硬件描述语言?A. VHDLB. VerilogC. HTMLD. SystemVerilog答案:C3. EDA工具主要用于什么领域?A. 软件开发B. 硬件设计C. 数据分析D. 网络管理答案:B4. 以下哪个不是EDA工具的功能?A. 逻辑综合B. 时序分析C. 代码调试D. 性能优化答案:C5. 在EDA技术中,FPGA代表什么?A. Field Programmable Gate ArrayB. Fixed Programmable Gate ArrayC. Flexible Programmable Gate ArrayD. Functional Programmable Gate Array答案:A6. 以下哪个是EDA技术中用于验证的工具?A. MATLABB. ModelSimC. AutoCADD. Photoshop答案:B7. EDA技术中的"A"代表什么?A. AnalysisB. AlgorithmC. ApplicationD. Architecture答案:A8. 在EDA技术中,以下哪个不是仿真工具?A. Xilinx ISEB. Cadence VirtuosoC. Synopsys VCSD. Mentor Graphics ModelSim答案:A9. EDA技术中,以下哪个是用于布局和布线的软件?A. Quartus IIB. Altium DesignerC. MATLABD. Eclipse答案:B10. 以下哪个不是EDA技术中的测试方法?A. 功能仿真B. 时序仿真C. 静态时序分析D. 动态时序分析答案:D二、填空题(每题2分,共20分)1. EDA技术的核心是______,它允许设计者在不实际制造硬件的情况下测试和验证设计。

(完整word版)EDA技术题库EDA技术题库⼀.填空题1. Verilog 的基本设计单元是模块。

它是由两部分组成,⼀部分描述接⼝;另⼀部分描述逻辑功能,即定义输⼊是如何影响输出的。

2. ⽤assign 描述的语句我们⼀般称之为组合逻辑,并且它们是属于并⾏语句,即于语句的书写次序⽆关。

⽽⽤always 描述的语句我们⼀般称之为组合逻辑或时序逻辑,并且它们是属于串⾏语句,即于语句的书写有关。

3.在case 语句中⾄少要有⼀条default 语句。

4. 已知x=4'b1001,y=4 '0110,则x的4位补码为4'b1111,⽽y的4位的补码为4 'b0110。

5. 两个进程之间是并⾏语句。

⽽在Always 中的语句则是顺序语句。

6. 综合是将⾼层次上描述的电⼦系统转换为低层次上描述的电⼦系统,以便于系统的具体硬件实现。

综合器是能⾃动将⾼层次的表述(系统级、⾏为级)转化为低层次的表述(门级、结构级)的计算机程序7. 设计输⼊的⽅式有原理图、硬件描述语⾔、状态图以及波形图。

8. 按照仿真的电路描述级别的不同,HDL 仿真器可以完成:系统级仿真,⾏为级仿真,RTL 级仿真,门级(时序)仿真。

按照仿真是否考虑硬件延时分类,可以分为:功能仿真和时序仿真。

仿真器可分为基于元件(逻辑门)仿真器和基于HDL语⾔的仿真器9. IP核是知识产权核或知识产权模块,在EDA技术中具有⼗分重要的地位。

半导体产业的IP定义为⽤于ASIC或FPGA中的预先设计好的电路功能模块。

IP分为软IP、固IP和硬IP。

10. 可编程逻辑器件PLD是⼀种通过⽤户编程或配置实现所需逻辑功能的逻辑器件,也就是说⽤户可以根据⾃⼰的需求,通过EDA开发技术对其硬件结构和⼯作⽅式进⾏重构,重新设计其逻辑功能11. 两种可编程逻辑结构是基于与- 或阵列可编程结构(乘积项逻辑可编程结构)、基于SRAM 查找表的可编程逻辑结构12. PLD按集成度分类:简单PLD复杂PLD按结构分类:基于“与-或”阵列结构的器件、基于查找表结构的器件;从编程⼯艺上分类:熔丝型、反熔丝型、EPROh型、EEPRO型、SRAM 型、Flash 型13. Verilog 的端⼝模式有三种:输⼊端⼝、输出端⼝、双向端⼝,对应的端⼝定义关键词分别是:input 、output 、inout14. Verilog 中常⽤有两种变量:寄存器型变量(⽤reg 定义)、⽹线型变量(⽤wire 定义)15. Verilog 有两种赋值⽅式:阻塞式赋值(=)、⾮阻塞式赋值(<=)16. Verilog 有四种循环语句:for 语句、repeat 语句、while 语句、forever 语句17.Verilog 的描述风格:RTL 描述、数据流描述、⾏为描述、结构描述18. 从状态机的信号输出⽅式上分,有Mealy 型和Moore 型两种状态机;从状态机的描述结构上分,有单过程状态机和多过程状态机;从状态机表达⽅式上分,有符号化状态机和确定状态编码的状态机;从状态机编码⽅式上分,有顺序编码状态机、⼀位热码编码状态机或其他编码⽅式状态机。

1、单项选择题:(20 分)1.IP 核在 EDA 技术和开发中具有十分重要的地位;提供用 VHDL 等硬件描述语言描述的功能块,但不涉及实现该功能块的具体电路的 IP 核为D 。

A .瘦IP B.固IP C.胖IP D.都不是2.综合是EDA 设计流程的关键步骤,在下面对综合的描述中,是错误的。

DA.综合就是把抽象设计层次中的一种表示转化成另一种表示的过程;B.综合就是将电路的高级语言转化成低级的,可与 FPGA / CPLD 的基本结构相映射的网表文件;C.为实现系统的速度、面积、性能的要求,需要对综合加以约束,称为综合约束;D.综合可理解为一种映射过程,并且这种映射关系是唯一的,即综合结果是唯一的。

3.大规模可编程器件主要有 FPGA、CPLD 两类,下列对 FPGA 结构与工作原理的描述中,正确的是 C。

A.FPGA 全称为复杂可编程逻辑器件;B.FPGA 是基于乘积项结构的可编程逻辑器件;C.基于 SRAM 的FPGA 器件,在每次上电后必须进行一次配置;D.在Altera 公司生产的器件中,MAX7000 系列属 FPGA 结构。

4.进程中的信号赋值语句,其信号更新是C。

A.按顺序完成;B.比变量更快完成;C.在进程的最后完成;5.VHDL 语言是一种结构化设计语言;一个设计实体(电路模块)包括实体与结构体两部分,结构体描述BA.器件外部特性;B. 器件的内部功能;C.器件的综合约束;D.器件外部特性与内部功能。

6.不完整的 IF 语句,其综合结果可实现AA.时序逻辑电路B.组合逻辑电C. 双向电路D. 三态控制电路7.子系统设计优化,主要考虑提高资源利用率减少功耗(即面积优化),以及提高运行速度(即速度优化);指出下列哪些方法是面积优化B①流水线设计②资源共享③逻辑优化④串行化⑤寄存器配平⑥关键路径法A. ①③⑤B. ②③④C. ②⑤⑥D. ①④⑥8.下列标识符中,是不合法的标识符。

杭州电子科技大学2005 年EDA 技术与VHDL 考试试题考试课程EDA 技术与VHDL 考试日期年月日成绩课程号B0405010 教师号任课教师姓名曾毓考生姓名学号(8 位)年级专业一、单项选择题:(20 分)1.大规模可编程器件主要有FPGA、CPLD 两类,下列对CPLD 结构与工作原理的描述中,正确的是。

A.CPLD 是基于查找表结构的可编程逻辑器件;B.CPLD 即是现场可编程逻辑器件的英文简称;C.早期的CPLD 是从GAL 的结构扩展而来;D.在Xilinx 公司生产的器件中,XC9500 系列属CPLD 结构;2.综合是EDA 设计流程的关键步骤,综合就是把抽象设计层次中的一种表示转化成另一种表示的过程;在下面对综合的描述中,是正确的。

A.综合就是将电路的高级语言转化成低级的,可与FPGA / CPLD 的基本结构相映射的网表文件;B.综合是纯软件的转换过程,与器件硬件结构无关;C.为实现系统的速度、面积、性能的要求,需要对综合加以约束,称为强制综合。

D.综合可理解为,将软件描述与给定的硬件结构用电路网表文件表示的映射过程,并且这种映射关系是唯一的;3.IP 核在EDA 技术和开发中具有十分重要的地位,IP 分软IP、固IP、硬IP;下列所描述的IP 核中,对于硬IP 的正确描述为。

A.提供用VHDL 等硬件描述语言描述的功能块,但不涉及实现该功能块的具体电路;B.提供设计的最总产品--- 模型库;C.以网表文件的形式提交用户,完成了综合的功能块;D.都不是。

4.基于EDA 软件的FPGA / CPLD 设计流程为:原理图/HDL 文本输入→→ 综合→适配→→编程下载→硬件测试。

①功能仿真②时序仿真③逻辑综合④配置⑤引脚锁定A.③① B. ⑤② C.④⑤ D. ①②5.下面对利用原理图输入设计方法进行数字电路系统设计,那一种说法是不正确的。

A.原理图输入设计方法直观便捷,但不适合完成较大规模的电路系统设计;B.原理图输入设计方法一般是一种自底向上的设计方法;C.原理图输入设计方法无法对电路进行功能描述;D.原理图输入设计方法也可进行层次化设计。

6.在VHDL 语言中,下列对进程(PROCESS)语句的语句结构及语法规则的描述中,不正确的是。

A.PROCESS 为一无限循环语句;敏感信号发生更新时启动进程,执行完成后,等待下一次进程启动。

B.敏感信号参数表中,不一定要列出进程中使用的所有输入信号;C.进程由说明部分、结构体部分、和敏感信号三部分组成;D.当前进程中声明的变量不可用于其他进程。

7.嵌套使用IF 语句,其综合结果可实现。

A.带优先级且条件相与的逻辑电路;B.条件相或的逻辑电路;C.三态控制电路;D.双向控制电路。

8.电子系统设计优化,主要考虑提高资源利用率减少功耗---- 即面积优化,以及提高运行速度 --- 即速度优化;指出下列那种方法不属于速度优化:。

A. 流水线设计B. 串行化C. 关键路径法D. 寄存器配平9.在一个VHDL 设计中idata 是一个信号,数据类型为integer,数据范围0 to 127,下面哪个赋值语句是正确的。

A.idata := 32;B.idata <= 16#A0#;C. idata <= 16#7#E1;D. idata := B#1010#;10.下列EDA 软件中,哪一不具有逻辑综合功能:。

A.Max+Plus IIB.ModelSimC.Quartus IID.Synplify第1 页共5 页二、EDA 名词解释,写出下列缩写的中文(或者英文)含义:(14 分)1.SOPC2.LUT3.JTAG4.GAL5.EAB6.IP7.HDL三、VHDL 程序填空:(10 分)下面程序是n 输入与门的VHDL 描述,试补充完整。

ieee;use ........................................... a ll;entity andn is(n : integer); -- 类属参数声明port ( a : in std_logic_vector( downto 0);c : out std_logic);end;behav of is -- 结构体声明beginprocess ( )int : std_logic; -- 变量声明beginint := ; -- 变量赋初值for I in a'length – 1 downto 0 loop -- 循环判断if a(i) = '0' thenint := '0';end if;end loop;c <= ; -- 输出判断结果end process;end behav;四、VHDL 程序改错:(10 分)本题程序为EDA 实验中的示例程序sch.vhd,仔细阅读程序,回答问题。

1.对该程序进行编译时出现错误提示:“VHDL Design File “sch” must contain an entity of the same name.”这是什么原因?如何修改?2.修改问题1 的错误后,如果编译时出现“Can’t open VHDL “WORK””这样的错误提示。

这又是什么原因,如何修改?library ieee;--1use ieee.std_logic_1164.all; --2 entity schk is--3port (din, clk, clr : in std_logic; -- 串行输入数据位/工作时钟/复位信号--4--5 --6ab : out std_logic_vector(3 downto 0) -- 检测结果输出);end schk;--7architecture bhv of schk is -- 8signal q : integer range 0 to 8; --9signal d : std_logic_vector(7 downto 0); -- 8 位待检测预置数--10 begin--11d = "11100101"; -- 8 位待检测预置数--12process (clk, clr) -- 13begin --14--17 if clr = '1' then q<= 0; --15 else if clk'event and clk = '1' then --16 case q iswhen 0 => if din = d(7) then q <= 1; else q <= 0; end if; --18when 1 => if din = d(6) then q <= 2; else q <= 0; end if; --19when 2 => if din = d(5) then q <= 3; else q <= 0; end if; --20when 3 => if din = d(4) then q <= 4; else q <= 0; end if; --21when 4 => if din = d(3) then q <= 5; else q <= 0; end if; --22when 5 => if din = d(2) then q <= 6; else q <= 0; end if; --23when 6 => if din = d(1) then q <= 7; else q <= 0; end if; --24when 7 => if din = d(0) then q <= 8; else q <= 0; end if; --25when others => q <= 0;--26 --27--28 end if;end case;-29end process; -process (q)--30begin--3132--33 --34 if q = 8 then ab <= "1010"; -- else ab <= "1011";end if;end process; - -35end bhv;--361.在上述程序代码中存在两处错误,编译时出现如下提示,试修改错误:Error: Line 12: File f:\eda\schk.vhd: VHDL syntax error: unexpected signal “d” in Concurrent Statement PartError: Line 29:File f:\eda\schk.vhd: VHDL syntax error: if statement must have END IF, but found PROCESS instead错误1 行号:程序改为:错误2 行号:程序改为:第2 页共5 页五、VHDL 程序设计:(16 分)设计一数据选择器MUX,其系统模块图和功能表如下图所示。

试采用下面三种方式中的两种来描述该数据选择器MUX 的结构体。

(a)用if 语句。

(b) 用case 语句。

(c) 用when else 语句。

Library ieee;Use ieee.std_logic_1164.all;Entity mymux isPort ( sel : in std_logic_vector(1 downto 0); -- 选择信号输入Ain, Bin : in std_logic_vector(1 downto 0); -- 数据输入Cout : out std_logic_vector(1 downto 0) );End mymux;六、根据原理图写出相应的VHDL 程序:(10 分)第3 页共5 页七、综合题(20 分)下图是一个A/D 采集系统的部分,要求设计其中的FPGA 采集控制模块,该模块由三个部分构成:控制器(Control)、地址计数器(addrcnt)、内嵌双口RAM(adram)。

控制器(control)是一个状态机,完成AD574 的控制,和adram 的写入操作。

Adram 是一个LPM_RAM_DP 单元,在wren 为’1’时允许写入数据。

试分别回答问题下面列出了AD574 的控制方式和控制时序图AD574 逻辑控制真值表(X 表示任意)CE CS RC K12_8 A0 工作状态0 X X X X 禁止X 1 X X X 禁止1 0 0 X 0 启动12 位转换1 0 0 X 1 启动8 位转换1 0 1 1 X 12 位并行输出有效1 0 1 0 0 高8 位并行输出有效1 0 1 0 1 低4 位加上尾随4 个0 有效AD574 工作时序:问题:1.要求AD574 工作在12 位转换模式,K12_8、A0 在control 中如何设置?2.试画出control 的状态机的状态图3.地址计数器每当ClkInc 时钟上升沿到达,输出地址加1,请对该模块进行VHDL 描述。