模拟CMOS集成电路实验报告

课程名称:模拟CMOS集成电路实验

设计题目:二阶运算放大器的设计与仿真

院系:

班级:

设计者:

学号:

设计要求:设计二阶运算放大器,完成电路图的设计与仿真。

设计准备:熟悉linux客户端的基本文件操作,掌握Cadence公司的Spectre仿真器的基本操作指令。能够使用spectre软件进行电路的交流、直流和瞬态仿真,并能根据仿真之后的结果来调整自己的设计参数,来得到更好的器件性能。

设计过程:

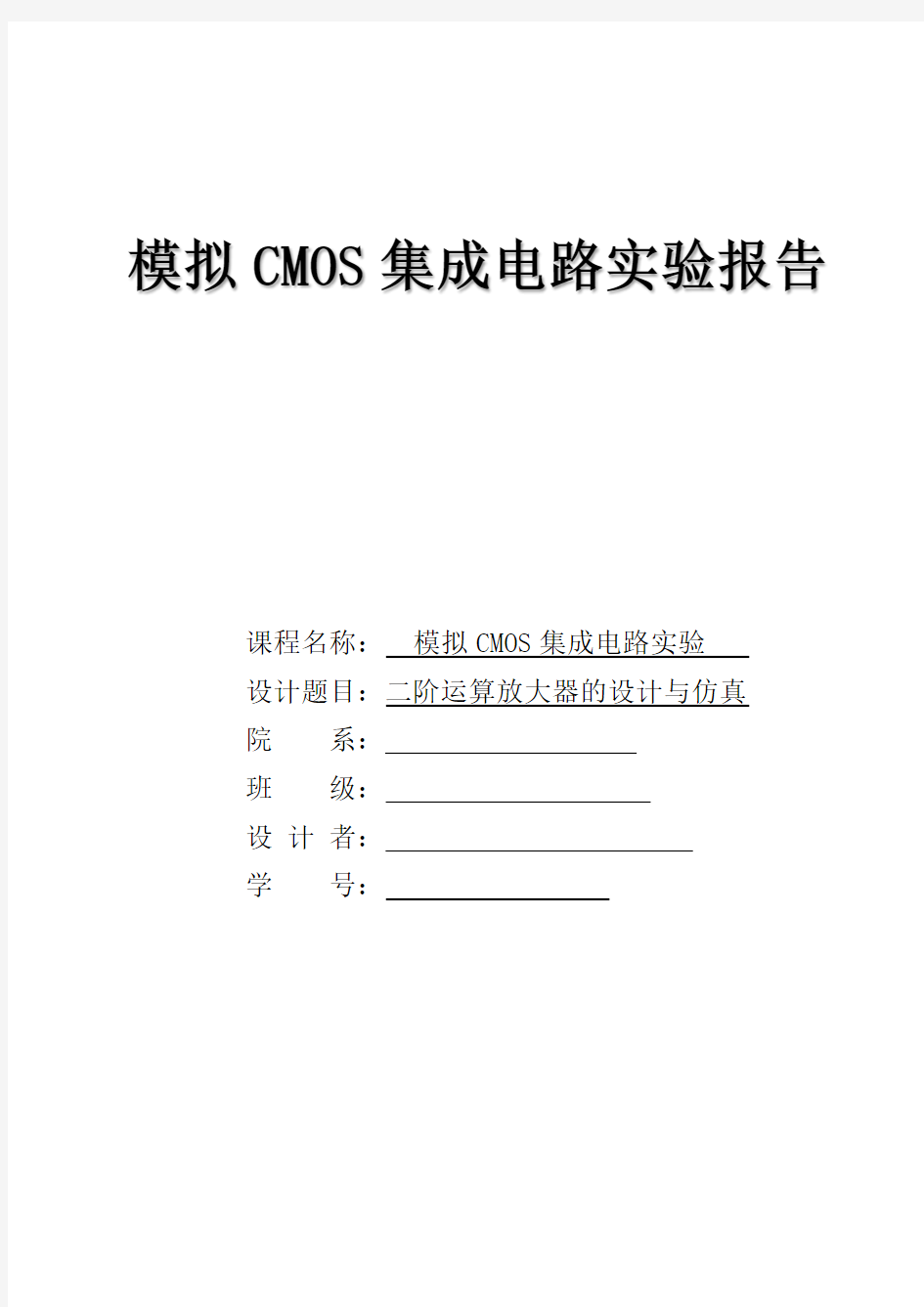

第一级运算放大器采用差动式共源放大器,提供比较大的增益,第二级运算放大器采用共源共栅结构提供比较大的输出摆幅。并且采用米勒电容补偿来进行频率补偿。

一.电路图部分

启动cadence的设计环境平台,建立library,设置激励源,进行电路的仿真

电路原理图

运算放大器设计指标:

工作电源工作范围5V

增益带宽5MHz

输出摆幅10V/us

相位裕度 60o 输出摆幅

0.5~4.5V 共模输入范围 0.5~4.5V 功耗 2mW

增益

4000V/V (72dB )

MOS 管工艺相关数据为

2211110/,50/,0.04,0.04,0.2n ox p ox n p u C uA V u C uA V V V λλγ--=====

根据设计指标,选择一个简单放大器与一个共源共栅放大器级联的结构设计开实现所需的电路。

运算放大器的小信号增益为

计算过程附在报告之后,为手写版本。

经过计算,得到理论的MOS 管尺寸(采用最小线宽为1um)

Schematic 实际电路图:

仿真电路图

激励源参数:共模输入ip:AC magnitude:1V

AC phase:0V

DC voltage:vbias V Offset voltage:vbias V Amplitude:va V frequency:f0 Hz in:AC magnitude:-1V

AC phase:0V

DC voltage:vbias V

Offset voltage:vbias V

Amplitude:-va V

frequency:f0 Hz

参数设置:vpower=5V vbias=2.4V va=20uV f0=500 Hz 首先进行了瞬态仿真,得到了输出波形。

从输出波形可以看出,输出波形的峰谷差达到了(4.02-3.83)=0.2V,而输入为20uv,增益达到了10000左右。

然后进行ac交流仿真,对于输入波形的频率进行了扫描,频率从1Hz到1GHz以20Hz为间隔进行仿真,输出波形如下图,可以看出在频率达到200Hz 时增益出现了下降的趋势,带宽较低。

在下方输出波形的波特图中,可以看出增益达到了78dB,相位裕度为(180 o -128 o)=52 o,基本达到了设计要求(由于图像过大压缩有损失,在报告后面附完整的图像)。

仿真过程中,放大器的放大倍数达到了要求,但是相位裕度一直维持在45o,经过调整参数达到了最终的结果,调整后器件的参数为(红色的为修改的数据)。

实验结论:本次运算放大器电路设计中,我们首先根据老师提供的数据进行了器件参数的计算,并经过验证,满足了对于放大器的要求,计算得到增益为80dB,相位裕度为60o,共模输入范围0.269V~4.52V,功耗为1.17mV。

在实际仿真过程中,通过直流、交流、瞬态仿真,得到相应的瞬态输出曲线、增益相位曲线和频率扫描曲线,发现由于使用的工艺参数与计算中的并不相同,出现了增益和相位裕度增益带宽积均变小的情况,通过后期调整参数,使各项指标都更接近设计要求,但是和要求还是有相应的差距。最终得到增益为78dB,相位裕度为52o,基本符合了设计要求。

三.如果要求A v至少提高为原来的2倍,其它要求不变,如何修改电路(注意讨论对其它性能参数的影响)?

使A v提高为原来的两倍,首先由增益公式得

[] [] []

26523667

26223667

242367

2/I()()

/I()()

1/()()

1/

u m m

m m

OD OD

A g g I

g g I

V V

C

λλλλ

λλλλ

λλλλ

=++

=++

=++

=

=

通过增益的表达式可知,可以通过降低I5、I6,或者增大M1(M2)、M6的尺寸。

如果M1、M6尺寸增大为原来的两倍,I2和I6保持不变,则111

2(/L)

m n OX

g I C W

μ

=增大,由p11C

(0)/C

V m

GB A g

ω

==

可知增益带宽积就会增大,但由于增益增大倍数大,所以1pω减小。由6666

/(2)

m

I g K S

=可知将会增大,66p OX6

2/(C(W/L))

OD

V Iμ

=减小,

,6

OUT MAX OD

V VDD V

=-增大,满足要求。由于6644

/

I S I S

=,所以

4

S也应该增大为原来的两倍,444

2/(/)

OD p OX

V I C W L

μ

=减小,即3GS

V减小。满足要求。

四.如果要求增益带宽积GB提高为原来的2倍,其它要求不变,如何修改电路(注意讨论对其它性能参数的影响)?

注意事项:

尾电流增加,各个器件尺寸不变的话,I 3和I 1增加,g m3和g m1增大,但增大倍数小,g m6增大,I 6增大,最终可由下面的公式推出,放大倍数下降。

[][][]

26523667262236672423672/I ()()/I ()()1/()()1/u m m m m OD OD A g g I g g I V V λλλλλλλλλλλλ=++=++=++==

仿真网表:

// Generated for: spectre

// Generated on: Jun 6 12:35:10 2015

// Design library name: lab1

// Design cell name: cut_amp1

// Design view name: schematic

simulator lang=spectre

global 0 vdd!

include "/home/homeO1/cadence/IC5141U4/tools/dfII/samples/artist/ahdlLib/quantity.spectre" parameters vpower=5 vbias=2.4 va=20u f0=500

include "/home/homeO5/user1/training/ic/spice_labs/spice_model/sm046005-1j.scs" section=typical

// Library name: lab1

// Cell name: amp1

// View name: schematic

subckt amp1 V out in ip vcn

Cl (V out 0) capacitor c=10p

Cc (Vout net034) capacitor c=6p

M4 (V out net034 vdd! vdd!) pmos_3p3 w=35u l=1u

M2 (net6 net6 vdd! vdd!) pmos_3p3 w=5u l=1u

M1 (net034 net6 vdd! vdd!) pmos_3p3 w=5u l=1u

M3 (net6 ip net063 0) nmos_3p3 w=2u l=1u

M6 (net063 vcn 0 0) nmos_3p3 w=15u l=1u

M5 (V out vcn 0 0) nmos_3p3 w=45u l=1u

M0 (net034 in net063 0) nmos_3p3 w=2u l=1u

ends amp1

// End of subcircuit definition.

// Library name: lab1

// Cell name: cut_amp1

// View name: schematic

M0 (net012 net012 0 0) nmos_3p3 w=100u l=2u

I4 (vdd! net012) isource dc=60u type=dc

V3 (net11 0) vsource dc=vbias mag=-1 type=sine sinedc=vbias ampl=-va \ freq=f0

V2 (in 0) vsource dc=vbias mag=1 type=sine sinedc=vbias ampl=va freq=f0

V0 (vdd! 0) vsource dc=vpower type=dc

I0 (out in net11 net012) amp1

simulatorOptions options reltol=1e-3 vabstol=1e-6 iabstol=1e-12 temp=27 \ tnom=27 scalem=1.0 scale=1.0 gmin=1e-12 rforce=1 maxnotes=5 maxwarns=5 \ digits=5 cols=80 pivrel=1e-3 ckptclock=1800 \

sensfile="../psf/sens.output" checklimitdest=psf

tran tran stop=20m errpreset=conservative write="spectre.ic" \

writefinal="spectre.fc" annotate=status maxiters=5

finalTimeOP info what=oppoint where=rawfile

ac ac start=1 stop=1G dec=20 annotate=status

dcOp dc write="spectre.dc" maxiters=150 maxsteps=10000 annotate=status dcOpInfo info what=oppoint where=rawfile

dc dc param=vbias start=0 stop=5 step=0.001 oppoint=rawfile maxiters=150 \ maxsteps=10000 annotate=status

modelParameter info what=models where=rawfile

element info what=inst where=rawfile

outputParameter info what=output where=rawfile

designParamVals info what=parameters where=rawfile

primitives info what=primitives where=rawfile

CMOS二级运算放大器设计 (东南大学集成电路学院) 一.运算放大器概述 运算放大器是一个能将两个输入电压之差放大并输出的集成电路。运算放大器是模拟电子技术中最常见的电路,在某种程度上,可以把它看成一个类似于BJT 或FET 的电子器件。它是许多模拟系统和混合信号系统中的重要组成部分。 它的主要参数包括:开环增益、单位增益带宽、相位阈度、输入阻抗、输入偏流、失调电压、漂移、噪声、输入共模与差模范围、输出驱动能力、建立时间与压摆率、CMRR、PSRR以及功耗等。 二.设计目标 1.电路结构 最基本的COMS二级密勒补偿运算跨导放大器的结构如图所示。主要包括四部分:第一级输入级放大电路、第二级放大电路、偏置电路和相位补偿电路。 图两级运放电路图 2.电路描述 电路由两级放大器组成,M1~M4构成有源负载的差分放大器,M5提供该放大器的工作电流。M6、M7管构成共源放大电路,作为运放的输出级。M6 提供给M7 的工作电流。M8~M13组成的偏置电路,提供整个放大器的工作电流。相位补偿电路由M14和Cc构成。M14工作在线性区,可等效为一个电阻,与电容Cc一起跨接在第二级输入输出之间,构成RC密勒补偿。 3.设计指标 两级运放的相关设计指标如表1。

表1 两级运放设计指标 三.电路设计 第一级的电压增益: )||(422111o o m m r r g R G A == 第二级电压增益: )||(766222o o m m r r g R G A =-= 所以直流开环电压增益: )||)(||(76426221o o o o m m o r r r r g g A A A -== 单位增益带宽: c m O C g A GBW π2f 1 d == 偏置电流: 2 13 122121)/()/()/(2??? ? ??-=L W L W R L W KP I B n B 根据系统失调电压: 7 5 6463)/()/(21)/()/()/()/(L W L W L W L W L W L W == 转换速率: ? ?? ???-=L DS DS C DS C I I C I SR 575,min 相位补偿: 12.1)/()/()/()/(1 61311 146 6+== m m m C g g L W L W L W L W g R

《集成电路CAD》课程设计报告 课题:基于Spectre运算放大器的设计 一:课程设计目标及任务 利用Cadence软件设计使用差分放大器,设计其原理图,并画出其版图,模拟器各项性能指标,修改宽长比,使其最优化。 二:运算放大器概况 运算放大器(operational amplifier),简称运放(OPA),如图1.1所示: 图1.1运放示意图 运算放大器最早被设计出来的目的是将电压类比成数字,用来进行加、减、乘、除的运算,同时也成为实现模拟计算机的基本建构方块。然而,理想运算放大器的在电路系统设计上的用途却远远超过加减乘除的计算。今日的运算放大器,无论是使用晶体管或真空管、分立式元件或集成电路元件,运算放大器的效能都已经接近理想运算放大器的要求。早期的运算放大器是使用真空管设计的,现在多半是集成电路式的元件。但是如果系统对于放大器的需求超出集成电路放大器的需求时,常常会利用分立式元件来实现这些特殊规格的运算放大器。 三:原理图的绘制及仿真

3.1原理图的绘制 首先在Cadence电路编辑器界面绘制原理图如下: 图3.1电路原理图 原理图中MOS管的参数如下表: Instance name Model W/m L/m Multiplier Library Cell name View name M1 nmosl 800n 500n 1 Gpdk180 nmos symbol M2 nmosl 800n 500n 1 Gpdk180 nmos symbol M3 pmosl 1.1u 550n 1 Gpdk180 pmos symbol M4 pmosl 1.1u 550n 1 Gpdk180 pmos symbol M5 nmosl 800n 500n 1 Gpdk180 nmos symbol

东北大学秦皇岛分校电子信息系 综合课程设计 高频功率放大器的设计及仿真 专业名称电子信息工程 班级学号5081112 学生姓名姜昊昃 指导教师邱新芸 设计时间2011.06.20~2011.07.01

课程设计任务书 专业:电子信息工程学号:5081112学生姓名(签名): 设计题目:高频功率放大器的设计及仿真 一、设计实验条件 Multisim软件 二、设计任务及要求 1.设计一高频功率放大器,要求的技术指标为:输出功率Po≥125mW,工作 中心频率fo=6MHz,η>65%; 2.已知:电源供电为12V,负载电阻,RL=51Ω,晶体管用2N2219,其主要参 数:Pcm=1W,Icm=750mA,V CES=1.5V, f T=70MHz,hfe≥10,功率增益Ap≥13dB(20倍)。 三、设计报告的内容 1.设计题目与设计任务(设计任务书) 2.前言(绪论)(设计的目的、意义等) 3.设计主体(各部分设计内容、分析、结论等) 4.结束语(设计的收获、体会等) 5.参考资料 四、设计时间与安排 1、设计时间:2周 2、设计时间安排: 熟悉实验设备、收集资料:2 天 设计图纸、实验、计算、程序编写调试:4 天 编写课程设计报告:3 天 答辩:1 天

1.设计题目与设计任务(设计任务书) 1.1 设计题目 高频功率放大器的设计及仿真 1.2 设计任务 要求设计一个技术指标为输出功率Po≥125mW,工作中心频率fo=6MHz η>65%的高频功率放大器。 2. 前言(绪论) 我们通过“模电”课程知道,当输入信号为正弦波时放大器可以按照电流的导通角的不同,将其分为甲类、乙类、甲乙、丙类等工作状态。甲类放大器电流的导通角为360度,适用于小信号低功率放大;乙类放大器电流的导通角约等于180度;甲乙类放大器电流的导通角介于180度与360度之间;丙类放大器电流的导通角则小于180度。乙类和丙类都适用于大功率工作。 丙类工作状态的输出功率和效率是上述几种工作状态中最高的。高频功率放大器大多工作于丙类。但丙类放大器的电流波形失真太大,因而只能用于采用调谐回路作为负载的谐振功率放大。由于调谐回路具有滤波能力,回路电流与电压仍然极近于正弦波形,失真很小。 可是若仅仅是用一个功率放大器,不管是甲类或者丙类,都无法做到如此大的功率放大。 综上,确定此高频电路由两个模块组成:第一模块是两级甲类放大器;第二模块是一工作在丙类状态的谐振放大器,它作为功放输出级,最好能工作在临界状态。此时,输出交流功率达到最大,效率也较高,一般认为此工作状态为最佳工作状态。 3. 系统原理 3.1 高频功率放大器知识简介 在通信电路中,为了弥补信号在无线传输过程中的衰耗要求发射机具有较大的功率输出,通信距离越远,要求输出功率越大。为了获得足够大的高频输出功率,必须采用高频功率放大器。高频功率放大器是无线电发射设备的重要组成部分。在无线电信号发射过程中,发射机的振荡器产生的高频振荡信号功率很小,

折叠式共源共栅运算放大器

目录 一.摘要 (2) 二.电路设计指标 (3) 三.电路结构 (3) 四.手工计算 (7) 五.仿真验证 (10) 六.结论 (12) 七.收获与感悟 (12) 八.参考文献 (13)

摘要 运算放大器在现代科技的各个领域得到了广泛的应用,针对不同的应用领域出现了不同类型的运放。本文完成了一个由pmos作输入的放大器。vdd为3.3v,负载电容为1pf,增益Av 大于80dB,带宽GBM大于100MHz的放大器。输出级采用共源级结构以提高输出摆幅及驱动能力,为达到较宽的带宽,本文详细分析推导了电路所存在的极零点,共源共栅镜像电流源产生Ibias。选择P沟道晶体管的宽度和长度,使得它们的m g 和ds r 与N沟道晶体管的情况相匹配。 关键字:运算放大器、共源共栅级、极点 Abstract Operation amplifiers are widely used in many field s nowadays。All kinds of differential operation amplifiers appear f6r special application.One basic cell of which is fully differential operation amplifiers is designed in the thesis.Power Supply 3.3v,load capacitor 1pf,Gain>80dB,GBM>100MHz。The output stage is common source amplifier for getting proper DC operation point,for the purpose of wider bandwidth,we carefully analysis the pole and zero in the circuit ,use common source common gate as current Ibias。Choose pmos w/l to make their mg and dsr which can match with nmos。 Kay words:Operation amplifiers、common source common gate、pole

实验一、两级运算放大器的仿真验证 一、实验目的 1、学习集成运算电路单元的设计参数的仿真、测试、验证。 2、学习采用Cadence工具实现IC电路设计的基本操作和方法,包括电路图的编辑以及仿真调试过程。 二、实验内容 本实验通过设计一个两级运算放大器电路学习Cadence工具下电路的设计和仿真方法。实验内容包括: 1.熟悉Cadence界面及基本的建立新的cell文件等基本过程; 2.完成两级运算放大器电路的设计; 3.利用Cadence的仿真环境得到波形,分析仿真结果。 该电路设计采用上华CSMC0.5umCMOS工艺设计,工作电压5V。 三、实验原理 运算放大器是一个能将两个输入电压之差放大并输出的集成电路。运算放大器是模拟电子技术中最常见的电路,在某种程度上,可以把它看成一个类似于BJT或FET 的电子器件。它是许多模拟系统和混合信号系统中的重要组成部分。

它的主要参数包括:开环增益、单位增益带宽、相位阈度、输入阻抗、输入偏流、失调电压、漂移、噪声、输入共模与差模范围、输出驱动能力、建立时间与压摆率、CMRR、PSRR以及功耗等主要包括四部分:第一级输入级放大电路、第二级放大电路、偏置电路和相位补偿电路。 1.共模抑制比:差分放大电路抑制共模信号及放大差模信号的能力,常用 共模抑制比作为一项技术指标来衡量,其定义为放大器对差模信号的电 压放大倍数Aud与对共模信号的电压放大倍数Auc之比,称为共模抑制 比,英文全称是Common Mode Rejection Ratio,因此一般用简写CMRR 来表示,符号为Kcmr,单位是分贝db。 2.共模输入范围:是指在差分放大电路中,二个输入端所加的是大小相 等,极性相同的输入信号叫共模信号,此信号的范围叫共模输入信号范 围。 3.电源抑制比:是输入电源变化量(以伏为单位)与转换器输出变化量 (以伏为单位)的比值(PSRR),常用分贝表示。通常把满量程电压变化 的百分数与电源电压变化的百分数之比称为电源抑制比。 4.输出摆幅:指的是,当输出信号为电压的时候,外部量的变化引起的输 出电压变化。对于无源器件,这个变化通常是从某个负电压到某个正电 压。而对于有源器件,这个变化是相对于某个固定电压,做一定幅度的 上下偏移。(无源器件也可以看作是相对电压0做偏移)。 四、实验步骤 1、登陆到UNIX系统。 在登陆界面,输入用户名stu01和密码123456。 2、Cadence的启动。 登录进去之后,点击Terminal出现窗口,输入icfb命令,启动Cadence软件。 3、根据设计指标及电路结构,估算电路参数。 4、利用Candence原理图的输入。 (1)Composer的启动。在CIW窗口新建一个单元的Schematic视图。 (2)添加器件。在comparator schematic窗口点击Add-Instance或者直

目录 1. 设计指标 (1) 2. 运算放大器主体结构的选择 (1) 3. 共模反馈电路(CMFB)的选择 (1) 4. 运算放大器设计策略 (2) 5. 手工设计过程 (2) 5.1 运算放大器参数的确定 (2) 5.1.1 补偿电容Cc和调零电阻的确定 (2) 5.1.2 确定输入级尾电流I0的大小和M0的宽长比 (3) 5.1.3 确定M1和M2的宽长比 (3) 5.1.4确定M5、M6的宽长比 (3) 5.1.5 确定M7、M8、M9和M10宽长比 (3) 5.1.6 确定M3和M4宽长比 (3) 5.1.7 确定M11、M12、M13和M14的宽长比 (4) 5.1.8 确定偏置电压 (4) 5.2 CMFB参数的确定 (4) 6. HSPICE仿真 (5) 6.1 直流参数仿真 (5) 6.1.1共模输入电压范围(ICMR) (5) 6.1.2 输出电压范围测试 (6) 6.2 交流参数仿真 (6) 6.2.1 开环增益、增益带宽积、相位裕度、增益裕度的仿真 (6) 6.2.2 共模抑制比(CMRR)的仿真 (7) 6.2.3电源抑制比(PSRR)的仿真 (8) 6.2.4输出阻抗仿真 (9) 6.3瞬态参数仿真 (10) 6.3.1 转换速率(SR) (10) 6.3.2 输入正弦信号的仿真 (11) 7. 设计总结 (11) 附录(整体电路的网表文件) (12)

采用折叠式结构的两级全差分运算放大器的设计 1. 设计指标 5000/ 2.5 2.551010/21~22v DD SS L out dias A V V V V V V GB MHz C pF SR V s V V ICMR V P mW μ>==?== >=±=?≤的范围 2. 运算放大器主体结构的选择 图1 折叠式共源共栅两级运算放大器 运算放大器有很多种结构,按照不同的标准有不同的分类。从电路结构来看, 有套筒 式共源共栅、折叠式共源共栅、增益提高式和一般的两级运算放大器等。本设计采用的是如图1所示的折叠式共源共栅两级运算放大器,采用折叠式结构可以获得很高的共模输入电压范围,与套筒式的结构相比,可以获得更大的输出电压摆幅。 由于折叠式共源共栅放大器输出电压增益没有套筒式结构电压增益那么高,因此为了得到更高的增益,本设计采用了两级运放结构,第一级由M0-M10构成折叠式共源共栅结构,第二级由M11-M14构成共源级结构,既可以提高电压的增益,又可以获得比第一级更高的输出电压摆幅。 为了保证运放在闭环状态下能稳定的工作,本设计通过米勒补偿电容Cc 和调零电阻Rz 对运放进行补偿,提高相位裕量! 另外,本文设计的是全差分运算放大器,与单端输出的运算放大器相比较,可以获得更高的共模抑制比,避免镜像极点及输出电压摆幅。 3. 共模反馈电路(CMFB )的选择 由于采用的是高增益的全差分结构,输出共模电平对器件的特性和失配相当敏感,而且不能通过差动反馈来达到稳定,因此,必须增加共模反馈电路(CMFB )来检测两个输出端

运算放大器的电路仿真设计 一、电路课程设计目的 错误!深入理解运算放大器电路模型,了解典型运算放大器的功能,并仿真实现它的功能; 错误!掌握理想运算放大器的特点及分析方法(主要运用节点电压法分析); ○3熟悉掌握Multisim软件。 二、实验原理说明 (1)运算放大器是一种体积很小的集成电路元件,它包括输入端和输出端。它的类型包括:反向比例放大器、加法器、积分器、微分器、电 压跟随器、电源变换器等. (2) (3)理想运放的特点:根据理想运放的特点,可以得到两条原则: (a)“虚断”:由于理想运放,故输入端口的电流约为零,可近似视为断路,称为“虚断”。 (b)“虚短”:由于理想运放A,,即两输入端间电压约为零,可近似视为短路,称为“虚短”. 已知下图,求输出电压。

理论分析: 由题意可得:(列节点方程) 011(1)822A U U +-= 0111 ()0422 B U U +-= A B U U = 解得: 三、 电路设计内容与步骤 如上图所示设计仿真电路. 仿真电路图:

V18mV R11Ω R22Ω R32Ω R44Ω U2 DC 10MOhm 0.016 V + - U3 OPAMP_3T_VIRTUAL U1 DC 10MOhm 0.011 V + - 根据电压表的读数,, 与理论结果相同. 但在试验中,要注意把电压调成毫伏级别,否则结果误差会很大, 致结果没有任何意义。如图所示,电压单位为伏时的仿真结 果:V18 V R11Ω R22Ω R32Ω R44Ω U2 DC 10MOhm 6.458 V + - U3 OPAMP_3T_VIRTUAL U1 DC 10MOhm 4.305 V + - ,与理论结果相差甚远。 四、 实验注意事项 1)注意仿真中的运算放大器一般是上正下负,而我们常见的运放是上负下正,在仿真过程中要注意。

全差分运算放大器设计 岳生生(200403020126) 一、设计指标 以上华0.6um CMOS 工艺设计一个全差分运算放大器,设计指标如下: ?直流增益:>80dB ?单位增益带宽:>50MHz ?负载电容:=5pF ?相位裕量:>60度 ?增益裕量:>12dB ?差分压摆率:>200V/us ?共模电压:2.5V (VDD=5V) ?差分输入摆幅:>±4V 二、运放结构选择

运算放大器的结构重要有三种:(a )简单两级运放,two-stage 。如图2所示;(b )折叠共源共栅,folded-cascode 。如图3所示;(c )共源共栅,telescopic 。如图1的前级所示。本次设计的运算放大器的设计指标要求差分输出幅度为±4V ,即输出端的所有NMOS 管的,DSAT N V 之和小于0.5V ,输出端的所有PMOS 管的,DSAT P V 之和也必须小于0.5V 。对于单级的折叠共源共栅和直接共源共栅两种结构,都比较难达到该 要求,因此我们采用两级运算放大器结构。另外,简单的两级运放的直流增益比较小,因此我们采用共源共栅的输入级结构。考虑到折叠共源共栅输入级结构的功耗比较大,故我们选择直接共源共栅的输入级,最后选择如图1所示的运放结构。两级运算放大器设计必须保证运放的稳定性,我们用Miller 补偿或Cascode 补偿技术来进行零极点补偿。 三、性能指标分析 1、 差分直流增益 (Adm>80db) 该运算放大器存在两级:(1)、Cascode 级增大直流增益(M1-M8);(2)、共源放大器(M9-M12) 第一级增益 1 3 5 11 1357 113 51 3 57 5 3 ()m m m o o o o o m m m m o o o o m m g g g g g g G A R r r r r g g r r r r =-=-=-+ 第二级增益 9 2 2 9112 9 9 11 ()m o o o m m o o g g G A R r r g g =-=-=- + 整个运算放大器的增益: 4 1 3 5 9 1 2 1 3 5 7 5 3 9 11 (80)10m m m m overall o o o o m m o o dB g g g g A A A g g g g r r r r = = ≥++ 2、 差分压摆率 (>200V/us ) 转换速率(slew rate )是大信号输入时,电流输出的最大驱动能力。 定义转换速率SR :

1前言1 2二级运算放大器电路 1 2.1电路结构 1 2.2设计指标 2 3 Cadence仿真软件 3 3.1 schematic原理图绘制 3 3.2 生成测试电路 3 3.3 电路的仿真与分析 4 3.1.1直流仿真 4 3.1.2交流仿真 4 3.4 版图绘制 5 3.4.1差分对版图设计 6 3.4.2电流源版图设计 7 3.4.3负载MOS管版图设计 7 3.5 DRC & LVS版图验证 8 3.5.1 DRC验证 8 3.5.2 LVS验证 8 4结论 9 5参考文献 9

本文利用cadence软件简述了二级运算放大器的电路仿真和版图设计。以传统的二级运算放大器为例,在ADE电路仿真中实现0.16umCMOS工艺,输入直流电源为5v,直流电流源范围27~50uA,根据电路知识,设置各个MOS管合适的宽长比,调节弥勒电容的大小,进入stectre仿真使运放增益达到40db,截止带宽达到80MHz和相位裕度至少为60。。版图设计要求DRC验证0错误,LVS验证使电路图与提取的版图相匹配,观看输出报告,要求验证比对结果一一对应。 关键词:cadence仿真,设计指标,版图验证。 Abstract In this paper, the circuit simulation and layout design of two stage operational amplifier are briefly described by using cadence software. In the traditional two stage operational amplifier as an example, the realization of 0.16umCMOS technology in ADE circuit simulation, the input DC power supply 5V DC current source 27~50uA, according to the circuit knowledge, set up each MOS tube suitable ratio of width and length, the size of the capacitor into the regulation of Maitreya, the simulation of stectre amplifier gain reaches 40dB, the cut-off bandwidth reaches 80MHz and the phase margin of at least 60.. The layout design requires DRC to verify 0 errors, and LVS validation makes the circuit map matching the extracted layout, viewing the output report, and requiring verification to verify the comparison results one by one. Key words: cadence simulation, design index, layout verification.

电子线路CAD短学期 设计报告 学院:电子信息学院 学号: 15041523 班级: 15040211 姓名:卢虎林 日期: 2017年3月11日

一、实验目的 通过一个实例来说明Pspice对设计方案和具体电路进行分析的过程,理解电路的自上而下的设计方法。 二、实验原理 设计一个心电图信号放大器。已知: (1)心电信号幅度在50μV~5mV之间,频率范围为0.032Hz~250Hz。 (2)人体内阻、检测电极板与皮肤的接触电阻(即信号源内阻)为几十千欧。 (3)放大器的输出电压最大值为-5V~+5V。 1、确定总体设计目标 由已知条件(1)可知该放大器的输入信号属于微弱信号,所要求的放大器应具有较高的电压增益和低噪声、低漂移特性。由已知条件(2)可知,为了减轻微弱心电信号源的负载,放大器必须有很高的输入阻抗。另外,为了减小人体接收的空间电磁场的各种信号(即共模信号),要求放大器应具有较高的共模抑制比。因此,最后决定的心电放大器的性能指标如下: 差模电压增益:1000(5V/5mV); 差模输入阻抗: >10MΩ; 共模抑制比:80dB; 通频带:0.05Hz~250Hz。 2、方案设计 根据性能指标要求,要采用多级放大电路,其中前置放大器的设计决定了输入阻抗,共模抑制比和噪声,可选用BiFET型运放,本设计采用了LF4111型运放(其中Avo=4 10 ,Rid≈4 10 Ω,Avc=2),由

于单极同相放大器的共模抑制比无法达到设计要求(可通过Pspice 仿真波形看出),本设计采用了由三个LF411型运放构成的仪用放大器。 第二级放大器的任务是进一步提高放大电路的电压增益,使总增益达到1000。其次为了消除高、低噪声,需要设计一个带通滤波器。因为滤波器没有特殊要求,本设计可采用较简单的一阶高通滤波器和一阶低通滤波器构成的带通滤波器。 3、详细设计 根据上述设计方案,确定了心电放大电路的原理图,如图5-1所示。A1、A2、A3及相应的电阻构成前置放大器,其差模增益被分配为40,其中A1、A2构成的差放被分配为16,其计算公式为:Avd1=(Vo1-Vo2)/Vi=(R1+R2+R3)/R1,Avd2=Vo3/(Vo1-Vo2)=- R6/R4=1.6。 为了避免输入端开路时放大器出现饱和状态,在两个输入端到地之间分别串接两个电阻R11、R22,其取值很大,以满足差模输入阻抗的要求。第二级由 A4及相应的电阻、电容构成。在通带内,其被分配的差模增益应为(1000/40=25),即 Avd3=vo/vo3=1+R10/R9=25 取R9=1KΩ,R10=24KΩ。C1、R8 构成高通滤波器,要求 f =0.05Hz。取R8=1MΩ,则可算出C1=4.58μF,取标称值电容 C1=4.7μF,算得fL=1/(2л C1 R8)=0.034Hz。C2,R10构成低通滤波器,要求f =200Hz。取R10=24KΩ,可算出C2=0.03316μF,取标称值电容C2=0.033μF,最后算出f =1/(2л C2 R10)=251.95Hz。可见满足带宽要求。

二级运算放大器

哈尔滨理工大学 软件学院 模拟IC课程设计报告 课程模拟IC设计 题目二级运算放大器 专业集成电路设计与集成 班级集成10-2班 学生唐贝贝 学号1014020227 指导老师陆学斌 2013年6月14日 目录 1.课程设计目的………………………………………………… 2.课程设计题目描述和要求……………………………………

3.课程设计具体内容…………………………………………… 3.1 设计过程分析…………………………………………… 3.2使用软件………………………………………………… 3.3 原理图…………………………………………………… 3.4 仿真网表………………………………………………… 3.5波形分析………………………………………………… 4.心得体会……………………………………………………… 一、课程设计目的 1.熟悉并掌握Hspice与cosmosScope软件的使用。 2.熟练应用Hspice仿真网表并修改分析网表,学会用comosScope查看 分析波形。 3.锻炼学生独立完成二级运算放大器的能力。 4. 在扎实的基础上强化实践能力,把模拟IC理论实践化。 二、课程设计题目描述和要求 设计指标: 静态功耗:小于5mw 开环增益:大于70dB 单位增益带宽大于5MHz 相位裕量:大于60度 转换速率(SR)大于20V/us 共模抑制比:大于60dB 电源抑制比:大于70dB

输入失调:小于1mV 负载电容:2-4pF 要求: 1、手工计算出每个晶体管的宽长比。通过仿真验证设计是否正确,保证每个晶体管的正常工作状态。 2、使用Hspice工具得到电路相关参数仿真结果,包括:幅频和相频特性(低频增益,相位裕度,单位增益带宽)、CMRR、PSRR、共模输入输出范围、SR 等。 3、每个学生应该独立完成电路设计,设计指标比较开放,如果出现雷同按不及格处理。 4、完成课程设计报告的同时需要提交仿真文件,包括所有仿真电路的网表,仿真结果。 5、相关问题参考教材第六章,仿真问题请查看HSPICE手册。 三、课程设计具体内容 3.1理论计算: 3.2原理图

实验报告 课程名称:电子电路设计与仿真 实验名称:集成运算放大器的运用 班级:计算机18-4班 姓名:祁金文 学号:5011214406 实验目的 1.通过实验,进一步理解集成运算放大器线性应用电路的特点。 2.掌握集成运算放大器基本线性应用电路的设计方法。 3.了解限幅放大器的转移特性以及转移特性曲线的绘制方法。 集成运算放大器放大电路概述 集成电路是一种将“管”和“路”紧密结合的器件,它以半导体单晶硅为芯片,采用专门的制造工艺,把晶体管、场效应管、二极管、电阻和电容等元件及它们之间的连线所组成的完整电路制作在一起,使之具有特定的功能。集成放大电路最初多用于各种模拟信号的运算(如比例、求和、求差、积分、微分……)上,故被称为运算放大电路,简称集成运放。集成运放广泛用于模拟信号的处理和产生电路之中,因其高性价能地价位,在大多数情况下,已经取代了分立元件放大电路。 反相比例放大电路

输入输出关系: 输入电阻: Ri=R1 反相比例运算电路 反相加法运算电路 反相比例放大电路仿真电路图 i o V R R V 12-=i R o V R R V R R V 1 212)1(-+=

压输入输出波形图 同相比例放大电路 输入输出关系: 输入电阻: Ri=∞ 输出电阻: Ro=0 同相比例放大电路仿真电路图 i o V R R V )1(12+=R o V R R V R R V 1 2i 12)1(-+ =

电压输入输出波形图 差动放大电路电路图

差动放大电路仿真电路图 五:实验步骤: 1.反相比例运算电路 (1)设计一个反相放大器,Au=-5V,Rf=10KΩ,供电电压为±12V。 (2)输入f=1kHz、ui=100mV的正弦交流信号,测量相应的uo,

课程设计任务书 学生姓名:专业班级:电信1101班 指导教师:工作单位:信息工程学院 题目: 高输入阻抗放大电路的设计仿真与实现 初始条件: 可选元件:运算放大器,三极管,电阻、电位器、电容、二极管若干,直流电源Vcc= +12V,V EE= -12V,或自选元器件。 可用仪器:示波器,万用表,直流稳压源,毫伏表等。 要求完成的主要任务: (1)设计任务 根据要求,完成对高输入阻抗放大电路的设计、装配与调试,鼓励自制稳压电源。(2)设计要求 ①电压增益>=100,输入信号频率<100HZ,共模抑制比≥60dB; ② 选择电路方案,完成对确定方案电路的设计; ③ 利用Proteus或Multisim仿真设计电路原理图,确定电路元件参数、掌握电 路工作原理并仿真实现系统功能; ④ 安装调试并按规范要求格式完成课程设计报告书; ⑤ 选做:利用仿真软件的PCB设计功能进行PCB设计。 时间安排: 1、前半周,完成仿真设计调试;并制作实物。 2、后半周,硬件调试,撰写、提交课程设计报告,进行验收和答辩。 指导教师签名:年月日 系主任(或责任教师)签名:年月日

目录 摘要 (3) 1.电路方案选择 (4) 2.高输入阻抗放大电路设计 (5) 2.1差分放大电路 (5) 2.1.1零点漂移 (5) 2.1.2差模信号与共模信号 (5) 2.1.3.共模抑制比 (6) 2.1.4差分放大电路的分析 (6) 2.2镜像恒流源 (7) 2.2.1镜像电流源电路特点 (8) 2.2.2镜像电流源电路分析 (8) 2.3同向比例放大电路 (8) 2.4电压串联负反馈 (9) 2.5电路原理设计图 (10) 3.直流稳压电源的设计 (10) 3.1理论分析 (10) 3.2原理图 (11) 3.3直流稳压电源仿真结果 (11) 4高输入阻抗放大电路仿真 (12) 5实物安装和调试 (17) 5.1布局焊接 (17) 5.2调试方法 (17) 5.3测试结果分析 (17) 5.4实物展示 (18) 6. PCB制作 (19) 7.个人总结 (23) 参考文献 (24)

两级运算放大器实验报告 一、实验名称:两级运算放大器 二、实验目的: 1.熟悉掌握Orcad captureCIS的使用方法以及常见的仿真方法和参数设置。 2.利用Orcad captureCIS设计两级运算放大器,并完成要求功能。 3.掌握运算放大器中的增益、带宽、输出摆幅、压摆率、速率、噪声等各个参数之间的折中调试。 三、实验步骤: (一)参数要求: 1.电源电压VCC= 2.7V. 2.CL=10pF. 3.增益Ad>80dB. 4.增益带宽积GW>5M. 5.共模电压输入范围ICMR=1~2V. 6.共模抑制比CMRR>70dB. 7.输出电压摆幅>2V. 8.diss<1mW. 9.SR>10V/us (二)实验步骤及数据: (1)由参数要求,共模电压输入范围为1~2V,电源电压为2.7V,Pdiss<1mW,由这些参数以及相位余度要为60度,由相应的公式估算出来,电路如图所示: 如电路所示,为一个差分输入级与共源放大器组成,采用了密勒补偿,按照计算步骤确定各个元件参数之后,下边进行仿真验证与调试。 (2)交流仿真验证增益带宽是否满足,仿真结果如图所示:

如图结果,增益Av=82dB,增益带宽积GW=6.6M,相位裕度有42度,满足要求,并且还有一定的余量。 (3)交流仿真验证共模电压输入范围ICMR与共模抑制比CMRR是否满足要求,仿真电路如图所示: 1、在仿真验证CMRR之前,先做了一个增益随共模输入电压的变化曲线,大致了解共模电压输入范围,结果如图所示: 如图所示,增益在大于80dB时,共模电压输入范围为0.96V~2.66V,能达到要求,且还有余量。 2、现在仿真验证一下CMRR随共模电压的变化曲线,需要更改仿真电路图,更改的电路图如图所示:

实 验 报 告 册 指导教师邱刚 课程名称模拟电子技术基础 实验名称集成运算放大器的设计 实验类型设计 学院名称电子与信息工程专业电子与信息工程 年级班级 2011级电信3班学生姓名赵明贵 学号 201107014314 成绩 2012年11月29日

实验四集成运算放大器的设计 运算放大器应用电路的设计与制作 一.实验目的 1.掌握运算放大器和滤波电路的基本工作原理; 2.掌握运用运算放大器实现滤波电路的原理方法; 3.会用Multisim10对电路进行仿真分析; 二.实验内容 1.讲解运算放大器和滤波电路的基本工作原理; 2.讲解用运算放大器实现滤波电路的原理方法; 3.用Multisim10对二阶有源低通滤波电路进行仿真分析; 三.实验仪器 Multisim10软件;电阻若干,导线若干,线路板一块,ua741运放两个,万用表,实验箱。 四.实验原理 集成运算放大器是高增益的直流放大器。在它的输入端和输出端之间加上不同的反馈网络,就可以实现各种不同的电路功能。可实现放大功能及加、减、微分、积分、对数、乘、除等模拟运算及其他非线性变换功能;将正、负两种反馈网络相结合,还可具有产生各种模拟信号的功能。 本实验着重以输入和输出之间施加线性负反馈网络后所具有的运算功能进行研究。理想运放在线性运用时具有以下重要特性: (1)理想运放的同相和反相输入端电流近似为零,即。 (2)理想运放在作线性放大时,两输入端电压近似相等,即:。 1.反相放大器 信号由反相端输入,电路如图3-1所示。在理想条件下,放大器的闭环增益。 增益要求确定之后,与的比值即确定,在选择其值时需注意:与不

集成运算放大器放大电路仿真设计 1集成运算放大器放大电路概述 集成电路是一种将“管”和“路”紧密结合的器件,它以半导体单晶硅为芯片,采用专门的制造工艺,把晶体管、场效应管、二极管、电阻和电容等元件及它们之间的连线所组成的完整电路制作在一起,使之具有特定的功能。集成放大电路最初多用于各种模拟信号的运算(如比例、求和、求差、积分、微分……)上,故被称为运算放大电路,简称集成运放。集成运放广泛用于模拟信号的处理和产生电路之中,因其高性价能地价位,在大多数情况下,已经取代了分立元件放大电路。 2 电路原理分析 2.1 电路如图1所示 R1 10kΩV1 500mV U1A TL082CD 3 2 4 8 1 R2 9.1kΩ RF 100kΩ V2 12 V V3 12 V XMM1 1 此电路为反向比例运算电路,这是电压并联负反馈电路。输入电压V1通过电阻R1作用于集成运放的反相输入端,故输出电压V0与V1反相。 图2 仿真结果图 输入输出关系理论输仿真输出值电路功能

其中 1 //2R RF R = 2.2电路如图3所示 R1 10kΩ Ui2 200mV U1A TL082CD 3 2 4 8 1 R24.7kΩ RF 100kΩ V212 V V312 V XMM1 Ui1 100mV R310kΩ 3 此电路为反相求和运算电路,其电路的多个输入信号均作用于集成运放的反相输入端,根据“虚短”和“虚断”的原则,0==p N u u ,节点N 的电流方程为F i i i =+31 所以)1 2 31( 0R Ui R Ui RF U +-= 输入输出关系 理论输出值 仿真输出值 电路功能 )1 2 31( 0R Ui R Ui RF U +-= -3V 2.999V 反相求和放大电路 其中RF R R R //3//12= 2.3电路如图5所示 出值 11 0V R RF V -= -5V -5V 反相比例运算电路

运算放大器应用电路的设计与制作 运算放大器 1.原理 运算放大器是目前应用最广泛的一种器件,当外部接入不同的线性或非线性元器件组成输入和负反馈电路时,可以灵活地实现各种特定的函数关系。在线性应用方面,可组成比例、加法、减法、积分、微分、对数等模拟运算电路。 运算放大器一般由4个部分组成,偏置电路,输入级,中间级,输出级。 图1运算放大器的特性曲线 图2运算放大器输入输出端图示 图1是运算放大器的特性曲线,一般用到的只是曲线中的线性部分。如图2所示。U -对应的端子为“-”,当输入U -单独加于该端子时,输出电压与输入电压U -反相,故称它为反相输入端。U +对应的端子为“+”,当输入U +单独由该端加入时,输出电压与U +同相,故称它为同相输入端。 输出:U 0= A(U +-U -) ; A 称为运算放大器的开环增益(开环电压放大倍数)。 在实际运用经常将运放理想化,这是由于一般说来,运放的输入电阻很大,开环增益也很大,输出电阻很小,可以将之视为理想化的,这样就能得到:开环电压增益A ud =∞;输入阻抗r i =∞;输出阻抗r o =0;带宽f BW =∞;失调与漂移均为零等理想化参数。 理想运放在线性应用时的两个重要特性 输出电压U O 与输入电压之间满足关系式:U O =A ud (U +-U -),由于A ud =∞,而U O 为有限值,因此,U +-U -≈0。即U +≈U -,称为“虚短”。 由于r i =∞,故流进运放两个输入端的电流可视为零,即I IB =0,称为“虚断”,这说明运放对其前级吸取电流极小。

上述两个特性是分析理想运放应用电路的基本原则,可简化运放电路的计算。 运算放大器的应用 (1)比例电路 所谓的比例电路就是将输入信号按比例放大的电路,比例电路又分为反向比例电路、同相比例电路、差动比例电路。 (a) 反向比例电路 反向比例电路如图3所示,输入信号加入反相输入端: 图3反向比例电路电路图 对于理想运放,该电路的输出电压与输入电压之间的关系为: 为了减小输入级偏置电流引起的运算误差,在同相输入端应接入平衡电阻 R ’=R 1 // R F 。 输出电压U 0与输入电压U i 称比例关系,方向相反,改变比例系数,即改变两个电阻的阻值就可以改变输出电压的值。反向比例电路对于输入信号的负载能力有一定的要求。 (b) 同向比例电路 同向比例电路如图4所示,跟反向比例电路本质上差不多,除了同向接地的一段是反向输入端: 图4 同相比例电路电路图 i 1 f O U R R U -=

电子课程实验报告题目:基于Mulitisim的集成运算放大器应用电路仿真

设计目的 1、集成运算放大电路当外部接入不同的线性或非线性元器件组成输入和负 反馈电路时,可以灵活地实现各种特定的函数关系,在线性应用方面,可组成比例、加法、减法、积分、微分等模拟运算电路。 2、本课程设计通过Mulitisim编写程序几种运算放大电路仿真程序,通过输 入不同类型与幅度的波形信号,测量输出波形信号对电路进行验证,并利用Protel软件对实现对积累运算放大电路的设计,并最终实现PC板图形式。 二、电路的理论知识 1.反相放大器 图1中所示的电路是最常见的运放电路,它显示出了如何在牺牲增益的条件下获得稳定,线性的放大器。标号为R f的反馈电阻用于将输出信号反馈作用于输入端,反馈电阻连接到负输入端表示电路为负反馈连接。输入电压V1通过输入电阻R1产生了一个输入电路i1。电压差△V加载在+、—输入端之间,放大器的正输入端接地。 图1 利用回路公式计算传输特性:

输入回路: V R i V ?+=111 (2) 反馈回路: V R i V f f out ?+-= (3) 求和节点 in f i i i +-=1 (4) 增益公式: V A V out ??-= (5) 由以上4个式子可以得到输出: Z R V Z i V in out /)/(/11-= (6) 式中,闭环阻抗Z=1/R f +1/AR f +1/R f 。 反馈电阻和输入电阻通常都较大)(Ωk 级,并且A 很大(大于100000),因此Z=1/R f 。更进一步,△V 通常很小(几微伏)且放大器的输入阻抗Z in 很大(大约ΩM 10),那么输入输入电流(I in =△V/Z in )非常小,可以认为为零。则传输曲线变为: 111)()/(V G V R R V f out -=-= (7) 式中,R f /R 1的比值称为闭环增益G ,负号表示输出反向。闭环增益可以通过选择两个电阻R f 和R 1来设定。 2.同相比例运放电路 同向比例运放电路组成如图2所示 ,将输入电阻R 1接地,并且将输入信号加载道+输入端。 图2 电压在通过由反馈电阻R f 和输入电阻R 1组成的分压电路的时候产生压降,中间位置的电压V -为: out f V R R R V ))/((11+=- (8) 根据理想运放的性质1,运放的输入电压△V 为零,因此V in =V -。重新排列公式