1、(5分)基于第一章所描述的摩尔定律,请你预言到2015年的时候CPU的时钟频率和晶体管个

数(复杂度),以及到时候单个芯片的FlASH所能存储的容量为多少(U盘最大能做到多大)。2、(5分)列举你所知道的现在最高端的cpu,DSP芯片,FPGA芯片,DRAM(内存),FLASH的

时钟频率和复杂度。

3、(5分)芯片成本有哪些构成。作为集成电路设计工程师,如何降低芯片的成本?

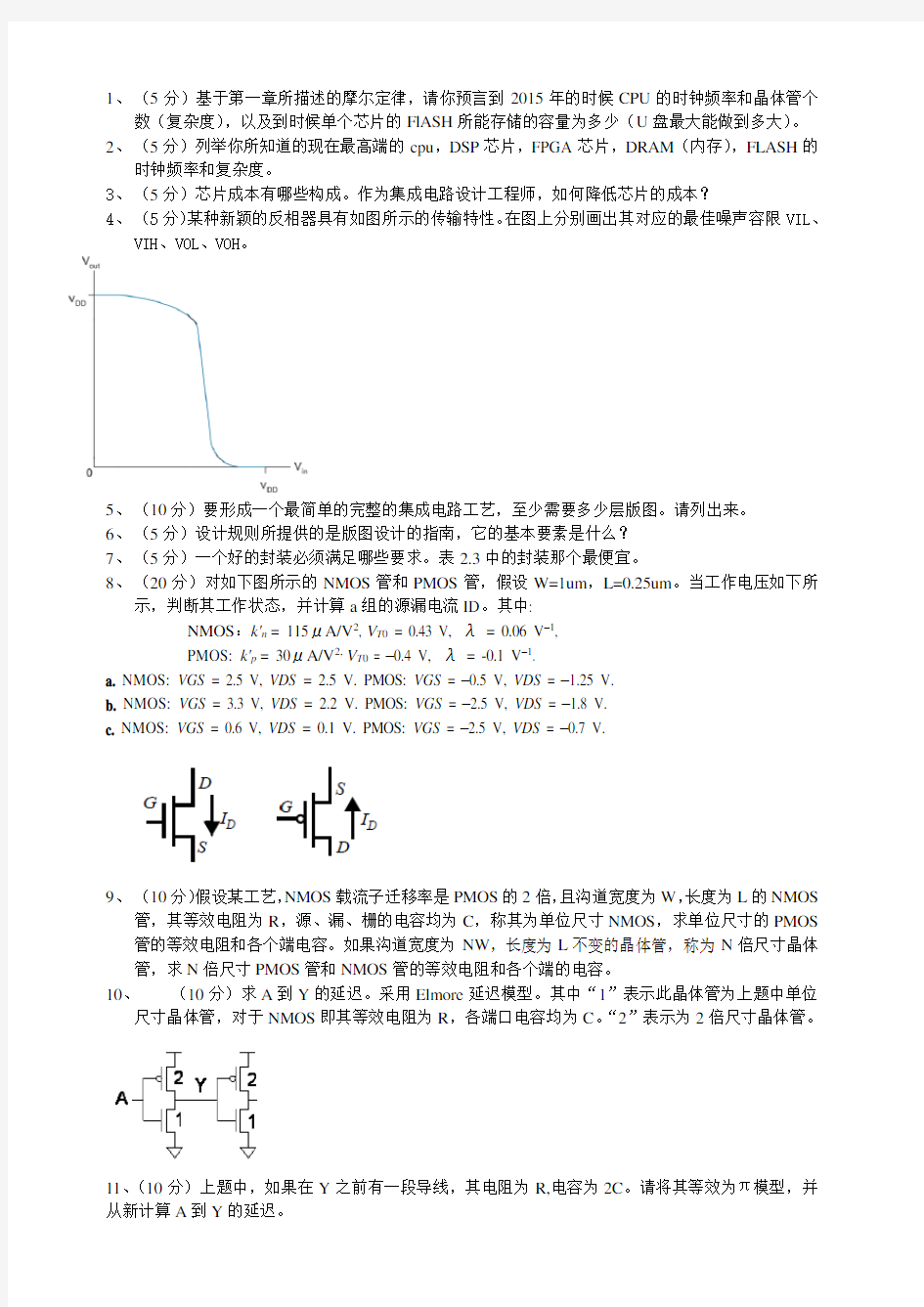

4、(5分)某种新颖的反相器具有如图所示的传输特性。在图上分别画出其对应的最佳噪声容限VIL、

VIH、VOL、VOH。

5、(10分)要形成一个最简单的完整的集成电路工艺,至少需要多少层版图。请列出来。

6、(5分)设计规则所提供的是版图设计的指南,它的基本要素是什么?

7、(5分)一个好的封装必须满足哪些要求。表2.3中的封装那个最便宜。

8、(20分)对如下图所示的NMOS管和PMOS管,假设W=1um,L=0.25um。当工作电压如下所

示,判断其工作状态,并计算a组的源漏电流ID。其中:

NMOS:k'n= 115μA/V2, V T0 = 0.43 V, λ= 0.06 V–1,

PMOS: k'p= 30μA/V2,V T0 = –0.4 V, λ= -0.1 V–1.

a. NMOS: VGS = 2.5 V, VDS = 2.5 V. PMOS: VGS = –0.5 V, VDS = –1.25 V.

b. NMOS: VGS = 3.3 V, VDS = 2.2 V. PMOS: VGS = –2.5 V, VDS = –1.8 V.

c. NMOS: VGS = 0.6 V, VDS = 0.1 V. PMOS: VGS = –2.5 V, VDS = –0.7 V.

9、(10分)假设某工艺,NMOS载流子迁移率是PMOS的2倍,且沟道宽度为W,长度为L的NMOS

管,其等效电阻为R,源、漏、栅的电容均为C,称其为单位尺寸NMOS,求单位尺寸的PMOS 管的等效电阻和各个端电容。如果沟道宽度为NW,长度为L不变的晶体管,称为N倍尺寸晶体管,求N倍尺寸PMOS管和NMOS管的等效电阻和各个端的电容。

10、(10分)求A到Y的延迟。采用Elmore延迟模型。其中“1”表示此晶体管为上题中单位

尺寸晶体管,对于NMOS即其等效电阻为R,各端口电容均为C。“2”表示为2倍尺寸晶体管。

11、(10分)上题中,如果在Y之前有一段导线,其电阻为R,电容为2C。请将其等效为π模型,并从新计算A到Y的延迟。

第一章 集成电路的测试 1.集成电路测试的定义 集成电路测试是对集成电路或模块进行检测,通过测量对于集成电路的输出回应和预期输出比较,以确定或评估集成电路元器件功能和性能的过程,是验证设计、监控生产、保证质量、分析失效以及指导应用的重要手段。 .2.集成电路测试的基本原理 输入Y 被测电路DUT(Device Under Test)可作为一个已知功能的实体,测试依据原始输入x 和网络功能集F(x),确定原始输出回应y,并分析y是否表达了电路网络的实际输出。因此,测试的基本任务是生成测试输入,而测试系统的基本任务则是将测试输人应用于被测器件,并分析其输出的正确性。测试过程中,测试系统首先生成输入定时波形信号施加到被测器件的原始输入管脚,第二步是从被测器件的原始输出管脚采样输出回应,最后经过分析处理得到测试结果。 3.集成电路故障与测试 集成电路的不正常状态有缺陷(defect)、故障(fault)和失效(failure)等。由于设计考虑不周全或制造过程中的一些物理、化学因素,使集成电路不符合技术条件而不能正常工作,称为集成电路存在缺陷。集成电路的缺陷导致它的功能发生变化,称为故障。故障可能使集成电路失效,也可能不失效,集成电路丧失了实施其特定规范要求的功能,称为集成电路失效。故障和缺陷等效,但两者有一定区别,缺陷会引发故障,故障是表象,相对稳定,并且易于测试;缺陷相对隐蔽和微观,缺陷的查找与定位较难。 4.集成电路测试的过程 1.测试设备 测试仪:通常被叫做自动测试设备,是用来向被测试器件施加输入,并观察输出。测试是要考虑DUT的技术指标和规范,包括:器件最高时钟频率、定时精度要求、输入\输出引脚的数目等。要考虑的因素:费用、可靠性、服务能力、软件编程难易程度等。 1.测试界面 测试界面主要根据DUT的封装形式、最高时钟频率、ATE的资源配置和界面板卡形等合理地选择测试插座和设计制作测试负载板。

2014—2015学年度《数电》期中考试试卷 班别 姓名: 学号: 题 号 一 二 三 四 五 总 分 得 分 一、 填空题(每空1分,共25分) 1、常用数制有十进制、 、 等。 2、在逻辑代数中,A+1= ;B+B = 。 3、数字电路的基本逻辑关系有 、 、 ,基本逻辑运算有 、 、 。 4、逻辑代数中的变量只有 和 两种取值。 5、(123.75)10= ( )2 6、(1010110010011)2= ( )16 7、(10110)2=( )10 8、数字电路中基本逻辑门是 、 、 。常用的复合门电路有 、 、 、 。 9、与非门实现的逻辑功能为 。异或门实现的逻辑功能是 。 10、如果把两输入与非门的两个输入端连在一起使用,它将成为一个 门。 二、 选择题(每题2分,共20分) 1、逻辑代数中的摩根定律可表示为C B A ??=( )。 A 、C B A ++ B 、A ·B · C C 、A +B +C D 、A +B ·C 2、有10101的二进制代码,表示十进制数为( )。 A 、11 B 、21 C 、25 D 、17 — 3、图中这个电路实现什么功能( ) A 、Y=1 B 、Y=0 C 、Y=A D 、Y= A 4、模拟电路与脉冲电路的不同在于( ) 模拟电路的晶体管多工作在开关状态 脉冲电路的晶体管多工作在饱和状态 模拟电路的晶体管多工作在截止状态 脉冲电路的晶体管多工作在开关状态 ≥1 A Y

5、若逻辑函数L=A+ABC+BC+B C,则L可化简为() A、L=A+BC B、L=A+C C、L=AB+B C D、L=A 6、在何种输入情况下,“或非”运算的结果是逻辑0,不正确的是( ) A.全部输入是0 B.全部输入是1 C.任一输入为0,其他输入为1 D.任一输入为1,其他输入为0。 7、.一位十六进制数可以用多少位二进制数来表示?() A.1 B.2 C.4 D. 16 8、以下表达式中符合逻辑运算法则的是() A.C·C=C2 B.1+1=10 C.0<1 D.A+1=1 9、四位16进制数最大的数是() A.1111 B .7777 C. FFFF D 都不是 10、以下表达式中符合逻辑运算法则的是()

第三章、器件 一、超深亚微米工艺条件下MOS 管主要二阶效应: 1、速度饱和效应:主要出现在短沟道NMOS 管,PMOS 速度饱和效应不显著。主要原因是 TH G S V V -太大。在沟道电场强度不高时载流子速度正比于电场强度(μξν=) ,即载流子迁移率是常数。但在电场强度很高时载流子的速度将由于散射效应而趋于饱和,不再随电场 强度的增加而线性增加。此时近似表达式为:μξυ=(c ξξ<),c s a t μξυυ==(c ξξ≥) ,出现饱和速度时的漏源电压D SAT V 是一个常数。线性区的电流公式不变,但一旦达到DSAT V ,电流即可饱和,此时DS I 与GS V 成线性关系(不再是低压时的平方关系)。 2、Latch-up 效应:由于单阱工艺的NPNP 结构,可能会出现VDD 到VSS 的短路大电流。 正反馈机制:PNP 微正向导通,射集电流反馈入NPN 的基极,电流放大后又反馈到PNP 的基极,再次放大加剧导通。 克服的方法:1、减少阱/衬底的寄生电阻,从而减少馈入基极的电流,于是削弱了正反馈。 2、保护环。 3、短沟道效应:在沟道较长时,沟道耗尽区主要来自MOS 场效应,而当沟道较短时,漏衬结(反偏)、源衬结的耗尽区将不可忽略,即栅下的一部分区域已被耗尽,只需要一个较小的阈值电压就足以引起强反型。所以短沟时VT 随L 的减小而减小。 此外,提高漏源电压可以得到类似的效应,短沟时VT 随VDS 增加而减小,因为这增加了反偏漏衬结耗尽区的宽度。这一效应被称为漏端感应源端势垒降低。

4、漏端感应源端势垒降低(DIBL): VDS增加会使源端势垒下降,沟道长度缩短会使源端势垒下降。VDS很大时反偏漏衬结击穿,漏源穿通,将不受栅压控制。 5、亚阈值效应(弱反型导通):当电压低于阈值电压时MOS管已部分导通。不存在导电沟道时源(n+)体(p)漏(n+)三端实际上形成了一个寄生的双极性晶体管。一般希望该效应越小越好,尤其在依靠电荷在电容上存储的动态电路,因为其工作会受亚阈值漏电的严重影响。 绝缘体上硅(SOI) 6、沟长调制:长沟器件:沟道夹断饱和;短沟器件:载流子速度饱和。 7、热载流子效应:由于器件发展过程中,电压降低的幅度不及器件尺寸,导致电场强度提高,使得电子速度增加。漏端强电场一方面引起高能热电子与晶格碰撞产生电子空穴对,从而形成衬底电流,另一方面使电子隧穿到栅氧中,形成栅电流并改变阈值电压。 影响:1、使器件参数变差,引起长期的可靠性问题,可能导致器件失效。2、衬底电流会引入噪声、Latch-up、和动态节点漏电。 解决:LDD(轻掺杂漏):在漏源区和沟道间加一段电阻率较高的轻掺杂n-区。缺点是使器件跨导和IDS减小。 8、体效应:衬底偏置体效应、衬底电流感应体效应(衬底电流在衬底电阻上的压降造成衬偏电压)。 二、MOSFET器件模型 1、目的、意义:减少设计时间和制造成本。 2、要求:精确;有物理基础;可扩展性,能预测不同尺寸器件性能;高效率性,减少迭代次数和模拟时间 3、结构电阻:沟道等效电阻、寄生电阻 4、结构电容: 三、特征尺寸缩小 目的:1、尺寸更小;2、速度更快;3、功耗更低;4、成本更低、 方式: 1、恒场律(全比例缩小),理想模型,尺寸和电压按统一比例缩小。 优点:提高了集成密度 未改善:功率密度。 问题:1、电流密度增加;2、VTH小使得抗干扰能力差;3、电源电压标准改变带来不便;4、漏源耗尽层宽度不按比例缩小。 2、恒压律,目前最普遍,仅尺寸缩小,电压保持不变。 优点:1、电源电压不变;2、提高了集成密度 问题:1、电流密度、功率密度极大增加;2、功耗增加;3、沟道电场增加,将产生热载流子效应、速度饱和效应等负面效应;4、衬底浓度的增加使PN结寄生电容增加,速度下降。 3、一般化缩小,对今天最实用,尺寸和电压按不同比例缩小。 限制因素:长期使用的可靠性、载流子的极限速度、功耗。

一级电阻分选电路的设计 摘要 本设计充分利用了现代集成芯片技术,采用了阻抗变换和比较的方法,其结果简单、控制可靠、使用方便、具有很高的灵敏性,又不易产生错误。具有很高的使用价值。 主要运用桥式整流电路,窗口比较电路和显示电路等基本电路,并利用三端稳压器稳定输出电压,并通过窗口比较电路输出高低电平,再通过LED显示电路显示出合适的电阻,从而方便快捷的挑选出一级电阻。本设计主要运用的芯片有W7805,W7905,CD4001,LM324D等。整体设计遵循硬件工程的方法,经过需求分析,总体设计,安装调试,模块测试和系统实现几个阶段。 关键词:稳压电路,窗口比较器,CD4001,电阻测量

目录 1 课题描述 (1) 2 设计方案 (1) 2.1电源电路设计 (2) 2.2检测电路 (2) 2.3显示电路 (5) 3元件选择 (5) 3.1 三端稳压器 (5) 3.2 LM324四运放 (6) 3.3 四输入或非门 (6) 4整体电路 (7) 总结 (8) 致谢 (9) 参考文献 (10)

1 课题描述 随着工业的快速发展,很多东西得到了批量的生产。但是,这就给质量检验增加了难度。过去的微电子技术已经不能满足现状所需,因此微电子技术的发展应运而生,新的测试方法,新的测试理论,新的测试领域以及新的测试领域不断出现,在许多方面已经冲破了传统仪器的观念,电子仪器的功能和作用发生了质的变化。因此,如何快速而又高效的检测便成了人们关注的问题。比如,生产出来的电阻由于各种原因而造成在一定范围内浮动,如何筛选变化在0.95~1.05范围内的合格电阻而抛弃那些不合格的电阻。本设计是对电阻进行检测,有电源部分,检测部分和显示部分构成。并且,此设计可以直接加载在220V 交流电上。其中,电源部分由整流桥整流和三态稳压管进行稳压,以输出+/- 5V 的直流电压,用以检测电路模块的工作。检测部分通过选定门限电压、标准电阻,通过窗口比较器进行比较,就可以快速而又准确的检测出被测电阻是否合格。 2 设计方案 整个电路系统如图1所示,由电源部分、检测部分和显示部分三部分构成[1]。 图1 整体电路框图 电源模块由桥式整流、电容滤波和三端集成稳压块W7805和W7809等部分组成,可使输出电压为+/-5V 。检测电路由LM324四运放集成芯片构成,其中一个运放作为电压跟随器事项阻抗变换,另外两个运放组成窗口比较器。 由门限电

数字电路期中试卷(答案)

第 2 页共 11 页

第 3 页共 11 页

第 4 页 共 11 页 三、简答题 (每小题5分,共25分) 1、用真值表证明等式:)(B A ⊕⊙A C =⊙)(C B ⊕ 证明:真值表如下: 由上述真值表(的后两列)知:)(B A ⊕⊙A C =⊙)(C B ⊕ 2、用代数法化 简函数: ADCBD D C B C B ABD D ABC L +++?+=)( 解: C B AB A C B A D A C B C AD AC B C B ABD ABC D C B C B ABD ABC D C B C B ABD ABCD D ABC ADCBD D C B C B ABD D ABC L +=+=++=++=++=+++=+++++=+++?+=)()()()()( 3、用卡诺图法化简函数: ∑∑+=)96,3,21()15,1312,111075,0(),,,(,,d ,,,,m D C B A R 解:画出卡诺图并化简,得

第 5 页 共 11 页 D C B C AB B A R +++= 4、分析下列功能表,说明其功能。 解:由功能表知: (1)功能表是4线-2线优先编码器的功能表; (2)此优先编码器有1个输入使能控制端E ,高电平有效; (3)有4个输入端,优先级别从3 I 、2I 、1 I 、0 I 依次降低,且为高电平有效; (4)有1个输出指示端GS ,低电平有效; (5)有2个输出端1Y 、0 Y ,高电平有效,权值分别为2、1。 (6)优先编码器的输出为: 321I I Y +=,3 210I I I Y +=,

H a r b i n I n s t i t u t e o f T e c h n o l o g y 集成电路测试原理及方法简介 院系:电气工程及自动化学院 姓名: XXXXXX 学号: XXXXXXXXX 指导教师: XXXXXX 设计时间: XXXXXXXXXX

摘要 随着经济发展和技术的进步,集成电路产业取得了突飞猛进的发展。集成电路测试是集成电路产业链中的一个重要环节,是保证集成电路性能、质量的关键环节之一。集成电路基础设计是集成电路产业的一门支撑技术,而集成电路是实现集成电路测试必不可少的工具。 本文首先介绍了集成电路自动测试系统的国内外研究现状,接着介绍了数字集成电路的测试技术,包括逻辑功能测试技术和直流参数测试技术。逻辑功能测试技术介绍了测试向量的格式化作为输入激励和对输出结果的采样,最后讨论了集成电路测试面临的技术难题。 关键词:集成电路;研究现状;测试原理;测试方法

目录 一、引言 (4) 二、集成电路测试重要性 (4) 三、集成电路测试分类 (5) 四、集成电路测试原理和方法 (6) 4.1.数字器件的逻辑功能测试 (6) 4.1.1测试周期及输入数据 (8) 4.1.2输出数据 (10) 4.2 集成电路生产测试的流程 (12) 五、集成电路自动测试面临的挑战 (13) 参考文献 (14)

一、引言 随着经济的发展,人们生活质量的提高,生活中遍布着各类电子消费产品。电脑﹑手机和mp3播放器等电子产品和人们的生活息息相关,这些都为集成电路产业的发展带来了巨大的市场空间。2007年世界半导体营业额高达2.740亿美元,2008世界半导体产业营业额增至2.850亿美元,专家预测今后的几年随着消费的增长,对集成电路的需求必然强劲。因此,世界集成电路产业正在处于高速发展的阶段。 集成电路产业是衡量一个国家综合实力的重要重要指标。而这个庞大的产业主要由集成电路的设计、芯片、封装和测试构成。在这个集成电路生产的整个过程中,集成电路测试是惟一一个贯穿集成电路生产和应用全过程的产业。如:集成电路设计原型的验证测试、晶圆片测试、封装成品测试,只有通过了全部测试合格的集成电路才可能作为合格产品出厂,测试是保证产品质量的重要环节。 集成电路测试是伴随着集成电路的发展而发展的,它为集成电路的进步做出了巨大贡献。我国的集成电路自动测试系统起步较晚,虽有一定的发展,但与国外的同类产品相比技术水平上还有很大的差距,特别是在一些关键技术上难以实现突破。国内使用的高端大型自动测试系统,几乎是被国外产品垄断。市场上各种型号国产集成电路测试,中小规模占到80%。大规模集成电路测试系统由于稳定性、实用性、价格等因素导致没有实用化。大规模/超大规模集成电路测试系统主要依靠进口满足国内的科研、生产与应用测试,我国急需自主创新的大规模集成电路测试技术,因此,本文对集成电路测试技术进行了总结和分析。 二、集成电路测试重要性 随着集成电路应用领域扩大,大量用于各种整机系统中。在系统中集成电路往往作为关键器件使用,其质量和性能的好坏直接影响到了系统稳定性和可靠性。 如何检测故障剔除次品是芯片生产厂商不得不面对的一个问题,良好的测试流程,可以使不良品在投放市场之前就已经被淘汰,这对于提高产品质量,建立生产销售的良性循环,树立企业的良好形象都是至关重要的。次品的损失成本可以在合格产品的售价里得到相应的补偿,所以应寻求的是质量和经济的相互制衡,以最小的成本满足用户的需要。 作为一种电子产品,所有的芯片不可避免的出现各类故障,可能包括:1.固定型故障;2.跳变故障;3.时延故障;4.开路短路故障;5桥接故障,等等。测试的作用是检验芯片是否存在问题,测试工程师进行失效分析,提出修改建议,从工程角度来讲,测试包括了验证测试和生产测试两个主要的阶段。

高校实验室IC集成电路芯片测试 解决方案 在高校的教学实验环节,需要大量地使用一些基本功能的集成芯片。譬如74/54系列的门电路,AD/DA芯片,放大器,比较器,二极管,三极管,光耦,接口芯片等。 由于学生初学电路,使用过程中,存在很多偶然的低级错误,造成芯片的损伤,给后面的实验造成很多麻烦,所以在实验过程中,为了排除这类因素,节省教学时间,需要用专用的amdtech芯片测试仪器对芯片的功能进行校验。除此之外,此测试仪支持芯片自动查找功能,查找成功后会自动显示芯片的型号。测试仪软硬件独立设计,芯片库可在线实时更新,简单易用。可根据用户提供的芯片,进行测试(需定制)。 1.1方案特色 1.基于标准USB接口,即插即用; 2.标准40脚锁扣插座,最大可测40脚的IC; 3.系统带自检功能,芯片型号可自动判别; 4.可测试74/54系列TTL芯片,4000/4500系列CMOS芯片; 5.可测试放大器,比较器,二极管,三极管,光耦,接口 芯片等集成电路芯片;

6.可测试常用的AD、DA芯片; 7.驱动程序支持win2000/winxp/win2003/win7/win8/ win10; 8.测试仪软硬件独立设计,芯片库可在线实时更新,简单 易用; 9.可根据用户提供的芯片,进行测试(需定制)。 1.2方案使用 1.首先安装软件,安装完成后,插入芯片测试仪,系统会自动提示安装驱动设备,按照提示,使用自动安装。 测试芯片时,不管什么类型的芯片,都是底部对齐,缺口朝上,如下图所示:

2.运行芯片测试仪软件。 测试步骤如下: (1)在【选择类型】下拉框里面,选择芯片的类型 (2)选择好类别后,在【选择器件】列表框里选择具体的待测 试芯片型号。 (3)选中芯片后,点击【测试】按钮,这时测试仪 的“ready”指示灯会点亮。软件会自动测试指定芯 片的好坏。 (4)如果芯片字迹模糊,而无法知道具体芯片型号 时,可以选择【自动扫描测试】按钮,软件会自动从 芯片库里面进行比对,如果对应上了具体型号,会自 动提示芯片的型号。 注:【自动扫描测试】是扫描当前类别里面的器件,

中国集体经济 CHINA COLLECTIVEECONOMY 势、消除劣势、抓住机会、规避威胁。 (一)内部环境分析 1.农村信用社的优势。(1)地域优势;(2)政策优势;(3)决策优势;(4)网点优势;(5)人员优势。 2.农村信用社的劣势。(1)历史包袱重,不良资产占比高;(2)规模小,风险管理能力低;(3)经营区域受限;(4)人员素质仍是短板;(5)金融创新能力不足;(6) 市场定位仍不明确。 (二)外部环境分析 1.机会。(1)支农惠农政策为农信社提供了更广阔的发展空间;(2)当地社会影响力大;(3)行业管理水平的提高,有力 推动了农信社的发展。 2.威胁。(1)行业竞争者多,同业竞争压力大;(2)宏观经济下行,客户违约风险增加;(3)利率市场化进程的推进增加了农信社的财务压力和经营风险;(4)人才流失仍是重要威胁;(5)影子银行的威胁。 (三)农信社的SWOT 分析 首先制定出农信社的SWOT 矩阵,如表1所示。 将SWOT 矩阵进行分解,对SO ———优势与机会、WO ———劣势与机会、ST ——— 优势与威胁、WT ———劣势与威胁等条件进行分析,并根据分析找出相应的可选择的目标市场。 1.基于SO 战略应确定的贷款目标市 场:利用地域、网点、人员优势,挖掘、深耕各类个人贷款市场;利用地域、网点、人员、决策优势,做好公司贷款的拓展。 2.基于WO 战略应确定的贷款目标 市场:拓展全部个人贷款市场,增加积累,消化不良;积极介入公司贷款市场中的中小微企业市场,但根据自身风险管理能力以及资本的承受能力,要做好单户额度的控制,大型企业谨慎进入;受风险管理水平、人员素质制约,企业贷款市场以流动资金贷款市场为主,固定资产贷款市场谨慎进入;受风险管理水平、人员素质制约,贸易型公司谨慎进入。 3.基于ST 战略应确定的贷款目标市 场:全部个人贷款市场。一方面提高服务水平,提高客户贷款便利度,另一方面强化风险控制;企业贷款市场中的中小微企 业,但要注意行业风险,做好成本测算;大型企业贷款市场谨慎进入,避免议价能力不足,降低资金运用效率;生产加工型企业贷款市场要提高风险管控意识;铺底性流动资金贷款市场以及固定资产贷款市场谨慎进入。 4.基于WT 战略应确定的贷款目标 市场:出于风险管理、风险承受能力以及资金收益考虑,大型公司贷款市场应谨慎进入;企业贷款市场中的中小微企业,但要注意行业风险,做好成本测算;生产加工型企业贷款市场要提高风险管控意识;铺底性流动资金贷款市场以及固定资产贷款市场谨慎进入。 通过SWOT 分析,得出农信社应确定的目标市场:积极拓展个人贷款市场,但要提高贷款便利度,加强风险控制;将公司类贷款市场中的中小微企业作为重要的市场目标,但要根据自身风险管理能力以及资本的承受能力,做好单户额度的控制。要注意防范行业风险。企业固定资产贷款市场、铺底性流动资金贷款市场等要谨慎进入;出于风险管理、风险承受能力以及资金收益率考虑,大型公司类贷款市场要谨慎进入。总之,农信社应选择个 人及中小微企业贷款市场为目标市场,但要控制中小企业的单户额度限制,求小、求散。 (作者单位:山东省农村信用社联合社) 摘要:近年来,集成电路封装测试行业技术进步较快,行业发展也十分迅速,一些内资和本土品牌企业的质量、技术和产能已经接近国际先进水平。未来国内集成电路封测市场增长前景广阔,但也需要应对各种挑战。国内封测企业必须进一步增强技术创新能力、加大成本管控,才能在日新月异的市场竞争中取得更大进步。 关键词:技术进步;行业发展前景;经营模式;核心竞争力 一、集成电路封装测试的技术进步封装测试是集成电路制造的后续工艺,为了使集成电路芯片的触点能与外界电路如PCB 板连接,也为了给芯片加上一个“保护壳”,防止芯片受到物理或化学损坏,需要对晶圆芯片的进一步加工,这一环节即封装环节。测试环节则是对芯片电子电路功能的检测确认。 集成电路封装技术发展历程大约可以分为三个阶段:第一阶段是1980年之 前的通孔插装(THD)时代,插孔直接安装到PCB 上,主要形式包括TO(三极管)、 DIP(双列直插封装),优点是可靠、散热好、结实、功耗大,缺点是功能较少,封装密度及引脚数难以提高,难以满足高效自动化生产的要求。 第二阶段是1980年代开始的表面贴装(SMT )时代,该阶段技术的主要特点是引线代替针脚,引线采用翼形或丁形,以两边或四边引线封装为主,从两边或四边表1 农信社的SWOT 矩阵 优势(S ) 劣势(W ) 机会(O )SO 战略 发挥优势,把握机会 WO 战略 利用外部机会,弥补内部劣势 威胁(T ) ST 战略 发挥优势,规模外部威胁 WT 战略减少劣势,规避威胁 ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, 我国集成电路封装测试行业的研究 ■ 尤晟 张燕 53

数字电子技术基础期末考试试卷及答案 Document serial number【KKGB-LBS98YT-BS8CB-BSUT-BST108】

数字电子技术基础试题(一) 一、填空题 : (每空1分,共10分) 1. 10 = ( ) 2 = ( ) 16 。 2 . 逻辑函数L = + A+ B+ C +D = 1 。 3 . 三态门输出的三种状态分别为:、和。 4 . 主从型JK触发器的特性方程= 。 5 . 用4个触发器可以存储位二进制数。 6 . 存储容量为4K×8位的RAM存储器,其地址线为 12 条、数据线为 8 条。 二、选择题: (选择一个正确的答案填入括号内,每题3分,共30分 ) 1.设下图中所有触发器的初始状态皆为0,找出图中触发器在时钟信号作用下,输出电压波形恒为0的是:(C )图。 2.下列几种TTL电路中,输出端可实现线与功能的电路是( D)。 A、或非门 B、与非门 C、异或门 D、OC门

3.对CMOS与非门电路,其多余输入端正确的处理方法是(D )。 A、通过大电阻接地(>Ω) B、悬空 C、通过小电阻接地(<1KΩ) B、 D、通过电阻接V CC 4.图2所示电路为由555定时器构成的(A )。 A、施密特触发器 B、多谐振荡器 C、单稳态触发器 D、T触发器 5.请判断以下哪个电路不是时序逻辑电路(C )。 A、计数器 B、寄存器 C、译码器 D、触发器 6.下列几种A/D转换器中,转换速度最快的是(A )。 A、并行A/D转换器 B、计数型A/D转换器 C、逐次渐进型A/D转换器 B、 D、双积分A/D转换器 7.某电路的输入波形 u I 和输出波形 u O 如下图所示,则该电路为( C)。 A、施密特触发器 B、反相器 C、单稳态触发器 D、JK触发器 8.要将方波脉冲的周期扩展10倍,可采用(C )。

2012~ 2013 学年第二学期 《模拟电子技术基础》课程设计报告 题目:数字逻辑信号测试器的设计 专业:电子信息工程 班级: 组成员: 指导教师: 电气工程学院 2013年6月5 日

任务书 课题名称数字逻辑信号测试器的设计 指导教师(职称)倪琳 执行时间2012 — 2013 学年第二学期第 15 周学生姓名学号承担任务 音响信号产生电路 音响信号产生电路 音响信号产生电路 输入信号识别电路 输入信号识别电路 输入信号识别电路及仿真 音响驱动电路及仿真 音响驱动电路及仿真 音响驱动电路及仿真 设计目的1、学习数字逻辑电平测试仪电路的设计方法; 2、研究数字逻辑电平测试仪电路的设计方案。 设计要求 1、技术指标:测试高电平、低电平,发出不同的声响。测量范围:低电平<0.8V, 高电平>3.5V ,高低电平分别用1KHZ和800HZ的声响表示;被测信号在0.8~3.5v之间不发声;工作电源为5V ,输入阻抗大于20KΩ。 2、设计基本要求 (1)设计一个数字逻辑电平测试仪电路; (2)拟定设计步骤; (3)根据设计要求和技术指标设计好电路,选好元件及参数; (4)运用仿真软件绘制设计电路图; (5)撰写设计报告。

数字逻辑电平测试仪设计 摘要 在检修数字集成电路组成的设备时,经常需要使用万用表和示波器对电路中的故障部位的高低电平进行测量,以便分析故障的原因。使用这些仪器能较准确的测出被测点信号的电平的高低和被测电平的周期,但是使用者必须一方面用眼睛看着万用表的表盘或示波器的屏幕,另一方面还要寻找测试点,因此使用起来很不方便。本文介绍了一个逻辑信号电平测试器,它可以方便快捷的测量某一点的电位的高低,通过声音的有无和声音的频率来判定被测电位的电平范围,从而能解决平常对电路中某点的逻辑电平进行测试其高低电平时,采用很不方便的万用表或示波器等仪器仪表的麻烦。该测试器采用运算放大器作电压比较器进行电平判断,根据电平高低使音响电路产生不同频率方波驱动扬声器,使扬声器有相应不同的声调输出提示。从而达到了测试效果。 关键词放大器;逻辑信号;电平测试;高电平;低电平

一种集成电路产品测试系统的设计与实现 曹维国1,邓中亮1,王峥2 1北京邮电大学电子工程学院,北京 (100876) 2凤凰微电子(中国)有限公司,北京 (100084) E-mail:Weiguo.cao@https://www.doczj.com/doc/7d13858389.html, 摘要:本文回顾了数字集成电路的测试技术;分析了该项技术在对SIM形式封装的数字集成电路测试中的缺陷和不足;针对目前的测试系统的单一和性能价格比例偏低的情况提出了一种新型的综合测试系统,详细介绍了该系统的工作原理及组成,讨论了该系统的软硬件设计方案,总结了其优点。 关键词:用户识别模块,集成电路,测试系统,精密测量单元 1.引言 数字集成电路测试的目的在于检测集成电路的故障并对检测到的故障进行定位、生成测试报告并对故障进行分类汇总以用于缺陷分析。从测试技术上分可分为测试生成技术、响应鉴别技术、测试仪技术和易测设计技术等。从测试方法上分可分为人工测试和穷举测试法、ATPG (自动测试图形生成)、DFT (Design For Test,可测性设计)、 BST (边界扫描测试)和BIST (Build In Self Test,内建自测试)[1]等。从阶段可分为设计阶段测试、生产阶段测试和产品测试[2]。测试技术和测试方法具有通用性和共用性,而阶段性测试则跟被测对象的不同会衍生不同的测试系统尤其是在产品测试阶段[3]。设计阶段测试可借助强大的EDA(Electronic Design Automation,电子设计自动化)工具,生产阶段的测试由集成电路制造商完整的制造体系来保证,但是封装后的数字集成电路的外形各种各样,管脚有多有少,尤其是对SIM (Subscriber Identity Module,用户识别模块)形式封装的数字集成电路的产品外部只有8个管脚可以利用,从而造成了该类产品测试阶段通用性和专用性的矛盾。目前针对SIM封装形式的数字集成电路进行产品测试的系统十分稀缺且都具有共同的不足: 1)没有补偿电路,无法进行回零测试; 2)只能进行电气性能的开短路和漏电流测试,无法进行加压测流和加流测压; 3)只能进行电气性能的测试,无法完成逻辑功能的测试; 4)价格比较高。 结合SIM封装形式的数字集成电路产品测试系统的要求和企业产品的具体应用进行设计开发了一套专用测试系统,实现对SIM封装形式的数字集成电路的逻辑功能测试和电气性能测试,并对测试的结果进行汇总分析形成报告以用于缺陷分析。 2.系统介绍 本测试系统由控制计算机﹑测试电路和测试适配器三部分组成.适用于SIM封装形式下的集成电路的开短路测试﹑工作电流测试﹑输入管脚漏电流测试﹑输出电平测试和基本逻辑功能测试。并且具备16个芯片的并行测试能力。系统框架图如图1所示:

《数字电子技术》考试试卷(第一套)课程号2904025035 考试时间100 分钟 (注:集成电路CD4532、74HC138、74HC151的功能见附表) 一、填空题(共28分) 1、(2分)(5E.8)H=(94.5 )D=(10010100.0101 )8421BCD。 2、(2分)逻辑函数L = + A+ B+ C +D = (1 )。 3、(2分)由传输门构成的电路如下图所示,当A=0时,输出L= B 。 4、(2分)三态门可能输出的三种状态是低电平、高电平和高阻态_。 5、(3分)A/D转换器一般要经过_ 采样__、保持、量化和__编码__这4个步骤,A/D转换器的转换速度主要取决于转换类型。对双积分型A/D 转换器、并行比较型A/D转换器和逐次比较型A/D转换器的相对速度进行比较,转换速度最快的是_并行比较型A/D转换器__。 适用专业年级(方向):应用物理、电信科技2010级 考试方式及要求:闭卷笔试

6、(2分)集成优先编码器CD4532(功能表见后)正常接电源和地,且待编码信号输入端I 0 =I 2 = I 6 = I 7 = 1,输入使能端EI=1,其余输入端为0,其输出Y 2Y 1Y 0为 111 。 7、(3分)集成数据选择器74HC151构成的电路如下图所示,则其输出 Y= ABC BC A C B A ++?? 。(注:不需化简) 01 8、(3分)某PLA 电路如下图所示,其输出逻辑函数表达式X= C B A C B A ABC +?+ 。 9、(2分)某单极性输出的8位D/A 转换器正常工作,当输入数字量为 (10101010)B 时,其输出电压为3.4V ,当输入数字量为(10101100) B 时,其输出电压为 3.44 V 。 10、(2分)一个存储容量为4K ×4的存储器有 214 个存储单元,若用该存储器构成32K ×8的存储系统,则需 16 片4K ×4的存储器。 11、(3分)对于JK 触发器,当1J K ==时,n+1Q = 1 ,当1 J K ==

第三代ZD9610型在线电路维修测试仪的发展历程 ——中国改革开放40年精密电路板维修检测设备领域发展缩影 摘要:第三代ZD9610型在线电路维修测试仪是精密电路板维修(芯片级)检测设备,在关键技术上取得重大突破,许多被长期困扰的维修测试难题得到解决。第三代ZD9610电路测试仪的发展历程,是中国改革开放40年精密电路板维修检测设备领域发展的一个缩影。 关键词:第三代ZD9610电路测试仪 >40管脚数字器件动态性能测试 5cVI曲线 0.前言 北京正达时代电子技术有限公司成立于1997年,核心人员是1990年代初期国内最早研制在线电路维修测试仪的专家骨干,长期致力于精密电路板维修仪器/电子元器件检测设备研发和服务。特别是第三代ZD9610型在线电路维修测试仪,在国内外业界具有重要影响力。 回顾中国改革开放40年,在经济腾飞浪潮中,国内在线电路维修测试仪经历了1998~2018高速发展的黄金20年。第三代ZD9610电路测试仪的发展历程,正是中国改革开放40年精密电路板维修检测设备领域发展的一个缩影。 1.国内在线电路维修测试仪黄金20年 在线电路维修测试仪设计精密,测试高效,结合计算机技术并且综合运用器件功能测试和器件管脚阻抗特性测试等测试手段,是重要的精密电路板维修(芯片级)检测设备。 1.1国内电路测试仪研制背景: 1980年代初,伴随改革开放步伐,国内陆续引进了大量现代化电气设备。由于这些设备上普遍采用数字集成电路器件,因而常被冠以“数控设备”这一时髦的名称。当时国内电路维修人员对数字器件概念模糊,器件故障无从判别,迫切需要检测手段。 1980年代末,新加坡“创能”品牌BW4040型在线电路维修测试仪(下文简称:电路测试仪)进入国内。名称中“在线”是指:测试电路板时无须焊下器件。型号中“4040”是指:具有40路数字通道,40路VI曲线通道。电路测试仪将测试技术与计算机技术相结合,具有+5V 数字器件库。既可以测试+5V数字器件功能,也可以采用VI曲线测试数字器件/模拟器件管脚阻抗特性。 面对电路测试仪在电路板维修中的巨大优势,国内企业也积极开始研究与试制,不断推出一代又一代电路测试仪产品。 1.2第一代电路测试仪: 国内第一代电路测试仪是从对BW4040电路测试仪的学习和仿制开始的,代表机型是正达ZD4040电路测试仪。主要特点:40路数字通道,40路VI曲线通道,器件库包含40管脚以下+5V数字器件。 具有40路数字通道,提供+5V测试电源是第一代电路测试仪的基本特征。由于增加VI曲线通道难度不大,所以ZD4080电路测试仪(80路VI曲线通道)也属于第一代电路测试仪。 第一代电路测试仪始于1990年代初,那时的计算机还是DOS操作系统。随着计算机技术的飞速发展,第一代ZD4040电路测试仪也同步改进和升级。今天的ZD4040-N电路测试仪可以支持windows10_64位操作系统,在维修中依然发挥着重要作用。 1.3第二代电路测试仪: 国内第二代电路测试仪开始摆脱全面仿制阶段,推出一些自主创新的特色功能。代表机型是正达ZD9001电路测试仪。主要特点是:40路数字通道,80路VI曲线通道,20路模拟功能

数字集成电路测试仪(YBD-868)} YBD868型数字集成电路测试仪是一种性能较高的通用仪器,测试脚数最大为双列直插式40脚,可测范围复盖了大多数的数字集成电路,测试准确可靠,操作简便,基本功能如下: ———* 器件好坏测试—————* 器件型号判别 ———* 器件动态老化————- * 器件代换查询 三.技术指标 1.操作系统:十六位轻触式立体键盘双音提示系统,被测器件安装采用锁紧插座。 2.显示系统:六位数码管显示器显示被测器件型号或各种功能提示,四只led显示仪器工作状态。 8. 外形尺寸:292*235*75立方厘米 9. 整机重量:2.0kg 四. 测试范围 ybd868型数字集成电路测试仪库存容量两千多片,包含以下各大系列: 1. ttl54系列 2. ttl55系列 3. ttl74系列 4. ttl75系列 5. cmos14系列 6. cmos40系列 7. cmos45系列

8. 光耦合器系列 9. led显示器系列 10. 常用ram系列 11. 常用单片机系列 12. 微机外围电路系列 五. 功能综述 1. 器件好坏判别: 当未知被测器件的好坏时,只要输入该器件的型号,并将器件放于对应的工作插座上,可判别出该仪器件的好坏。 2. 器件型号判别: 当未知被测器件的型号时,只需输入该器件的引脚数目,并将被测器件放于对应的工作插座上仪器即可立即判别出该器件的型号。 3. 器件代换查询: 输入欲查询的器件型号,按下“代换查询“键就可知道是否有逻辑功能与之完全相同的其它器件。 4. 器件动态老化: 当怀疑被测器件的动态稳定性时,只要输入该器件的型号,并将被测器件放于对应的插座上,按下“动态老化“键,仪器就可对该器件进行动态老化和连续测试。

国内集成电路的现状及发展 作者:崔建红 单位:山东工商学院邮政编码:264000 摘要:集成电路是一种微型电子器件或部件,它的出现给电子行业带来了新的契机。从最初集成电路在我国发展以来,我国已取得了可喜的成就。但仍然面临资源利用率低,芯片与整机脱节,缺乏自我品牌,创新能力较弱等问题。我们都应采取有效的对策。在今后发展中加以解决,争取使我国由消费大国走向产业强国。 关键词:国内、集成电路、发展现状、措施、 Present Situation and Development of The Domestic Integrated Circuit Author:Cui Jianhong Unit:Shandong Institute of Business and Technology Zip Code:264000 Summary:IC is a miniature electronic devices or components, its appearance to the electronics industry has brought new opportunities. Since the initial IC has developed in our country , China has achieved gratifying achievements. But we still faces many problems,such as resource utilization is low, the chip out of the whole ,lack of our own brand, weak innovation capabilityand so on. We should take effective measures to solve them in future development and Striving to make our country join in industrial power by the country of consumption. Keyword:national, integrated circuits, development status, measures 一、集成电路的定义与特点 集成电路是一种微型电子器件或部件。采用一定的工艺,把一个电路中所需的晶体管、二极管、电阻、电容和电感等元件及布线互连一起,制作在一小块或几小块半导体晶片或介质基片上,然后封装在一个管壳内,成为具有所需电路功能的微型结构;其中所有元件在结构上已组成一个整体,这样,整个电路的体积大大缩小,且引出线和焊接点的数目也大为减少,从而使电子元件向着微小型化、低功耗和高可靠性方面迈进了一大步。它在电路中用字母“IC”(也有用文字符号“N”等)表示。 集成电路按其功能、结构的不同,可以分为模拟集成电路、数字集成电路和数/模混合集成电路三大类。

第一部分 门电路 一、 填空题 1. 数字集成电路按开关元件不同,可分为 TTL 集成电路 和 CMOS 集成电路 两大类。 2. 数字电路中的三种基本逻辑门电路是 与门 、 或门 、 非门 。 3.三态门是在普通门的基础上增加 控制 电路构成的,它的三种输出状态是 高电平、 低电平 和 高阻态 。 4. 与门、与非门的闲置输入端应接 高 电平;或门、或非门的闲置输入端应接 低 电平。 5. 图1所示三态门在1EN =时,Y 的输出状态是 高阻态 。 6. 利用TTL 与非门实现输出线与应采用 OC 门,实现总线传输应采用 三态 门。 7. 图2为几种常见逻辑门电路的逻辑符号,试分别写出其名称和逻辑表达式。 名称 逻辑表达式 名称 逻辑表达式 (a ) 与门 Y=AB ; (b ) 非门 ; (c ) 与非门 ; (d ) 或非门 。 8. 当决定某一件事情的多个条件中有一个或一个以上具备时,该件事情就会发生,这种关系称为 或 逻辑关系。 二、 选择题 1. 下列几种逻辑门中,能用作反相器的是 C 。 A. 与门 B. 或门 C. 与非门 2. 下列几种逻辑门中,不能将输出端直接并联的是 B 。 A. 三态门 B. 与非门 C. OC 门 3. TTL 与非门的输入端在以下四种接法中,在逻辑上属于输入高电平的是 C 。 A. 输入端接地 B. 输入端接同类与非门的输出电压 C. 输入端经10k Ω电阻接地 D. 输入端经51Ω电阻接地 4. TTL 与非门的输入端在以下4种接法中,在逻辑上属于输入低电平的是 D 。 A. 输入端经10k Ω电阻接地 B. 输入端接同类与非门的输出电压 C. 输入端悬空 D. 输入端经51Ω电阻接地 5. 逻辑电路如图3所示,该电路实现的逻辑关系为 C 。 A. Y AB = B. Y AB = C. Y AB = D. Y A B =+ EN EN & ▽ Y A B 图1 填空题5用图 & A B Y (a Y A B & Y A B ≥1 (d) (c) 图2 填空题7用图 1 A (b

电子测量仪器的分类及应用 电子测量仪器按其工作原理与用途,大致划为以下几类。 1.多用电表 模拟式电压表、模拟多用表(即指针式万用表VOM)、数字电压表、数字多用表(即数字万用表DMM)都属此类。这是经常使用仪表。它可以用来测量交流/直流电压、交流/直流电流、电阻阻值、电容器容量、电感量、音频电平、频率、晶体管NPN或PNP电流放大倍数β值等。 2.示波器 示波器是一种测量电压波形的电子仪器,它可以把被测电压信号随时间变化的规律,用图形显示出来。使用示波器不仅可以直观而形象地观察被测物理量的变化全貌,而且可以通过它显示的波形,测量电压和电流,进行频率和相位的比较,以及描绘特性曲线等。 3.信号发生器 信号发生器(包括函数发生器)为检修、调试电子设备和仪器时提供信号源。它是一种能够产生一定波形、频率和幅度的振荡器。例如:产生正弦波、方波、三角波、斜波和矩形脉冲波等。 4.晶体管特性图示仪 晶体管特性图示仪是一种专用示波器,它能直接观察各种晶体管特性曲线及曲性簇。例如:晶体管共射、共基和共集三种接法的输入、输出特性及反馈特性;二极管的正向、反向特性;稳压管的稳压或齐纳特性;它可以测量晶体管的击穿电压、饱和电流、自或a参数等。 5.兆欧表 兆欧表(俗称摇表)是一种检查电气设备、测量高电阻的简便直读式仪表,通常用来测量电路、电机绕组、电缆等绝缘电阻。兆欧表大多采用手摇发电机供电,故称摇表。由于它的刻度是以兆欧(MΩ)为单位,故称兆欧表。 6.红外测试仪 红外测试仪是一种非接触式测温仪器,它包括光学系统、电子线路,在将信息进行调制、线性化处理后达到指示、显示及控制的目的。目前已应用的红外测温仪有光子测温和热测温仪两种,主要用于电热炉、农作物、铁路钢轨、深埋地下超高压电缆接头、消防、气体分析、激光接收等温度测量及控制场合。 7.集成电路测试仪 该类仪器可对TI1、PM0S、CM0S数字集成电路功能和参数测试,还可判断抹去字的芯片型号及对集成电路在线功能测试、在线状态测试。