数字电路期中考试试卷 A 卷

一、填空(每题2分,共16分)

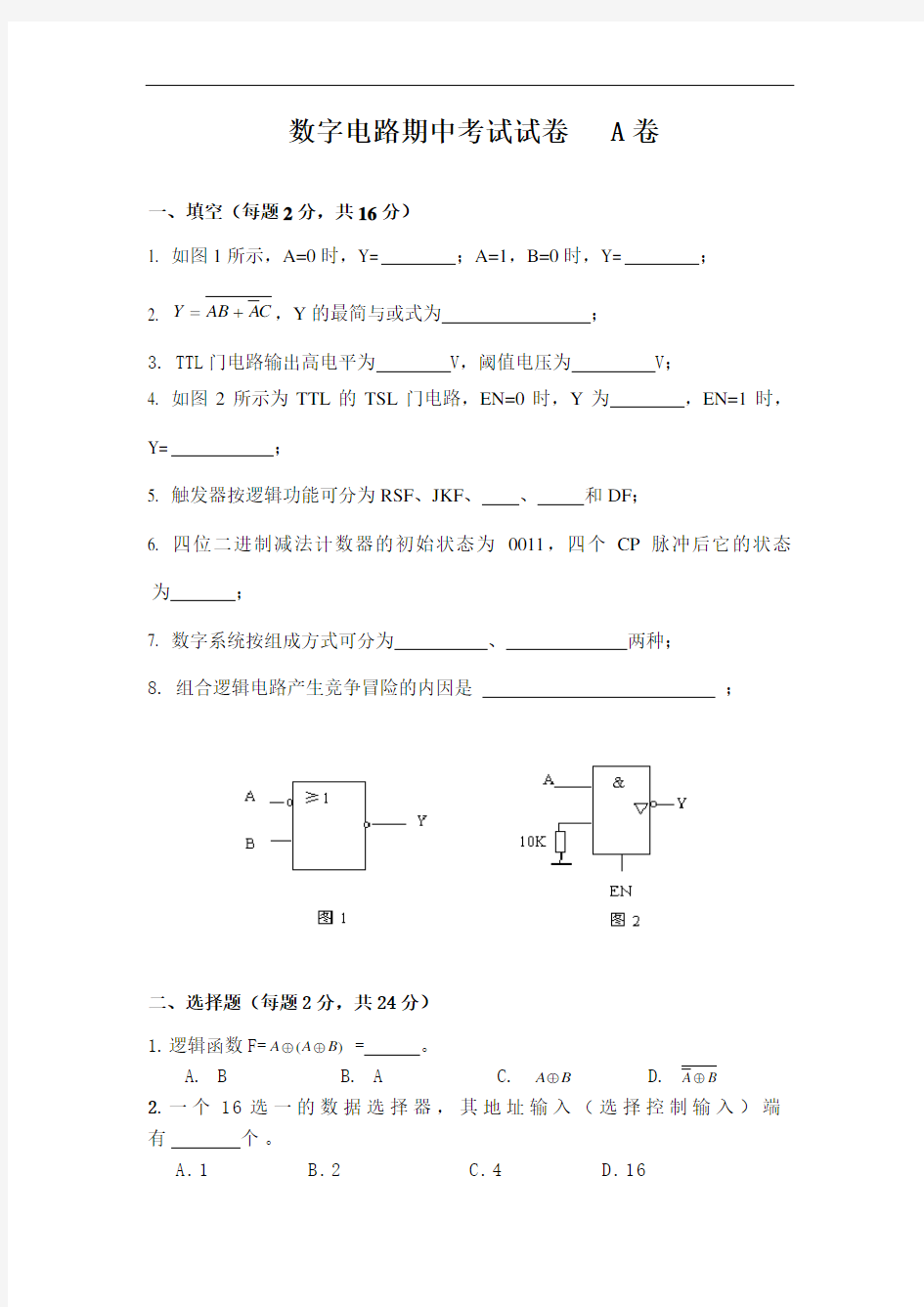

1. 如图1所示,A=0时,Y= ;A=1,B=0时,Y= ;

2. C A AB Y +=,Y 的最简与或式为 ;

3. TTL 门电路输出高电平为 V ,阈值电压为 V ;

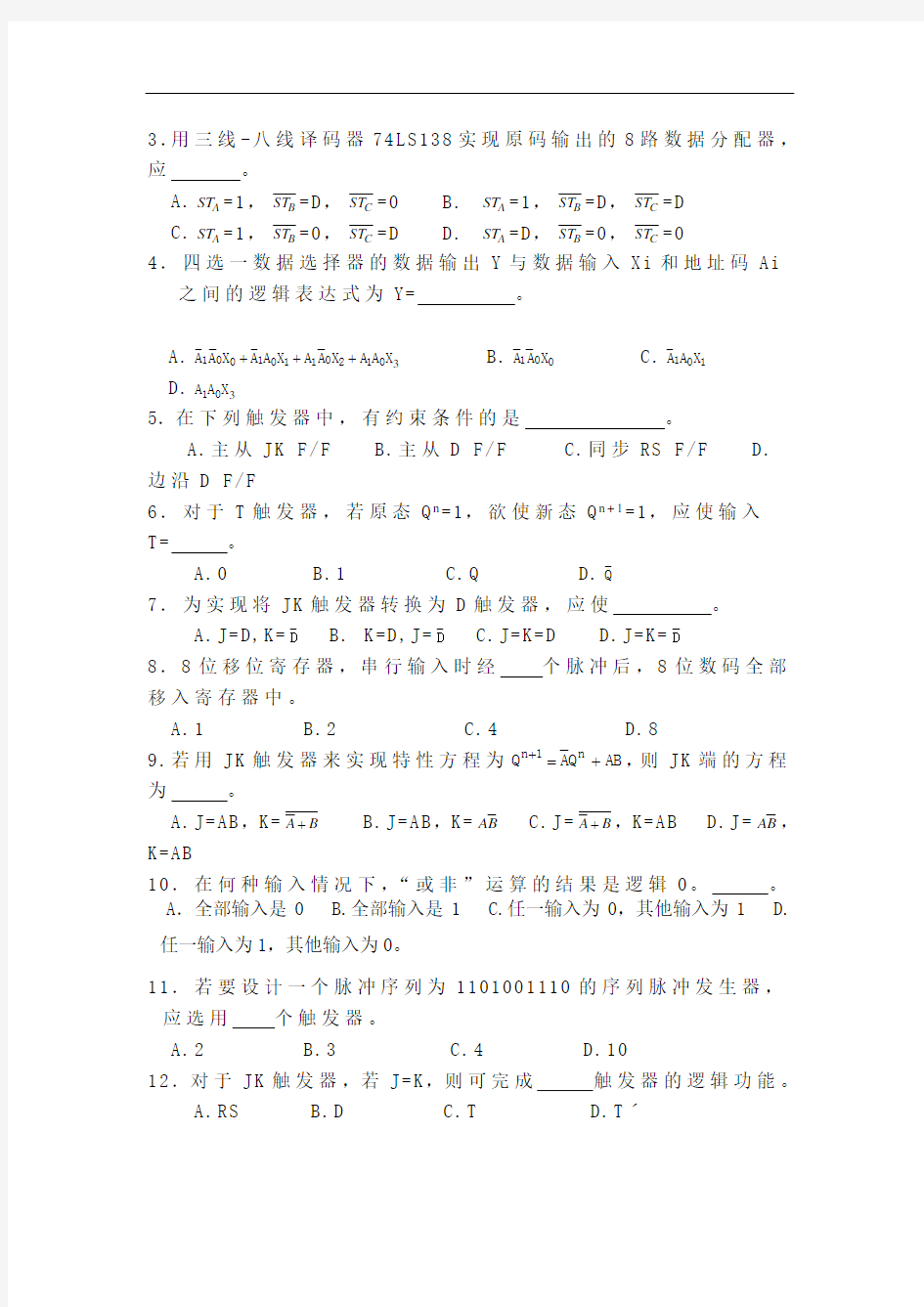

4. 如图2所示为TTL 的TSL 门电路,EN=0时,Y 为 ,EN=1时,Y= ;

5. 触发器按逻辑功能可分为RSF 、JKF 、 、 和DF ;

6. 四位二进制减法计数器的初始状态为0011,四个CP 脉冲后它的状态为 ;

7. 数字系统按组成方式可分为 、 两种; 8. 组合逻辑电路产生竞争冒险的内因是 ;

二、选择题(每题2分,共24分) 1.逻辑函数F=)(B A A ⊕⊕ = 。

A. B

B. A

C. B A ⊕

D. B A ⊕

2.一个16选一的数据选择器,其地址输入(选择控制输入)端

有 个。

A.1

B.2

C.4

D.16

3.用三线-八线译码器74LS 138实现原码输出的8路数据分配器,应 。 A.A ST =1,B ST =D ,C ST =0 B. A ST =1,B ST =D ,C ST =D C.A ST =1,

B

ST =0,

C

ST =D D.

A ST =D ,B

ST =0,

C

ST =0

4.四选一数据选择器的数据输出Y 与数据输入X i 和地址码Ai

之间的逻辑表达式为Y= 。

A.3X A A X A A X A A X A A 01201101001+++

B.001X A A

C.101X A A

D.3X A A 01

5.在下列触发器中,有约束条件的是 。

A.主从J K F/F

B.主从 D F/F

C.同步RS F /F

D.

边沿 D F/F

6.对于T 触发器,若原态Q n =1,欲使新态Q n +1=1,应使输入T = 。

A.0

B.1

C.Q

D.Q

7.为实现将J K 触发器转换为D 触发器,应使 。

A.J=D,K=D

B. K =D ,J=D

C.J=K=D

D.J=K=D

8.8位移位寄存器,串行输入时经 个脉冲后,8位数码全部移入寄存器中。

A.1

B.2

C.4

D.8

9.若用J K 触发器来实现特性方程为AB Q A Q n 1n +=+,则JK 端的方程为 。 A.J=AB ,K=B A + B.J=A B ,K =B A C.J =B A +,K=A B D.J =B A ,

K =AB

10.在何种输入情况下,“或非”运算的结果是逻辑0。 。 A .全部输入是0 B.全部输入是1 C.任一输入为0,其他输入为1 D.任一输入为1,其他输入为0。

11.若要设计一个脉冲序列为1101001110的序列脉冲发生器,应选用 个触发器。

A.2

B.3

C.4

D.10

12.对于J K 触发器,若J=K ,则可完成 触发器的逻辑功能。

A.RS

B.D

C.T

D.T ˊ

三、求F的最简“与非”表达式(每小题7分,共14分)

1.试简化函数(用代数法)

2.(用卡诺图法)

四、写出下列各图中的输出逻辑表达式,并化为最简与或式;

(G1、G2为OC门,TG1、TG2为CMOS传输门) (每小题5分,共10分)

五、试分析如图3所示的组合逻辑电路。(每小题4分,共16分)

1. 写出输出逻辑表达式;

2. 化为最简与或式;

3. 列出真值表;

4. 说明逻辑功能。

六、由同步十进制加法计数器74LS160构成一数字系统如图所示,假设计数器的初态为0,测得组合逻辑电路的真值表如下所示:(每小题5分,共20分)

1. 画出74LS160的状态转换图;

2. 画出整个数字系统的时序图;

3. 如果用同步四位二进制加法计数器74LS161代替74LS160,试画出其电路图(要求采用置数法);

4. 试用一片二进制译码器74LS138辅助与非门实现该组合逻辑电路功能。