附表二:武汉工业学院

课程考核试题参考答案及评分标准

学年:2009-2010 学期: 2

课程名称:可编程逻辑器件(A卷)考核方式:开卷

任课教师:肖忠、康胜武课程所在院(系、部):电气信息工程系

考试班级:电子信息工程071-2,通信工程071-2,自动化071-2,电气工程及自动化071-3

注:标准答案需写清题号;每小题得分、共得分;参考答案要点;评分标准等

一、简答题(30分,共5小题,每小题6分)

1. 优点:便于修改和调试,缩短开发周期,降低开发成本,简化系统构成,缩小系统体积,降低系统功耗,提高系统可靠性等。(5’)

2. 二者结构、工艺不同,主要从以下几方面进行选择:(每条1’)

(1)逻辑单元:CPLD适用于逻辑型系统,FPGA适用于数据型系统。

(2)内部互连资源与连线结构:CPLD适用于实现有限状态机,FPGA适用于实现小型化、集成化。

(3)编程工艺:CPLD采用EPROM结构,内部逻辑一经编程后还会以丢失,FPGA采用RAM型编程,是易失性器件,需与配置芯片配合使用。

(4)规模:中小规模电路设计可采用CPLD,大规模逻辑电路的设计采用FPGA。

(5)封装形式:小规模电路:PLCC,引脚数量大的系统宜选用SMD的TQFP、PQFP、BGA等封装形式。

3. MAX+PLUSII的设计流程如下:(每步1’)

(1)设计输入

(2)设计检查

(3)设计编译

(4)时序/功能仿真

(5)定时分析

注:用流程框图表示也算回答正确。

4. EDA软件系统应当包含以下子模块:(每条1’)

(1)设计输入子模块:该模块接受用户的设计描述,并进行语义正确性、语法规则的检查、检查通过后,将用户的设计描述数据转换为EDA软件系统的内部数据格式,存入设计数据库被其他子模块调用。

(2)设计数据库子模块:该模块存放系统提供的库单元以及用户的设计描述和中间设计结果。

(3)分析验证子模块:该模块包括各个层次的模拟验证、设计规则的检查、故障诊断等。

(4)综合仿真子模块:该模块包括各个层次的综合工具。

(5)布局布线子模块:该模块实现由逻辑设计到物理实现的映射,因此与物理实现的方式密切相关。

5. 顺序语句:

特点:在程序执行时,按照语句的书写顺序执行,前面的语句的执行结果可能直接影响后面语句的

执行。(1’)

用途:主要用于模块的算法部分,用若干顺序语句构成一个进程或描述一个特定的算法或行为。顺序语句不能直接构成结构体,必须放在进程、过程中。(2’)

并行语句:

特点:不按书写顺序执行,可作为一个整体运行,程序执行时只执行被激活的语句。被激活的并行语句是同时执行的。(2’)

用途:主要用于表示算法模块间的连接关系,模拟实际硬件电路工作的并行性,可以直接构成结构体。(1’)

二、程序阅读分析(30分,共3小题,每小题10分)

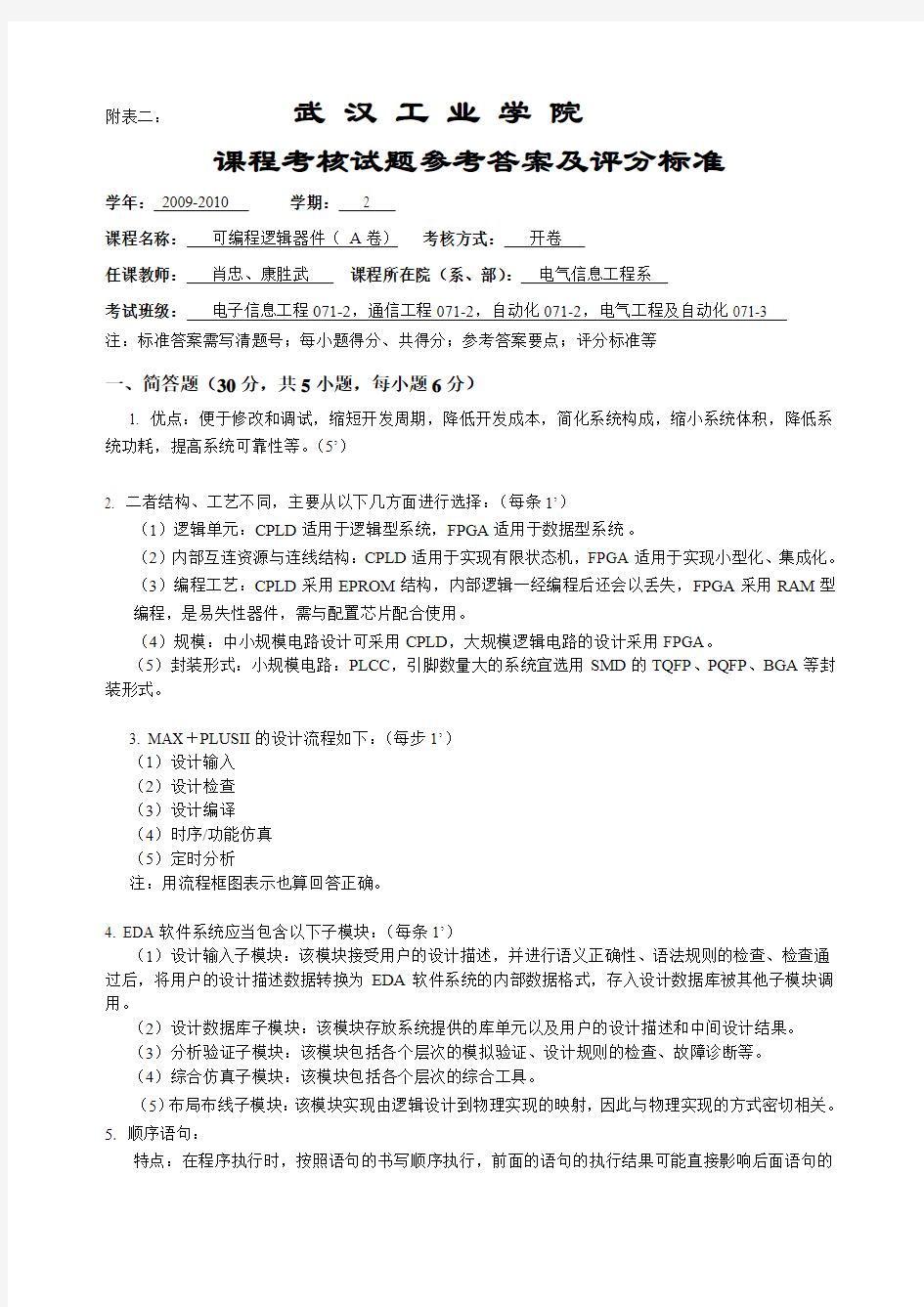

1.(1)该电路是一个双四输入数据比较器(3’)

(2)电路输出状态如下:(7’)

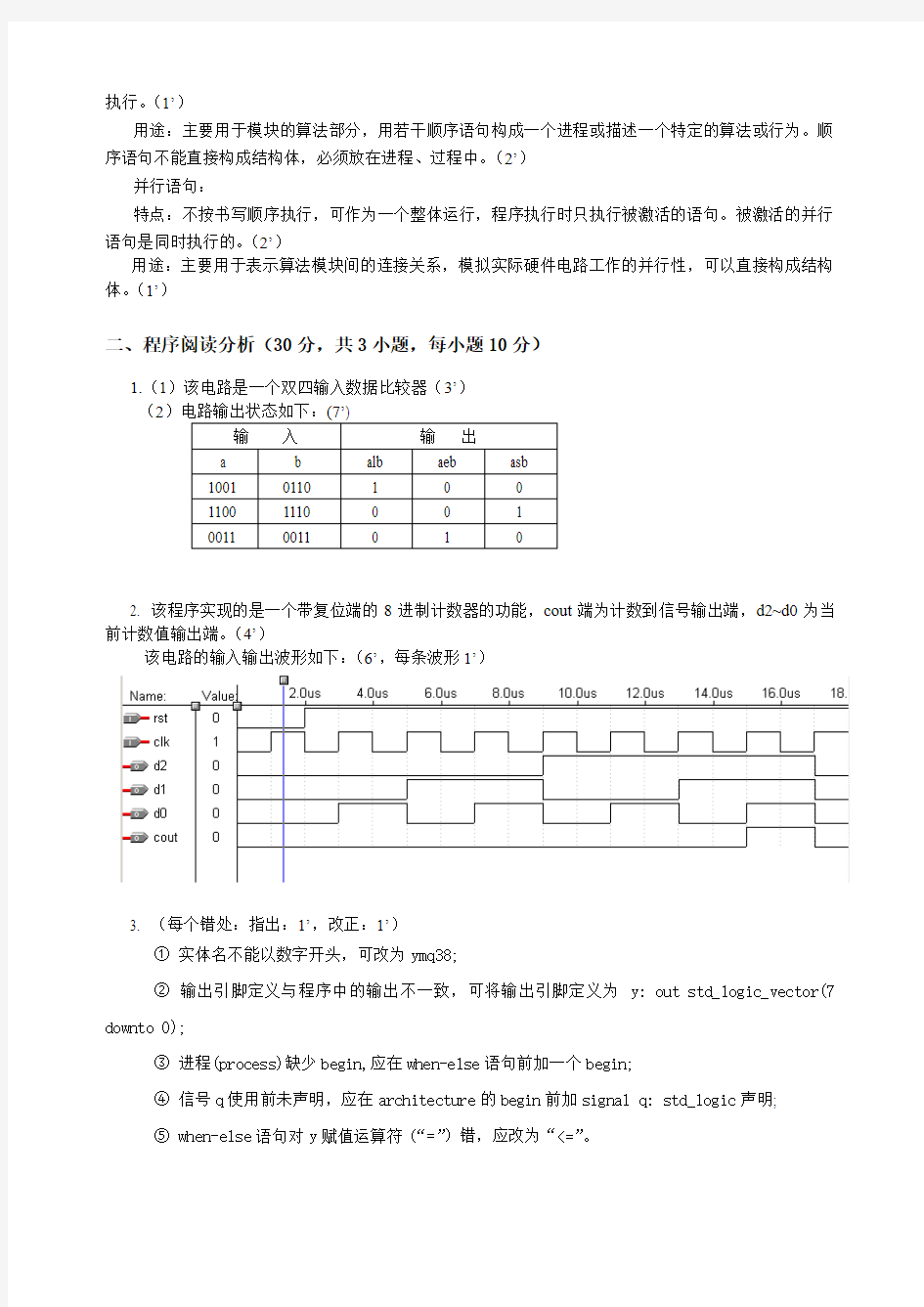

2. 该程序实现的是一个带复位端的8进制计数器的功能,cout端为计数到信号输出端,d2~d0为当前计数值输出端。(4’)

该电路的输入输出波形如下:(6’,每条波形1’)

3. (每个错处:指出:1’,改正:1’)

①实体名不能以数字开头,可改为ymq38;

②输出引脚定义与程序中的输出不一致,可将输出引脚定义为y: out std_logic_vector(7 downto 0);

③进程(process)缺少begin,应在when-else语句前加一个begin;

④信号q使用前未声明,应在architecture的begin前加signal q: std_logic声明;

⑤ when-else语句对y赋值运算符(“=”)错,应改为“<=”。

三、程序设计(共40分,第1题10分,第2题15分,第3题15分)

(注:程序设计题答案不唯一,以下仅为一种参考答案。)

1. 总线开关的参考程序如下:

LIBRARY ieee;

USE ieee.std_logic_1164.all; (1’)

ENTITY aaa IS

PORT( en, select : IN STD_LOGIC ;

A, B : IN STD_LOGIC_VECTOR(6 DOWNTO 0 ) ;

Y : OUT STD_LOGIC_VECTOR(6 DOWNTO 0)

END aaa ; (4’) ARCHITECTURE ar OF aaa IS

BEGIN

PROCESS(en, select )

BEGIN

IF oe=’0’THEN Y<=”ZZZZZZZ”;

ELSIF oe=’1’THEN

IF select=’0’THEN Y<=A;

ELSIF select=’1’THEN Y<=B;

END IF;

END IF ;

END PROCESS ;

END ar ; (5’)

2. M10计数器参考程序:

LIBRARY ieee;

USE ieee.std_logic_1164.all;

USE ieee.std_logic_arith.all;

USE ieee.std_logic_unsigned.all; (1’)

ENTITY aaa IS

PORT(clk, rst, en : IN STD_LOGIC;

cout: OUT STD_LOGIC;

q: BUFFER STD_LOGIC_VECTOR(3 DOWNTO 0)

);

END aaa; (4’)

ARCHITECTURE bd OF aaa IS

BEGIN

PROCESS(clk,reset,en)

BEGIN

IF (rst='0') THEN q<="0000";

ELSIF (clk'event AND clk='1') THEN

IF en=’1’THEN

IF (q=9) THEN q<="0000";

ELSE q<=q+1;

END IF;

END IF;

END IF;

END PROCESS;

END bd; (10’)

3. 用VHDL语言编程实现一个LED字符发生器参考程序:

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

ENTITY genc IS (1’)

PORT( rst, cp : IN STD_LOGIC;

a,b,c,d,e,f,g: OUT STD_LOGIC

); (1’)

END genc;

ARCHITECTURE aa OF genc IS

TYPE state IS(s0,s1, s2, s3, s4, s5 );

SIGNAL pstate: state;

SIGNAL dout: STD_LOGIC_VECTOR(6 DOWNTO 0 ); (2’)

BEGIN

pr1: PROCESS(cp, rst,)

BEGIN

IF rst='0' THEN pstate <=s0;

ELSIF (cp'event AND cp='0' )THEN

CASE pstate IS

WHEN s0=> pstate <=s1;

WHEN s1=> pstate <=s2;

WHEN s2=> pstate <=s3;

WHEN s3=> pstate <=s4;

WHEN s4=> pstate <=s5;

WHEN s5=> pstate <=s1;

WHEN OTHERS=> pstate <=s0;

END CASE;

END IF;

END IF;

END PROCESS; (5’)

pr2: PROCESS(pstate)

BEGIN

CASE style IS

WHEN s0 => dout<="0000000"; --无显示

WHEN s1 => dout<="0110111"; --“H”

WHEN s2 => dout<="1110111"; --“A”

WHEN s3 => dout<="1100111"; --“P”

WHEN s4 => dout<="1100111"; --“P”

WHEN s5 => dout<="0111011"; --“Y”

WHEN OTHERS=> dout<="0000000";--无显示

END CASE;

END PROCESS; (5’)

a<=dout(6); b<=dout(5); c<=dout(4); d<=dout(3); e<=dout(2); f<=dout(1); g<=dout(0);

END aa; (1’)

试卷一参考答案及评分标准 一、不定项选择:(每题2分,25题,共50分。) 1.ABCE 2.ABD 3.BCDE 4.BCE 5.CDE 6.DE 7.ACDE 8.BCE 9.BCE 10.BCDE 11.ACE 12.BCDE 13.BCDE 14.AD 15.AD 16.BE 17.D 18.ADE 19.C 20.BC 21.ABC 22.ABCDE 23.ABC 24.ABCE 25.ABDE 二、引文解释:(每题7分,2题,共14分) 26.“资本可变部分比不变部分的相对减少,或资本价值构成的变化,只是近似地表示出资本的物质组成部分构成上的变化”。(引自第1卷第23章) 1)资本技术构成和资本价值构成之间存在一定的关系,即资本技术构成的变化会引起资本价值构成的相应变化。(2分) 2)当劳动生产率提高时,由于单个劳动者在相同时间内需要的生产资料数量增加,从而会引起资本技术构成的提高,进而引起不变资本价值的增加和可变资本价值的相对减少。(3分) 3)由于劳动生产率的提高会引起生产资料价值的下降,因此资本价值构成的提高会低于资本技术构成的提高。(3分)4)例如…(2分) 27.“周转时间的缩短对剩余价值的生产,从而对利润的生产的直接影响,在于使可变资本部分由此提高效率”。(引自第3卷第4章) 1)资本周转时间包含了生产时间和流通时间。由于劳动生产率的提高而缩短生产时间和由于改进交通而缩短流通时间,都可以增加利润量、提高利润率。(2分)例如:…(2分) 2)资本周转时间缩短引起资本周转次数增多,导致年利润量增加和年利润率的提高,从表面上看似乎是资本周转速度本身加快所致。(2分)但实际上,根本的原因则是因为可变资本由于资本周转次数的增加而提高了使用效率,即生产出更多的年剩余价值量。(4分) 三、说明下列概念的内涵和相互关系:(1题,共10分) 28.劳动过程、价值形成过程、价值增殖过程 区别:①涵义:(2分)②劳动过程和价值形成过程的区别:劳动过程考察的是劳动的质、目的和内容;价值形成过程考察的是劳动的量(1分)③价值形成过程和价值增殖过程的区别:价值形成过程中创造的新价值等于劳动力价值;价值增殖过程中创造的新价值包含剩余价值。(2分)④劳动生产率的变化对劳动过程创造的使用价值量和价值形成和价值增殖中创造的价值量影响不同。(2分) 联系:①劳动过程与价值形成过程的统一构成一般商品生产过程;劳动过程与价值增殖过程的统一构成资本主义生产过程。(1分)②劳动时间超过必要劳动时间,价值形成过程就转化为价值增殖过程(2分)

武科大EDA系统设计试卷及答案 一、单项选择题:(20分) 1.IP核在EDA技术和开发中具有十分重要的地位;提供用VHDL等硬件描述语言描述的功能块,但不涉及实现该功能块的具体电路的IP核为_____ D_____。 A .瘦IP B.固IP C.胖IP D.都不是 2.综合是EDA设计流程的关键步骤,在下面对综合的描述中,____ D _____是错误的。 A.综合就是把抽象设计层次中的一种表示转化成另一种表示的过程; B.综合就是将电路的高级语言转化成低级的,可与FPGA / CPLD的基本结构相映射的网表文件; C.为实现系统的速度、面积、性能的要求,需要对综合加以约束,称为综合约束; D.综合可理解为一种映射过程,并且这种映射关系是唯一的,即综合结果是唯一的。 3.大规模可编程器件主要有FPGA、CPLD两类,下列对FPGA结构与工作原理的描述中,正确的是__C__。 A. FPGA全称为复杂可编程逻辑器件; B. FPGA是基于乘积项结构的可编程逻辑器件; C.基于SRAM的FPGA器件,在每次上电后必须进行一次配置; D.在Altera公司生产的器件中,MAX7000系列属FPGA结构。 4.进程中的信号赋值语句,其信号更新是___C____。 A.按顺序完成; B.比变量更快完成; C.在进程的最后完成; D.都不对。 5. VHDL语言是一种结构化设计语言;一个设计实体(电路模块)包括实体与结构体两部分,结构体描述_____B______。 A.器件外部特性; B.器件的内部功能; C.器件的综合约束; D.器件外部特性与内部功能。 6.不完整的IF语句,其综合结果可实现____ A ____。 A. 时序逻辑电路 B. 组合逻辑电路 C. 双向电路 D. 三态控制电路 7.子系统设计优化,主要考虑提高资源利用率减少功耗(即面积优化),以及提高运行速度(即速度优化);指出下列哪些方法是面积优化_____ B____。 ①流水线设计②资源共享③逻辑优化④串行化⑤寄存器配平⑥关键路径法 A. ①③ ⑤ B. ②③④ C. ②⑤ ⑥ D. ①④⑥ 8.下列标识符中,_____B_____是不合法的标识符。 A. State0 B. 9moon C. Not_Ack_0 D.

道路勘测设计期末考试试卷(A) 答案及评分标准(样板) 一、名词解释(3分×5=15分) 1.设计速度:在气候条件好、行车密度小、汽车运行只受道路本身条件影响时,一般司机能保持安全而舒适地行驶的最大速度。 2.动力因数:某型汽车在海平面高程,在滿载情况下,单位车座克服道路阻力和惯性阻力的性能。 评分标准: 答出下划线部分即可得分,每题3分 二、填空题(15分,每空0.5分) 1.方格网式、环形放射式、自由式、混合式。 2. 具有足够的驱动力来克服各种行驶阻力(或R T ≥) 和 驱动力小于或等于轮胎于路面之间的附着力(或k G T ?≤)。 路面平整坚实; 路面粗糙不滑。 3.停车视距;超车视距 评分标准: 每空的分数为0.5分。 三、判断并说明理由(15分, 判断0.5分,说明理由1.0分) 1.错误;应改为:公路等级的确定与远景交通量、使用任务及其性质有关。 2.错误:应改为:横向力系数可以衡量不同重量汽车的在弯道的稳定程度。 3.错误:应改为:按二者最大值计算确定 4.错误:应改为:?=??

的缓和曲线,则超高过渡可仅在缓和曲线的一个区段进行。 答出基本要点得5分;答得不完整酌情扣分。 2.答案及评分标准 要点: 限制最大合成坡度可以防止急弯陡坡组合,引起横向滑移危机行车安全;限制最小的合成坡度主要以防止道路排水不畅,影响行车安全 答出每一要点给2.5分。答得不完整酌情扣分。 五、叙述题与作图题(15分) 1.答案及评分标准 要点: 纸上定线的方法步骤及作用: (1)定导向线。 ①分析地形,找出各种可能的走法。 ②求平距a,并定匀坡线。作用一是放通了路线,证明方案是成立的,二是放坡可发现中间控制点,为下步工作提供依据。 ③确定中间控制点,分段调整纵坡,定导向线。目的是大概定出具有理想坡度的折线,利用了有利地形,避开了不利地形,可作为试定平面线形的参考。 (2)修正导向线。 ①试定平面线形,点绘纵断面图,设计理想纵坡 ②定修正导向线。目的:用纵断面修改平面,避免纵向大填大挖 ③定二次导向线。目的:用横断面最佳位置修正平面,避免横向填挖过大。 (3)具体定线。 在二次修正导向线基础取反复试线,采取直线型定线方法或曲线型定线方法,定出平面线形。 评分标准: 本题共10分。纸上定线的方法步骤6分;作用要点4分,每一要点给1分。 2.答案及评分标准

(A卷) 赣南师范学院 2010—2011学年第一学期期末考试试卷(A卷)(闭卷)年级 2008 专业电子科学与技术(本)课程名称 EDA技术基础 2、学生答题前将密封线外的内容填写清楚,答题不得超出密封线; 3、答题请用蓝、黑钢笔或圆珠笔。 一、单项选择题(30分,每题2分) 1.以下关于适配描述错误的是 B A.适配器的功能是将综合器产生的网表文件配置于指定的目标器件中,使之产生最终的下载文件 B.适配所选定的目标器件可以不属于原综合器指定的目标器件系列 C.适配完成后可以利用适配所产生的仿真文件作精确的时序仿真 D.通常,EDAL软件中的综合器可由专业的第三方EDA公司提供,而适配器则需由FPGA/CPLD供应商提供 2.VHDL语言是一种结构化设计语言;一个设计实体(电路模块)包括实体与结构体两部分,结构体描述 D 。 A.器件外部特性B.器件的综合约束 C.器件外部特性与内部功能D.器件的内部功能 3.下列标识符中, B 是不合法的标识符。 A.State0 B.9moon C.Not_Ack_0 D.signall 4.以下工具中属于FPGA/CPLD集成化开发工具的是 D A.ModelSim B.Synplify Pro C.MATLAB D.QuartusII 5.进程中的变量赋值语句,其变量更新是 A 。 A.立即完成B.按顺序完成 C.在进程的最后完成D.都不对 6.以下关于CASE语句描述中错误的是 A A.CASE语句执行中可以不必选中所列条件名的一条 B.除非所有条件句的选择值能完整覆盖CASE语句中表达式的取值,否则最末一个条件句的选择必须加上最后一句“WHEN OTHERS=><顺序语句>” C.CASE语句中的选择值只能出现一次 D.WHEN条件句中的选择值或标识符所代表的值必须在表达式的取值范围 7.以下哪个程序包是数字系统设计中最重要最常用的程序包 B A.STD_LOGIC_ARITH B.STD_LOGIC_1164 C.STD_LOGIC_UNSIGNED D.STD_LOGIC_SIGNED 8.基于EDA软件的FPGA / CPLD设计流程为:原理图/HDL文本输入→A →综合→适配→时序仿真→编程下载→硬件测试。 A.功能仿真B.逻辑综合C.配置D.引脚锁定 9.不完整的IF语句,其综合结果可实现 D A.三态控制电路B.条件相或的逻辑电路 C.双向控制电路D.时序逻辑电路 10.下列语句中,属于并行语句的是A A.进程语句B.IF语句C.CASE语句D.FOR语句11.综合是EDA设计流程的关键步骤,综合就是把抽象设计层次中的一种表示转化成另一种表示的过程;在下面对综合的描述中, C 是错误的。 A.综合就是将电路的高级语言转化成低级的,可与FPGA / CPLD的基本结构相映射的网表文件 B.综合可理解为,将软件描述与给定的硬件结构用电路网表文件表示的映射过程,并且这种映射关系不是唯一的 C.综合是纯软件的转换过程,与器件硬件结构无关 D.为实现系统的速度、面积、性能的要求,需要对综合加以约束,称为综合约束 12.CPLD的可编程是主要基于什么结构 D 。 A.查找表(LUT)B.ROM可编程 C.PAL可编程D.与或阵列可编程 13.以下器件中属于Altera 公司生产的是 B A.ispLSI系列器件B.MAX系列器件 C.XC9500系列器件D.Virtex系列器件 14.在VHDL语言中,下列对时钟边沿检测描述中,错误的是 D A.if clk'event and clk = '1' then B.if clk'stable and not clk = '1' then C.if rising_edge(clk) then D.if not clk'stable and clk = '1' then 15.以下关于状态机的描述中正确的是 B A.Moore型状态机其输出是当前状态和所有输入的函数 B.与Moore型状态机相比,Mealy型的输出变化要领先一个时钟周期C.Mealy型状态机其输出是当前状态的函数

试卷参考答案和评分标准The document was prepared on January 2, 2021

试卷参考答案 一. 听力材料及答案. Ⅰ. 听录音,把你所听到单词的序号填写在题前括号内。(10分) 1.house 2. bedroom 3. wash 4. dishes 5. making 6. dirty 7. women 8. without 9. work 10. dresser 1----5 A B A B B 6----10 B B A B A Ⅱ. 听句子,从 ABCD 四个选项中选出所包含的信息,并将字母标号填写在题前的括号内。(10分) ( C ) Ming is coming to Canada by plane. ( A ) ’s time to make lunch. ( D ) ’s the sink Here it is. ( C ) did she arrive She arrived at 5:50. ( B ) is Mary’s favourite shape. Ⅲ. 听对话, 用1,2,3……排列下列图片顺序,并将序号写在相应图片的括号内。(10分) 1. A: Is it a refrigerator? B: Yes, it is. 2.A: When do you go to school?

B: I go to school on September first. 3. A: What’s he doing B: He is writing a letter for his mother. 4.A: What’s the temperature outside? B: It’s 20 degrees. 5.A: What’s this B: This is a kitchen. 图片顺序为:1( 5 ),2( 3 ),3( 1 ),4( 2 ),5( 4 ) Ⅳ. 听录音,根据听到的句子的意思写出句子中所缺的英语单词,每空只填一词。(10分) 1. is going to play the piano . 2.I like to have my boots on a rainy day. 3.This is the way we take a shower , on a Sunday morning. 4.Look! This is the living room .

2007 至2008学年度第二学期期末考核 《EDA》试题(开卷) 卷号:B 时间:120 分钟 2008 年6 月 专业:电子信息工程学号:姓名: 一填空题(20分) 1、VHDL 2、DEVICE.LIB SYMBOLS.LIB 3、实际零件焊接到电路板时所指示的外观和焊点的位置 4、电子设计自动化电子CAD技术 5、A L T E R A,X I L I N X 6、WAIT 7、电路连接 8、SRAM-BASE 9、2.54mm 300mil 10、元件外观和元件引线端子的图形 二名词解释(20分) 1 PLD/FPGA PLD是可编程逻辑器件(Programable Logic Device)的简称,FPGA是现场可编程门阵列(Field Programable Gate Array)的简称,两者的功能基本相同,只是实现原理略有不同,所以我们有时可以忽略这两者的区别,统称为可编程逻辑器件或PLD/FPGA。 2.过孔 当需要连接两个层面上的铜膜走线时就需要过孔(Via),过孔 又称为贯孔、沉铜孔和金属化孔。 过孔分为穿透式(Through)、半隐藏式(Blind)和隐藏式(Buried) 3.铜膜线 就是连接两个焊盘的导线,称为Track,一般铜膜线走线在不 同层面取不同的走向,例如顶层走水平线,则底层走垂直线。顶 层和底层走线之间的连接采用过孔(Via)连接。 4 PROM、PAL和PLA PROM:与阵列固定,或阵列可编程,一般用作存储器,其输入为存储器的地址,输出为存储器单元的内容。但输入的数目太大时,器件功耗增加,其局限性大。 PLA:与或阵列均可编程,但是其慢速特性和相对PAL、PROM而高得多的价格妨碍了它被广泛使用。PAL:或阵列固定,与阵列可编程,其第二代产品GAL具有了可电擦写、可重复编程、可设置加密的功能。 5 自顶向下的/自下而上的设计方法 自下而上的设计方法,使用该方法进行硬件设计是从选择具体元器件开始,并用这些元器件进行逻辑电路设计,从而完成系统的硬件设计,然后再将各功能模块连接起来,完成整个系统的硬件设计,自顶向下的设计方法就是从系统的总体要求出发,自顶向下分三个层次对系统硬件进行设计。 第一个层次是行为描述第二个层次是数据流描述第三个层次为逻辑综合

《光学》试题(一)标准答案及评分标准 一、选择题(每小题2.5分,共25分) 1、D 2、A 3、C 4、B 5、B 6、D 7、A 8、C 9、B 10、C 二、填空题(每小题2分,共20分) ① 6.00×10-4 ② 2(n-1)h ③ 0.458 ④ 120 ⑤ 250 ⑥ 3:1 ⑦ 8.3% ⑧ 2I 0/3 ⑨ 1.22λ/D ⑩ 56.1% 三、试用作图法找像的位置和大小(5分) 四、论述题(10分) (1) 同频率 (2)两光波相遇是有固定的位相差 (3)两光波相遇点相同的振动分量 (4)两光波相遇光程差不能太大,要小于光源的相干长度。 (5)两光波相遇点所产生的振动后的振幅不能太悬殊。 评分标准:每小题各占据2分。如没有论述,则酌情扣分。 五. 1.(a )→x=-20mm 180mm =′=′x f f x S'=60-180=120mm (实像) (5分) (b )x=20mm x'=-180mm (5分) S'=60-180=240mm (虚像) 2.由于右边321n n n ,故没有额外程差,而左边3221,n n n n 发生额外程差 对于右边 λj R r n h n j 22 2=2 λ)5+(=25+2 j R r n j 两式相减,可求得波长 Ο A R r n j 6480=5) r -(=2j 25+2λ 对于左j 级亮纹满足

m m r n R r j n R r j R r n j j j j 24.4=18 =62 .1×210×10×6480×10+4×4=2+=)21 +(==21 -37-22 222 2 左左左λλ λλ 3.设光栅常数为d ,可见光谱两面三刀端波长所对应的光栅方程为 760 ?=θsin 400?=sin 2211K d K d θ 如果发生重叠是400nm 的二级与760nm 的一级: 1 221/760=sin /800=/400?2=sin θθθθ d d d 所以不发生重叠。 而当K 1=3 K 1=2时 1 221)(/1520=/760×2=θsin )(/1200=/400×3=sin θθθ nm d d nm d d 发生重叠 发生重叠时,1级光谱的角宽 d d /360=/)400-760(≈θΔ 发生重叠时, 3×400=2×λ λ= 600 nm 所以重叠范围 600~760 nm 4.当晶片引起的位相差对薄些波长形成全波片时,这些波长的光将不能通过系统,即 π2=)-(20K d n n e λ π K的取值范围 7-010×7800)-(d n n e ~7-010 ×3900)-(d n n e 即9~17 K=9时 ΟA l K n n e 7644=9 000688.0=-= λ09

这是长期总结的EDA期末考试试题 试题一 1-2与软件描述语言相比,VHDL有什么特点? P6 答:编译器将软件程序翻译成基于某种特定CPU的机器代码,这种代码仅限于这种CPU而不能移植,并且机器代码不代表硬件结构,更不能改变CPU的硬件结构,只能被动地为其特定的硬件电路结构所利用。综合器将VHDL程序转化的目标是底层的电路结构网表文件,这种满足VHDL设计程序功能描述的电路结构,不依赖于任何特定硬件环境;具有相对独立性。综合器在将VHDL(硬件描述语言)表达的电路功能转化成具体的电路结构网表过程中,具有明显的能动性和创造性,它不是机械的一一对应式的“翻译”,而是根据设计库、工艺库以及预先设置的各类约束条件,选择最优的方式完成电路结构的设计。 l-3什么是综合?有哪些类型?综合在电子设计自动化中的地位是什么? P5 什么是综合? 答:在电子设计领域中综合的概念可以表示为:将用行为和功能层次表达的电子系统转换为低层次的便于具体实现的模块组合装配的过程。 有哪些类型? 答:(1)从自然语言转换到VHDL语言算法表示,即自然语言综合。 (2)从算法表示转换到寄存器传输级(RegisterTransport Level,RTL),即从行为域到结构域的综合,即行为综合。 (3)从RTL级表示转换到逻辑门(包括触发器)的表示,即逻辑综合。 (4)从逻辑门表示转换到版图表示(ASIC设计),或转换到FPGA的配置网表文件,可称为版图综合或结构综合。 综合在电子设计自动化中的地位是什么? 答:是核心地位(见图1-3)。综合器具有更复杂的工作环境,综合器在接受VHDL程序并准备对其综合前,必须获得与最终实现设计电路硬件特征相关的工艺库信息,以及获得优化综合的诸多约束条件信息;根据工艺库和约束条件信息,将VHDL程序转化成电路实现的相关信息。 1-4在EDA技术中,自顶向下的设计方法的重要意义是什么? P7~10 答:在EDA技术应用中,自顶向下的设计方法,就是在整个设计流程中各设计环节逐步求精的过程。 1-5 IP在EDA技术的应用和发展中的意义是什么? P11~12 答:IP核具有规范的接口协议,良好的可移植与可测试性,为系统开发提供了可靠的保证。 2-1 叙述EDA的FPGA/CPLD设计流程。 P13~16 答:1.设计输入(原理图/HDL文本编辑);2.综合;3.适配;4.时序仿真与功能仿真;5.编程下载;6.硬件测试。 2-2 IP是什么?IP与EDA技术的关系是什么? P24~26 IP是什么? 答:IP是知识产权核或知识产权模块,用于ASIC或FPGA/CPLD中的预先设计好的电路功能模块。 IP与EDA技术的关系是什么? 答:IP在EDA技术开发中具有十分重要的地位;与EDA技术的关系分有软IP、固IP、硬IP:软IP是用VHDL等硬件描述语言描述的功能块,并不涉及用什么具体电路元件实现这些功能;软IP通常是以硬件描述语言HDL源文件的形式出现。固IP是完成了综合的功能块,具有较大的设计深度,以网表文件的形式提交客户使用。硬IP提供设计的最终阶段产品:掩模。 3-1 OLMC(输出逻辑宏单元)有何功能?说明GAL是怎样实现可编程组合电路与时序电路的。 P34~36 答:OLMC单元设有多种组态,可配置成专用组合输出、专用输入、组合输出双向口、寄存器输出、寄存器输出双向口等。 说明GAL是怎样实现可编程组合电路与时序电路的? 答:GAL(通用阵列逻辑器件)是通过对其中的OLMC(输出逻辑宏单元)的编程和三种模式配置(寄存器模式、复合模式、简单模式),实现组合电路与时序电路设计的。 3-2 什么是基于乘积项的可编程逻辑结构? P33~34,40 答:GAL、CPLD之类都是基于乘积项的可编程结构;即包含有可编程与阵列和固定的或阵列的PAL(可编程阵列逻辑)器件构成。 3-3 什么是基于查找表的可编程逻辑结构? P40~41 答:FPGA(现场可编程门阵列)是基于查找表的可编程逻辑结构。 3-7 请参阅相关资料,并回答问题:按本章给出的归类方式,将基于乘积项的可编程逻辑结构的PLD器件归类为CPLD;将基于查找表的可编程逻辑结构的PLD器什归类为FPGA,那么,APEX系列属于什么类型PLD器件? MAX II系列又属于什么类型的PLD器件?为什么? P54~56 答:APEX(Advanced Logic Element Matrix)系列属于FPGA类型PLD器件;编程信息存于SRAM中。MAX II系列属于CPLD类型的PLD器件;编程信息存于EEPROM中。 4-3. 图3-31所示的是双2选1多路选择器构成的电路MUXK,对于其中MUX21A,当s='0'和'1'时,分别有y<='a'和y<='b'。试在一个结构体中用两个进程来表达此电路,每个进程中用CASE语句描述一个2选1多路选择器MUX21A。 LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; ENTITY MUX221 IS PORT(a1,a2,a3:IN STD_LOGIC_VECTOR(1 DOWNTO 0); --输入信号 s0,s1:IN STD_LOGIC; outy:OUT STD_LOGIC);--输出端 END ENTITY; ARCHITECTURE ONE OF MUX221 IS SIGNAL tmp : STD_LOGIC; BEGIN

怀化学院 课程考核标准答案与评分标准 一、名词解释(每小2分,共10分) 1特殊杂质:是指在特定的药物生产和贮藏过程中引入的杂质。 2恒重系指供试品连续两次干燥或灼烧后的重量差异在0.3mg以下的重量. 3准确度:是指用该方法测定结果与真实值或认可的参考值之间接近的程度,一般用回收率(%)表示。 4专属性:指在其他成分(如杂质、辅料等)可能存在时,采用的分析方法能够正确测定被检出物的特性。 5LOD检测限: 指分析方法能够从背景信号中区分出药物时,所需样品中药物的最低浓度,无需定量测定. 二、选择题(每小题2分,共40分) 1A 2B 3D 4B 5A 6A 7C 8C 9D 10D 11B 12B 13 A14D 15C 16D 17D 18C 19A 20B 三、填空题(每空1分,共20分) 1、中国药典,局颁标准 2、千分之一、百分之一、+10% 3、安全有效、先进性、针对性、规范性 4、酸性、硝酸银、氯化银白色、氯化钠 5、水杨酸、澄清度 6、芳伯氨基、酯键 7、新生态氢、砷化氢、砷斑 四、是非判断题(每空1分,共10)

1、测定的精密度用标准差或变异系数表示(√) 2、青霉素钠属于头孢菌素族(×) 3、具有芳香第一胺反应(重氮-偶合反应)的药物是盐酸普鲁卡因(×) 4、异烟肼的特殊杂质是游离肼(√) 5、药物中所含杂质的最大允许量叫做检测限(×) 6、利用麦芽酚反应可鉴别的药物是硫酸链霉素(√) 7、对药品检验工作中测量的有效数字的要求是只允许最末的一位差1(×) 8、用生物学方法测定药物含量,称为含量测定(×) 9、异烟肼的特殊杂质是游离肼(√) 10、《中国药典》(2010年版)检查细菌内毒素所用的试剂是家兔(×) 五、简答题(每小题5分,共10分) 1.药品检验工作的基本程序是什么? 药品检验的基本程序是: (1)取样;(1分) (2)外观性状观察;(1分) (3)鉴别;(1分) (4)检查;(1分) (5)含量测定;(1分) (6)写出检验报告书。 2.含量测定中分析方法的认证指标 含量测定时,采用不同的分析方法及分析不同类别的样品,对分析方法的效能指标的种类及标准的要求也不同。 ①容量分析: 精密度:用原料药精制品考察方法的精密度,5个样品试验数据RSD≯0.2%。 准确度:以回收率表示。原料精制品(>99.5%)或对照品回收率99.7%—100.3%(n=5) 1

测试题一参考答案和评分标准 一、选择题:每题2分,共50分。 二、读图题:(8分) (1)A、辽,B、北宋,C、西夏;(2)澶渊之盟;(3)金、南宋、西夏对峙形势图;(4)郾城大捷,岳飞;(5)经济重心完成南移。(每空1分) 三、连线题:共5分。 ( B )苏轼( A )宋应星( E )关汉卿( C )施耐庵( D )白居易 四、材料解析:第1题9分,第2题8分,本大题共17分。 1、(1)唐太宗;(1分)重视科举,扩充国学;(1分)文成公主入吐蕃(或设立都督府,任用突厥贵族进行管理,保留原有民族的习惯与生活方式;唐太宗为突厥将

领疗伤等)。(1分)(2)武则天时期的治世(2分)和唐玄宗时期的开元盛世(2分)。(3)国家统一,社会安定;统治者大都重视发展生产;科举制为唐朝选拔了大量人才(或统治者大都重用人才);开明的民族政策,民族关系友好;开放的对外政策,对外友好往来等等。言只有理可酌情给分。(3分) 2、(1)唐朝对外交往比较活跃,与亚洲以至非洲、欧洲的一些国家,都有往来;宋朝鼓励海外贸易,还设置了管理海外贸易的市舶司。(2分)对外开放政策。(2分)(2)害怕外商与沿海人民交往滋生事端,便利洋人侵略中国;自恃中国地大物博,藐视西方各国,夜郎自大;(2分)闭关锁国政策。(2分) (3)唐宋的对外开放政策促进了经济的发展,提高了当时中国在世界上的声望;(2分)清朝的闭关政策阻碍了中国的发展和进步,使中国在世界上逐渐落伍了(2分)启示:加强交流、实行开放能够促进社会的进步与发展;闭关自守、盲目自大只能导致落后挨打。我国今天应坚持对外开放,加强与世界各国的经济文化交流与合作(2分)(言之有理,可酌情赋分) 五、融入情境,探究问题(13分) (1)戚继光抗倭;郑成功从荷兰殖民者手中收复台湾;清朝康熙帝时取得两次雅克卫反击战的胜利,遏制了沙俄在我国黑龙江流域的侵略;签订了《尼布楚条约》,划定了中段边界。(4分) (2) 西藏地区:1.建立对达赖、班禅的册封制度,历世达赖、班禅的继承都必须经过中央政府册封;2.雍正时,清朝设置驻藏大臣,与达赖与班禅共同管理西藏事

《EDA》期末试卷 一、选择题(每小题3分,共30分) 1、在下图中,F0的逻辑关系为: A.A0⊕A1 B.A0⊙A1 C.A0·A1 D.A0·A1 2、在VHDL中,用语句()表示clock的下降沿。 A.clock='1' B.clock'EVENT AND clock='1' C.clock='0' D.clock'EVENT AND clock='0' 3、如果p1=’1’,p2=’1’,则执行z <= a WHEN p1 = '1' ELSE b WHEN p2 = '1' ELSE c ;之后z 的值为: A.a B.b C.c D.不确定 4、进程中的信号赋值语句,其信号更新是: A.按顺序完成 B.比变量更快完成 C.在进程最后完成 D.都不对 5、不完整的IF语句,其综合结果可实现: A.时序逻辑电路 B.组合逻辑电路 C.双向电路 D.三态控制电路 6、reg的数据类型为std_logic_vector(7 downto 0),初值为FF,执行reg(0)<=’0’;reg(7 downto 1)<=reg(6 downto 0);之后,reg的值为: A.FF B.FE C.FC D.FD 7、在VHDL中()不能将信息带出对它定义的当前进程。 A. 信号 B. 常量 C. 数据 D. 变量 8、执行下列语句后Q的值等于: …… SIGNAL E: STD_LOGIC_VECTOR (2 TO 5); SIGNAL Q: STD_LOGIC_VECTOR (9 DOWNTO 2); …… E<=(2=>’1’, 4=>’1’, OTHERS=>’0’); Q<=(2=>E (2), 4=>E (3), 5=>’1’, 7=>E (5), OTHERS=>E (4)); …… A.”11011011” B.”00110100” C.”11011001” D.”00101100” 9、在一个VHDL设计中Idata是一个信号,数据类型为std_logic_vector,试指出下面那个赋值语句是错误的。 A.idata <= “00001111”; B.idata <= b”0000_1111”; C.idata <= X”AB”; D.idata <= B”21”; 10、在一个VHDL设计中idata是一个信号,数据类型为integer,数据范围0 to 127,下面哪个赋值语句是正确的。

齐齐哈尔大学试题标准答案及评分标准 考试科目:工业催化原理 适用对象:化工05 使用学期:2008 试卷代码:A 课程编码:001702013 共4道大题 总分80分 共2页 教师须知: 期末考试批完卷后,请将答案随答题纸、成绩单,一起交到学院教科办存档。 一、填空题(每小题5分,共10小题50分) 1.在化学反应中催化剂能加速反应速率而不改变反应的标准自有焓的一种作用。 (3) 均相催化:反应过程中反应物与催化剂形成均一相的催化反应。(1) 多相催化:反应过程中反应物与催化剂处于不同相的催化反应。(1) 2. 催化作用通过改变反应历程改变反应速度 在化学反应中加入催化剂通常可以使反应速度加快,但反应终了时催化剂的终态和始态是不发生变化的,催化剂加速反应速度是通过改变反应历程来实现的。主要是降低了反应的活化能。(5) 3.说明反应速率常数和温度和活化能相关 4. 费米能级:是半导体性质的一个重要物理量,它表示半导体中电子的平均位能。确切的说,它表示在任意温度下,电子出现的几率为1/2的那个能级的能量。(3) 逸出功:把一个电子从半导体内部拉到外部,变成完全自由电子时,所需要的最小能量(2) 5. ①吸附的表面是均匀的(1) ②各吸附中心的能量相同(1) ③吸附粒子间的相互作用可以忽略(1) ④吸附粒子与空的吸附中心碰撞才有可能被吸附,一个吸附粒子只占据一个吸附中心,吸附是单分子层的。(2) 6.扩散,吸附,表面反应,脱附,扩散(5) 7. 分子孔径较小,扩散阻力主要是气体分子与孔径的碰撞。(5) 8. H a pK BH H B a 0lg ≡?-=+ +γγ(4) 表示固体酸酸强度(1) 9. 催化中重要的半导体是过渡金属氧化物或硫化物(2)。半导体分为三类:本征半导体、n-型半导体和p 型半导体。(3)

语文试题答案及评分标准 卷一(选择题,共50分) 一、(本大题10个小题,每小题2分,共20分) 二、(本大题6个小题,每小题3分,共18分) 三、(本大题4小个小题,每小题3分,共12分) 卷二(非选择题,共70分) 四、(本大题5个小题,共15分) 21.(5分) 想要研究自然现象与人类社会的关系,通晓古往今来变化的规律,成为一家之言。 22.(3分) (1)天生我材必有用 (2)我们共享雾霭、流岚、虹霓。 (3)胜似闲庭信步。 (4)以先国家之急而后私仇也。 (5)相逢何必曾相识。 【评分标准】如果答题超过三句,选择正确答案给分。答对一句得1分,答对三句即得满分,答题错误不倒扣分。句中有错别字或漏字、添字,该句不得分。 23.(4分) 五、(本大题5个小题,每小题3分,共15分) 24.(3分) (1)树比人活的长久,但并不以此傲人;(2)树绝对不伤人;(3)树比人坚忍;(4)树

会帮助人。 【评分标准】每点1分,答出三点即可 25、(3分) 这句话运用了象征(托物言志、比喻)的手法,表面上说的是树,实际上说的是人(1分)。“不曾”说明人往往是很坚强的,能够战胜各种不幸和灾难(1分),“却”字使句 意发生了转折,指出人们常常会被名利和赞扬所压垮(1分) 26、(3分) 虔诚、尊敬——嫉妒——自卑、伤感——自信、自强(每一点1分) 27、(3分) 文章的主旨(2分):我们不管身处何种环境,地位如何卑微,都没有理由也不应该自惭 形秽,而应像小草那样坦然、快乐地生活。 草的特征(1分):不因卑微而羞愧、安然的怡然挺立。 28、(3分) 感悟如下均可:自卑人人都有,但要勇于面对;人们虽然会在各个方面存在差异,但不 能自惭形秽,要豁达自信;人应该坦然快乐地生活,你就能走出自卑的泥潭,收获属于 自己的成功。 【评分标准】(只要谈到其中的某一点,意思相近即可得2分,能结合实际生活谈2分)六、作文(45分) 29.【评分标准】 说明:①不写题目扣2分; ②不足700字,每少50字扣2分; ③错别字每2个扣1分,重复的不计,最多扣3分; ④卷面不整洁,字迹潦草,不能进入一类卷。 范文 1、学会转身,是生活的智慧 转身是一种生活方式,让达成目标的人们重新审视生活;转身是一种生活态度,是摒弃名利后的一种本质的回归;转身也是一种选择,是对光鲜外表下深藏的隐患的警醒。二战时期纳粹法西斯在欧洲大肆残杀犹太人,匈牙利处于腥风血雨之中。 当时那里有一位意大利籍商人叫佩拉斯卡,在纷乱的战世中,却选择留在匈牙利解救

一、单项选择题(30分,每题2分) 1.以下关于适配描述错误的是 B A.适配器的功能是将综合器产生的网表文件配置于指定的目标器件中,使之产生最终的下载文件 B.适配所选定的目标器件可以不属于原综合器指定的目标器件系列 C.适配完成后可以利用适配所产生的仿真文件作精确的时序仿真D.通常,EDAL软件中的综合器可由专业的第三方EDA公司提供,而适配器则需由FPGA/CPLD供应商提供 2.VHDL语言是一种结构化设计语言;一个设计实体(电路模块)包括实体与结构体两部分,结构体描述 D 。 A.器件外部特性B.器件的综合约束 C.器件外部特性与内部功能D.器件的内部功能3.下列标识符中, B 是不合法的标识符。 A.State0 B.9moon C.Not_Ack_0 D.signall 4.以下工具中属于FPGA/CPLD集成化开发工具的是 D A.ModelSim B.Synplify Pro C.MA TLAB D.QuartusII 5.进程中的变量赋值语句,其变量更新是 A 。 A.立即完成B.按顺序完成 C.在进程的最后完成D.都不对 6.以下关于CASE语句描述中错误的是 A A.CASE语句执行中可以不必选中所列条件名的一条 B.除非所有条件句的选择值能完整覆盖CASE语句中表达式的取值,否则最末一个条件句的选择必须加上最后一句“WHEN OTHERS=><顺序语句>” C.CASE语句中的选择值只能出现一次 D.WHEN条件句中的选择值或标识符所代表的值必须在表达式的取值范围 7.以下哪个程序包是数字系统设计中最重要最常用的程序包 B A.STD_LOGIC_ARITH B.STD_LOGIC_1164 C.STD_LOGIC_UNSIGNED D.STD_LOGIC_SIGNED 8.基于EDA软件的FPGA / CPLD设计流程为:原理图/HDL文本输入→ A →综合→适配→时序仿真→编程下载→硬件测试。 A.功能仿真B.逻辑综合C.配置D.引脚锁定 9.不完整的IF语句,其综合结果可实现 D A.三态控制电路B.条件相或的逻辑电路 C.双向控制电路D.时序逻辑电路 10.下列语句中,属于并行语句的是A A.进程语句B.IF语句C.CASE语句D.FOR 语句 11.综合是EDA设计流程的关键步骤,综合就是把抽象设计层次中的一种表示转化成另一种表示的过程;在下面对综合的描述中, C 是错误的。 A.综合就是将电路的高级语言转化成低级的,可与FPGA / CPLD 的基本结构相映射的网表文件 B.综合可理解为,将软件描述与给定的硬件结构用电路网表文件表示的映射过程,并且这种映射关系不是唯一的 C.综合是纯软件的转换过程,与器件硬件结构无关 D.为实现系统的速度、面积、性能的要求,需要对综合加以约束,称为综合约束 12.CPLD的可编程是主要基于什么结构 D 。 A.查找表(LUT)B.ROM可编程

2000年级临床医学本科2003-2004年度期末外科学试卷A标准答案 、选择题(第23道题答案为多个,故这道题均给分) 1 . D 2.C 3.B 4.B 5.D 6.C 7.D 8.B 9.C10.E11.D12.C13.D14.C 15.A16.C17.C18.B19.C20.D21.D 22.D23.B24.A25.B26.C27.B 28.C29.D30.E 二、名词解释(每小 题 3分) 1、嵌顿性疝:疝门较小而腹内压突然增高时(1分),疝内容物可强行扩张疝囊颈而进入 疝囊(1分),随后因囊颈的弹性收缩,又将内容物卡住,使其不能回纳(1分)。 2、绞窄性肠梗阻:系指梗阻并伴有肠壁血运障碍者。 3、门脉高压症:门静脉的压力正常值约在13—24cmH2O之间,如果压力高于此界限,就 定义为门脉高压症(2分)。临床表现为脾肿大脾亢,食管胃底静脉曲张,腹水等症状(1 分)。 4、胆源性胰腺炎:胆道疾病造成胆汁返流至胰管引起的急性胰腺炎。一般指胆囊或胆总 管的结石通过oddi括约肌引起损伤或嵌顿于壶腹部引起的胰腺炎。(讲到上述一点即可得3分) 5、D2胃癌切除术:胃周淋巴结清除范围以D(disection)表示(1分),第二站淋巴结(N2) 完全清除者为D2。 三、问答题(每小题6分) 1、原发性肝癌的诊断 答:(1)凡是中年以上,特别是有肝病史的病人,如有原因不明的肝区疼痛、消瘦、进行性肝肿大者应考虑有肝癌的可能。(2分) (2)定性诊断(2分): a. 血清甲胎蛋白的测定本法对诊断肝细胞癌有相对专一性。放免测定持续血 清AFP大于或等于400ug/L ,并能排除妊娠、活动性肝病、生殖腺胚胎源性肿瘤 等,即可考虑肝癌的诊断。(1.5分) b. 血液酶学及其他肿瘤标记物检查Y-GT及同工酶,AFP异质体,异常凝血 酶原,a 1-抗胰蛋白酶,AKP等也可作为辅助诊断,但缺乏特异性。(0.5 分) (3)定位诊断(2分) a. B超诊断符合率达84%,非侵入性是其优点。 b. CT检查诊断符合率达90%以上。 c. DSA(肝动脉造影检查)对〈2 cm的小肝癌阳性率高达9 0%。 d. MRI、放射性核素肝扫描、X线检查等。 (说出三项影象检查即给2分) 2 ?胆囊结石的临床表现及相关并发症 有症状型胆囊结石的主要临床表现为 〈1〉消化不良等胃肠道症状:进油腻性食物后出现上腹隐痛不适、饱胀、 暧气、厄逆等。(1分) 〈2〉胆绞痛是其典型表现:疼痛位于上腹部,呈连续性,向肩部放射伴恶心 呕吐,系进油腻食物后或结石移位致胆囊收缩所致。(1分) 〈3〉Mirizzi综合征:持续嵌顿或压迫于胆囊壶腹部及颈部的较大结石引起肝

一、单项选择题(30分) 1.以下描述错误的是 C A.QuartusII是Altera提供的FPGA/CPLD集成开发环境 B.Altera是世界上最大的可编程逻辑器件供应商之一 C.MAX+plusII是Altera前一代FPGA/CPLD集成开发环境QuartusII的更新换代新产品 D.QuartusII完全支持VHDL、Verilog的设计流程 2.以下工具中属于FPGA/CPLD开发工具中的专用综合器的是 B A.ModelSim B.Leonardo Spectrum C.Active HDL D.QuartusII 3.以下器件中属于Xilinx 公司生产的是 C A.ispLSI系列器件 B.MAX系列器件 C.XC9500系列器件 D.FLEX系列器件 4.以下关于信号和变量的描述中错误的是 B A.信号是描述硬件系统的基本数据对象,它的性质类似于连接线 B.信号的定义范围是结构体、进程 C.除了没有方向说明以外,信号与实体的端口概念是一致的 D.在进程中不能将变量列入敏感信号列表中 5.以下关于状态机的描述中正确的是 B A.Moore型状态机其输出是当前状态和所有输入的函数 B.与Moore型状态机相比,Mealy型的输出变化要领先一个时钟周期 C.Mealy型状态机其输出是当前状态的函数 D.以上都不对 6.下列标识符中, B 是不合法的标识符。 A.PP0 B.END C.Not_Ack D.sig 7.大规模可编程器件主要有FPGA、CPLD两类,下列对CPLD结构与工作原理的描述中,正确的是 C 。 A.CPLD即是现场可编程逻辑器件的英文简称 B.CPLD是基于查找表结构的可编程逻辑器件 C.早期的CPLD是从GAL的结构扩展而来 D.在Altera公司生产的器件中,FLEX10K 系列属CPLD结构 8.综合是EDA设计流程的关键步骤,在下面对综合的描述中, D 是错误的。 A.综合就是把抽象设计层次中的一种表示转化成另一种表示的过程 B.综合就是将电路的高级语言转化成低级的,可与FPGA / CPLD的基本结构相映射的网表文件 C.为实现系统的速度、面积、性能的要求,需要对综合加以约束,称为综合约束 D.综合可理解为,将软件描述与给定的硬件结构用电路网表文件表示的映射过程,并且这种映射关系是唯一的(即综合结果是唯一的) 9.嵌套使用IF语句,其综合结果可实现 A 。 A.带优先级且条件相与的逻辑电路 B.条件相或的逻辑电路 C.三态控制电路 D.双向控制电路 10.在VHDL语言中,下列对时钟边沿检测描述中,错误的是 D 。 A.if clk'event and clk = ‘1’ then B.if falling_edge(clk) then C.if clk’event and clk = ‘0’ then D.if clk’stable and not clk = ‘1’ then 11.下列那个流程是正确的基于EDA软件的FPGA / CPLD设计流程 B A.原理图/HDL文本输入→适配→综合→功能仿真→编程下载→硬件测试B.原理图/HDL文本输入→功能仿真→综合→适配→编程下载→硬件测试C.原理图/HDL文本输入→功能仿真→综合→编程下载→→适配硬件测试; D.原理图/HDL文本输入→功能仿真→适配→编程下载→综合→硬件测试12.在VHDL语言中,下列对进程(PROCESS)语句的语句结构及语法规则的描述中,正确的是 A 。 A.PROCESS为一无限循环语句;敏感信号发生更新时启动进程,执行完成后,等待下一次进程启动 B.敏感信号参数表中,应列出进程中使用的所有输入信号 C.进程由说明部分、结构体部分、和敏感信号参数表三部分组成 D.当前进程中声明的变量也可用于其他进程 13.下列语句中,不属于并行语句的是 B A.进程语句 B.CASE语句 C.元件例化语句 D.WHEN…ELSE…语句 14.VHDL语言共支持四种常用库,其中哪种库是用户的VHDL设计现行工作库 D A.IEEE库 B.VITAL库C.STD库D.WORK库15.VHDL语言是一种结构化设计语言;一个设计实体(电路模块)包括实体与结构体两部分,结构体描述 D 。 A.器件外部特性 B.器件的综合约束 C.器件外部特性与内部功能 D.器件的内部功能 二、EDA名词解释,写出下列缩写的中文含义(10分) 1.CPLD:复杂可编程逻辑器件 2.ASIC:专用集成电路 3.LUT:查找表 4.EDA:电子设计自动化 5.ROM:只读存储器 三、程序填空题(20分) 以下是一个模为24(0~23)的8421BCD码加法计数器VHDL描述,请补充完整