实验一 原理图输入设计实验

一、实验目的

1、 初步了解MAX +plus Ⅱ软件。

2、 学习和掌握原理图输入方式,了解设计这一种迅速入门的便捷工具。

3、 学习和掌握EDA 的波形分析工具及分析方法。

二、实验要求

1、 设计半加器的原理图。

2、 用仿真的方法,进行半加器的波形分析。

3、 生成半加器的底层器件。

4、 组成一位全加器。

5、 在EDA 实验箱上下载实验程序并验证一位全加器。

三、实验设备

1、 装有MAX +plus Ⅱ计算机 一台

2、 EDA ——Ⅳ实验箱 一台

四、实验原理

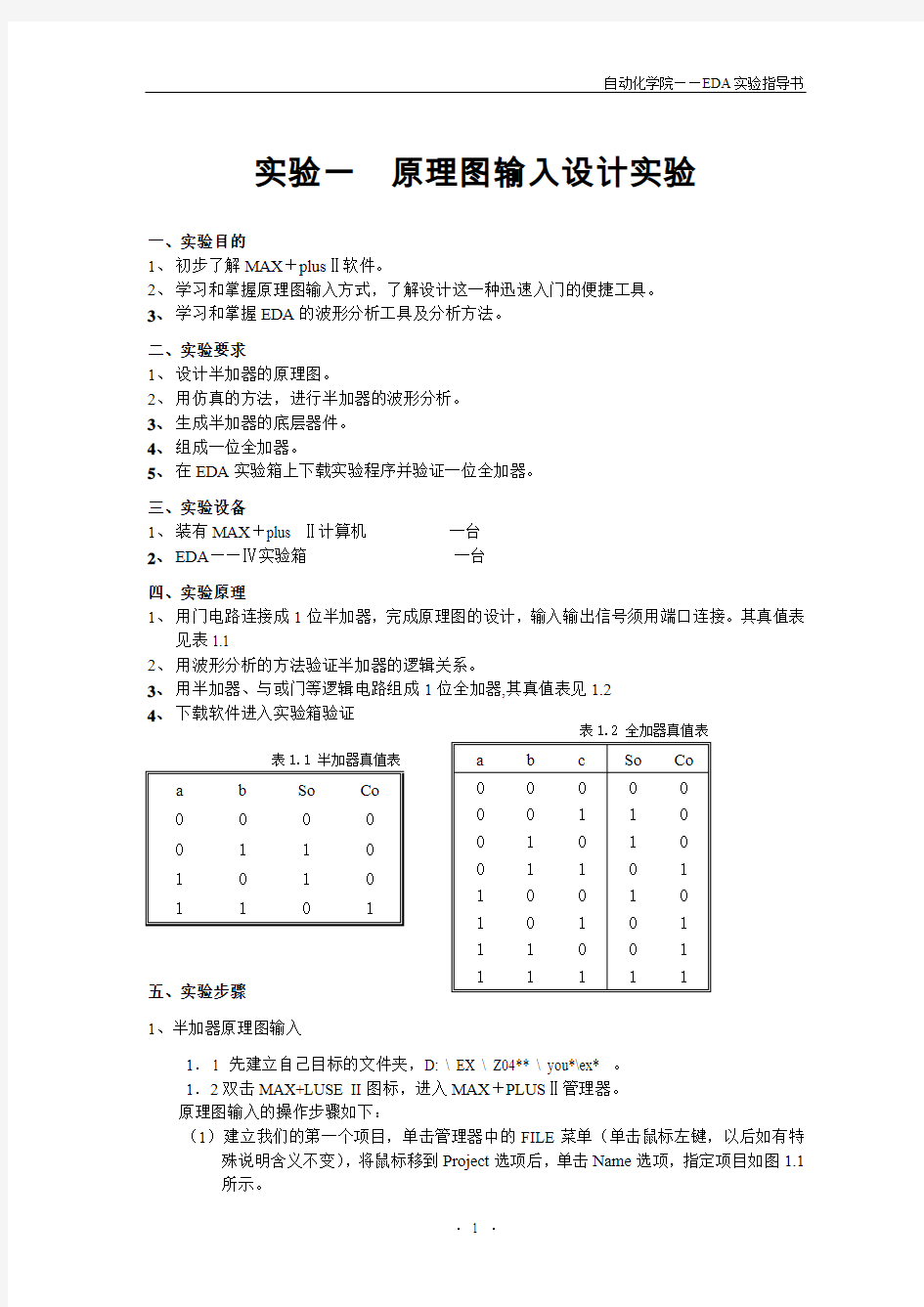

1、 用门电路连接成1位半加器,完成原理图的设计,输入输出信号须用端口连接。其真值表

见表1.1

2、 用波形分析的方法验证半加器的逻辑关系。

3、 用半加器、与或门等逻辑电路组成1位全加器,其真值表见1.2

4、 下载软件进入实验箱验证

五、实验步骤

1、半加器原理图输入

1. 1 先建立自己目标的文件夹,D: \ EX \ Z04** \ you*\ex* 。

1.2双击MAX+LUSE II 图标,进入MAX +PLUS Ⅱ管理器。

原理图输入的操作步骤如下:

(1) 建立我们的第一个项目,单击管理器中的FILE 菜单(单击鼠标左键,以后如有特

殊说明含义不变),将鼠标移到Project 选项后,单击Name 选项,指定项目如图1.1

所示。

表1.2 全加器真值表

表1.1 半加器真值表

图1.1 指定项目名的屏幕

在Project Name的输入编辑框中,键入设计半加器项目名称“hadder”,屏幕如图1.1所示:(注意项目所存放的目录):

(2)再在管理器中单击File \ New选项,设定图形文件。选择Graphic Editor file,单击OK按钮后,便进入到MAX+PLUSE II 的图形编辑器。

(3)归属项目文件File \ Project \ Set Project to Current File;

(4)保存半加器的文件名;屏幕如图1.2所示;

图1.2 欲保存文件前的屏幕

(5)如图1.3所示,选择图形编辑器的Symbol Name 输入编辑框中键入AND2后,单击ok按钮。此时可看到光标上粘着被选的符号,将其移到合适的位置(参考图 1.4)

单击鼠标左键,使其固定;

图1.3 选择元件符号的屏幕

(6)重复(2)、(3)步骤,在图中安放input、output等元件符号,如图1.4所示;

图1.4放置所有元件符号的屏幕

(7)在图1.4中,用移动光标的方法将元器件之间进行连线;

图1.5 完成全部连接线的屏幕

图中器件:AND2 、XNOR、EXP、INPUT、OUTPUT

(8)重复(5)的方法将完成所有的电路连线,如图1.5所示;

(9)在图1.5的界面下,对半加器的原理图进行编译;对文件进行编译,单击编译器快捷方式按钮;

(10)单击Start按钮后,计算机开始处理数据,其进度情况用水平线表示;

(11)如果有“0 errors”和“0 warnings”字符出现,则表示编译完全通过,单击确定OK按钮后;

(12)在图形编辑器界面上,建立底层器件(加封),在File \ Great Default Symbol 封装半加器;

(13)一般警告性错误可以忽略;

(14)编译结束后,即可退出编译窗口,即在编译对话框中选择关闭按钮即可;

2、波形编辑

波形编辑的操作步骤如下:

(1)建立波形文件,在MAX+PLUS II的管理器内,单击File \ New选项下,选择Waveform Editor file,并单击其右边的小黑箭头,在下拉选项中“*.scf”,单击

OK按钮后,便进入到MAX+PLUS II的波形编辑器;

(2)归属其项目下File \ Project \ Set Project to Current File;;

(3)在波形编辑器中,选择Node \ Enter Node From SNF,将出现信号分析导入选择

对话框,如图1.6所示;

图1.6 信号分析导入选择分析输入信号引脚

(4)在图1.6内的Node Enter Node From SNF的文本编辑框中,双击List按键,全选择后,单击OK按钮后,进入输入信号待编辑状态;

(5)在信号编辑器内,编辑输入信号,原则是输入信号的组合,应该覆盖所有的逻辑关系,如图1.7所示。(其方法为首先选中一个要赋值的信号区间,按住鼠标左键,在区间范围内拉出一个黑色区域,松开鼠标左键,再点左边工具栏上的“1”,使这个时间段赋值为高电平时间;注意时间不要选择太小,比如就选10ns,这样结果可能不对,因为电路的延迟可能就达到10ns);

图1.7 编辑输入信号的屏幕

另外在“options”项目下,可进行下面设置:

①Snap to Grid:鼠标按网格选取,用鼠标左键可以决定是否选取;

②Show Grid显示网格;

③Grid Size:设置网格大小;

④End Time:设置仿真结束时间0.5us的仿真时间;

(6)保存波形文件,单击File \ Save As菜单,后缀为*.scf;

(7)对波形文件进行编译,单击编译器快捷方式按钮;

(8)编译结束,退出编译窗口,即在编译对话框中点击关闭按钮即可;

(9)在MAX+plusⅡ\ Simulator 进行仿真;

(10)在波形上可分析输入与输出实验结果,验证逻辑关系,如图1.8所示;

图1.8 波形分析输出

(11)对照表1.1,验证逻辑关系;

(12)(选作)观察自动分配引脚,单击按钮,屏幕如图1.9所示;

图1.17 观察自动分配引脚的屏幕

(13)(选作)双击Fit查看引脚分配情况,如图1.10所示;

图1.10 查看引脚分配的屏幕

(14)(选作)在MAX+plusⅡ\ Floorplan Editor 观察资源分配情况,如图1.11所示;

图1.11 查看芯片资源分配的屏幕

3、位全加器实验

(1)在MAX+plusⅡ管理器的File \ New内,新建一个全加器图形文件;

(2)归属项目文件File \ Project \ Set Project to Current File;

(3)保存文件,全加器原理图文件名不可与半加器器件原理图的文件名相同;

(4)半加器的基础之上,组成1位全加器,如图1.12所示;

(5)对全加器原理图进行第一次编译;

图1.12 1位全加器组成

图中器件:OR2、INPUT、OUTPUT

(6)选择器件型号,在图1.8中单击Assign \ Device菜单,屏幕如图1.10所示;

图1.13 选择待编程芯片的屏幕

(7)全加器进行第二次编译;

(8)必须做手动接口的引脚分配,Assign \ Pin / Location / Chip;如图1.14;(可以参照实验箱的引脚分配图。(附录三));(原理图端口与芯片组引脚需一一对应)(9)全加器进行第三次编译;

图1.14 引脚分配图

(10)程序下载实验箱,

(11)在图1.8中(此处认为实验板已安装妥当,有关安装方法见实验板详细说明)单击按钮,屏幕显示如图1.15所示。

图1.15 程序下载

(12)在图1.15中点击“Program”或者选择“Configure”即可进行下载;

(13)如有问题,点击(1 Programming File),选择相应的下载文件;

(14)在实验箱上验证实验结果;

(15)操作开关SW1、SW2、SW3为A、B、C输入信号,观测发光二极管D101、D102为Cout与Sout输出状态并验证全加器真值表;

硬件资源分配

EPF10K10LC84-3

引脚设备装置器件原理图端口

@36 SW3 Cin

@35 SW2 Bin

@30 SW1 Ain

@17 D101 Cout

@16 D102 Sout

六、思考题

1、如果在下载前未选择器件,会出现什么问题?为什么?

2、如果器件的引脚分配发生冲突了,会出现什么问题?如何解决?

3、

1、在一旅游胜地,有两辆缆车可供游客上下山,请设计一个控制缆车正常运行的逻辑电路。要求:缆车A和B在同一时刻只能允许一上一下的行驶,并且必须同时把缆车的门关好后才能行使。设输入为A、B、C,输出为Y。(设缆车上行为“1”,门关上为“1”,允许行驶为“1”) (1) 列真值表;(4分) (2)写出逻辑函数式;(3分) (3)用基本门画出实现上述逻辑功能的逻辑电路图。(5分) 解:(1)列真值表:(3)逻辑电路图: A B C Y 000 001 010 011 100 101 110 111 (2)逻辑函数式: 2、某同学参加三类课程考试,规定如下:文化课程(A)及格得2分,不及格得0分;专业理论课程(B)及格得3分,不及格得0分;专业技能课程(C)及格得5分,不及格得0分。若总分大于6分则可顺利过关(Y),试根据上述内容完成: (1)列出真值表; (2)写出逻辑函数表达式,并化简成最简式; (3)用与非门画出实现上述功能的逻辑电路。 (3)逻辑电路图 A B C Y 000 001 010 011 100 101 110 111 (2)逻辑函数表达式3、中等职业学校规定机电专业的学生,至少取得钳工(A)、车工(B)、电工(C)中级技能证书的任意两种,才允许毕业(Y)。试根据上述要求:(1)列出真值表;(2)写出逻辑表达式,并化成最简的与非—与非形式;(3)用与非门画出完成上述功能的逻辑电路。 解:(1(3)逻辑电路: A B C Y 000 001 010 011 100 101 110 111 (2)逻辑表达式: 最简的与非—与非形式: 4、人的血型有A、B、AB和O型四种,假定输血规则是:相同血型者之间可输出,AB血型者可接受其他任意血型,任意血型者可接受O型血。图1是一个输血判断电路框图,其中A1A0表示供血者血型,B1B0表示受血者型,现分别用00、01、10和11表示A、B、AB和O四种血型。Y 为判断结果,Y=1表示可以输血,Y=0表示不允许输血。请写出该判断电路的真值表、最简与—或表达式,并画出用与非门组成的逻辑图。 输血判断电路框图: 解:(1)真值表:(3)逻辑图: 输入输出 A1A0B1B0Y 0000 0001 0010 0011

原理图设计规范 本文档的目的在于说明使用PROTEL和ORCAD进行原理图设计时的一些注意事项,为设计人员提供设计规范,方便设计人员之间进行交流和相互检查。 第一部分:PROTEL设计规范 一、原理图元件封装使用标准库命名,按照《元件库引用说明》执行;电路设计 中有用到新的封装的请填写《新建封装申请》后建立新封装,并根据标准库的命名标准将其封装名填入相应的原理图元件封装里面。 二、PROTEL原理图的电气法则的测试ERC:要求没有错误能正确导出网表,1.执行菜单命令【Tool】/【ERC…】; 2.执行上面的命令后在出现以下的电气法则测试对话框,并设置: ⑴.在【ERC Options】下选取以下几项: ●【Multiple net name on net】检测同一网络命名多个网络名称; ●【Unconnectde net labes】检测未实际连接的网络标号 ●【Unconnected power objects】检测为实际连接的电源图件; ●【Duplicate sheet numbers】检测电路图编号的重号; ●【Duplicate component designator】检测元件的重号; ●【Bus label format errors】检测总先标号格式错误; ●【Bus label format errors】检测输入引脚的浮接; ⑵.在【Options】下选取以下几项: ●【Create report file】在测试后,会自动在将测试结果存在报告文件中(*.erc), 文件名和与原理图名一致; ●【Add error markers】在测试后,会自动在错误位置上放置错误符号; ⑶.【Sheet to Netlist】测试原理图的范围设置为【Active project】; ⑷.【Net Identifier Scope】选择网络识别器的范围设置为【Sheet Symbol/Port Connection】;

实验一 用原理图输入方法设计8位全加器 1.实验目的和要求 本实验为综合性实验,综合了简单组合电路逻辑,MAX+plus 10.2的原理图输入方法, 层次化设计的方法等内容。其目的是通过一个8位全加器的设计熟悉EDA 软件进行电子线路设计的详细流程。学会对实验板上的FPGA/CPLD 进行编程下载,硬件验证自己的设计项目。 2.实验原理 1位全加器可以用两个半加器及一个或门连接而成,半加器原理图的设计方法很多,我们用一个与门、一个非门和同或门(xnor 为同或符合,相同为1,不同为0)来实现。先设计底层文件:半加器,再设计顶层文件全加器。 (1) 半加器的设计: 半加器表达式:进位:co=a and b 和:so=a xnor ( not b ) 半加器原理图如下: (2) 全加器的设计: 全加器原理图如下: 3.主要仪器设备(实验用的软硬件环境) 实验的硬件环境是: 微机 I113co a so b 1 0101 0110001 10 0co so b a not xnor2 and2 I113ain cout cout ain bin sum cin bin sum cin f_adder or2a f e d u3 u2 u1 b a c co so B co so B h_adder A h_adder A

EDA实验开发系统 ZY11EDA13BE 并口延长线,JTAG延长线 实验的软件环境是: MAX+plus 10.2 4.操作方法与实验步骤 ●按照4.1 节介绍的方法与流程,完成半加器和全加器的设计,包括原理图输入、编译、综合、适配、仿真、实验板上的硬件测试,并将此全加器电路设置成一个硬件符号入库。 ●建立一个更高的原理图设计层次,利用以上获得的1位全加器构成8位全加器,并完成编译、综合、适配、仿真、硬件测试。 5.实验内容及实验数据记录 1.设计半加器: 用原理图输入的方法输入一个半加器的逻辑图,如图所示: 然后在assign里头的device里头根据试验箱的芯片设置Decices,接着就设置输入输出荧脚的输入端和输出端,设置如表1所示: 表1.半加器引脚端口设置 引脚名称设置端口 ain input Pin=45 bin input Pin=46 co output Pin=19 so output Pin=24 然后Save,名称为h_add.gdf,再save & Compile。 结果如图所示:

1.5 PCB 板的设计步骤 (1 )方案分析 决定电路原理图如何设计,同时也影响到 PCB 板如何规划。根据设计要求进行方案比较、选择,元 器件的选择等,开发项目中最重要的环节。 (2 )电路仿真 在设计电路原理图之前,有时会会对某一部分电路设计并不十分确定,因此需要通过电路方针来验 证。还可以用于确定电路中某些重要器件参数。 (3 )设计原理图元件 PROTEL DXP 提供了丰富的原理图元件库,但不可能包括所有元件,必要时需动手设计原理图元件,建立 自己的元件库。 (4)绘制原理图 找到所有需要的原理元件后,开始原理图绘制。根据电路复杂程度决定是否需要使用层次原理图。完成原 理图后,用ERC (电气法则检查)工具查错。找到岀错原因并修改原理图电路,重新查错到没有原则性错误为 止。 5 )设计元件圭寸装 和原理图元件一样, PROTEL DXF 也不可能提供所有元件的封装。需要时自行设计并建立新的元件封装库。 6)设计PCB 板 确认原理图没有错误之后,开始 PCB 板的绘制。首先绘岀 PCB 板的轮廓,确定工艺要求(如使用几层板 等)。然后将原理图传输到 PCB 板中,在网络表、设计规则和原理图的引导下布局和布线。利用设计规则查 错。是电路设计的另一个关键环节,它将决定该产品的实用性能,需要考虑的因素很多,不同的电路有不同 要求 (7 )文档整理 对原理图、PCB 图及器件清单等文件予以保存,以便以后维护和修改 DXP 的元器件库有原理图元件库、 PCB 元件库和集成元件库,扩展名分别为 DXP 仍然可以打开并使用 Protel 以往版本的元件库文件。 在创建一个新的原理图文件后 ,DXP 默认为该文件装载两个集成元器件库: Miscellaneous Connectors.IntLib 。因为这两个集成元器件库中包含有最常用的元器件。 注意: Protel DXP 中,默认的工作组的文件名后缀为 .PrjGrp ,默认的项目文件名后缀为 .PrjPCB 。如 果新建的是 FPGA 设计项目建立的项目文件称后缀为 .PrjFpg 。 也可以将某个文件夹下的所有元件库一次性都添加进来, 方法是:采用类似于 Windows 的操作,先选中该文 件夹下的第一个元件库文件后,按住 Shift 键再选中元件库里的最后一个文件,这样就能选中该文件夹下的所 有文件,最后点打开按钮,即可完成添加元件库操作。 3.1原理图的设计方法和步骤 下面就以下图 所示的简单 555定时器电路图为例,介绍电路原理图的设计方法和步骤。 3.1.1创建一个新项目 电路设计主要包括原理图设计和 PCB 设计。首先创建一个新项目,然后在项目中添加原理图文件和 PCB 文件,创建一个新项目方法: ?单击设计管理窗口底部的 File 按钮,弹岀一个面板。 ? New 子面板中单击 Blank Project ( PCB )选项,将弹岀 Projects 工作面板。 ?建立了一个新的项目后,执行菜单命令 File/Save Project As ,将新项目重命名为 "myProject1 . PrjPCB ”保存该项目到合适位置 3.1.2创建一张新的原理图图纸 ?执行菜单命令 New / Schematic 创建一张新的原理图文件。 ?可以看到 Sheetl.SchDoc 的原理图文件,同时原理图文件夹自动添加到项目中。 ?执行菜单命令 File/Save As ,将新原理 SchLib 、PcbLib 、IntLib 。但 Miscellaneous Devices 」ntLib 禾

组合逻辑电路设计心得体会篇一:实验一_组合逻辑电路分析与设计 实验1 组合逻辑电路分析与设计 XX/10/2 姓名:学号: 班级:15自动化2班 ? 实验内容................................................. .. (3) 二.设计过程及讨论 (4) 1.真值表................................................. .(转载于: 小龙文档网:组合逻辑电路设计心得体会)................4 2.表达式的推导................................................. .....5 3.电路图................................................. .................7 4.实验步骤................................................. .............7 5. PROTEUS软件仿真 (9)

三测试过程及结果讨论.....................................11 1.测试数据................................................. ...........11 2.分析与讨论................................................. . (13) 四思考题................................................. (16) 实验内容: 题目: 设计一个代码转换电路,输入为4位8421码输出为4位循环码(格雷码)。 实验仪器及器件: 1.数字电路实验箱,示波器 2.器件:74LS00(简化后,无需使用,见后面) 74LS86(异或门),74LS197 实验目的: ①基本熟悉数字电路实验箱和示波器的使用 ②掌握逻辑电路的设计方法,并且掌握推导逻辑表达式的方法 ③会根据逻辑表达式来设计电路 1.真值表:

实验一 原理图输入设计实验 一、实验目的 1、 初步了解MAX +plus Ⅱ软件。 2、 学习和掌握原理图输入方式,了解设计这一种迅速入门的便捷工具。 3、 学习和掌握EDA 的波形分析工具及分析方法。 二、实验要求 1、 设计半加器的原理图。 2、 用仿真的方法,进行半加器的波形分析。 3、 生成半加器的底层器件。 4、 组成一位全加器。 5、 在EDA 实验箱上下载实验程序并验证一位全加器。 三、实验设备 1、 装有MAX +plus Ⅱ计算机 一台 2、 EDA ——Ⅳ实验箱 一台 四、实验原理 1、 用门电路连接成1位半加器,完成原理图的设计,输入输出信号须用端口连接。其真值表 见表1.1 2、 用波形分析的方法验证半加器的逻辑关系。 3、 用半加器、与或门等逻辑电路组成1位全加器,其真值表见1.2 4、 下载软件进入实验箱验证 五、实验步骤 1、半加器原理图输入 1. 1 先建立自己目标的文件夹,D: \ EX \ Z04** \ you*\ex* 。 1.2双击MAX+LUSE II 图标,进入MAX +PLUS Ⅱ管理器。 原理图输入的操作步骤如下: (1) 建立我们的第一个项目,单击管理器中的FILE 菜单(单击鼠标左键,以后如有特 殊说明含义不变),将鼠标移到Project 选项后,单击Name 选项,指定项目如图 1.1所示。 表1.2 全加器真值表 表1.1 半加器真值表

图1.1 指定项目名的屏幕 在Project Name的输入编辑框中,键入设计半加器项目名称“hadder”,屏幕如图1.1所示:(注意项目所存放的目录): (2)再在管理器中单击File \ New选项,设定图形文件。选择Graphic Editor file,单击OK按钮后,便进入到MAX+PLUSE II 的图形编辑器。 (3)归属项目文件File \ Project \ Set Project to Current File; (4)保存半加器的文件名;屏幕如图1.2所示; 图1.2 欲保存文件前的屏幕 (5)如图1.3所示,选择图形编辑器的Symbol Name 输入编辑框中键入AND2后,单击ok按钮。此时可看到光标上粘着被选的符号,将其移到合适的位置(参考图1.4) 单击鼠标左键,使其固定; 图1.3 选择元件符号的屏幕 (6)重复(2)、(3)步骤,在图中安放input、output等元件符号,如图1.4所示;

原理图的绘制 A、新建工作空间和原理图 项目是每项电子产品设计的基础,在一个项目文件中包括设计中生成的一切文件,比如原理图文件、PCB图文件、以及原理库文件和PCB库文件。在项目文件中可以执行对文件的各种操作,如新建、打开、关闭、复制与删除等。但是需要注意的是,项目文件只是起到管理的作用,在保存文件时项目中的各个文件是以单个文件的形式存在的。所以每完成一个库就保存一次。 新建工作区间 1、在菜单栏中选择File-New-Project-PCB Project. 2、形成一个PCB-Project1.PriPCB面板然后重命名最后分别添加scematic sheet形成Sheet.SchDoc文件保存后面一次添加形成PCB.PcbDoc、Pcblib.Pcblib、schlib.schlib文件分别进行保存。 3、在schlib.schlib文件里面添加你需要的库文件进行保存这时候要区分引脚与网口标号,特别是引脚一定要放置正确按照所发的书上进行标号,创建一个库就保存一次直到你需要的几个模块的器件你都画好了。 4、然后找到库文件将你画好的东西放置到Sheet.SchDoc原理图上面这时候再来放置网口标号用线将该连接的地方连接起来画好了看看自己的和书上的区别检查是否有错误的地方,最后将文件进行保存。点击Libraries面板,点左上角Libraries按钮,

如果你想在所有工程里都用就在Imstalled里点Install添加,如果只想在当前工程里使用就在Projiect里面点Add Library。 5、画封装图。 根据我们焊电路板的板子来测量距离将需要的器件进行封装,封装的过程中那一页会出现一个十字号将焊盘放置在十字号上确保第一个焊盘的x、y值都为零然后按照自己测量的数据一次拍好焊盘在一个在Top Layer这一层上放置,防止完成后切换到Top Overlay上面进行划线封装。对于LED灯要表明它的正极同样的道理没画好一个库进行一次保存直到最终完成了。最终形成了一个PCB Project文件库。 6、所有元器件编号的方法 你可以双击元件来改变,Visual属性为True。还可以让所有元件自动编号。 7、形成PCB图 在原理图里面双击你要添加的那一个模块添加PCB封装图浏览一下然后查看引脚映射是否一一对应如果对应就是没有出现错误最后点设计然后点击形成PCB图就可以了这个过程中也有一个地方查错的只要对了就会有一个对勾。这也是我自己一个一个添加的原因防止哪里出现了错误难以发现、最终画好了是出现的虚实线连接。 8、布线绘制图 这里面可以选择自动布线也可以进行手动添加布线,布线的时候

\ 广州大学学生实验报告 开课学院及实验室:电子信息楼410 2013年5月20日 学院 机械与电气 工程学院 年级、专 业、班 11级电气1班姓名·学号 实验课程名 称 数字电子技术实验成绩 实验项目名称; 实验二设计性实验——组合逻辑电路的设计 指导 老师 一、实验目的 1、学习组合逻辑电路的设计方法; 2、掌握使用通用逻辑器件实现逻辑电路的一般方法。 二、实验原理 使用中、小规模集成电路来设计组合电路时最常见的逻辑电路设计方法。设计的过程通常是根据 给出的实际逻辑问题,求出实现这一逻辑功能的最简单逻辑电路,这就是设计组合逻辑电路时要完成 的工作。 , 组合逻辑电路的设计工作通常可按如下步骤进行。 (1)进行逻辑抽象 (2)写出逻辑函数式 (3)选定器件的类型 (4)将逻辑函数化简或变换成适当形式 (5)根据化简或变换后的逻辑函数式画出逻辑电路的连接图 (6)工艺设计 例设计一个监视交通信号灯工作状态的逻辑电路。每一组信号灯由红、黄、绿3盏灯组成,如图 3-22所示。正常工作情况下,任何时刻必有一盏灯亮,而且只允许有一盏灯亮。而当出现其他5种 点亮状态时,电路发生故障,这是要求发出故障信号,以提醒维护人员前去修理。 { 首先进行逻辑抽象。 取红、黄、绿3盏灯的状态为输入变量,分别用R、Y、G表示,并规定灯亮时为1,不亮为0。取故 障信号为输出变量,以Z表示,并规定正常工作状态下Z=0,发生故障时Z=1。更具题意可列出表3-9 所示的逻辑真值表。 表3-9真值表 R Y G Z\ R Y G Z 000[ 1 1000 00| 1 01011 0{ 1 001101

第3章电路原理图设计基础 在本章中,您将了解到利用Protel 99 SE 进行印刷电路板的设计要经过怎样的步骤;绘制一张完整、正确、漂亮的电路原理图需要经过怎样的步骤;怎样设置图纸的尺寸和原理图编辑器的工作环境等内容。 3.1 电路原理图的设计步骤 根据电路原理图自动转换成印刷电路板图是Protel 99 SE的重要功能之一,因此首先介绍印刷电路板设计的一般步骤。 3.1.1 印刷电路板设计的一般步骤 利用Protel 99 SE 进行印刷电路板的设计,整个过程需要三个步骤。 电路原理图设计(Sch:利用Protel 99 SE的原理图设计系统,绘制完整的、正确的电路原理图。 产生网络表:网络表是表示电路原理图或印刷电路板中元件连接关系的文本文件。是连接电路原理图与印刷电路板图的桥梁。 印刷电路板设计(PCB:根据电路原理图,利用Protel 99 SE提供的强大的PCB设计功能,进行印刷电路板的设计。 3.1.2 电路原理图设计的一般步骤 电路原理图设计是整个电路设计的基础,它决定了后面工作的进展。电路原理图的设计过程一般可以按图3.1所示的设计流程进行。

图3.1 电路原理图设计流程 其中,开始:即启动Protel 99 SE原理图编辑器。 设置图纸大小:包括设置图纸尺寸,网格和光标的设置等。 加载元件库:在Protel 99 SE中,原理图中的元器件符号均存放在不同的原理图元件库中,在绘制电路原理图之前,必须将所需的原理图元件库装入原理图编辑器。 放置元器件:即将所需的元件符号从元件库中调入到原理图中。 调整元器件布局位置:调整各元器件的位置。 进行布线及调整:将各元器件用具有电气性能的导线连接起来,并进一步调整元器件的位置、元器件标注的位置及连线等。 最后存盘打印。 3.2 图纸设置

组合逻辑电路的设计 一.实验目的 1、加深理解组合逻辑电路的工作原理。 2、掌握组合逻辑电路的设计方法。 3、掌握组合逻辑电路的功能测试方法。 二.实验器材 实验室提供的芯片:74LS00与非门、74LS86异或门,74LS54与或非门,实验室提供的实验箱。 三.实验任务及要求 1、设计要求 (1)用与非门和与或非门或者异或门设计一个半加器。 (2)用与非门和与或非门或者异或门设计一个四位奇偶位判断电路。 2、实验内容 (1)测试所用芯片的逻辑功能。 (2)组装所设计的组合逻辑电路,并验证其功能是否正确。 三.实验原理及说明 1、简述组合逻辑电路的设计方法。 (1)分析实际情况是否能用逻辑变量来表示。 (2) 确定输入、输出逻辑变量并用逻辑变量字母表示,作出逻辑规定。 (3) 根据实际情况列出逻辑真值表。 (4) 根据逻辑真值表写出逻辑表达式并化简。 (5) 画出逻辑电路图,并标明使用的集成电路和相应的引脚。 (6) 根据逻辑电路图焊接电路,调试并进一步验证逻辑关系是否与实际情况相符。 2、写出实验电路的设计过程,并画出设计电路图。 (1)半加器的设计 如果不考虑有来自低位的进位将两个1位二进制数相加。 A、B是两个加数,S是相加的和,CO是向高位的进位。 逻辑表达式 S=A’B+A’B=A⊕B CO=AB (2)设计一个四位奇偶位判断电路。 当四位数中有奇数个1时输出结果为1;否则为0。 A, B, C, D 分别为校验器的四个输入端,Y时校验器的输出端

逻辑表达式 Y=AB’C’D’+A’BC’D’+A’B’C D’+A’B’C’D+A’BCD+AB’CD+ABC’D+ABCD’ =(A⊕B)⊕(C⊕D) 四.实验结果 1、列出所设计电路的MULTISM仿真分析结果。 (1)半加器的设计,1-A被加数,2-B加数,XMMI(和数S)XMM2(进位数CO) (2)设计一个四位奇偶位判断电路。

PCB电路板原理图的设计步骤 PCB从单层发展到双面、多层和挠性,并且仍旧保持着各自的发展趋势。由于不断地向高精度、高密度和高可靠性方向发展,不断缩小体积、减少成本、提高性能,使得印刷板在未来设备的发展工程中,仍然保持着强大的生命力。那 么PCB是如何设计的呢?看完以下七大步骤就懂啦! 1、前期准备 包括准备元件库和原理图。在进行PCB设计之前,首先要准备好原理图SCH 元件库和PCB元件封装库。PCB元件封装库最好是工程师根据所选器件的标准尺寸资料建立。原则上先建立PC的元件封装库,再建立原理图SCH元件库PCB元件封装库要求较高,它直接影响PCB的安装;原理图SCH元件库要求相对宽松,但要注意定义好管脚属性和与PCB元件封装库的对应关系。 2、PCB结构设计 根据已经确定的电路板尺寸和各项机械定位,在PCB设计环境下绘制PCB

板框,并按定位要求放置所需的接插件、按键/开关、螺丝孔、装配孔等等。充分考虑和确定布线区域和非布线区域(如螺丝孔周围多大范围属于非布线区域)。 3、PCB布局设计 布局设计即是在PCB板框内按照设计要求摆放器件。在原理图工具中生成网络表(Design→Create Netlist),之后在PCB软件中导入网络表(Design →Import Netlist)。网络表导入成功后会存在于软件后台,通过Placement操作可以将所有器件调出、各管脚之间有飞线提示连接,这时就可以对器件进行布局设计了。 PCB布局设计是PCB整个设计流程中的重要工序,越复杂的PCB板,布局的好坏越能直接影响到后期布线的实现难易程度。布局设计依靠电路板设计师的电路基础功底与设计经验丰富程度,对电路板设计师属于较高的要求。初级电路板设计师经验尚浅、适合小模块布局设计或整板难度较低的PCB布局设计任务。 4、PCB布线设计

中国石油大学现代远程教育 电工电子学课程实验报告 所属教学站:青岛直属学习中心 姓名:杜广志学号: 年级专业层次:网络16秋专升本学期: 实验时间:2016-11-05实验名称:组合逻辑电路的设计 小组合作:是○否●小组成员:杜广志 1、实验目的: 学习用门电路实现组合逻辑电路的设计和调试方法。 2、实验设备及材料: 仪器:实验箱 元件:74LS00 74LS10 3、实验原理: 1.概述 组合逻辑电路又称组合电路,组合电路的输出只决定于当时的外部输入情况,与电路过去状态无关。因此,组合电路的特点是无“记忆性”。在组成上组合电路的特点是由各种门电路连接而成,而且连接中没有反馈线存在。所以各种功能的门电路就是简单的组合逻辑电路。 组合逻辑电路的输入信号和输出信号往往不止一个,其功能描述方法通常有函数表达式、真值表、卡诺图和逻辑图等几种。 组合逻辑电路的分析与设计方法,是立足于小规模集成电路分析和设计的基本方法之一。 2.组合逻辑电路的分析方法 分析的任务是:对给定的电路求解其逻辑功能,即求出该电路的输出与输入之间的逻辑关系,通常是用逻辑式或真值表来描述,有时也加上必须的文字说明。 分析的步骤: (1)逐级写出逻辑表达式,最后得到输出逻辑变量与输入逻辑变量之间的逻辑函数式。 (2)化简。 (3)列出真值表。 (4)文字说明 上述四个步骤不是一成不变的。除第一步外,其它三步根据实际情况的要求而采用。 3.组合逻辑电路的设计方法 设计的任务是:由给定的功能要求,设计出相应的逻辑电路。 设计的步骤; (1)通过对给定问题的分析,获得真值表。 在分析中要特别注意实际问题如何抽象为几个输入变量和几个输出变量之间的逻辑关系问题,其输出变量之间是否存在约束关系,从而获得真值表或简化

实 验 报 告 实验日期: 学 号: 姓 名: 实验名称: 常用组合逻辑电路设计 总 分: 一、实验目的 学习常用组合逻辑电路的可中和代码编写,学习并熟悉VHDL 编程思想与调试方法,掌握LPM 元件实现逻辑设计,从而完成电路设计的仿真验证和硬件验证,记录结果。 二、实验原理 VHDL 设计采用层次化的设计方法,自上向下划分系统功能并逐层细化逻辑描述。层次关系中的没一个模块可以是VHDL 描述的实体,上层VHDL 代码中实例化出各个下层子模块。 利用VHDL 语言和LPM 元件设计这两种方法方法实现两个二位数大小比较的电路,根据A 数是否大于、小于、等于B 数,相应输出端F1、F2、F3为1,设A=A2A1,B=B2B1(A2A1、B2B1表示两位二进制数),当A2A1>B2B1时,F1为1;A2A1 port(a2,a1:in STD_LOGIC; b2,b1:in STD_LOGIC; f1,f2:buffer STD_LOGIC; f3:out STD_LOGIC); end bijiao; architecture bijiao_arch of bijiao is begin f1<=(a2 and(not b2))or(a1 and (not b1)and a2)or(a1 and (not b1)and(not b2)); f2<=((not a2)and b2)or((not a2)and(not a1)and b1)or((not a1)and b1 and b2); f3<=not(f1 or f2); end bijiao_arch; (2)波形仿真 网格大小 100ns 结束时间 2μs 功能仿真:时序仿真:输入信号00, 01,10,11 输入信号00, 01,10,11 输出信号001, 010,100 信号均为二 进制表达 输入信号00, 01,10,11 5)建立和编辑顶层原理图文件 对于顶层文件,即可使用VHDL文本输入方式,也可使用原理图输入方式。这里我们将使用原理图的输入方式来建立顶层文件。 (1)原理图形符号的生成(Symbol) 为了在原理图的设计中利用前面已使用VHDL进行有关设计的成果,我们先要将经过编译后的VHDL程序生成可供原理图设计中直接调用的原理图形符号。 选择 count_t.vhd,执行Create Schematic Symbol操作(如图4.47 所示),即可生成可供原理图设计中直接调用的原理图形符号count_t。同理,对其他两个文件执行相同的操作。 图4.47 原理图形符号的创建操作 (2)顶层原理图文件的创建 选中工程,鼠标右点,在弹出的窗口中选择New Source(如图4.48所示),再在弹出的窗口中选择文件的类型为Schematic,并输入文件名pic_top后,执行”下一步”,即完成了原理图文件的创建,进入原理图的编辑状态。 图4.48 原理图的创建操作 (3)原理图的编辑 ① 放置元件(Symbols):在Symbols 的e:/xilinx/bin/24sec中选中所需元件的原理图符号,并在右边的图中期望的位置点左键进行放置,如图4.49所示。若位置不合适,可进行移动调整。 图4.49 在原理图中放置元件的操作 ② 元件间的连线:点,进行连线操作。 ③ 放置I/O端口并编辑端口名:点,放置I/O端口。选中端口,点右键, 在弹出的对话框中选择“Rename Port”后,再在弹出的对话框中输入系统设定的端口名。或者双击端口,在弹出的对话框中输入系统设定的端口名。 ④ 原理图的保存:原理图编辑好后(如图4.50所示),应执行存盘操作,将原理图进行保存。 PCB从单层发展到双面、多层和挠性,并且仍旧保持着各自的发展趋势。由于不断地向高精度、高密度和高可靠性方向发展,不断缩小体积、减少成本、提高性能,使得印刷板在未来设备的发展工程中,仍然保持着强大的生命力。那么PCB是如何设计的呢?看完以下七大步骤就懂啦! 1、前期准备 包括准备元件库和原理图。在进行PCB设计之前,首先要准备好原理图SCH 元件库和PCB元件封装库。PCB元件封装库最好是工程师根据所选器件的标准尺寸资料建立。原则上先建立PC的元件封装库,再建立原理图SCH元件库PCB元件封装库要求较高,它直接影响PCB的安装;原理图SCH元件库要求相对宽松,但要注意定义好管脚属性和与PCB元件封装库的对应关系。 2、PCB结构设计 根据已经确定的电路板尺寸和各项机械定位,在PCB设计环境下绘制PCB 板框,并按定位要求放置所需的接插件、按键/开关、螺丝孔、装配孔等等。充分考虑和确定布线区域和非布线区域(如螺丝孔周围多大范围属于非布线区域)。 3、PCB布局设计 布局设计即是在PCB板框内按照设计要求摆放器件。在原理图工具中生成 网络表(Design→Create Netlist),之后在PCB软件中导入网络表(Design →Import Netlist)。网络表导入成功后会存在于软件后台,通过Placement操作可以将所有器件调出、各管脚之间有飞线提示连接,这时就可以对器件进行布局设计了。 PCB布局设计是PCB整个设计流程中的重要工序,越复杂的PCB板,布局的好坏越能直接影响到后期布线的实现难易程度。布局设计依靠电路板设计师的电路基础功底与设计经验丰富程度,对电路板设计师属于较高的要求。初级电路板设计师经验尚浅、适合小模块布局设计或整板难度较低的PCB布局设计任务。 4、PCB布线设计 PCB布线设计是整个PCB设计中工作量大的工序,直接影响着PCB板的性能好坏。在PCB的设计过程中,布线一般有三种境界:首先是布通,这是PCB 设计的基本的入门要求;其次是电气性能的满足,这是衡量一块PCB板是否合格的标准,在线路布通之后,认真调整布线、使其能达到好的电气性能;再次是整齐美观,杂乱无章的布线、即使电气性能过关也会给后期改板优化及测试与维修带来极大不便,布线要求整齐划一,不能纵横交错毫无章法。 原理图设计: 1、信号线束:把单条走线和总线汇集在一起进行连接,可在一个原理图中使用,也可以通 过输入/输出端口,与另外的原理图之间建立连接。 2、电气节点:在导线的T形交叉点处自动放置电气节点,表示所画线路在电气意义上是连 接的。但在十字交叉点处,系统无法判断导线是否连接,不会自动放置电气 节点。如果导线确实是相互连接的,就需要手动放置电气节点。P+J 3、特色工作面板 (1)SCH Inspector(检查器)面板:用于实时显示在原理图中所选取对象的属性;可同时编辑多个被选对象的属性。亦可用①用SCH Filter选中所需对象;②用SCH List对对象进行参数更改。来实现 (2)SCH Filter(过滤器)面板:查找多个具有相同或相似属性的对象,进而对其进行编辑或修改; (3)SCH List(列表)面板:进行过滤查找后,查找的结果除了在编辑窗口内直接显示出来以外,用户还可以使用SCH List面板对查找结果进行系统的浏览,并且可 以对有关对象的属性直接编辑修改。 (4)选择内存面板:把当前原理图文件或所有打开的原理图文件中的选取对象存入某一内部存储器中,需要时直接调用;还可以随时把新的选取对象加入内部存储器 中或者清除不在需要的对象等。 ①存储:Shift+1或者STO1按钮;②浏览:apply;③调用:RCL1按钮。 4、联合与片段: (1)联合及打碎器件:选中对象+右键unions。联合后的对象可以作为单个对象在窗口内进行移动、排列等编辑操作或者删除。 (2)片段:片段的生成与联合的生成过程基本相同。所不同的是,片段可以长久保存,并且能够使用系统提供的片段面板进行查看、管理。System-snippets PCB设计: 1、多层板的埋孔、过孔和盲孔(作用:连接所设计的电子线路,电气检查也不会报错) 导通孔:一种用于内层连接的金属化孔,并不用于插入元件引线或其他增强材料; 过孔:至少连通顶层和底层之间的电气连接通孔,过孔在顶层和底层上没有实际的电气连接;埋孔:一端连接在顶层或底层,另一端连接在中间层的电气连接半开孔;(一面没有空间允许设置过孔焊盘,另外在高速电路设计时设置埋孔还可以减小过孔焊盘的寄生电容、寄生电感对电子线路的影响) 盲孔:在两层中间层之间进行电气连接的金属化孔;(可以增加其他层面的走线空间,在高速电路设计中盲孔有利于电子线路电气性能的提高) 元件孔:用于将插针式元器件固定在印刷版上并进行电气连接的孔。 注:使用盲孔、埋孔一是因为对印刷电路板尺寸有要求,布线密度高,布线空间不够;二是在高速电路设计中,使用埋孔、盲孔能有效减小线路信号辐射,从而减小布线给高频小信号带来的电气干扰,但是在多层设计中大规模使用盲孔和埋孔会增加印刷版的制造成本。使用过孔对不同板层间的电子线路进行电气连接,能有效地减小印刷电路板的制造成本,也有利于提高印刷电路板的成品率。 2、印刷电路板常用术语 封装:插针式、表贴式; 过孔:被沉积上一层金属导电膜的小孔,用来连接不同层之间的铜膜导线,以建立电气连接。 2015年全省技工教育和职业培训 参评教案参评组别:B组 专业分类:电工电子 课程名称:电子技术基础 组合逻辑电路的设计 作者姓名:徐崇丽 单位:山东工程技师学院 通讯地址:_聊城市湖南西路8号 联系电话:0635-8426630 科目电子技术基础 授课 日期 2015.4.25 课 时 2 章节名称7-4 组合逻辑电路的设计班级鲁化电工班1401 授 课方式讲授法、启发法、练习法、演示法 作业 题数 1 作 业 拟 用 时 间 30 分钟 教学目的只有一堂让自己感动的课,才能感染你的学生 认知目标 掌握组合逻辑电路的设计步骤 能力目标 能够根据控制要求进行组合电路的设计 选 用 教 具 挂 图 1、投影仪 2、电子课件 3、教学电脑 4、黑板 重点 1、组合逻辑电路的设计步骤; 2、逻辑表达式的化简; 3、由最简表达式绘制组合逻辑电路 图 难 点 1、将控制要求转换成真值表 2、卡诺图化简表达式 教 学 回 顾 组合逻辑电路的分析步骤 说明 学生在学习了《组合逻辑电路的分析》基础上,对逻辑代数的化简、真值表、逻辑门电路等步骤都有了相应程度的理解,鉴于学生在以上环节反映出的问题,在新的课程讲解中将再次强调,借助练习帮助学生更好地掌握。 教学过程 时间分配教学内容 教学 过程 教学 方法 任务目标︵2分钟︶ 任务目标:三人表决器设计 课题引入:有一场卡拉OK比赛,学校请了三个评委,如果你是电 子设计师,怎么设计一个电路能够根据“少数服从多数”的原则让评委 对选手进行评判呢? 情境 导入 引起 注意 鼓 励 法 知识准备(约5分钟) 【例】试分析下列电路的逻辑功能。(板书步骤) 一、电路 二、表达式,化简得最简表达式 由图,可得ABC P=,P C P B P A L? + ? + ? = 化简,得C B B A L⊕ + ⊕ = 三、真值表 四、功能 “不一致”电路。 积极思考:功能电路 A B C L A B C L 0 0 0 0 1 0 0 1 0 0 1 1 1 0 1 1 0 1 0 1 1 1 0 1 0 1 1 1 1 1 1 0 老师 引导 学生 讨论 多媒 体演 示 板书 结果 讨 论 法 演 示 法 归 纳 法 & & & & ≥1 A B C L P 实验一原理图输入方式设计数字逻辑电路 一、实验目的: 1、了解基本组合逻辑电路的原理及利用Quartus II 软件进行设计的一般方法。 2、熟悉Quartus II 原理图输入法的设计流程,掌握编辑、编译和仿真的方法。 3、掌握原理图的层次化设计方法。 4、了解Quartus II 软件的编程下载及引脚锁定的方法。 5、了解Quartus II宏功能模块的使用方法。 二、实验的硬件要求: 1、EDA/SOPC实验箱。 2、计算机。 三、实验原理 见附件《Quartus设计的一般步骤》、《元件例化和调用的操作步骤》、《QuartusII基于宏功能模块的设计》 四、实验内容: 1、用原理图方式设计1位二进制半加器半加器。 新建一个工程“HalfAdder”,选择芯片“Cyclone III EP3C16Q240C8”,建立原理图如图1-1,保存为“HalfAdder.BDF”。 图1-1 半加器电路图 编译工程。 建立波形文件,对半加器电路分别进行时序仿真和功能仿真,其波形如下: 图1-2半加器时序仿真波形,注意观察输出延时,以及毛刺的产生原因 图1-3半加器功能仿真波形 2、原理图层次化设计。 新建一工程,取名“FullAdder”;将上面设计的半加器“HalfAdder.BDF”复制到当前工程目录,并生成“符号元件”HalfAdder.BSF。 建立一个原理图文件,取名“FullAdder.BDF”,利用“符号元件”HalfAdder.BSF及其它元件设计全加器电路如下图: 图1-4 全加器电路图 用功能仿真测试全加器的逻辑功能。 图1-5 全加器功能仿真波形 图1-6是输入输出信号与FPGA连接示意图,图中用到了“拨档开关”作为输入,“LED 显示模块”显示输出值。表1-1是本实验连接的FPGA管脚编号。 第三章组合逻辑电路的分析和设计 [教学要求] 1.掌握逻辑代数的三种基本运算、三项基本定理、基本公式和常用公式; 2.掌握逻辑函数的公式化简法和卡诺图化简法; 3.了解最小项、最大项、约束项的概念及其在逻辑函数化简中的使用。 4.掌握组合逻辑电路的分析和设计方法; 5.了解组合电路中的竞争和冒险现象、产生原因及消除方法。 [教学内容] 1.逻辑代数的三种基本运算、三项基本定理、基本公式和常用公式 2.逻辑函数的公式化简法和卡诺图化简法 3.最小项、最大项、约束项的概念及其在逻辑函数化简中的使用 4.组合逻辑电路的分析方法 5.组合逻辑电路的设计方法 6.组合电路中的竞争和冒险现象、产生原因及消除方法 组合逻辑电路――在任何时刻,输出状态只决定于同一时刻各输入状态的组合,而和先前状态无关的逻辑电路。 组合逻辑电路具有如下特点: (1)输出、输入之间没有反馈延迟通路; (2)电路中不含记忆单元。 3.1 逻辑代数 逻辑代数是分析和设计逻辑电路不可缺少的数学工具。逻辑代数提供了一种方法,即使用二值函数进行逻辑运算。逻辑代数有一系列的定律和规则,用它们对数学表达式进行处理,可以完成对电路的化简、变换、分析和设计。 一、逻辑代数的基本定律和恒等式 常用逻辑代数定律和恒等式表:P90 加乘非 基本定律 结合律 交换律 分配律 反演律(摩根定律) 吸收律 其他常用恒等式 表中的基本定律是根据逻辑加、乘、非三种基本运算法则,推导出的逻辑运算的一些基本定律。对于表中所列的定律的证明,最有效的方法就是检验等式左边的函数和右边函数的真值表是否吻合。 证明: 证明如下: 二、逻辑代数的基本规则 实验4.9 组合逻辑电路的设计 一、实验目的 1.掌握组合逻辑电路的设计方法与测试方法 2.了解组合逻辑电路的竞争冒险现象 二、实验仪器与器材 1.集成与非门若干块 2.数字实验箱一台 三、实验原理 组合逻辑电路的设计是给定一定的逻辑功能,要求用门电路实现这一逻辑功能。用小规模集成电路(SSI)进行组合逻辑电路设计的一般步骤是: (1)根据实际问题对逻辑功能的要求,定义输入输出逻辑变量,列出真值表。(2)通过化简和变换得到符合要求(一般为与非关系)的最简逻辑表达式。(3)根据最简的逻辑表达式画出逻辑图,实现逻辑功能。 组合逻辑电路设计的关键之一,是对输入逻辑变量和输出逻辑变量作出合理的定义,在定义时,应注意以下几点: (1)有具有二值性的命题才能定义成输入或输出逻辑变量。 (2)把逻辑变量取1值的定义表达清楚。 组合逻辑电路的设计都是在理想的情况下进行的,即假定一切逻辑器件都没有延迟效应。但事实并非如此,信号通过任何导线和器件都存在一个响应时间。由于工艺上的原因,各器件的延迟时间离散型非常大,往往按照理想情况下设计的逻辑电路,在实际工作中有可能会产生错误输出。一个组合逻辑电路,在它的输入信号变化时,输出出现瞬时错误的现象称为组合逻辑电路的冒险现象。冒险现象直接影响数字设备的可靠性和稳定性,故要设法消除。 四、实验内容 1.设计一个交通灯报警电路。在三个输入变量中,当两个或两个以上输入端为 “1”时,属不正常状态,应该发出报警。 (1)逻辑抽象 输入变量为A、B、C三个交通灯,灯亮时认为是“1”,灯灭时为“0”。输出变量为Y,正常时,输出为“0”,灯不亮铃不响;出现故障时,输出为“1”,灯亮铃响。ISE原理图输入方法

pcb电路板原理图的设计步骤

原理图及PCB板设计基础

组合逻辑电路的设计教案

(完整版)实验一原理图输入方式设计数字逻辑电路

组合逻辑电路的分析与设计

组合逻辑电路的设计.