4

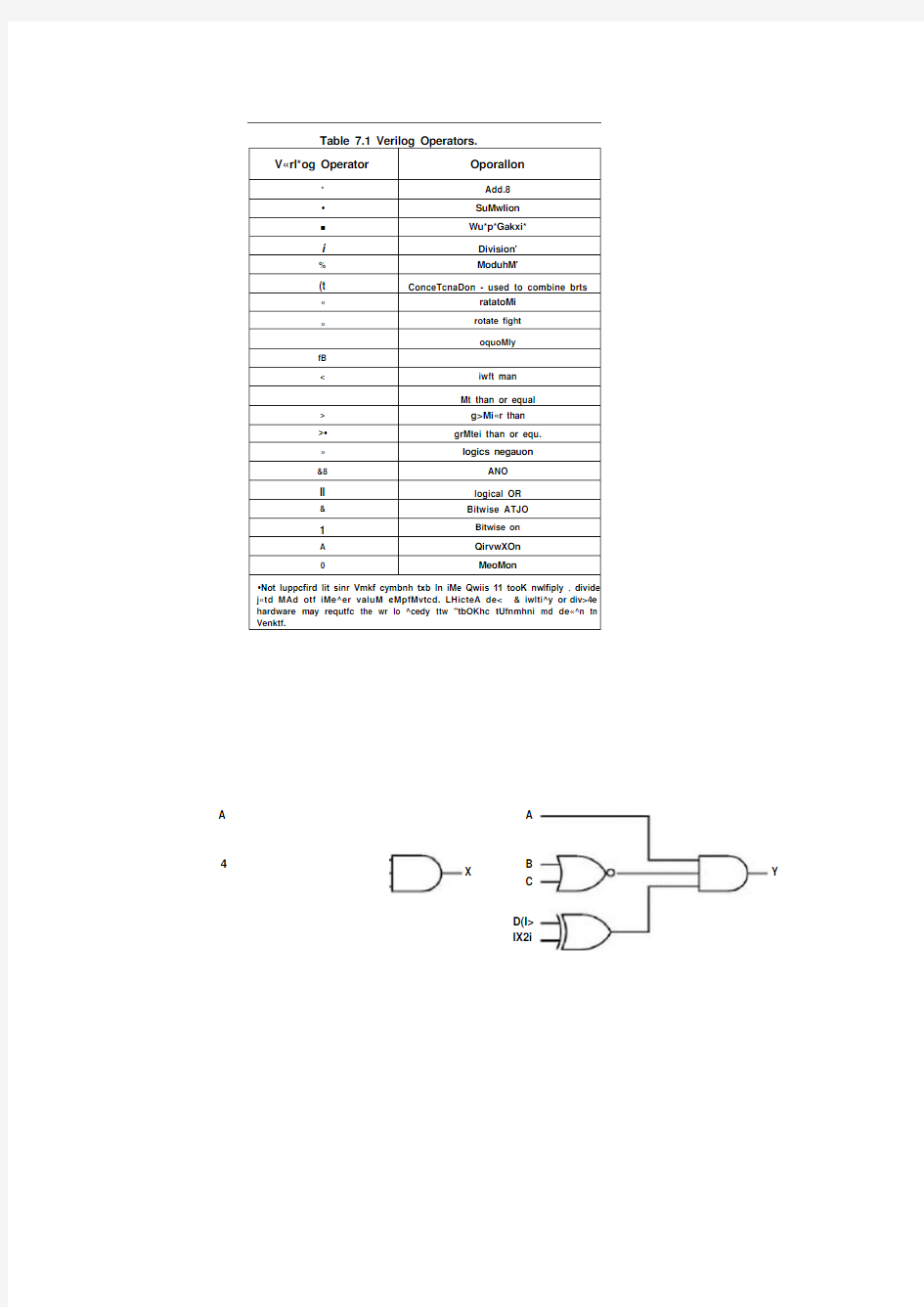

Table 7.1 Verilog Operators.

V?rl*og Operator Oporallon

* Add.8

?SuMwIion

■Wu*p*Gakxi*

i Division'

% ModuhM'

(t ConceTcnaDon - used to combine brts

?ratatoMi

?rotate fight

oquoMly

fB

< iwft man

Mt than or equal

> g>Mi?r than

>?grMtei than or equ.

?logics negauon

&8 ANO

II logical OR

& Bitwise ATJO

1 Bitwise on

A QirvwXOn

0 MeoMon

?Not luppcfird lit sinr Vmkf cymbnh txb In iMe Qwiis 11 tooK nwlfiply . divide j?td MAd otf iMe^er valuM ?cMpfMvtcd. LHicteA de<

4e hardware may requtfc the wr lo ^cedy ttw "tbOKhc tUfnmhni md de?^n tn Venktf.

A A

X

B

C

D(l>

IX2i

Y

module galenetwork(A, B, C. D, X. Y);

input A;

Input B;

Input C;

input [2:1] D:

output X, Y;

reg Y;

// concurrent assignment statement

wire X = A & ~(B|C) & {D[1]入 D(2]);

/*-4/ivays concurrent statement- sequentiaf execution inside 7 always @( A or B or C or D)

Y = A & ~(B|C) & (D[1] A D⑵);

endmodule

module DEC_7SEG(Hox_digjt. segmont^a. tegment^b, 8ogmenl_c* aoQmonl_d. Mgmenl_o.

sogmont t Mgmonl_g);Input [3:0] Hexjchflil:

output segmenF a. segmenVb, segfnent_c, segment _d:output segmented, segmonlj,

&egm9nt_g;

reg (6:0] segmenedata:

always(lP(Hex_digil)

* Case ararMwir ■ logic truth taae “Mg gstesy

case (Hex digit)

41>

OOOO:

4-bOOOI:

4'b 0010:

4'b00l1:

4 b 0100:

4 b 0101:

4'b0110:

4b0111:

4'b 1000:

4 b 1001:

4 b 1010:

4 b 1011;

4 b 1100:

4 b 1101:

4 b 1110:

rbilll:

default: endcase fidgrnent_data s 7*b 1111110;

sogment_data s 7b 0110000;

9egmen(_da(a s 7*b

1101101:segment data ?

7'b 1111001; segment data =

7*b0l10011; segmentdata =

7T> 1011011; aegment_data s

71)1011111; segmenT^dala s

Tb1110000; 8?gmen(_dala *

7*b 1111111; segment data =

Z'b 1111011; segment data =

71> 1110111; segment^data =

7^0011111; $egment_data ?

7'b 1001110; aegmont_data s

7b0111101; segmont_data ■

Tb 1001111; segment data z Tb

1000111; segment^data = Tb

Fl

? Muttrpfexcr cxampto shows three ways to model a 2 to 1 mux ?/ module multiplexer(A, B,

mux_conlroh mux_out1, mux_cxjt2? mux_out3); input A; 广 Input Signals and Mux Control ?/ Input B; Input mux_conlrol : cxjtput mux_oul1 .fnux_OLrt2, mux_out3; reg mux_out2, mux^outS :

/? CondfbafKl Continuous Assignment Statement ■/ wire mux_oull ■ (mux_control)?

B:A;

? // statement inside Btways statement ?/ always

歎 A or 6 or mux_control)

If (mux_conlrol) mux_out2 = 8;

else

mux_out2 s A;

/? Case statement instde always statement ?; always (2>(A or 8 or mux_control)

case (mux_control) 0; mux_oul3 s A : 1: mux_out3 s B : default; mux_out3 ? A; endcaoe

endmodule

module instate (a. control. lri_out); Input a, control; output trLout : reg tri_out;

always ^(control or a)

If (control)

;? Assignment of Z value generates a tri -state output V IrLout = rbZ; else

lri_out = a;

endmodule

C OBK OI

module ilatch( A, B, Output 1, Ou(pul2); Input A. B; output Output] - Output2; reg Outputl. Output2;

?lw ?y ?@( A or B) if(IA) begin

OutpuU ■ 0; Outpul2 = 0; erxl else

H(B) begin Outputl s 1; Outputs = 1;

end else /"latch inferred since no ^atue */

Outputl = 0; /■IS assigned to Output2here */

endmodule

module DFFs(D. clock, reset enable. Q1,Q2, Q3? 04); Input D; Input dock; Input reset; Input ?nable; oulpul Q1, Q2? Q3? 04; reg Qt 02.03, 04:

always 歌posedge clock) O1

sD;

广 Posrfjve &dffe tnggewt D fbpJtop V

/- PosfbvQ edge tnggemd D fiip-tlop V /*

Wfth synchmfwus reset V

atway* gposedge clock)

If (reset)

02 = 0;

elflo

Q2 = 0;

,? PosrftvG edge tngfferwt D fUpHop '/

/? With asynchronous res&t 7 always ^posedge clock or posedge reset)

1( (reset)

Q3s0:

e<*e

03 sO :

/? Posrfivtf edge tnggemct D fUp tfop ?/

h wrih asynchronous reset Jind enabis V

always 叙pcsedge clock or posedoe reset)

It (reset)

04 = 0;

else If (enable)

04 sO ;

endmodule

—oi

::

Q MK

R0??

ciH h ftO Ml

(-※

N J

module counter(clock, reset, max_count, count); input clock;

input reset : input [7:0] max_count; output [7:0] count; reg [7:0] count;

八 use positive dock edge for counter 7 always @(posedge clocK or posedge reset) begin if (reset)

8unt = 0;

else if (count <

max_count) count 2

count + 1;

else count = 0;

end

en dmodule

Res

et

Figure 7.1 Stale Diagram for sl_mach exam pie

厂 Reset Counter 7 /* Chech for maximum count 7 /* Increment Counter */ /* Counter set bach to 0 V

module state_mach (elk, reset, inputl, input2 ,output"; input elk, reset, input1, input?;

output output 1;

reg output 1;

reg [1:0] state;

? MaKe State Assigmenrs 7 parameter [1:0] state_A = 0, state_B = 1, slate_C = 2; always@(posedge clK or posedge reset) begin

if (reset)

state = state_A;

else

/* Define Next State Transitions using a Case7 "Statement based

on the Current State V case (state) state_A:

if (input1==0) state s sta1e_B:

else

state = state_C;

state_B: state = slate_C;

state_C: If (inptit2) state = state_A; default: state = state_A:

endcase

end

广Define State Machine Outputs ?/ always @(sta 怡)

begin

case (state) state_A: outputl s 0; slate_B: outputl = 1; state_C: outputl = 0; default: outputl =0;

endcase

end

endmodule

module ALU ( ALU_control, Ainput. Binput, ClocR, Shift output); input [2:0] ALU_control;

input [15X>] Ain put; input [15:0] Binput;

input Clock; outp Shift__output:reg ”5:0)ALU_ ?Seiect ALU Arithmebc/Logicat Operation V always (SKALU control or Ainput or Binput) case (ALU_controH2:11> 0: ALU_ouIput = Ainput ■ Binpul; 1: ALU_output s Ainput - Bmput; 2: ALU…output s Ainput & Binput; 3; ALU_output s Ainput | Binput; default; ALU_output = 0; endcase * Shift bits left using shift iefl operator if reguifed snd /oad register V always @(posedgo Clock) If (ALU_conlrol(0]==1) Shift^output s ALU^output?1; else Shlfl_oulpUt ■ ALU_OUtpul; endmodute module mult (dataa, datab, result); input [7:0] dataa; Input [7:0] datat);output [15:0] result; wire [15:0] sub_wtre0; wire [15:0] result = sub_wire0[15:0]; /* Altera LPM 8x8 multiply function result = dataa * datab V lpm_muhlpm_mult_component ( .dataa (dataa), .datab (datab), .result (sub_wire0)); defp aram lpm_mult_componeniJpm_widtha ? 8. Ipm_mult_component. Ipm_widthb = & ipm_mult_comp onent.lpm _widthp = 16, lprTi_mult_componentJpm_widths = 1. lpm_mult_conriponenlJpm_type ?tPM_MULT\ lpm_mult_c ompon enlJpm_re presentation = "UNSIGNED;endmodule 烘焙理论知识 第一部分原辅料基本知识 一、制作面包、糕点、蛋糕应选择什么技术指标的小麦面粉? 答: 1.面包:应选择面包专用粉,即蛋白质含量在11.5~13.5%,湿面筋≥33%,灰分≤0.6%,粉质曲线稳定时间≥10.0min的高筋粉。 2.糕点、蛋糕:应选择糕点、蛋糕专用粉,即蛋白质含量在7~9%,湿面筋≤24%,灰分≤0.55%,粉质曲线稳定时间≤2.0min的低筋粉。 二、面粉、酵母、水、盐、糖、蛋、乳粉和乳化剂在面包、中点、西点产品中各起什么作用?答: 1.面粉:构成产品的“骨架”或“框架”,是保持产品形状结构的基本原料。 2.油脂: (1)增加营养、增进风味 (2)增强面坯可塑性,有利成型 (3)调节面筋胀润度,降低筋力 (4)保持产品柔软,延长保存期 (5)使产品酥松、酥脆。 (6)可充气发泡,使产品体积膨大。 3.糖: (1)增加营养,提供热量,也是面包和发酵类糕点中酵母生长的营养素。 (2)改善面包和烘烤类、油炸类糕点的色泽和外观。 (3)改善口味,增加产品的甜度。 (4)是产品的风味剂。 (5)是产品的保鲜剂、防腐剂。 (6)是糕点面团降筋剂。 (7)是糕点的定形剂。 4.蛋: (1)是蛋糕起泡剂。 (2)是面团增筋剂。 (3)是产品的保鲜剂。 (4)改善制品的色泽。 (5)增加制品的香气。 (6)增加制品的营养价值。 5.乳粉: (1)增加制品的营养价值。 (2)改善制品的色泽。 (3)是面团增筋剂。 (4)是产品保鲜剂。 (5)是产品质量改善剂。 (6)调控面团发酵速度。 (7)提高面团吸水率。 6.水: (1)使面粉蛋白质吸水形成面筋“骨架”,使淀粉吸水糊化,溶解各种原辅料,形成均质的面团。 (2)调控面团软硬度。 (3)调控面团温度。 (4)延长面包产品保鲜期。 7.乳化剂: (1)使各种物料乳化、混合、均质。 (2)提高面团筋力,增大面包体积。 (3)是产品的保鲜剂。 (4)是蛋糕的起泡剂。 8.酵母:是面包体积膨大,组织疏松柔软的生物膨松剂或发酵剂。 9.盐: (1)调控面团发酵速度。 (2)改善产品风味。 (3)增强面团筋力。 (4)改善面包内部色泽,提高白度。 三、化学膨松剂主要用于哪几类烘烤食品?起什么作用?有哪几种产品?最常用的产品有哪些?这些膨松剂各有什么优缺点,各适用于哪些烘烤食品? 1.化学膨松剂主要用于糕点、蛋糕、饼干类产品。 2.化学膨松剂主要起到使糕点、蛋糕、饼干体积膨胀、组织疏松、改善口感等作用3.化学膨松剂有复合膨松剂(泡打粉)、碳酸氢钠(小苏打)、碳酸氢铵(大起子、臭碱、臭起子)。 4.最常用的化学膨松剂是复合膨松剂(泡打粉)。 5.化学膨松剂的优缺点: (1)复合膨松剂:膨胀能力较小,膨胀速度较慢,使产品水平膨胀(即横胀),使产品内部组织均匀、细腻,适用于各种饼类糕点、蛋糕、饼干等。 缺点:使用量过多,会使产品表面产生过多黑色斑点。 (2)小苏打:基本上与复合膨松剂相同。 缺点:但不适用于重油类糕点,会产生皂化反应,使产品产生令人讨厌的“皂味”。 (3)碳酸氢铵:膨胀能力大,膨胀速度快,使产品纵向膨胀(即竖胀、拔高),使产品体积大,内部组织更加疏松。 缺点:不适宜单独使用,产品内部组织不均匀、粗糙、大气孔多;不适用于含水量高的产品,会使产品产生强烈刺激的“氨味”,象“尿素”味一样。 四、影响酵母生长活性的因素有哪些? 答: 1.面团温度:适宜温度在27~32℃之间,最适温度27~29℃。温度太低,酵母活性不旺盛,甚至活性停止,面团不能正常发酵;温度太高,酵母活性过旺,面团发酵速度过快,面团提前完成发酵,造成发酵不足;同时,酵母衰老也过快,易产生杂菌。 2.面团酸碱度(pH值):酵母适宜在酸性条件下生长,最适pH值为5~6之间;不适宜在碱性条件下生长;pH<4或pH>8,酵母活性均大大降低。 XFP模块电路设计 一、应用要求 1、多速率应用:TELECOM(SONET OC-192 and G.709 “OTU-2”) DATACOM(10 Gb/s Ethernet and 10 Gb/s Fibre Channel) 2、XFI(9.95Gb/s~11.7Gb/s)高速信号可以在改良的FR4电路板上传输 300mm或普通的FR4电路板上传输200mm。 3、热插拔智能化,能够提供模块的实时工作状态的监视值 二、指标要求 3、封装结构:按照XFP-MSA的要求 三、方案选择 1、发射器件的选择:采用公司成熟的TO封装工艺开发的发射器件。 2、接收组件的选择:采用公司成熟的TO封装工艺开发的接收组件。 四、电路设计 1、原理框图 LOS Data In TxDis SCL SDA TxFault 2、原理图设计 3、PCB设计 (1)传输线设计: 在PCB设计中采用微带线来进行信号传输,保证高深信号在PCB上传输不发生波形畸变,我们通过AppCAD模拟可得到微带线的宽度和各微带线之间的间距。在10Gb/s的工作速率下,信号波长已经可以与器件尺寸相比拟,基于电路性能、器件选择和电磁兼容等因素的考虑,必须以网络散射分析(S参数)、信号完整性分析、电磁仿真分析、电路仿真分析等手段,来综合考量实际电路系统的工作性能。对电路板、元器件进行结构性电磁仿真并精确提取相应的SPICE电路模型参数,作为电路设计的依据,以此有效减小电感器件在高频设计应用中的误差影响。而且现在国外的产品技术参数大多包含有S参数,通常可用于精确的高频应用分析。信号传输微带线的等效分析见下图。 计算机基础知识概述 一、概述 1.计算机的发展 (1)1946年,美国宾夕法尼亚大学成功研制了世界上第一台电子数学积分计算机。(计算机简称:ENIAC) (2)ENIAC的特点 a.采用二进制 b.储存程序控制 2.计算机的特点、用途和分类 (1)特点 a.高速、精确的运算能力 b.准确的逻辑判断能力 c.强大的存储能力 d.自动功能 e.网络与通讯功能 (2)用途 a.科学计算 b.信息处理 c.过程控制 d.辅助功能 e.网络通信 f.人工智能 g.多媒体应用 h.嵌入式系统 (3)分类 a.按处理数据的类型分类 数字计算机、模拟计算机、数字和模拟计算机(混合计算机) b.按用途分类 专用计算机、通用计算机 c.按性能、规模和处理能力分类 巨型机、大型计算机、微型计算机、工作站和服务器 二、信息的表示和储存 1.计算机中的单位及换算 (1)单位 位(bit)是计算机中数据的最小单位,代码只有0和1,采用多个数码表示一个数,其中每一个数码称为1位。 字节(Byte)是存储容量的基本单位,一个字节由8位二进制位组成。 1KB=1024B=210B 1MB=1024KB=220B 1GB=1024MB=230B 1TB=1024GB=240B 2.进位计数制及其转换(见笔记) 3.字符的编码 (1)字符包括西文字符和中文字符。ASCII码是常用的字符编码,被指定为国际标准。国际通用ASCII码是7位,即用7位二进制数来表示一个字符的编码,共有27=128个不同的编码值。 (2)特殊字符的编码 a字符的编码为1100001,十进制为97;b为98 A字符的编码为1000001,十进制为65;B为66 0字符的编码为0110000,十进制为48;1为49 空格(SP)编码为0100000 回车(CR)编码为0001101 删除(DEL)编码为1111111 退格(BS)编码为0001000 小写比大写字母的码值大32 计算机内一个字节存放一个7位ASCII码,最高位置为0 (3)汉字输入码分类 音码、音形码、形码数字码 三、计算机硬件系统 1.组成 a.运算器(加法器+寄存器+累加器) b.控制器(指令寄存器+指令译码器+操作控制器+程序计数器) c.存储器 烘焙基本知识培训 第一部分:面粉基本知识 一、面粉的组成: 1、面粉由碳水化合物.蛋白质.脂肪.矿物质和水等组成. (1)、碳水化合物:碳水化合物即糖类,是面粉中含量最高的化学成分,约占面粉重的75%,其中绝大部分以淀粉的形式存在的。 (2)、蛋白质:面粉中的蛋白质主要由麦胶蛋白、麦谷蛋白、麦清蛋白和麦球蛋白等组成,麦胶蛋白和麦谷蛋白是形成面筋的主要成分。 2、面粉根据蛋白质(含量)不同可分为低筋、中筋、高筋面粉。 二.面粉的工艺性能 (一)、面筋的工艺性能 1、面粉的筋力和面筋的工艺性能 面粉的筋力好坏.强弱决定于面粉面筋质的数量和质量.面筋质主要是由麦胶蛋白和麦谷 蛋白两种蛋白质组成. 2、面筋的工艺性能 评定面筋质量和工艺性能的指标有延伸性.可塑性.弹性.韧性和比延伸性.不同烘焙食品对面筋的工艺性能的要求也不同:制作面包要求弹性和延伸性都好的面粉,制作糕 点.饼干则要求弹性.韧性.延伸性都不高,但可塑性良好的面粉. (二)面粉蛋白质数量和质量 面粉的烘焙品质是由蛋白质的数量和质量两个方面来决定的. (三)面粉的吸水率 面粉吸水率是检验面粉烘焙品质的重要指标.面粉吸水率高,可以提高面包的出品率,而且面包中水份增加,面包心就比较柔软,保存时间也相应延长.因此,面包厂不但要选择吸水率较高的面粉,而且要求面粉的吸水率最好保持在恒定的水平,以利于正常生产. (四)面包面粉的选择 1、面粉的筋力 面粉中的面筋形成网状结构,构成面包的"骨架".面粉筋力不足,影响面包的组织和形状.因此,面粉要有足够数量的蛋白质和优质的面筋. 2、面粉白度 面粉颜色影响面包的颜色.愈靠近麦粒中心部位磨制的面粉颜色愈白,品质愈好。 3、发酵耐力 即面团超过预定的发酵时间还能生产良好质量的面包。面粉发酵耐力强,对生产中各种特殊情况适应性就强,有利于保持面包质量。 4、吸水率 面粉吸水率高低不仅影响到面包质量,而且直接关系到经济效益。吸水率高,出品率亦高。能降低产品成本,有利于产品贮存和保鲜。 (五)面粉的熟化(亦称后熟。陈化) 新磨制面粉的特点:新面粉搅拌成面团后,面团非常粘,不宜操作,而且筋力很弱,生产出来的面包体积小,弹性,疏松性差,内部组织粗糙,表皮色泽暗,无光泽。特别是面包在烘焙期间和出炉后,极容易塌陷和收缩变形而变成废品。面粉熟化后即可改善这种现象。 面粉自然熟化时间一般在1个月左右。 通常采用化学方法加速新粉熟化,在面粉中添加面团改良剂溴酸钾。维C等,在一周内即可使用。 三、面团流变学特性 (一)、粉质曲线 1、吸水率 2、面团形成时间 3、稳定时间 面团的稳定时间越长,韧性越好,面筋的强度越大,面团加工性质好。 4.弱化度 弱化度表明面团在搅拌过程中的破坏速率,也就是对机械搅拌的承受能力,也代表面筋的强度。指标数值越大,面筋越弱,面团越易流变。塌陷变形,面团不易加工,面团烘焙品质不良。 第二部分:面包的生产工艺及配方 一、原辅料及其作用、添加量: 1、面粉——主要由碳水化合物、蛋白质、水、无机盐等组成,面粉的量永远为100%。 2、糖——在面包中主要作为甜味剂和酵母食物,增加面包柔软度和保鲜期,同时糖的焦糖化作用产 生面包金黄的色泽,甜面包中用量一般为15-20%,咸面包中为5%左右。 3、油脂——面包应用固体奶油,因固体油脂不易被氧化而酸败,油脂的作用主要为润滑面筋,使面 包组织均匀细腻,增强保气能力和增加面包体积,在面包中用量一般为6-10%。 4、奶粉——奶粉具有增强面筋,增大面包体积作用,同时具有增加吸水率的作用,在面包中用量一 般为3-5%。 5、盐——增加风味,调节发酵速度,抑制细菌生长的作用,甜面包中用量一般为1-1.2%,咸面包 中一般为1.5-2%。 6、酵母——用量一般在0.8-1.2%,应视气候的变化而变化。 7、添加剂——具有调节水的软硬度,增强面筋,改善面包组织结构的作用。 二.面包配方及工艺流程(快速法) (一)面包配方实例: 基于MRF24J40的IEEE802.15.4无线收发电 路设计 时间:2010-11-30 19:05:33 来源:作者:黄智伟何娜 IEEE802.15.4无线收发器MRF24J40芯片内部包含有SPI接口、控制寄存器、MAC 模块、PHY驱动器四个主要的功能模块,支持IEEE802.15.4,MiWiTM,ZigBee等协议,工作在2.405~2.48 GHz ISM频段,接收灵敏度为-91 dBm,最大输入电平为+5 dBm,输出功率为+0 dBm,功率控制范围为38.75 dB,集成有20 MHz和32.768 kHz主控振荡器,MAC/基带部分采用硬件CSMA-CA结构,自动ACK6和FCS检测,CTR、CCM和CBC-MAC 模式采用硬件加密(AES-128),电源电压范围为2.4~3.6 V,接收模式电流消耗为18 mA,发射模式电流消耗为22 mA,睡眠模式电流消耗为2μA。 MRF24J40采用6 mm×6 mm QFN-40封装,引脚端封装形式如图1所示。图中:引脚端RFP和RFN分别为芯片的RF差分输入/输出正端和负端,两者都是模拟输入/输出端口,与系统天线相连接;VDD为电源电压输入引脚端,每个电源电压输入引脚端都必须连接一个电源去耦电容;GND为接地引脚端,必须低阻抗的连接到电路的接地板;GPIOO~GPIO5是通用数字I/O口,其中GPIO0也被用来作为外部功率放大器使能控制,GPIO1和GPIO2也被用来作为外部TX/RX开关控制;RESET为复位引脚端,低电平有效;WAKE为外部唤醒触发输入端;INT为到微控制器的中断引脚端;SDO,SDI,SCK和CS是MRF24J40的SPI接口输入输出引脚端,其中SDO是MRF24J40的串行数据输出,SDI是MRF24J40的串行接口数据输入,SCK是串行接口的时钟,CS是串行接口使能控制引脚端;LPOSC1和LPOSC2为32 kHz晶振输入正端和负端;OSC1和OSC2为20 MHz晶振输入正端和负端;CLKOUT为20/10/5/2.5 MHz时钟输出端;LCAP引脚端用来连接一个180 pF的PLL环路滤波器电容;XIP和RXQP为接收I通道和Q通道输出正端。 2 MRF24J40构成的IEEE802.15.4无线收发电路 MRF24J40构成的IEEE802.15.4无线收发电路如图2所示,各电源电压引脚端根据需要分 给两个例子, 一个是VHDL做顶层调用verilog 一个是verilog 做顶层调用VHDL VHDL调用verilog: module sync_block #( parameter INITIALISE = 2'b00 ) ( input clk, // clock to be sync'ed to input data_in, // Data to be 'synced' output data_out // synced data ); //VHD entity dcm_reset is port( ref_reset : in std_logic; -- Synchronous reset in ref_clk domain ref_clk : in std_logic; -- Reliable reference clock of known frequency (125MHz) dcm_locked : in std_logic; -- The DCM locked signal dcm_reset : out std_logic -- The reset signal which should be connected to the DCM ); end dcm_reset; component sync_block port ( clk : in std_logic; -- clock to be sync'ed to data_in : in std_logic; -- Data to be 'synced' data_out : out std_logic -- synced data ); end component; dcm_locked_sync_tx : sync_block port map( clk => ref_clk, data_in => dcm_locked, data_out => dcm_locked_sync ); verilog调用VHDL:(目标还是上述VHDL模块) module gmii_if ( …… ); dcm_reset rx_dcm_reset ( .ref_reset (tx_reset), .ref_clk (tx_clk), 烘焙试题库 1、简述面包按质地的分类? 答:面包按质地分为: 1)软质面包:表皮组织都比较柔软面包。 2)硬质面包:内部组织比较结实的面包。 3)脆皮面包:表皮较干易折断,内部比较柔软的面包 4)松质面包:内部组织分层次的面包。 2、简述德式面包与美式面包特点? 答:德式面包以小麦粉为主料,多采用一次发酵法,面包酸度大,如黑面包, Vc 含量高于其 他面包。美式面包以长方形白吐司为主,松软,弹性足。 3、简述小麦的四种分类?答:1)按产地分:美国小麦、加拿大小麦、澳洲小麦、中国南方小麦及北方小麦等。 2 )按表皮颜色来分:红麦、白麦、花麦。 3)按播种季节来分:春小麦和冬小麦。 4 )按角质含量来分:硬质小麦和软质小麦。 4、简述面包粉和糕点粉成分的国际标准 答)面包粉:水分12-13 %,蛋白质11-13%,碳水化合物74 -76 %,脂肪1-1,5%,灰分 0.5 %。 蛋糕粉水分12-13%,蛋白质7-9.5 %,碳水化合物75 -77 %,脂肪1-1.5%,灰分0.4% 5、简述面筋形成机理及物理性质?答:当面粉加水经过搅拌或揉搓后,麦谷蛋白吸水膨胀,再膨胀过程中,吸收了麦胶蛋白、酸溶蛋白及少量可溶性蛋白,形成了网状结构即面筋。 面筋的物理性质有: 1)弹性:面筋在拉伸或按压后恢复到原来状态的能力。 2)延伸性:面筋拉伸时表现的延伸性能。 3)韧性:面筋在拉伸时的抵抗能力。 6、选择面粉时要考虑哪几种因素?答:1)蛋白质含量及质量:蛋白质含量在11 -13 之间。 2)粉色:要求粉色洁白,灰分较少。 3)吸水量:达到一定吸水量。 4)搅拌及发酵耐力:搅拌耐力强,面团不易打过,发酵耐力强,面包不易发过 7、简述烘焙酵母的三种分类及使用方法? 1)鲜酵母:和面粉直接混匀即可,0 —4C冷藏保存,保值期2个月 2)活性干酵母:需要用水活化使用,保质期两年。 3)即发酵母:直接与面粉拌匀即可,保值期两年。 8、简述酵母发酵机理? 答:酵母发酵过程是将碳水化合物转变为二氧化碳及酒精过程,酵母的发酵原理用面粉中的糖份与其他营养物,在适宜的生长条件下繁殖产生二氧化碳气体,使面团膨胀成海绵状结构 QH IN CV葡蔔穗)+(5 0? f 6CO2 -+H3o+2871q 其化学方程式:有氧呼吸 口血厲]葡蔔镭)一?【儈希)兀6 4 100kj 无氧呼吸 9)简述酵母在面包制作中的作用? 开心品味屋- 烘培原料、工具、模具,DIY 套餐,餐饮调料、香料、辅料 烘焙基础知识大全 好像我们这里还没有特别全的有关烘焙基础知识的帖子,刚好自己也在摸索阶段,那我就逐渐完善这 个帖子吧~ (一)烘焙工具的基本知识 烤箱 建议采用可以上下管加热,且有温度和时间刻度,容积至少在13L 以上的家用电烤箱。 PS:如果烤箱为华氏计量温度,可以运用此公式换算摄氏温度:摄氏=(华氏-32℃)×5÷9 家用烤箱的品牌和规格有很多,选择时要注意一下几点: 1)最高温度可以达到250 度,因为很多需要烘烤的食品一般都不会超过250 度。 2)可以定时60 分钟或更长时间,因为有些点心或肉类需要烤很久,能定时60 分钟或120 分钟的 烤箱在烤制时更方便。 3)内容积在20L 以上为宜,并且内部有至少两层放臵烤盘的位臵。足够的空间才可以放臵比较常 用的蛋糕模具,相对来说容积大的烤箱空间内部温度更均匀。另外,不同的产品在烘烤时需要调整 放臵的上下不同位臵。 4)要买有顶部和底部两层加热管的烤箱。这样,就可以分开控制开关,有些产品需要单独用上火 或下火时烘烤。 备注:烤箱在使用时需要提前预热,也就是设定好温度,提前打开空烧5 分钟左右,使内部达到需 要的烘烤温度。另外,烤箱买回后,在首次使用前,应用纸巾将加热管上的油擦去(某些厂家给加 热管涂油的目的,是为了避免在未销售时加热管受潮生锈),否则在使用时会有黑烟冒出。 40 摄氏度,可以用来发酵面团和酸奶,以代替温水和棉被。 50 摄氏度,可以将食物脱水,制成各种水果干、蔬菜干、肉干,以便于保存,烘干的时候要稍微 打开烤箱门,以利于水分散发。 60 摄氏度,可以用来制作香肠、腊肉。 开心品味屋- 烘培原料、工具、模具,DIY 套餐,餐饮调料、香料、辅料 烤盘和烤网 一般随烤箱会附带烤盘和烤网。烤盘用来盛放需要烘烤的食物,如肉类、饼干类和面包等等。烤网 可以用来放臵带有模具的食品,如蛋糕、各种派等等,烤网还有一个重要的作用,就是将烤好的食 本文档含有很多Verilog HDL例子://与门 module zxhand2(c,a,b); input a,b; output c; assign c= a & b; endmodule //或门 module zxhor2(c,a,b); input a,b; output c; assign c= a | b; endmodule //非门 module zxhnot2(c,b); input b; output c; assign c=~ b; endmodule ////异或门 module zxhxro2(c,a,b); input b; output c; assign c=a ^ b; endmodule 两选一电路 module data_scan(d0,d1,sel,q); output q; input d0,d1,sel; wire t1,t2,t3; n1 zxhand2(t1,d0,sel); n2 zxhnot2 (t4,sel); n3 zxhand2(t2,d1,t4); n4 zxhor2(t3,t1,t2); assign q=t1; endmodule verilog HDL实例(一) 练习一.简单的组合逻辑设计 目的: 掌握基本组合逻辑电路的实现方法。 这是一个可综合的数据比较器,很容易看出它的功能是比较数据a与数据b,如果两个数据相同,则给出结果1,否则给出结果0。在Verilog HDL中,描述组合逻辑时常使用assign结构。注意 equal=(a==b)?1:0,这是一种在组合逻辑实现分支判断时常使用的格式。 模块源代码: //--------------- compare.v ----------------- module compare(equal,a,b); input a,b; output equal; assign equal=(a==b)?1:0; //a等于b时,equal输出为1;a不等于b时, //equal输出为0。 endmodule 测试模块用于检测模块设计得正确与否,它给出模块的输入信号,观察模块的内部信号和输出信号,如果发现结果与预期的有所偏差,则要对设计模块进行修改。 测试模块源代码: `timescale 1ns/1ns //定义时间单位。 module comparetest; reg a,b; wire equal; initial //initial常用于仿真时信号的给出。 begin a=0; b=0; #100 a=0; b=1; #100 a=1; b=1; #100 a=1; b=0; #100 $stop; //系统任务,暂停仿真以便观察仿真波形。 end compare compare1(.equal(equal),.a(a),.b(b)); //调用模块。 Endmodule 烘焙知识大全 蛋糕,面包等做法知识 面粉烘焙的基础材料介绍 高筋面粉:中筋面粉:低筋面粉 全麦面粉:是用小麦的麦壳连米糠及胚芽骨胚乳碾磨而成,常用来制作全麦面包、馒头、饼干。 玉米淀粉:简称玉米粉,是玉蜀黍淀粉,可作为勾芡稠化的材料,有胶冻能力,经加水调开后,加热至65度时,即可产生胶凝作用,多用于派馅,布丁馅的作用。还可在蛋糕的配方中加入可适当降低面粉的筋度等。 玉米碎粒:是由玉蜀黍磨研而成细小碎粒,在烘焙产品中用作做玉米粉面包和杂粮面包,制作比萨、法式面包时也可将其撒在烤盘上,作为整形后面团防黏之用增加口感。 元宵粉:泡过的糯米加水磨成米浆后,再干燥成粉,极细致。多用来制作汤元、元宵、冰皮月饼等。 澄粉:即小麦淀粉,无筋性,用于制作虾饺皮、水晶饺等(又称水晶粉)。 葛粉:葛根水磨成粉后, 糕粉:又称凤片粉,圆糯米泡水之后,炒熟,然后再磨成粉,因为是熟粉,所以要冷藏才不会产生油味,多用于制作老婆饼。 葛粉:葛根水磨成粉后,再脱水干燥,属淀粉类胶冻原料,常用于制作日式凉点,口感受滑糯,软硬适中。 麦片:通常是指燕麦片,烘焙产品中用于制作杂粮面包和小西饼等。 裸麦粉:是由裸麦磨制而成,因其蛋白质成分与小麦不同,不含有面筋,多数与60%-70%其他面粉混合使用,不然面包质地会太紧实,沉重,口感不佳。 小麦胚芽:为小麦在磨粉过程中将胚芽部分与本体分离,用作胚芽面包之制作,小麦胚芽中含有丰富的营养价值,尤为孩童和老年人之营养食品。 麸皮:为小麦最外层的表皮,多数当作饲料使用,但也可掺在高筋白面粉中制作高纤维麸皮面包。 油脂:烘焙基础材料介绍 油脂可以分为液态和固态两种形式。做海绵蛋糕或戚风蛋糕时用的是液态油,以便能融入面糊中拌匀,故色拉油或融化的黄油都可以使用。 做面糊类蛋糕用的是固体油,如黄油、麦淇淋等等,目的是能拌入大量的空气使蛋糕组织膨胀。 第一章电工基本基础 第一节直流电路和分析方法 本节主要讨论电路的基本物理量、电路的基本定律,以及应用它们来分析与计算各种直流电路的方法,包括分析电路的工作状态和计算电路中的电位等。这些问题虽然在本节直流电路中提出,但也同样适用于后文介绍的线性交流电路与电子电路中,是分析计算电路的重要基础。 一、电路及基本物理量 1.电路和电路图 电路是由电工设备和元器件按一定方式连接起来的总体,它提供了电流通过的路径。如居室的照明灯电路、收音机电子电路、机床控制电气电路等。随着电流的流动,在电路中进行能量的传输和转换,通常把电能转换成光、热、声、机械等形式的能量。 电路可以是简单的,也可能是复杂的。实际的电路由元件、电气设备和连接导线连接构成。为了便于对电路进行分析和计算,通常把实际的元件加以理想化,用国家统一规定的电路图形符号表示;用这些简单明了的图形符号来表示电路连接情况的图形称为电路图。 例如,图1—1(a)所示的符号代表干电池(电源),长线端代表正极,短线端代表负极。图1—1(b)所示的符号代表小灯泡(负载)。图1—l(c)所示的符号代表开关。用直线表示连接导线将它们连接起来,就构成了一个电路,如图1—2所示。 一般电路都是由电源、负载、开关和连接导线四个基本部分组成的。电源是把非电能能量转换成电能,向负载提供电能的设备,如干电池、蓄电池和发电机等。负载即用电器,是将电能转变成其他形式能量的元器件。如电灯可将电能转变为光能,电炉可将电能转变为热能,扬声器可将电能转变为声能,而电动机可将电能转变为机械能等。开关是控制电路接通或断开的器件。连接导线的作用是输送与分配电路中的电能。 2.电路的基本物理量 (1)电流电荷有规则的运动就形成电流。通常在金属导体内部的电流是自由电子在 电场力作用下运动而形成的。而在电解液中(如蓄电池中),电流是由正、负离子在电场力作用下,沿着相反方向的运动而形成的。 电流的大小用电流强度即电荷的流动率来表示。设在极短的时间内通过导体横截面的电荷量为dq如,则 电流强度 dq i dt (1—l) 其中i是电流强度的符号,电流强度习惯上常被称为电流。 如果任意一时刻通过导体横截面的电荷量都是相等的,而且方向也不随时间变化, 一、组合逻辑实验 (2) 实验13X8译码器程序 (2) 实验2二-十进制译码器 (2) 实验3BCD码—七段数码管显示译码器 (3) 实验48-3编码器 (4) 实验58-3优先编码器 (4) 实验6十—二进制编码器 (5) 实验7三选一数据选择器 (5) 实验8半加器 (6) 实验9全加器 (7) 实验10半减器 (8) 实验11全减器 (8) 实验12多位数值比较器 (9) 实验13奇偶校验 (9) 实验14补码生成 (10) 实验158位硬件加法器的设计 (10) 实验164位并行乘法器 (10) 实验17七人表决器 (10) 实验18格雷码变换 (11) 二、时序逻辑实验 (11) 实验1D触发器 (11) 实验2JK触发器 (12) 实验3四位移位寄存器 (12) 实验4异步计数器 (13) 实验5同步计数器 (14) 实验6可逆计数器 (15) 实验7步长可变的加减计数器 (16) 实验8含异步清0和同步时钟使能的4位加法计数器 (17) 实验9顺序脉冲发生器 (18) 实验10序列信号发生器 (18) 实验11用状态机实现串行数据检测器 (19) 实验12分频器 (20) 实验13Moore状态机 (21) 实验14Mealy状态机 (23) 实验15三层电梯 (24) 实验16性线反馈移位寄存器(LFSR)设计 (32) 实验17正负脉宽数控调制信号发生器 (32) 三、存储器设计 (34) 实验1只读存储器(ROM) (34) 实验2SRAM (34) 实验3FIFO (35) 四、扩展接口实验 (39) 实验1流水灯 (39) 实验2VGA彩色信号显示控制器设计 (40) 蛋糕的种类烘焙基础知识-CAL-FENGHAI-(2020YEAR-YICAI)_JINGBIAN 蛋糕的种类有很多,根据材料和做法的不同,比较常见的可以分为以下几类: 1、海绵蛋糕(Sponge Cake):海绵蛋糕是一种乳沫类蛋糕,构成的主体是鸡蛋、糖搅打出来的泡沫和面粉结合而成的网状结构。因为海绵蛋糕的内部组织有很多圆洞,类似海绵一样,所以叫作海绵蛋糕。海绵蛋糕又分为全蛋海绵蛋糕和分蛋海绵蛋糕,这是按照制作方法的不同来分的,全蛋海绵蛋糕是全蛋打发后加入面粉制作而成的;分蛋海绵蛋糕在制作的时候,要把蛋清和蛋黄分开后分别打发再与面粉混合制作而成的。 2、戚风蛋糕(Chiffon Cake):是比较常见的一种基础蛋糕,也是现在很受西点烘焙爱好者喜欢的一种蛋糕,像是生日蛋糕一般就是用戚风蛋糕来做底,所以说戚风蛋糕算是一个比较基础的蛋糕。戚风蛋糕的做法很像分蛋的海绵蛋糕,其不同之处就是材料的比例,新手还可以加入发粉和塔塔粉,因此蛋糕的组织非常松软。 3、天使蛋糕(Angel Fool Cake):天使蛋糕也是一种乳沫类蛋糕,就是蛋液经过搅打后产生的松软的泡沫,所不同的是天使蛋糕中不加入一滴油脂,连鸡蛋中含有油脂的蛋黄也去掉,只用蛋清来做这个蛋糕,因此做好的蛋糕颜色清爽雪白,故称为天使蛋糕。 4、重油蛋糕(Pound Cake):也称为磅蛋糕,是用大量的黄油经过搅打再加入鸡蛋和面粉制成的一种面糊类蛋糕。因为不像上述几种蛋糕一样是通过打发的蛋液来增加蛋糕组织的松软,所以重油蛋糕在口感上会比上面几类蛋糕来得实一些,但因为加入了大量的黄油,所以口味非常香醇。比较常见的是在面糊中加入一些水果或果脯,这样可以减轻蛋糕的油腻味。 5、奶酪蛋糕(Cheese Cake):音译也可以称为芝士蛋糕,是现在比较受大家喜欢的一种蛋糕。奶酪蛋糕是指加入了多量的乳酪做成的蛋糕,一般奶酪蛋糕中加入的都是奶油奶酪(cream cheese)。 奶酪蛋糕又分为以下几种: (1)重奶酪蛋糕:即奶酪的份量加得比较多,一般1个8寸的奶酪蛋糕,奶油奶酪的份量应该不少于250克。因为奶酪的份量比较多,所以重奶酪蛋糕的口味比较实,奶酪味很重,所以在制作时多会加入一些果酱来增加口味。 (2)轻奶酪蛋糕:轻奶酪蛋糕在制作时奶油奶酪加得比较少,同时还会用打发的蛋清来增加蛋糕的松软度,粉类也会加得很少,所以轻奶酪蛋糕吃起来的口感会非常绵软,入口即化。(3)冻奶酪蛋糕:是一种免烤蛋糕,会在奶酪蛋糕中加入明胶之类的凝固剂,然后放冰箱冷藏至蛋糕凝固,因为不经过烘烤,所以不会加入粉类材料。 6、慕斯蛋糕(Mousse Cake):也是一种免烤蛋糕,是通过打发的鲜奶油,一些水果果泥和胶类凝固剂冷藏制成的蛋糕,一般会以戚风蛋糕片做底。 【例3.1】4位全加器 module adder4(cout,sum,ina,inb,cin); output[3:0] sum; output cout; input[3:0] ina,inb; input cin; assign {cout,sum}=ina+inb+cin; endmodule 【例3.2】4位计数器 module count4(out,reset,clk); output[3:0] out; input reset,clk; reg[3:0] out; always @(posedge clk) begin if (reset) out<=0; //同步复位 else out<=out+1; //计数 end endmodule 【例3.3】4位全加器的仿真程序 `timescale 1ns/1ns `include "adder4.v" module adder_tp; //测试模块的名字 reg[3:0] a,b; //测试输入信号定义为reg型 reg cin; wire[3:0] sum; //测试输出信号定义为wire型 wire cout; integer i,j; adder4 adder(sum,cout,a,b,cin); //调用测试对象 always #5 cin=~cin; //设定cin的取值 initial begin a=0;b=0;cin=0; for(i=1;i<16;i=i+1) #10 a=i; //设定a的取值 end - 1 - initial begin for(j=1;j<16;j=j+1) #10 b=j; //设定b的取值 end initial//定义结果显示格式 begin $monitor($time,,,"%d + %d + %b={%b,%d}",a,b,cin,cout,sum); #160 $finish; end endmodule 【例3.4】4位计数器的仿真程序 `timescale 1ns/1ns `include "count4.v" module coun4_tp; reg clk,reset; //测试输入信号定义为reg型 wire[3:0] out; //测试输出信号定义为wire型 parameter DELY=100; count4 mycount(out,reset,clk); //调用测试对象 always #(DELY/2) clk = ~clk; //产生时钟波形 initial begin//激励信号定义 clk =0; reset=0; #DELY reset=1; #DELY reset=0; #(DELY*20) $finish; end //定义结果显示格式 initial $monitor($time,,,"clk=%d reset=%d out=%d", clk, reset,out); endmodule 【例3.5】“与-或-非”门电路 module AOI(A,B,C,D,F); //模块名为AOI(端口列表A,B,C,D,F) input A,B,C,D; //模块的输入端口为A,B,C,D output F; //模块的输出端口为F - 2 - 实验四串口接收模块电路设计 一、实验目的: 1、熟练使用ISE设计工具。 2、理解串口传输协议。理解采用“自顶向下”设计思路,分解模块的方法。 3、在ISE使用Verilog HDL设计串口接收模块,完成仿真、下载。 二、原理分析 (一)串口传输协议概述 设计完成异步串口通信通用异步收发是一种典型的异步串口通信,简称UART。串口通信时序如图1所示。 图1 通用异步收发时序图 由图1可以看出,在没有数据传送时,通信线会一直处于高电平,即逻辑1状态;当有数据传送时,数据帧以起始位开始,以停止位结束。起始位为低电平,即逻辑0状态;停止位为高电平,即逻辑1状态,其持续时间可选为1位、1.5位或2位(本次设计选择持续时间1位)。接收端在接收到停止位后,知道一帧数据已经传完,转为等待数据接收状态;只要再接收到0状态,即为新一帧数据的起始状态。 数据帧的数据位低位(LSB)在前,高位(MSB)在后,根据不同的编码规则,数据位可能为5位、6位、7位或者8位(本次设计数据位定位8位)。校验位也可根据需要选择奇校验、偶校验或者不要校验(本次设计不要校验位)。 (二)串口时序分析 串口通讯常用“波特率”表述串口传输速率,常用的参数有9600 bps 和115200 bps等。在硬件传输角度看,波特率表征了传输一位数据所需要的时间。例如:波特率是9600 bps,传输一位数据的时间是1/9600= 0.000104166666666667秒。如果FPGA系统时钟是20MHZ,则一位数据传输时间相当于(1/9600)/(1/20M)=2083个20MHZ时钟周期。 设一帧数据位数=1(开始位)+8(数据位)+1(校验位)+1(结束位)=11位,所以传输一帧数据的时间是11*1/9600=0.00114583333333333333333333333333秒。 为了稳定采集串口数据帧的数据,需要在每位数据的“中间时刻”采样,由此,需要在每位数据开始时刻对时钟进行计数,若系统时钟是20MHZ,则在计数至2083/2=1042时采样此时刻的数值。 三、系统分析: 为实现串口接收电路,FPGA应该完成: 1、及时发现数据传输的开始,并判断每一位的开始。 2、按照“在数据位中间采样”的要求,确认采样时刻。 3、将采样得到串行数据转换为并行数据。 蛋糕烘焙理论知识 蛋糕的分类及性质 蛋糕的种类很多,归纳起来可分为三大类: 一、乳沫类,又叫清蛋糕它又分为蛋白类和海绵类两种 1、蛋白类-天使蛋糕,主要原料为蛋白、砂糖、面粉。特点:洁白的,口感稍显粗糙,味道不算太好,但外观漂亮,蛋腥味浓。 2、全蛋类-海绵蛋糕,主要原料为全蛋、砂糖、面粉,蛋糕油和液体油。特点:口感清香,结构绵软,有弹性,油脂轻。 二、戚风类 在九十年代初,随着台资烘焙企业进入大陆市场,他们制作的戚风蛋糕也就逐渐流行。 其实戚风蛋糕的历史并不短,至少已有三、四十年了,所谓戚风,是英文CHIFFON译音,该单词原是法文,意思是拌制的馅料向打发的蛋白那样柔软,而戚风的打发正是将蛋黄和蛋白分开搅拌,先把蛋白部分搅拌的很蓬松,很柔软,再拌入蛋黄面糊,因而将这类蛋糕称之为戚风蛋糕。它面糊稀软,蓬松,产品特点:蛋香、油香、有回味,结构绵软有弹性,组织细密紧韧。 三、面糊类-重油蛋糕 它是利用配方中之固体油脂在搅拌时拌入空气,面糊于烤炉内受热膨胀成蛋糕,主要原料是蛋、糖、面粉和黄油。它面糊浓稠,膨松,产品特点:油香浓郁、口感深香有回味,结构相对紧密,有一定的弹性。又称为奶油蛋糕,因为油的用量达到了100%。 蛋糕的原料 一、鸡蛋是蛋糕制作的重要材料之一,在蛋糕中的成本占到1/3-1/2。 1、鸡蛋的化学成分: 鸡蛋中含有蛋清、蛋黄和蛋壳,其中蛋清占60%,蛋黄占30%,蛋壳占10%。蛋白中含有水分、蛋白质、碳水化合物、脂肪、维生素,蛋白中的蛋白质主要是卵白蛋白、卵球蛋白和卵粘蛋白。蛋黄中的主要成分为脂肪、蛋白质、水分、无机盐、蛋黄素和维生素等,蛋黄中的蛋白质主要是卵黄磷蛋白和卵黄球胆白。 2、鸡蛋的主要功能: ①、粘结、凝固作用 鸡蛋含有相当丰富的蛋白质,这些蛋白质在搅拌过程中能捕集到大量的空气而形成泡沫状,与面粉的面筋形成复杂的网状结构,从而构成蛋糕的基本组织,同时蛋白质受热凝固,使蛋糕的组织结构稳定。②、膨发作用 已打发的蛋液内含有大量的空气,这些空气在烘烤时受热膨胀,增加了蛋糕的体积,同时蛋的蛋白质分布于整个面糊中,起到保护气体的的作用。 ③、柔软作用 由于蛋黄中含有较丰富的油脂和卵磷脂,而卵磷脂是一种非常有效的乳化剂,因而鸡蛋能起到柔软作用。此外,鸡蛋对蛋糕的颜色、香味以及营养等方面也有重要的作用。 二、砂糖 电源电路单元 前面介绍了电路图中的元器件的作用和符号。一张电路图通常有几十乃至几百个元器件,它们的连线纵横交叉,形式变化多端,初学者往往不知道该从什么地方开始,怎样才能读懂它。其实电子电路本身有很强的规律性,不管多复杂的电路,经过分析可以发现,它是由少数几个单元电路组成的。好象孩子们玩的积木,虽然只有十来种或二三十种块块,可是在孩子们手中却可以搭成几十乃至几百种平面图形或立体模型。同样道理,再复杂的电路,经过分析就可发现,它也是由少数几个单元电路组成的。因此初学者只要先熟悉常用的基本单元电路,再学会分析和分解电路的本领,看懂一般的电路图应该是不难的。 按单元电路的功能可以把它们分成若干类,每一类又有好多种,全部单元电路大概总有几百种。下面我们选最常用的基本单元电路来介绍。让我们从电源电路开始。 一、电源电路的功能和组成 每个电子设备都有一个供给能量的电源电路。电源电路有整流电源、逆变电源和变频器三种。常见的家用电器中多数要用到直流电源。直流电源的最简单的供电方法是用电池。但电池有成本高、体积大、需要不时更换(蓄电池则要经常充电)的缺点,因此最经济可靠而又方便的是使用整流电源。 电子电路中的电源一般是低压直流电,所以要想从 220 伏市电变换成直流电,应该先把220 伏交流变成低压交流电,再用整流电路变成脉动的直流电,最后用滤波电路滤除脉动直流电中的交流成分后才能得到直流电。有的电子设备对电源的质量要求很高,所以有时还需要再增加一个稳压电路。因此整流电源的组成一般有四大部分,见图 1 。其中变压电路其实就是一个铁芯变压器,需要介绍的只是后面三种单元电路。 二、整流电路 整流电路是利用半导体二极管的单向导电性能把交流电变成单向脉动直流电的电路。 ( 1 )半波整流 半波整流电路只需一个二极管,见图 2 ( a )。在交流电正半周时 VD 导通,负半周时 VD 截止,负载 R 上得到的是脉动的直流电 一:世界家具行业发展简史 世界家具风格的演变。 1、歌特式家具(古典式) 2、意大利家具(米兰国际展在全世界最具影响力,在15世纪文化复兴以后,建筑影响了家具的风格) 3、德国家具(15——20世纪) A、北日耳曼风格家具(以雕刻和镶嵌来装饰) B、北欧风格家具(以原木为材料,在丹麦、瑞典等北欧是一种潮流) C、德国的包豪斯家具(20世纪依赖机器,设计师将工艺、工业融于一起) 4、英国家具 A、都铎式家具:15世纪,虽具皇家色彩但有些苯拙,简单粗糙,橡木时期; B、雅可宾式家具:16世纪,特点是球/圆形脚、家具直线多,这种样式也叫弗兰德式; C、胡桃木时期:17世纪初,曲线代替雅可宾的直线; D、安娜女王式家具:17世纪中叶,曲线椅子、弯脚和琴式高椅背,东方风格、刺绣; E、奇彭代尔.赫普怀特家具风行:融合了中国元素的回纹、窗格造型。 同时期其它风行的家具还有 A)、亚当式家具:六角八角形,椭圆形,古典精神 B )、新个人风格:19世纪 5、法国家具 A、巴洛克式(路易十四式)风格,17世纪,豪华奔放型(深圳金凤凰同其风格); B、洛可可风格,17世纪下半页,是为巴洛克风格的延续,很粗放,不够细腻; C、帝国式家具:粗线条、古典题材、深绿、红褐,红木、檀木、花梨等为材料 D、新古典主义风格:法国、英国、美国等流行于19世纪(是对巴洛克、洛可可风格的延续简单线条,透明型) 以下国家的流行风格都是由其发展而来: 法国的帝欧式 英国的摄政式 美国的邓肯法夫式 现代的迪卡、天一、金凤凰、也源于此风格。 6、美国家具:1 7、18世纪,简单造型,形式多样,美式新 古典家具由英法起源。 7、中国:可以说发展于明清时期(红木家具时期) A、明代家具:14——18世纪,结构沿用中国早期建筑的梁柱结构,简洁、比例适中,对称均匀,线条挺秀,舒展。现在的“友联)具有明式风格。 B、清代家具:设计简单,继承了明代家具的整体结构,以不施过多装饰的特点见长;显得华丽、厚重。现代的“美联“具有清式风格。 明式家具巧妙而合理使用各种榫卯结构,造型蕴涵着对比美,对称和均衡的美。 清代家具漆冷红工艺,弯腿造型,雕刻屏风。 C、红木家具的特色和流派。 明式家具没有流派,到清朝才出现各地特色的家具。具体有:苏式、广式、宁式、京式。 (a)、苏式。明式家具是苏式的代表作,由于广式、京式家具的涌现,进入宫廷的苏式家具就越来越少。生产出来的家具就逐渐转向市场。为了能迎合各消费层次的不同需求,必须改进苏式家具的工艺和用料,表面用料整齐、文理漂亮、而在背板、顶底板、抽斗侧板及底板用其它杂木代替,雕花采用不规则的图案,如灵芝、云头,图案的随意性大,无标准,做工要求低。在接缝区采用贴布补救涨缩毛病,保持典雅的民族装饰风格及精湛的传统工艺。烘焙理论知识

XFP模块电路设计

计算机基础知识概述

烘焙基本知识培训

无线模块电路设计

原创:VHDL verilog 互相调用的例子

烘焙理论知识题库

烘焙基础知识大全

VerilogHDL实例

烘焙知识大全(汇总整理)

电工基础知识概述

verilog_FPGA实例

蛋糕的种类烘焙基础知识

Verilog的135个经典设计实例

实验四串口接收模块电路设计

蛋糕烘焙理论知识

电源电路设计模块图

家具基础知识概述