cadence等长规则设置

提到绕等长的问题,就不得不说一下等长约束规则的设置了。在allegro的规则管理器里,只有你想不到的规则,没有设置不了的。正是因为其五花八门,所以经常有很多的BUG出现,对于很多人来说,建规则会成为比较难跨越的高山。

等长规则的设置有多种不同的方法,有傻白甜型,有端方君子型,有腹黑高冷型,总有一款适合你的。

1、做人从傻白甜开始

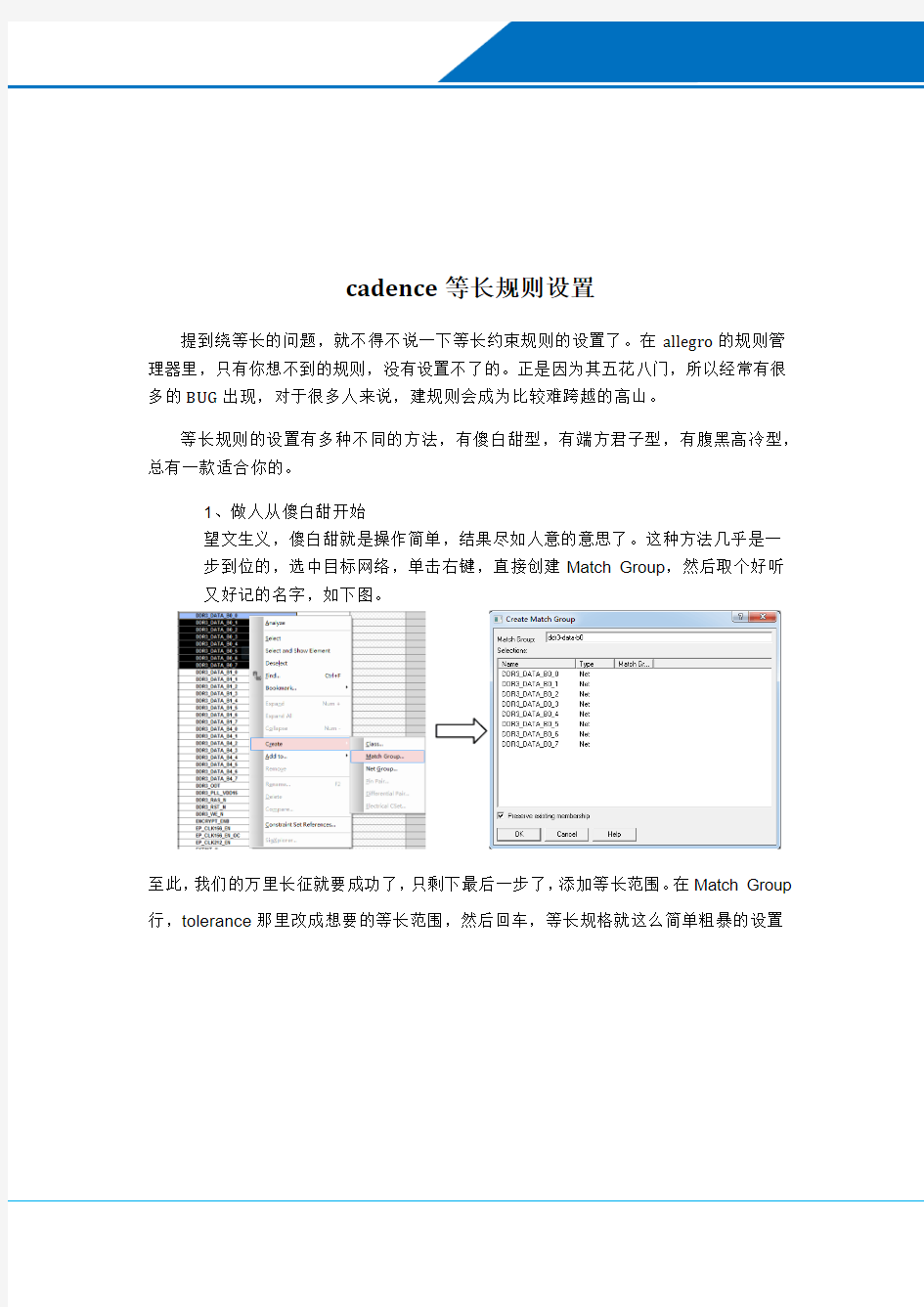

望文生义,傻白甜就是操作简单,结果尽如人意的意思了。这种方法几乎是一

步到位的,选中目标网络,单击右键,直接创建Match Group,然后取个好听

又好记的名字,如下图。

至此,我们的万里长征就要成功了,只剩下最后一步了,添加等长范围。在Match Group 行,tolerance那里改成想要的等长范围,然后回车,等长规格就这么简单粗暴的设置

好了。

2、端方君子,心之所向

对于简单的点对点的拓扑,傻白甜能起到相应的作用,但是对于一些比较复杂的拓扑结构,可能就收效甚微了,这时候就需要我们的君子登场了。

为什么说这种方法是端方君子型呢,主要是因为它一步一步,有理有据,按照步骤试一下的话,就会觉得,原来如此,建等长规则还是比较简单的。下面就是动作分解了,首先选中目标网络,建立net group。

建立net group后,选中建立的net group,单击右键,选择SigXploer命令,打开SigXploe,也可以选择单个网络打开SigXploe,网络的拓扑显示如下。

是感觉真的很美好呢?

3、腹黑高冷才是真绝色

然而,也有君子搞不定的时候,因为毕竟不是所有的BUG都是光明正大的阳谋,让你

可以知道怎么去改正,就像拓扑连接不正确时,可以通过给阻容器件赋模型来解决。有

的BUG就像避无可避的阴谋诡计,比如无法打开SigXploer,器件模型出问题等,无处

着手时,这时候就需要剑走偏锋,腹黑的方法才能够一招致胜。这次直接选择网络建立pin Pair,不管什么拓扑错误或是其他,直接避过,建立点对点的连接,这也正是高冷

风范,不管什么BUG,都是“我不听,我不听”。

然后再选择目标pin Pair ,直接建立Match Group 。建立Match Group 之后的步骤,就要问傻白甜了。

建立等长规则的方法有多种,不管遇上什么样的BUG,都会有方法去解决。

第一章在Allegro 中准备好进行SI 仿真的PCB 板图 1)在Cadence 中进行SI 分析可以通过几种方式得到结果: * Allegro 的PCB 画板界面,通过处理可以直接得到结果,或者直接以*.brd 存盘。 * 使用Specctre Quest 打开*.brd,进行必要设置,通过处理直接得到结果。这实际与上述方式类似,只不过是两个独立的模块,真正的仿真软件是下面的SigXplore 程序。 * 直接打开SigXplore 建立拓扑进行仿真。 2)从PowerPCB 转换到Allegro 格式 在PowerPCb 中对已经完成的PCB 板,作如下操作: 在文件菜单,选择Export 操作,出现File Export 窗口,选择ASCII 格式*.asc 文件格式,并指定文件名称和路径(图1.1)。 图1.1 在PowerPCB 中输出通用ASC 格式文件

图1.2 PowerPCB 导出格式设置窗口 点击图1.1 的保存按钮后出现图1.2 ASCII 输出定制窗口,在该窗口中,点击“Select All”项、在Expand Attributes 中选中Parts 和Nets 两项,尤其注意在Format 窗口只能选择PowerPCB V3.0 以下版本格式,否则Allegro 不能正确导入。 3)在Allegro 中导入*.ascPCB 板图 在文件菜单,选择Import 操作,出现一个下拉菜单,在下拉菜单中选择PADS 项,出现PADS IN 设置窗口(图1.3),在该窗口中需要设置3 个必要参数: 图1.3 转换阿三次文件参数设置窗口 i. 在的一栏那填入源asc 文件的目录 ii. 在第二栏指定转换必须的pads_in.ini 文件所在目录(也可将此文件拷入工作目录中,此例) iii. 指定转换后的文件存放目录 然后运行“Run”,将在指定的目录中生成转换成功的.brd 文件。 注:pads_in.ini 所在目录路:.Psd_14.2ToolsPCBbin 中。 4)在Allegro 文件菜单中使用打开功能将转换好的PCB 板调入Allegro 中。第二章转换IBIS 库到dml 格式并加载

Cadence OrCAD Capture 具有快捷、通用的设计输入能力,使Cadence OrCAD Capture 线路图输入系统成为全球最广受欢迎的设计输入工具。它针对设计一个新的模拟电路、修改现有的一个PCB 的线路图、或者绘制一个HDL 模块的方框图,都提供了所需要的全部功能,并能迅速地验证您的设计。OrCAD Capture 作为设计输入工具,运行在PC 平台,用于FPGA、PCB 和Cadence? OrCAD? PSpice?设计应用中,它是业界第一个真正基于Windows 环境的线路图输入程序,易于使用的功能及特点已使其成为线路图输入的工业标准。 本文介绍在Cadence OrCAD Capture 设计的时候,在不同的元件库中,包含的元件资料,都是介绍Cadence OrCAD Capture 本身自带的元件库,所以大家在自己的软件中,都可以看到,方便的选择自己的元件了 AMPLIFIER.OLB 共182个零件,存放模拟放大器IC,如CA3280,TL027C,EL4093等。 ARITHMETIC.OLB 共182个零件,存放逻辑运算IC,如TC4032B,74LS85等。 A TOD.OLB 共618个零件,存放A/D转换IC,如ADC0804,TC7109等。 BUS DRIVERTRANSCEIVER.OLB 共632个零件,存放汇流排驱动IC,如74LS244,74LS373等数字IC。 CAPSYM.OLB 共35个零件,存放电源,地,输入输出口,标题栏等。 CONNECTOR.OLB 共816个零件,存放连接器,如4 HEADER,CON A T62,RCA JACK等。 COUNTER.OLB 共182个零件,存放计数器IC,如74LS90,CD4040B。 DISCRETE.OLB 共872个零件,存放分立式元件,如电阻,电容,电感,开关,变压器等常用零件。 DRAM.OLB 共623个零件,存放动态存储器,如TMS44C256,MN41100-10等。 ELECTRO MECHANICAL.OLB 共6个零件,存放马达,断路器等电机类元件。 FIFO.OLB 共177个零件,存放先进先出资料暂存器,如40105,SN74LS232。

PCB零件封装的创建 孙海峰零件封装是安装半导体集成电路芯片的外壳,主要起到安装、固定、密封、保护芯片和增强电热性能的作用,它是芯片内部电路与外部电路的桥梁。随着电子技术飞速发展,集成电路封装技术也越来越先进,使得芯片内部电路越来越复杂的情况下,芯片性能不但没受影响,反而越来越强。 在Cadence软件中,设计者要将绘制好的原理图正确完整的导入PCB Editor 中,并对电路板进行布局布线,就必须首先确定原理图中每个元件符号都有相应的零件封装(PCB Footprint)。虽然软件自带强大的元件及封装库,但对于设计者而言,往往都需要设计自己的元件库和对应的零件封装库。在Cadence中主要使用Allegro Package封装编辑器来创建和编辑新的零件封装。 一、进入封装编辑器 要创建和编辑零件封装,先要进入Allegro Package封装编辑器界面,步骤如下: 1、执行“开始/Cadence/Release 16.3/PCB Editor”命令,弹出产品选择对话框,如下图, 点击Allegro PCB Design GXL即可进入PCB设计。 2、在PCB设计系统中,执行File/New将弹出New Drawing对话框如下图, 该对话框中,在Drawing Name中填入新建设计名称,并可点击后面Browse 改变设计存储路径;在Template栏中可选择所需设计模板;在Drawing Type 栏中,选择设计的类型。这里可以用以设计电路板(Board)、创建模型(Module),还可以用以创建以下各类封装: (1)封装符号(Package Symbol) 一般元件的封装符号, 后缀名为*.psm。PCB 中所有元件像电阻、电容、电感、IC 等的封装类型都是Package Symbol; (2)机械符号(Mechanical Symbol) 由板外框及螺丝孔所组成的机构符号, 后缀名为*.bsm。有时设计PCB 的外框及螺丝孔位置都是一样的, 比如显卡, 电脑主板, 每次设计PCB时要画一次板外框及确定螺丝孔位置, 显得较麻烦。这时我们可以将PCB的外框及螺丝孔建

CDNLive! Paper – Signal Integrity (SI for Dual Data Rate (DDR Interface Prithi Ramakrishnan iDEN Subscriber Group Plantation, Fl Presented at Introduction The need for Signal Integrity (SI analysis for printed circuit board (PCB design has become essential to ensure first time success of high-speed, high-density digital designs. This paper will cover the usage of Cadence’s Allegro PCB SI tool for the design of a dual data rate (DDR memory interface in one of Motorola’s products. Specifically, this paper will describe the following key phases of the high-speed design process: Design set-up Pre-route SI analysis Constraint-driven routing Post-route SI analysis DDR interfaces, being source synchronous in nature, feature skew as the fundamental parameter to manage in order to meet setup and hold timing margins. A brief overview of source synchronous signaling and its challenges is also presented to provide context. Project Background This paper is based on the design of a DDR interface in an iDEN Subscriber Group phone that uses the mobile Linux Java platform. The phone is currently in the final stages of system and factory testing, and is due to be released in the market at the end of August 2007 for Nextel international customers. The phone has a dual-core custom processor with an application processor (ARM 11 and a baseband processor (StarCore running at 400MHz and 208MHz respectively. The processor has a NAND and DDR controller, both supporting 16-bit interfaces. The memory device used is a multi-chip package (MCP with stacked NAND (512Mb and DDR (512Mb parts. The NAND device is run at 22MHz and the DDR at 133MHz. The interface had to be supported over several memory vendors, and consequently had to account for the difference in timing margins, input capacitances, and buffer drive strengths between different dies and packages. As customer preference for smaller and thinner phones grows, the design and placement of critical components and modules has become more challenging. In addition to incorporating various sections such as Radio Frequency (RF, Power Management, DC, Audio, Digital ICs, and sub-circuits of these modules, design engineers must simultaneously satisfy the rigid placement requirements for components such as speakers, antennas, displays, and cameras. As such, there are

Cadence原理图库设计 一.工具及库文件目录结构 Cadence提供Part Developer库开发工具供大家建原理图库使用。 Cadence 的元件库必具备如下文件目录结构为: Library----------cell----------view(包括Sym_1,Entity,Chips,Part-table) Sym_1:存放元件符号 Entity:存放元件端口的高层语言描述 Chips:存放元件的物理封装说明和属性 Part-table:存放元件的附加属性,用于构造企业特定部件 我们可以通过定义或修改上述几个文件的内容来创建和修改一个元件库,但通过以下几个步骤来创建元件库则更直观可靠一些。 二.定义逻辑管脚 在打开或新建的Project Manager中,如图示,打开Part Developer。 然后出现如下画面, 点击Create New,下图新菜单中提示大家选择库路径,新建库元件名称及器件类型。

点击ok后,Part Developer首先让大家输入元件的逻辑管脚。一个原理图符号可以有标量管脚和矢量管脚。 标量管脚在符号中有确定位置,便于检查信号与管脚的对应,但矢量管脚却可使原理图更简洁,适用于多位 总线管脚。 点击上图中的Edit,编辑器会让我们对首或尾带有数字的字符串的多种输入方式(A1; 1A; 1A1)进行选择,一但选定,编辑器即可对同时具有数字和字母的管脚输入进行矢量或标量界定。 管脚名首尾均不带数字的字符串如A; A1A则自动被识别为标量管脚。 按照元件手册决定管脚名称及逻辑方向,选择是否为低电平有效,点击ADD即可加入新的管脚。 (注:不论是标量或矢量管脚,均可采用集体输入,如在Pin Names栏可输入A1-A8, 1C-16C)

* * copyright (c) 2005 华北电力大学(北京)自动化系现场总线实验室 * All rights reserved * *文件名: ORCAD使用心得.DOC *文件标识: *摘要:本文写了写我自己的ORCAD使用心得。文中每一条每*一段都记录了这一段时间以来焚膏继晷、暑寒相接、痛苦并快乐的探索历程。今天用了一整天时间把此草稿写完,也算是对自*己有个交待,且对后来人有所启示。不幸的是,这些天茶余饭*后总为发表有ISBN标记的论文而发愁,没有太多心思弄别的.*就写这么多吧。学术腐败,郁闷!! 中国人的悲哀,诺贝尔的遗憾。 *当前版本:1.0.0 *作者:秦宇飞 *完成日期:2005年10月28日 * */ ORCAD使用心得 我自2005年8月25号起,到2005年10月22日止,用CAPTURE和ALLEGR画板,增删数次,校审N回,终成两块电路板。郁闷与欢喜之余,深感ORCAD功能强大,熟练使用真是享受呀。现将我的使用心得写出来,供大家参考。因网上已有许多介绍CAPTURE和ALLEGR操作的文章,这里就不详述具体的操作步骤。 零、ORCAD的安装注意事项 ORCAD的安装涉及CADENCE LICENSE MANAGER安装的问题。选择ALLEGRO程序里的CADENCE LICENSE MANAGER,如果选择CAPTURE里的CADENCE LICENSE MANAGER,会提示IKERNEL错误,这样CADENCE LICENSE MANAGER总也装不上去,程序也无法使用。我也弄不明白为什么CAPTURE 和ALLEGRO里同样的CADENCE LICENSE MANAGER安装程序会有不同的结果。至于其它步骤请看程序中的破解文档吧。 一、 CAPTURE 1、 CAPTURE版本选择 CAPTURE建议使用10.0以上版本。因为9.0的撤消只有一次,用得很郁闷。此外CAPTURE10.0以上版本对ALLEGRO的支持更好。 CAPTURE10.0以上版本增加了从网上原理图库中找元件封装的功能。虽然元件不是很多,但是比自己画方便了很多。我是在画完原理图之后才发现这个功能的,“超级郁闷”(童同学语)。 操作:在原理图编辑窗口点右键,PLACE DATABASE PART再点ICA,然后搜索零件就行了。可以直接放到原理图。 2、命名 (1)、元件编号一定不要重名,虽然文档里不同文件夹内的元件编号可以相同,但是这样会在DRC检测时出问题,所以最好不要这么做。 (2)、CAPTURE的元件库中有两个“地”易弄混。虽然它们的符号不一样。一个叫GND_SIGNAL,另一个叫GND,这个要在使用中要注意。

Allegro元件封装(焊盘)制作方法总结 ARM+Linux底层驱动 2009-02-27 21:00 阅读77 评论0 字号:大中小 https://www.doczj.com/doc/6f17219154.html,/html/PCBjishu/2008/0805/3289.html 在Allegro系统中,建立一个零件(Symbol)之前,必须先建立零件的管脚(Pin)。元件封装大体上分两种,表贴和直插。针对不同的封装,需要制 作不同的Padstack。 Allegro中Padstack主要包括以下部分。 1、PAD即元件的物理焊盘 pad有三种: 1. Regular Pad,规则焊盘(正片中)。可以是:Circle 圆型、S quare 方型、Oblong 拉长圆型、Rectangle 矩型、Octagon 八 边型、Shape形状(可以是任意形状)。 2. Thermal relief 热风焊盘(正负片中都可能存在)。可以是: Null(没有)、Circle 圆型、Square 方型、Oblong 拉长圆型、 Rectangle 矩型、Octagon 八边型、flash形状(可以是任意形 状)。 3. Anti pad 抗电边距(负片中使用),用于防止管脚与其他的网 络相连。可以是:Null(没有)、Circle 圆型、Square 方型、 Oblong 拉长圆型、Rectangle 矩型、Octagon 八边型、Shape形 状(可以是任意形状)。 2、SOLDERMASK:阻焊层,使铜箔裸露而可以镀涂。 3、PASTEMASK:胶贴或钢网。 4、FILMMASK:预留层,用于添加用户需要添加的相应信息,根据需要使用。 表贴元件的封装焊盘,需要设置的层面及尺寸: Regular Pad: 具体尺寸根据实际封装的大小进行相应调整后得到。推荐使用《IPC-SM-78 2A Surface Mount Design and Land Pattern Standard》中推荐的尺寸进行尺寸设计。同时推荐使用IPC-7351A LP Viewer。该软件包括目前常用的大多数S

Cadence ORCAD CAPTURE元件库介绍 - Cadence OrCAD Capture 具有快捷、通用的设计输入能力,使Cadence O rCAD Capture 线路图输入系统成为全球最广受欢迎的设计输入工具。它针对设计一个新的模拟电路、修改现有的一个PCB 的线路图、或者绘制一个HDL 模块的方框图,都提供了所需要的全部功能,并能迅速地验证您的设计。OrC AD Capture 作为设计输入工具,运行在PC 平台,用于FPGA 、PCB 和C adence? OrCAD? PSpice?设计应用中,它是业界第一个真正基于Windows 环境的线路图输入程序,易于使用的功能及特点已使其成为线路图输入的工业标准。 本文介绍在Cadence OrCAD Capture 设计的时候,在不同的元件库中,包含的元件资料,都是介绍Cadence OrCAD Capture 本身自带的元件库,所以大家在自己的软件中,都可以看到,方便的选择自己的元件了 AMPLIFIER.OLB 共182个零件,存放模拟放大器IC,如CA3280,TL027C,EL4093等。 ARITHMETIC.OLB 共182个零件,存放逻辑运算IC,如TC4032B,74LS85等。 ATOD.OLB 共618个零件,存放A/D转换IC,如ADC0804,TC7109等。 BUS DRIVERTRANSCEIVER.OLB 共632个零件,存放汇流排驱动IC,如74LS244,74LS373等数字IC。 CAPSYM.OLB 共35个零件,存放电源,地,输入输出口,标题栏等。 CONNECTOR.OLB 共816个零件,存放连接器,如4 HEADER,CON AT62,RCA JACK等。 COUNTER.OLB 共182个零件,存放计数器IC,如74LS90,CD4040B。 DISCRETE.OLB 共872个零件,存放分立式元件,如电阻,电容,电感,开关,变压器等常用零件。 DRAM.OLB 共623个零件,存放动态存储器,如TMS44C256,MN41100-10等。

Cadence 封装尺寸总结 1、 表贴IC a )焊盘 表贴IC 的焊盘取决于四个参数:脚趾长度W ,脚趾宽度Z ,脚趾指尖与芯片中心的距离D ,引脚间距P ,如下图: 焊盘尺寸及位置计算:X=W+48 S=D+24 Y=P/2+1,当P<=26mil 时 Y=Z+8,当P>26mil 时 b )silkscreen 丝印框与引脚内边间距>=10mil ,线宽6mil ,矩形即可。对于sop 等两侧引脚的封装,长度边界取IC 的非引脚边界即可。丝印框内靠近第一脚打点标记,丝印框外,第一脚附近打点标记,打点线宽视元件大小而定,合适即可。对于QFP 和BGA 封装(引脚在芯片底部的封装),一般在丝印框上切角表示第一脚的位置。 c )place bound 该区域是为防止元件重叠而设置的,大小可取元件焊盘外边缘以及元件体外侧+20mil 即可,线宽不用设置,矩形即可。即,沿元件体以及元件焊盘的外侧画一矩形,然后将矩形的长宽分别+20mil 。 d )assembly 该区域可比silkscreen 小10mil ,线宽不用设置,矩形即可。对于外形不规则的器件,assembly 指的是器件体的区域(一般也是矩形),切不可粗略的以一个几乎覆盖整个封装区域的矩形代替。 PS :对于比较确定的封装类型,可应用LP Wizard 来计算详细的焊盘尺寸和位置,再得到焊盘尺寸和位置的同时还会得到silkscreen 和place bound 的相关数据,对于后两个数据,可以采纳,也可以不采纳。

2、通孔IC a)焊盘 对于通孔元件,需要设置常规焊盘,热焊盘,阻焊盘,最好把begin层,internal层,bottom 层都设置好上述三种焊盘。因为顶层和底层也可能是阴片,也可能被作为内层使用。 通孔直径:比针脚直径大8-20mil,通常可取10mil。 常规焊盘直径:一般要求常规焊盘宽度不得小于10mil,通常可取比通孔直径大20mil (此时常规焊盘的大小正好和花焊盘的内径相同)。这个数值可变,通孔大则大些,比如+20mil,通孔小则小些,比如+12mil。 花焊盘直径:花焊盘内径一般比通孔直径大20mil。花焊盘外径一般比常规焊盘大20mil (如果常规焊盘取比通孔大20mil,则花焊盘外径比花焊盘内径大20mil)。这两个数值也是可以变化的,依据通孔大小灵活选择,通孔小时可取+10-12mil。 阻焊盘直径:一般比常规焊盘大20mil,即应该与花焊盘外径一致。这个数值也可以根据通孔大小调整为+10-12mil。注意需要与花盘外径一致。 对于插件IC,第一引脚的TOP(begin)焊盘需要设置成方形。 b) Silkscreen 与表贴IC的画法相同。 c) Place bound 与表贴IC的画法相同。 d) Assembly 与表贴IC的画法相同。 3、表贴分立元件 分立元件一般包括电阻、电容、电感、二极管、三极管等。 对于贴片分立元件,封装规则如下: a)焊盘 表贴分立元件,主要对于电阻电容,焊盘尺寸计算如下:

Cadence元件库介绍 AMPLIFIER.OLB共182个零件,存放模拟放大器IC,如CA3280,TL027C,EL4093等。ARITHMETIC.OLB共182个零件,存放逻辑运算IC,如TC4032B,74LS85等。 ATOD.OLB共618个零件,存放A/D转换IC,如ADC0804,TC7109等。 BUS DRIVERTRANSCEIVER.OLB共632个零件,存放汇流排驱动IC,如74LS244,74LS373等数字IC。CAPSYM.OLB共35个零件,存放电源,地,输入输出口,标题栏等。 CONNECTOR.OLB共816个零件,存放连接器,如4HEADER,CON AT62,RCA JACK等。COUNTER.OLB共182个零件,存放计数器IC,如74LS90,CD4040B。 DISCRETE.OLB共872个零件,存放分立式元件,如电阻,电容,电感,开关,变压器等常用零件。DRAM.OLB共623个零件,存放动态存储器,如TMS44C256,MN41100-10等。 ELECTRO MECHANICAL.OLB共6个零件,存放马达,断路器等电机类元件。 FIFO.OLB共177个零件,存放先进先出资料暂存器,如40105,SN74LS232。 FILTRE.OLB共80个零件,存放滤波器类元件,如MAX270,LTC1065等。 FPGA.OLB存放可编程逻辑器件,如XC6216/LCC。 GATE.OLB共691个零件,存放逻辑门(含CMOS和TLL)。 LATCH.OLB共305个零件,存放锁存器,如4013,74LS73,74LS76等。 LINE DRIVER RECEIVER.OLB共380个零件,存放线控驱动与接收器。如SN75125,DS275等。MECHANICAL.OLB共110个零件,存放机构图件,如M HOLE2,PGASOC-15-F等。MICROCONTROLLER.OLB共523个零件,存放单晶片微处理器,如68HC11,AT89C51等。MICRO PROCESSOR.OLB共288个零件,存放微处理器,如80386,Z80180等。 MISC.OLB共1567个零件,存放杂项图件,如电表(METER MA),微处理器周边(Z80-DMA)等未分类的零件。 MISC2.OLB共772个零件,存放杂项图件,如TP3071,ZSD100等未分类零件。 MISCLINEAR.OLB共365个零件,存放线性杂项图件(未分类),如14573,4127,VFC32等。MISCMEMORY.OLB共278个零件,存放记忆体杂项图件(未分类),如28F020,X76F041等。MISCPOWER.OLB共222个零件,存放高功率杂项图件(未分类),如REF-01,PWR505,TPS67341等。MUXDECODER.OLB共449个零件,存放解码器,如4511,4555,74AC157等。 OPAMP.OLB共610个零件,存放运放,如101,1458,UA741等。 PASSIVEFILTER.OLB共14个零件,存放被动式滤波器,如DIGNSFILTER,RS1517T,LINE FILTER等。PLD.OLB共355个零件,存放可编程逻辑器件,如22V10,10H8等。 PROM.OLB共811个零件,存放只读记忆体运算放大器,如18SA46,XL93C46等。REGULATOR.OLB共549个零件,存放稳压IC,如78xxx,79xxx等。 SHIFTREGISTER.OLB共610个零件,存放移位寄存器,如4006,SNLS91等。 SRAM.OLB共691个零件,存放静态存储器,如MCM6164,P4C116等。 TRANSISTOR.OLB共210个零件,存放晶体管(含FET,UJT,PUT等),如2N2222A,2N2905等。

Cadence软件visor功能的使用说明,远程连接软件为Exceed 设置连接的IP地址就可连接 使用方法如下 1.在桌面找到exceed图标,双击打开-这时弹出登陆界面-输入用户名.密码.就可 登陆系统 2.在登陆到的系统桌面上右击鼠标,可以看到弹出一各菜单,这时可依次选择 TOOLS在弹出的下级菜单中选则terminal , 这时弹出一个像DOS对话框的 窗口出来如图 3.我们要进入project文件夹,因为我们所有的文件都存放于此,进入文件夹的 方法如下: 在当前命令行中继续输入命令:cd project按回车确定执行命令,可以看到目录的路径变成了user/user1/project/这时侯输入命令ls再按回车确定执行命令,就可以看到显示出该目录下的所有文件和子目录 4.例如我们要进入one这个目录就可输入命令(在当前的命令行上输入)cd one 按回车确定执行命令,可以看到目录的路径变成了user/user1/project/one/查看目录下的文件就可输入命令ls 5.在one目录下会有两个子目录,gds和lay说明一下gds 文件夹是用来存 放.gds文件的目录,一般都存放于此。Lay文件夹是用来存放Cadence 导入后的应用文件的目录, 6.下面我们要进入Cadence 导入后的应用文件的目录也就是lay 目录,方法是 继续在当前目录上输入命令cd lay按回车确定执行命令,可以看到目录的路径变成了user/user1/project/lay/ 在该目录下运行Cadence软件:注linux与windows不同,在这个目录下运行该软件该软件就只能查看和修改该目录下的文件。 7.在当前命令行目录下继续输入Cadence软件的执行命令icfb &再按回车确定 执行命令,就可以看到软件正在打开,等到软件完全打开了,我们可以看到在

1. Allegro 零件库封装制作的流程步骤。 2. 规则形状的smd 焊盘制作方法。 3. 表贴元件封装制作方法。 4. 0805贴片电容的封装制作实例。 先创建焊盘,再创建封装 一、先制作焊盘 制作焊盘软件路径:candence\Release 16.6\PCB Editor Utilities\Pad Designer Pad Designer 界面 solderMask_top 比其它层大0.1mm,焊盘数据可以用复制、粘贴来完成。 当前层

Null:空; Circle:圆形; Square: 正方形; Oblong:椭圆形; Rectangle:长方形; Octagon: 八边形; Shape:形状; 封装制作完成后,选择路径,命名后进行保存Rect_x1_15y1_45 二、制作封装 操作步骤:打开Allegro 软件(allegro PCB design GXL ) file(new) OK 进入零件封装编辑界面。 设置图纸的尺寸(元件尺寸太小,所以图纸的尺寸也要设置小) 单位:毫米 X \Y:坐标原点绝对坐标设置 精度: 4 封装类型 线(机械)设置 栅格点设置,setup--Grid

第20讲 一、正式绘制元件封装 操作步骤: layout Pins 如果要把焊盘放在原点(0,0),选择好焊盘后,在命令(command )行输入x 0 0 ,然后回车,这样焊盘就自动跳到坐标原点(0,0)上啦。 二、盘放置好后,绘制零件的框。步骤如下: Add Line 输入坐标的方式输入,用命令(command )输入 如下图 表示具有电气连接的焊盘 表示没有电气连接的焊盘或引脚 选择路径,找到需要的焊盘 Rectangular:焊盘直线排列 Polar:焊盘弧形排列 Qty:表示直线排列数量; Spacing:两个焊盘中心 点之间的距离; Order:排列方向 旋转角度 Pin#:焊盘编号1 Inc:表示增量为1 Text block:表示字符的大小 OffsetX:表示字符放在焊盘中心 Class 与subclass 要选好 单独显示这一层的效果

实验一基本门电路设计——电路仿真 一、实验内容: 完成CMOS 反相器的电路设计完成CMOS 反相器的电路设计 实验目的 掌握基本门电路的设计方法掌握基本门电路的设计方法 熟悉Cadence 的设计数据管理结构,以及定制设计的原理图输入、电路仿真、版图设计、版图验证工具的使用 二、实验目的:基于csmc05工艺,完成一个具有逻辑反相功能的电路 设计要求:设计要求: 1.反相器的逻辑阈值在Vdd/2附近,即噪声容限最大 2.反相器的版图高度限制为24微米,电源和地线宽度各为2微米 3.反相器宽度限制为mos 器件不折栅 4.为了给顶层设计留出更多的布线资源,版图中只能使用金属1和多晶硅作为互连线,输入,输出和电源、地线等pin脚必须使用金属1 5.版图满足设计规则要求,并通过LVS 检查 三、设计过程: 启动icfb 1.建立自己的设计库 2.用Virtuoso Schematic Composer 画电路图 3. 在Analog Design Environment中进行电路仿真 4. 用Virtuoso (XL)Layout Editer 画版图 5. 利用diva 工具进行DRC检查,用dracula进行DRC和LVS验证。 四、实验步骤 1.Cadence软件操作步骤: (1).点击桌面虚拟机快捷方式图标; (2).打开虚拟机(存放路径:F:\cadence); (3).启动虚拟机

(4).单击右键,Open Teminal,弹出终端对话框,输入Cadence启动命令icfb&(&是后台运行的意思)。 2.. 新建一个库 建立自己的Design Lib 第一步: CIW-> Tools-Library manager 第二步:File-New 弹出“New Library ”对话框,在“Name”项填写要建的design lib的名字,这里是“lesson1”,选择“Attach to an existing techfile” 第三步: 弹出”Attach Design Library to Technology File”对话框,在“Technology Library”中选择st02

Cadence封装制作实例 这是因为本人现在在学习PCB layout,而网上没有很多的实例来讲解,如果有大师愿意教我那有多好啊,嘿嘿!这里本人把学习cadence封装后的方法通过实例给其他的初学者更好的理解,因为本人也是初学者,不足或错误的地方请包涵,谢谢! 一. M12_8芯航空插座封装制作 1.阅读M12_8芯航空插座的Datasheet了解相关参数; 根据Datasheet可知: a.航空插座的通孔焊盘Drill尺寸为 1.2mm≈50mil,我们可以设计其焊盘为 P65C50(焊盘设计会涉及到); b.航空插座的直径为 5.5mm=21 6.53mil,以5.5/2mm为半径; 2.根据参数设计该航空插座的焊盘; a.已知钻孔直径Drill_size≈50mil可知:Regular Pad=Drill_size+16mil 通孔焊盘尺寸计算规则: 设元器件直插引脚直径为M,则 1)钻孔直径Drill_size=M+12mil,M≤40

=M+16mil,40<M≤80 =M+20mil,M>80 2)规则焊盘Regular Pad=Drill_size+16mil,Drill_size<50mil =Drill_size+30mil,Drill_size≥50mil =Drill_size+40mil,Drill_size为矩形或椭圆形 3)阻焊盘Anti-Pad=Regular Pad+20mil 4)热风焊盘Drill_size<10mil,内径ID=Drill_size+10mil,外径 OD=Drill_size+20mil; Drill_size>10mil,内径ID= Drill_size+20mil 外径OD= Regular Pad+20mil = Drill_size+36mil,Drill_size<50mil = Drill_size+50mil,Drill_size≥50mil = Drill_size+60mil,Drill_size为矩形或椭圆b.按照通孔焊盘计算方式我们命名为P65C50,打开Pad_Designer; File\NEW,点击Browse,选择文件所放路径,新建P65C50.pad文件 新建好文件后,设置相关参数:

Introduction Consider the proverb, “It takes a village to raise a child.” Similarly, multiple design team members participate in assuring PCB power integrity (PI) as a design moves from the early concept phase to becoming a mature product. On the front end, there’s the electrical design engineer who is responsible for the schematic. On the back end, the layout designer handles physical implemen-tation. Typically, a PI analysis expert is responsible for overall PCB PI and steps in early on to guide the contributions of others. How quickly a team can assure PCB PI relates to the effectiveness of that team. In this paper, we will take a look at currently popular analysis approaches to PCB PI. We will also introduce a team-based approach to PCB PI that yields advantages in resource utilization and analysis results. Common Power Integrity Analysis Methods There are two distinct facets of PCB PI – DC and AC. DC PI guarantees that adequate DC voltage is delivered to all active devices mounted on a PCB (often using IR drop analysis). This helps to assure that constraints are met for current density in planar metals and total current of vias and also that temperature constraints are met for metals and substrate materials. AC PI concerns the delivery of AC current to mounted devices to support their switching activity while meeting constraints for transient noise voltage levels within the power delivery network (PDN). The PDN noise margin (variation from nominal voltage) is a sum of both DC IR drop and AC noise. DC PI is governed by resistance of the metals and the current pulled from the PDN by each mounted device. Engineers have, for many years, applied resistive network models for approximate DC PI analysis. Now that computer speeds are faster and larger addressable memory is available, the industry is seeing much more application of layout-driven detailed numerical analysis techniques for DC PI. Approximation occurs less, accuracy is higher, and automation of How a Team-Based Approach to PCB Power Integrity Analysis Yields Better Results By Brad Brim, Sr. Staff Product Engineer, Cadence Design Systems Assuring power integrity of a PCB requires the contributions of multiple design team members. Traditionally, such an effort has involved a time-consuming process for a back-end-focused expert at the front end of a design. This paper examines a collaborative team-based approach that makes more efficient use of resources and provides more impact at critical points in the design process. Contents Introduction (1) Common Power Integrity Analysis Methods (1) Applying a Team-Based Approach to Power Integrity Analysis (3) Summary (6) For Further Information (7)

Cadence ORCAD CAPTURE元件库介绍AMPLIFIER.OLB 共182个零件,存放模拟放大器IC,如CA3280,TL027C,EL4093等。ARITHMETIC.OLB 共182个零件,存放逻辑运算IC,如TC4032B,74LS85等。 ATOD.OLB 共618个零件,存放A/D转换IC,如ADC0804,TC7109等。 BUS DRIVERTRANSCEIVER.OLB 共632个零件,存放汇流排驱动IC,如74LS244,74LS373等数字IC。CAPSYM.OLB 共35个零件,存放电源,地,输入输出口,标题栏等。CONNECTOR.OLB 共816个零件,存放连接器,如4 HEADER,CON AT62,RCA JACK等。COUNTER.OLB 共182个零件,存放计数器IC,如74LS90,CD4040B。 DISCRETE.OLB 共872个零件,存放分立式元件,如电阻,电容,电感,开关,变压器等常用零件。 DRAM.OLB 共623个零件,存放动态存储器,如TMS44C256,MN41100-10等。ELECTRO MECHANICAL.OLB 共6个零件,存放马达,断路器等电机类元件。 FIFO.OLB 共177个零件,存放先进先出资料暂存器,如40105,SN74LS232。FILTRE.OLB 共80个零件,存放滤波器类元件,如MAX270,LTC1065等。 FPGA.OLB 存放可编程逻辑器件,如XC6216/LCC。 GATE.OLB 共691个零件,存放逻辑门(含CMOS和TLL)。 LATCH.OLB

共305个零件,存放锁存器,如4013,74LS73,74LS76等。 LINE DRIVER RECEIVER.OLB 共380个零件,存放线控驱动与接收器。如SN75125,DS275等。MECHANICAL.OLB 共110个零件,存放机构图件,如M HOLE 2,PGASOC-15-F等。MICROCONTROLLER.OLB 共523个零件,存放单晶片微处理器,如68HC11,AT89C51等。 MICRO PROCESSOR.OLB 共288个零件,存放微处理器,如80386,Z80180等。 MISC.OLB 共1567个零件,存放杂项图件,如电表(METER MA),微处理器周边(Z80-DMA)等未分类的零件。 MISC2.OLB 共772个零件,存放杂项图件,如TP3071,ZSD100等未分类零件。MISCLINEAR.OLB 共365个零件,存放线性杂项图件(未分类),如14573,4127,VFC32等。MISCMEMORY.OLB 共278个零件,存放记忆体杂项图件(未分类),如28F020,X76F041等。MISCPOWER.OLB 共222个零件,存放高功率杂项图件(未分类),如REF-01,PWR505,TPS67341等。 MUXDECODER.OLB 共449个零件,存放解码器,如4511,4555,74AC157等。 OPAMP.OLB 共610个零件,存放运放,如101,1458,UA741等。PASSIVEFILTER.OLB 共14个零件,存放被动式滤波器,如DIGNSFILTER,RS1517T,LINE FILTER 等。 PLD.OLB 共355个零件,存放可编程逻辑器件,如22V10,10H8等。 PROM.OLB