在 HCS08微控制器上使用 FLASH存储器模拟 EEPROM

- 格式:doc

- 大小:447.50 KB

- 文档页数:17

HCS08系列微控制器参考手册第一册苏州大学飞思卡尔嵌入式系统研发中心翻译 2009年11月目录第一章通用信息与结构框图 (1)1.1HCS08系列微控制器介绍 (1)1.2HCS08CPU编程模型 (2)1.3外设模块 (2)1.4MC9S08GB60的特点 (3)1.4.1 HCS08系列的共性 (3)1.4.2 MC9S08GB60的特点 (3)1.5MC9S08GB60的结构框图 (4)第二章引脚及其连接 (5)2.1简介 (5)2.2推荐的系统连接 (5)2.2.1 电源 (7)2.2.2 MC9S08GB60振荡器 (7)2.2.3 复位 (8)2.2.4 背景/模式选择(BKGD/MS) (8)2.2.5 通用I/O及外设端口 (8)第三章工作模式 (10)3.1简介 (10)3.2特征 (10)3.3运行模式 (10)3.4背景调试模式 (11)3.5等待模式 (12)3.6停止模式 (12)3.6.1 Stop1模式 (13)3.6.2 Stop2模式 (13)3.6.3 Stop3模式 (14)3.6.4 停止模式下激活BDM使能 (14)3.6.5 设置OSCSTEN位 (15)3.6.6 停止模式下LVD使能 (15)3.6.7 停止模式下的片上外设模块 (15)3.6.8 系统选择寄存器(SOPT) (17)3.6.9 系统电源管理状态和控制寄存器1(SPMSC1) (18)3.6.10 系统电源管理状态和控制寄存器2(SPMSC2) (19)第四章片上存储器 (21)4.1简介 (21)4.2HCS08核定义的存储器组织 (21)4.2.1 HCS08存储器组织 (21)4.2.2 MC9S08GB60存储映像 (22)4.2.3 复位和中断向量表 (23)4.3寄存器地址和位分配 (24)4.4RAM (29)4.560K字节的FLASH (29)4.5.1 特征 (30)4.5.2 写入、擦除和空白检测命令 (30)4.5.3 命令时间和突发模式写入 (32)4.5.3.1 行和FLASH的组织结构 (32)4.5.3.2 程序命令时序 (33)4.5.4 访问错误 (34)4.5.5 向量重定向 (34)4.5.6 FLASH块保护(MC9S08GB60) (34)4.6MC9S08GB60的安全性 (35)4.7MC9S08GB60的FLASH寄存器和控制位 (36)4.7.1 FLASH时钟分频寄存器(FCDIV) (36)4.7.2 FLASH选项寄存器(FOPT和NVOPT) (37)4.7.3 FLASH配置寄存器(FCNFG) (38)4.7.4 FLASH保护寄存器(FPROT和NVPROT) (38)4.7.5 FLASH状态寄存器(FSTAT) (39)4.7.6 FLASH命令寄存器(FCMD) (40)4.8FLASH存储器应用实例 (41)4.8.1 FLASH模块时钟的初始化 (41)4.8.2 擦除FLASH的一页(512字节) (42)4.8.3 DoOnStack子程序 (43)4.8.4 SpSub子程序 (45)4.8.5 FLASH的字节编程 (46)第五章复位和中断 (47)5.1简介 (47)5.2MC9S08GB60复位和中断的特征 (47)5.4计算机正常操作监控模块(COP)看门狗 (48)5.5中断 (48)5.5.1 中断堆栈结构 (49)5.5.2 外部中断请求(IRQ)引脚 (50)5.5.2.1 引脚配置选项 (50)5.5.2.2 边沿/电平触发 (50)5.5.3 中断向量、中断源和局部屏蔽 (51)5.6低电压检测系统(LVD) (52)5.6.1 上电复位操作 (52)5.6.2 LVD复位操作 (52)5.6.3 LVD中断操作 (53)5.6.4 低电压警告(LVW) (53)5.7实时中断(RTI) (53)5.8复位、中断以及系统控制寄存器和控制位 (53)5.8.1 中断请求状态和控制寄存器(IRQSC) (54)5.8.2 系统复位状态寄存器(SRS) (55)5.8.3 系统背景调试强制复位寄存器(SBDFR) (56)5.8.4 系统选项寄存器(SOPT) (56)5.8.5 系统设备识别寄存器(SDIDH、SDIDL) (57)5.8.6 系统实时中断状态和控制寄存器(SRTISC) (57)5.8.7 系统电源管理状态控制寄存器1(SPMSC1) (58)5.8.8 系统电源管理状态和控制寄存器2(SPMSC2) (59)第六章中央处理单元 (61)6.1简介 (61)6.2编程结构和CPU寄存器 (61)6.2.1 累加器(A) (62)6.2.2 变址寄存器(H:X) (63)6.2.3 堆栈指针(SP) (64)6.2.4 程序计数器(PC) (66)6.2.5 条件码寄存器(CCR) (66)6.3寻址方式 (70)6.3.1 隐含寻址方式(INH) (71)6.3.2 相对寻址方式(REL) (71)6.3.3 立即寻址方式(IMM) (72)6.3.4 直接寻址方式(DIR) (72)6.3.5 扩展寻址方式(EXT) (72)6.3.6.1 无偏移量变址方式(IX) (73)6.3.6.2 无偏移量变址、变址加1寻址方式(IX+) (73)6.3.6.3 8位偏移量变址方式(IX1) (73)6.3.6.4 8位偏移量变址、变址加1寻址方式(IX1+) (73)6.3.6.5 16位偏移量变址方式(IX2) (73)6.3.6.6 8位偏移量堆栈寻址方式(SP1) (74)6.3.6.7 16位偏移量堆栈寻址方式(SP2) (74)6.4特殊操作 (75)6.4.1 复位序列 (75)6.4.2 中断 (76)6.4.3 等待模式 (76)6.4.4 停止模式 (76)6.4.5 背景模式 (77)6.4.6 总线周期的用户观点 (77)6.5通过指令类别进行指令集描述 (78)6.5.1 数据传送指令 (78)6.5.1.1 加载与存储 (78)6.5.1.2 位的置位与清零 (81)6.5.1.3 存储器到存储器的传送 (82)6.5.1.4 寄存器传输和半字节交换 (82)6.5.2 算术运算指令 (83)6.5.2.1 加、减、乘和除指令 (83)6.5.2.2 加一、减一、清零和求补 (88)6.5.2.3 比较和测试 (88)6.5.2.4 BCD的计算 (88)6.5.3 逻辑操作指令 (89)6.5.3.1 与、或、异或与求补 (90)6.5.3.2 位测试指令 (91)6.5.4 移位类指令 (91)6.5.5 跳转、转移和循环控制指令 (93)6.5.5.1 无条件跳转和转移指令 (94)6.5.5.2 简单转移 (95)6.5.5.3 有符号转移 (95)6.5.5.4 无符号转移 (95)6.5.5.5 位条件转移 (96)6.5.5.6 循环控制 (96)6.5.6 相关堆栈指令 (97)6.6指令简表 (102)6.7汇编语言指南 (114)6.7.1 列表行 (115)6.7.2 汇编指令 (116)6.7.2.1 BASE——设定编译器的缺省数进制 (116)6.7.2.2 INCLUDE——指定附加源文件 (116)6.7.2.3 NOLIST/LIST——关闭或打开程序列表 (116)6.7.2.4 ORG——设置程序的起始位置 (117)6.7.2.5 EQU——把一个标号和一个数值相关联 (118)6.7.2.6 dc.b——定义存储器中字节化常量 (119)6.7.2.7 dc.w——在存储器中定义16位(字)常量 (119)6.7.2.8 ds.b——定义存储(保留)内存变量字节 (120)6.7.3 标号 (121)6.7.4 表达式 (122)6.7.5 通用文件协议 (123)6.7.6 目标代码(S19)文件 (125)第七章开发支持 (129)7.1介绍 (129)7.2特点 (130)7.3背景调试控制器(BDC) (130)7.3.1 BKGD引脚描述 (131)7.3.2 通信细节 (132)7.3.2.1 BDC通信速率考虑事项 (132)7.3.2.2 位时序细节 (133)7.3.3 BDC寄存器和控制位 (135)7.3.3.1 BDC状态和控制寄存器 (135)7.3.3.2 BDC断点匹配寄存器 (137)7.3.4 BDC命令 (137)7.3.4.1 SYNC——要求时序参考脉冲 (138)7.3.4.2 ACK_ENABLE (139)7.3.4.3 ACK_DISABLE (139)7.3.4.4 BACKGROUND (139)7.3.4.5 READ_STATUS (140)7.3.4.6 WRITE_CONTROL (140)7.3.4.7 READ_BYTE (141)7.3.4.8 READ_BYTE_WS (142)7.3.4.10 WRITE_BYTE (143)7.3.4.11 WRITE_BYTE_WS (143)7.3.4.12 READ_BKPT (144)7.3.4.13 WRITE_BKPT (144)7.3.4.14 GO (144)7.3.4.15 TRACE1 (145)7.3.4.16 TAGGO (145)7.3.4.17 READ_A (145)7.3.4.18 READ_CCR (145)7.3.4.19 READ_PC (146)7.3.4.20 READ_HX (146)7.3.4.21 READ_SP (147)7.3.4.22 READ_NEXT (147)7.3.4.23 READ_NEXT_WS (148)7.3.4.24 WRITE_A (148)7.3.4.25 WRITE_CCR (148)7.3.4.26 WRITE_PC (149)7.3.4.27 WRITE_HX (149)7.3.4.28 WRITE_SP (149)7.3.4.29 WRITE_NEXT (149)7.3.4.30 WRITE_ NEXT_WS (150)7.3.5 串行接口硬件握手协议 (150)7.3.6 取消握手协议 (152)7.3.7 BDC硬件断点 (155)7.3.8 与M68HC12BDM的不同之处 (155)7.3.8.1 8位体系结构 (156)7.3.8.2 命令格式 (156)7.3.8.3 状态位的读写 (156)7.3.8.4 BDM与停止和等待模式 (157)7.3.8.5 SYNC指令 (157)7.3.8.6 硬件断点 (157)7.4标识部分和BDC强制复位 (158)7.4.1 系统设备识别寄存器(SDIDH:SDIDL) (158)7.4.2 系统背景调试强制复位寄存器 (158)7.5片上调试系统(DBG) (159)7.5.1 比较器A和B (159)7.5.2总线信息捕捉和FIFO操作 (160)7.5.4 标记与强制断点和触发器 (161)7.5.5 CPU断点请求 (162)7.5.6 触发模式 (162)7.5.6.1 单独A触发模式 (163)7.5.6.2 A或B触发模式 (163)7.5.6.3 A然后B触发模式 (163)7.5.6.4 事件B触发模式(存储数据) (163)7.5.6.5 A然后事件B触发模式(存储数据) (163)7.5.6.6 A和B数据触发(全模式) (164)7.5.6.7 A与非B数据触发(全模式) (164)7.5.6.8 触发范围内:A≤地址≤B (164)7.5.6.9 触发范围外:地址<A 或者地址>B (164)7.5.7 DBG寄存器和控制位 (165)7.5.7.1 调试比较器A的高地址页寄存器(DBGCAH) (165)7.5.7.2 调试比较器A的低位寄存器(DBGCAL) (165)7.5.7.3 调试比较器B的高地址页寄存器(DBGCAH) (165)7.5.7.4 调试比较器B的低位寄存器(DBGCAL) (165)7.5.7.5 调试FIFO高地址页寄存器(DBGFH) (165)7.5.7.6 调试FIFO低位寄存器(DBGFL) (165)7.5.7.7 调试控制寄存器(DBGC) (166)7.5.7.8 调试触发寄存器(DBGT) (167)7.5.7.9 调试状态寄存器(DBGS) (168)7.5.8 应用信息与举例 (169)7.5.8.1 定向的调试器例子 (171)7.5.8.2 例1:终止对地址A的处理 (171)7.5.8.3 例2:终止对地址A指令的处理 (172)7.5.8.4 例3:终止在地址A或B上的指令处理 (172)7.5.8.5 例4:开始跟踪在地址A的指令 (173)7.5.8.6 例5:A到B顺序后停止的尾部跟踪 (173)7.5.8.7 例6:起始跟踪数据B写入地址A (174)7.5.8.8 例7:从地址B中读取被捕获的首八位数据 (174)7.5.8.9 例8:捕获在读地址A后写入到地址B的值 (175)7.5.8.10 例9:在一个例程中触发所有的执行命令 (175)7.5.8.11 例10:通过触发来试图处理外部FLASH (176)7.5.9 硬件断点和ROM修补 (176)附录A 指令集详述 (177)A.2命名规则 (177)A.3规范定义 (180)A.4指令集 (180)ADC Add with Carry(带进位位加) (180)ADD Add without Carry(无进位位加) (181)AIS Add Immediate Value to Stack Pointer(立即数加到SP) (182)AIX Add Immediate Value to Index Register(立即数加到HX) (182)AND Logical AND(逻辑与) (183)ASL Arithmetic Shift Left(算术左移) (184)ASR Arithmetic Shift Right(算术右移) (184)BCC Branch if Carry Bit Clear(C为0则转移) (185)BCLR n Clear Bit n in Memory(内存单元n位清零) (185)BCS Branch if Carry Bit Set(C为1则转移) (186)BEQ Branch if Equal(等于则转移) (187)BGE Branch if Greater Than or Equal To(大于或等于则转移) (187)BGND Background(进入背景调试模式) (188)BGT Branch if Greater Than(大于则转移) (188)BHCC Branch if Half Carry Bit Clear(H为0则转移) (189)BHCS Branch if Half Carry Bit Set(H为1则转移) (189)BHI Branch if Higher(大于则转移) (190)BHS Branch if Higher or Same(大于或等于则转移) (191)BIH Branch if IRQ Pin High(引脚IRQ为1则转移) (191)BIL Branch if IRQ Pin Low(引脚IRQ为0则转移) (192)BIT Bit Test(位测试) (192)BLE Branch if Less Than or Equal To(小于或等于则转移) (193)BLO Branch if Lower(小于则转移) (193)BLS Branch if Lower or Same(小于或等于则转移) (194)BLT Branch if Less Than(小于则转移) (195)BMC Branch if Interrupt Mask Clear(I为0则转移) (195)BMI Branch if Minus(结果为负则转移) (196)BMS Branch if Interrupt Mask Set(I为1则转移) (196)BNE Branch if Not Equal(不等于则转移) (197)BPL Branch if Plus(结果为正则转移) (197)BRA Branch Always(无条件短转移) (198)BRCLR n Branch if Bit n in Memory Clear(M位n为0则转移) (199)BRN Branch Never(三个总线周期的空操作) (200)BRSET n Branch if Bit n in Memory Set(M位n为1则转移) (200)BSET n Set Bit n in Memory(M位n置1) (201)BSR Branch to Subroutine(转移到子程序) (201)CBEQ Compare and Branch if Equal(比较,等于则转移) (202)CLC Clear Carry Bit(进位位C清零) (203)CLI Clear Interrupt Mask Bit(中断屏蔽位I清零) (203)CLR Clear(清零) (204)CMP Compare Accumulator with Memory(A与M比较) (204)COM Complement(按位取反) (205)CPHX Compare Index Register with Memory(HX与M比较) (206)CPX Compare X with Memory(X与M比较) (207)DAA Decimal Adjust Accumulator(A十进制调整) (208)DBNZ Decrement and Branch if Not Zero(减1不为0则转移) (209)DEC Decrement(自减1) (209)DIV Divide(无符号除法) (210)EOR Exclusive-OR Memory with Accumulator(M与A异或) (211)INC Increment(自加1) (211)JMP Jump(无条件跳转) (212)JSR Jump to Subroutine(跳转到子程序) (213)LDA Load Accumulator form Memory(取M内容到A) (213)LDHX Load Index Register form Memory(取M内容到HX) (214)LDX Load X from Memory(取M内容到X) (215)LSL Logical Shift Left(逻辑左移) (215)LSR Logical Shift Right(逻辑右移) (216)MOV Move(M单元间数据传送) (217)MUL Unsigned Multiply(无符号数乘法) (218)NEG Negate(Two’s Complement) (求补) (218)NOP No Operation(空操作) (219)NSA Nibble Swap Accumulator(A的高低4位对调) (219)ORA Inclusive-OR Accumulator and Memory(逻辑或) (220)PSHA Push Accumulator onto Stack(A进栈) (220)PSHH Push H onto Stack(H进栈) (221)PSHX Push X onto Stack(X进栈) (221)PULA Pull Accumulator from Stack(A出栈) (222)PULH Pull H from Stack(H出栈) (222)PULX Pull X from Stack(X出栈) (223)ROL Rotate Left through Carry(带进位位的循环左移) (223)ROR Rotate Right through Carry(带进位位的循环右移) (224)RSP Reset Stack Pointer(堆栈指针置$FF) (224)RTI Return from interrupt(中断返回) (225)RTS Return from Subroutine(子程序返回) (226)SBC Subtract with Carry(带借位减法) (226)SEC Set Carry Bit(进位位置位) (227)SEI Set Interrupt Mask Bit(中断屏蔽位置位) (227)STA Store Accumulator in Memory(A存入M) (228)STHX Store Index Register(HX存入M) (229)STOP Enable IRQ Pin, Stop Processing(停机) (229)STX Store X in Memory(X存入M) (230)SUB Subtract(无借位减法) (231)SWI Software Interrupt(软件中断) (231)TAP Transfer Accumulator to Processor Status Byte(写CCR) (232)TAX Transfer Accumulator to X(A复制到X) (233)TPA Transfer Processor Status Byte to Accumulator(读CCR) (233)TST Test for Negative or Zero(小于或等于0测试) (234)TSX Transfer Stack Pointer to index Register(复制SP到HX) (235)TXA Transfer X to Accumulator(复制X到A) (235)TXS Transfer Index Register Low to Stack Pointer(HX-1写入SP) (235)WAIT Enable Interrupts; Stop Processor(待机) (236)附录B 通用文件规范 (237)B.1引言 (237)B.2存储映射区域划分 (238)B.3中断向量定义 (238)B.4位定义的两种方式 (239)B.5MC9S08GB60完整的通用文件 (240)第一章通用信息与结构框图1.1 HCS08系列微控制器介绍新型的FreescaleHCS08系列微控制器,尽管包含新指令,可以执行快速调试和开发功能,但仍然和旧的M68HC08系列完全兼容。

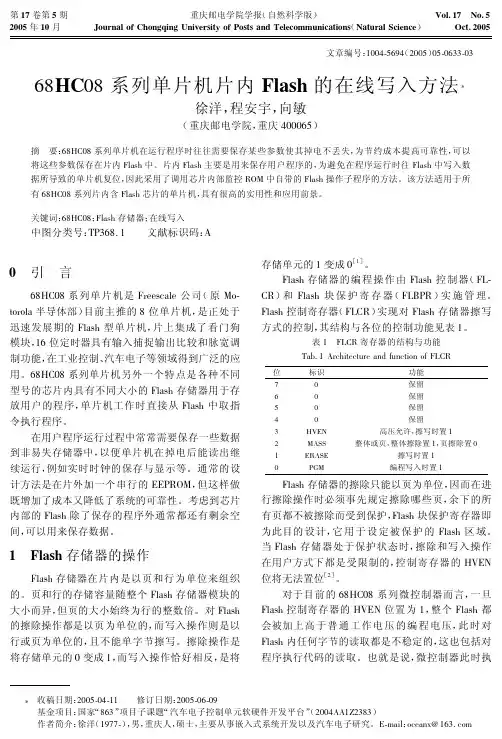

文章编号:!""#$%&’#((""%)"%$"&))$")** &+!""+系列单片机片内#$%&’的在线写入方法!徐洋,程安宇,向敏(重庆邮电学院,重庆#"""&%)摘*要:&+,-"+系列单片机在运行程序时往往需要保存某些参数使其掉电不丢失,为节约成本提高可靠性,可以将这些参数保存在片内./012中。

片内./012主要是用来保存用户程序的,为避免在程序运行时往./012中写入数据所导致的单片机复位,因此采用了调用芯片内部监控345中自带的./012操作子程序的方法。

该方法适用于所有&+,-"+系列片内含./012芯片的单片机,具有很高的实用性和应用前景。

关键词:&+,-"+;./012存储器;在线写入中图分类号:67)&+8!**文献标识码:9()引)言&+,-"+系列单片机是.:;;1<0/;公司(原5=$ >=:=/0半导体部)目前主推的+位单片机,是正处于迅速发展期的./012型单片机,片上集成了看门狗模块,!&位定时器具有输入捕捉输出比较和脉宽调制功能,在工业控制、汽车电子等领域得到广泛的应用。

&+,-"+系列单片机另外一个特点是各种不同型号的芯片内具有不同大小的./012存储器用于存放用户的程序,单片机工作时直接从./012中取指令执行程序。

在用户程序运行过程中常常需要保存一些数据到非易失存储器中,以便单片机在掉电后能读出继续运行,例如实时时钟的保存与显示等。

通常的设计方法是在片外加一个串行的??7345,但这样做既增加了成本又降低了系统的可靠性。

考虑到芯片内部的./012除了保存的程序外通常都还有剩余空间,可以用来保存数据。

32位微控制器片内FLASH模拟EEPROM的优化方法介绍在许多嵌入式系统中,由于存储空间有限,使用片内FLASH 模拟EEPROM的需求越来越高。

尽管片内FLASH一般用于程序存储,但通过使用特定的技术和策略,可以优化其性能,实现EEPROM的模拟功能。

本文将探讨一些优化方法,以提高片内FLASH模拟EEPROM的性能和可靠性。

优化方法以下是32位微控制器片内FLASH模拟EEPROM的一些优化方法:1. 均衡使用均衡使用在设计嵌入式系统时,合理规划和平衡使用片内FLASH的空间。

避免将所有数据存储在同一个区域,而是将数据分散存储于不同的FLASH块中。

这有助于减少对特定FLASH块的擦除和写入次数,提高整体使用寿命。

2. 页面写入页面写入当需要更新EEPROM模拟数据时,使用页面写入技术。

页面写入允许仅擦除和更新需要修改的页,而不是整个FLASH块。

这样可以提高写入速度,并降低擦写操作对整个系统的影响。

3. 坏块管理坏块管理片内FLASH中存在可能变得不可用的坏块。

建议在设计中引入坏块管理机制,以跳过坏块并继续使用可用的块。

可以使用坏块检测和修复算法,例如差错校验码(ECC)和纠错码(ECC)等。

4. 数据压缩和编码数据压缩和编码为了节省片内FLASH的空间,可以使用数据压缩和编码技术。

通过选择适当的算法和技术,可以减小数据的存储空间,并提高系统的效率和性能。

5. 缓存和缓冲区缓存和缓冲区在实现片内FLASH模拟EEPROM时,考虑引入缓存和缓冲区以提高读取和写入操作的效率。

通过将数据预先加载到缓存中,可以减少对FLASH的访问次数,从而提高性能和响应速度。

结论通过使用上述优化方法,可以改善32位微控制器片内FLASH模拟EEPROM的性能和可靠性。

均衡使用、页面写入、坏块管理、数据压缩和编码以及缓存和缓冲区的使用,将有助于提高系统的效率,并减少对片内FLASH的擦写次数,延长其寿命。

在实际设计中,可以根据具体需求选择适当的优化策略,以满足系统的要求。

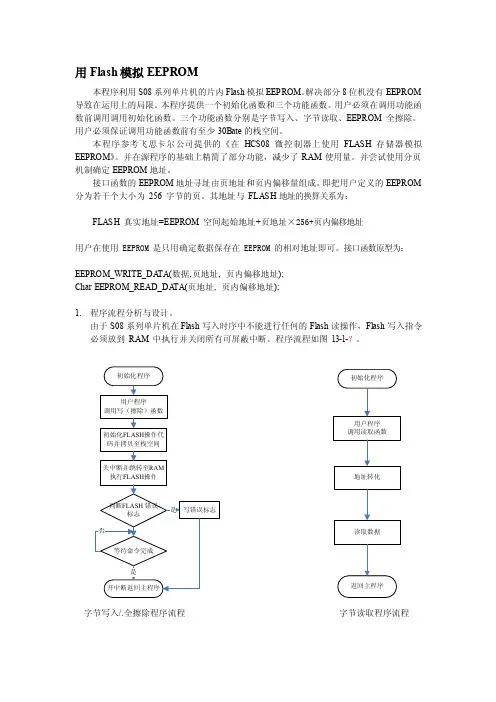

用Flash模拟EEPROM本程序利用S08系列单片机的片内Flash模拟EEPROM。

解决部分8位机没有EEPROM 导致在运用上的局限。

本程序提供一个初始化函数和三个功能函数。

用户必须在调用功能函数前调用调用初始化函数。

三个功能函数分别是字节写入、字节读取、EEPROM全擦除。

用户必须保证调用功能函数前有至少30Bate的栈空间。

本程序参考飞思卡尔公司提供的《在HCS08 微控制器上使用FLASH 存储器模拟EEPROM》。

并在源程序的基础上精简了部分功能,减少了RAM使用量。

并尝试使用分页机制确定EEPROM地址。

接口函数的EEPROM地址寻址由页地址和页内偏移量组成。

即把用户定义的EEPROM 分为若干个大小为256字节的页。

其地址与FLASH地址的换算关系为:FLASH真实地址=EEPROM空间起始地址+页地址×256+页内偏移地址用户在使用EEPROM是只用确定数据保存在EEPROM的相对地址即可。

接口函数原型为:EEPROM_WRITE_DA TA(数据,页地址, 页内偏移地址);Char EEPROM_READ_DA TA(页地址, 页内偏移地址);1.程序流程分析与设计。

由于S08系列单片机在Flash写入时序中不能进行任何的Flash读操作,Flash写入指令必须放到RAM中执行并关闭所有可屏蔽中断。

程序流程如图13-1-?。

字节写入/.全擦除程序流程字节读取程序流程图13-1-?2.程序源代码。

此程序在CodeWarrior 6.0继承编译环境中编译通过/*****************************************************///河南工业大学Freescale MCU&DSP联合实验室// 文件名:flash_program.h// CPU :MC9S08A W60// 版本:v1.0// 日期:2008年8月12日// 调试环境:CodeWarrior 6.0// 作者:曾滔// 描述: 头文件,用于保存初始化EEPROM设定、用户定制参数、编译器参数等信息。

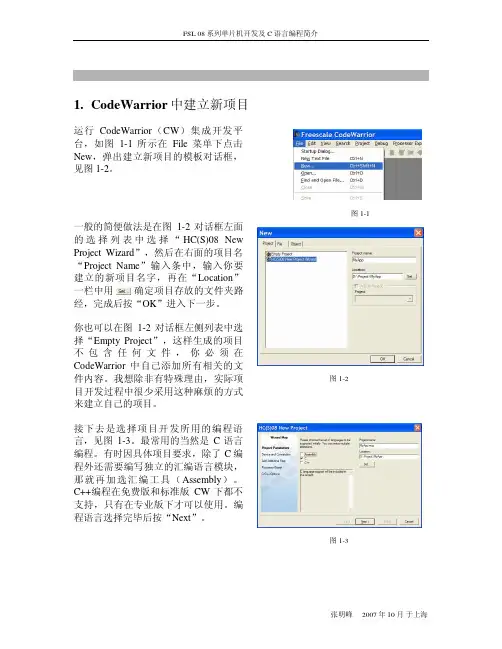

1.CodeWarrior中建立新项目运行CodeWarrior(CW)集成开发平台,如图1-1所示在File菜单下点击New,弹出建立新项目的模板对话框,见图1-2。

一般的简便做法是在图1-2对话框左面的选择列表中选择“HC(S)08 New Project Wizard”,然后在右面的项目名“Project Name”输入条中,输入你要建立的新项目名字,再在“Location”一栏中用确定项目存放的文件夹路经,完成后按“OK”进入下一步。

你也可以在图1-2对话框左侧列表中选择“Empty Project”,这样生成的项目不包含任何文件,你必须在CodeWarrior中自己添加所有相关的文件内容。

我想除非有特殊理由,实际项目开发过程中很少采用这种麻烦的方式来建立自己的项目。

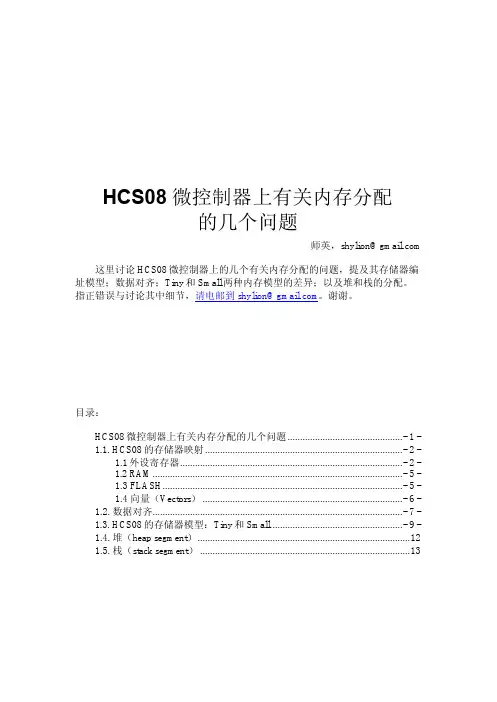

接下去是选择项目开发所用的编程语言,见图1-3。

最常用的当然是C语言编程。

有时因具体项目要求,除了C编程外还需要编写独立的汇编语言模块,那就再加选汇编工具(Assembly)。

C++编程在免费版和标准版CW下都不支持,只有在专业版下才可以使用。

编程语言选择完毕后按“Next”。

图1-1图1-2图1-3这时将出现如图1-4的对话框,让你选择项目开发对应的MCU 型号。

在CW5.x 版本下支持几乎所有的HC08和大部分HCS08单片机型号。

在最新的CW6.x 中,增加了飞思卡尔最低端的8位机(RS08系列)和低端32位处理器(Coldfire V1系列)的支持,但HC08系列的有些型号没有被包含在内。

由于HC08为比较老的产品系列,已经不推荐在新项目设计中选用,因此影响不会太大。

对于新用户来说,请尽量直接安装CW6.x 或以后推出的更新版本。

以典型的9S08系列为例,当你选择了一个MCU 型号后,在图1-4右侧会显示出所有针对该型号芯片可用的项目调试场景。

其中:∙ “Full Chip Simulator ”是芯片全功能模拟仿真,即无需任何目标系统的硬件资源,直接在你的PC 机上模拟运行单片机的程序,在模拟运行过程中可以观察调试程序的各项控制和运行流程,分析代码运行的时间,观察各种变量,等等。

HCS08微控制器上有关内存分配的几个问题师英,shylion@ 这里讨论HCS08微控制器上的几个有关内存分配的问题,提及其存储器编址模型;数据对齐;Tiny和Small两种内存模型的差异;以及堆和栈的分配。

指正错误与讨论其中细节,请电邮到shylion@。

谢谢。

目录:HCS08微控制器上有关内存分配的几个问题..............................................- 1 -1.1. HCS08的存储器映射...............................................................................- 2 -1.1外设寄存器.........................................................................................- 2 -1.2 RAM....................................................................................................- 5 -1.3 FLASH................................................................................................- 5 -1.4 向量(Vectors)................................................................................- 6 -1.2. 数据对齐....................................................................................................- 7 -1.3. HCS08的存储器模型:Tiny和Small....................................................- 9 -1.4. 堆(heap segment) (12)1.5. 栈(stack segment) (13)1.1. HCS08的存储器映射每个HCS08微控制器的存储器映射(Memory Map )都不一样,但是它们都有相同的分配结构——一个线性的统一编址的16bit (总共64K )寻址空间。

STM32 FLASH模拟EEPROM实验笔记一、根据所选IC确定每页的大小ST系列芯片中,FLASH的大小大于或者等于256k,则每页大小为2k(最多2k大小);FLASH的大小于256k大小,则每页大小为1k.二、在模拟EEPROM中写数据(1)在模拟EEPROM中写数据,有以下几个参数必须具备:写入数据的虚拟地址,写入的数据,写入的数据的数量(注:写入的数据必须每次写入半字)。

(2)在写入数据之前必须判断,要求写入的数据的虚拟地址是否非法(写入的虚拟地址值小于该芯片的FLASH的起始地址或者大于该芯片的FLASH的最大地址值均是视为非法地址)。

(3)解锁FLASH》》》》写入关键字1,关键字2(注:写入关键字就是写入解锁序列,写入的顺序不能乱)。

(4)根据要求写入的数据的虚拟地址计算出实际的偏移地址(相对于FLASH的起始地址),扇区地址,在扇区中的偏移(注意:在扇区内的偏移以2个字节为基本单位),扇区剩余空间大小。

(5)判断要求写入的数据的个数是否不大于该扇区剩余空间的大小,如成立将要求写入的数据的个数赋值给表示空间大小的变量。

(6)进入循环,进行实际的写入数据操作》》》》》》读取该扇区整个扇区的数据--→检验在该扇区中从扇区内的实际偏移开始,一直到扇区剩余空间大小(此时的剩余空间大小值等于要求写入数据的数量),检验这整个区域内是否需要擦除,如果检烟道数据不等于0xFFFF,就需要擦除该扇区的整个扇区----→该扇区擦除前复制到数组中的有效的数据重新写入到该扇区----→写入要求写入的数据到要求写入的虚拟地址中--→判断是否写入结束,如果该扇区不能够则扇区一到一个扇区,写入新扇区的数据数量等于总数量减去写入到上一个扇区的数据数量。

每次写操作完都必须做如次判定,直至要求写入的数据完全写入为止。

写入结束后跳出循环。

(7)上锁FLASH。

注意:在写入和从模拟的EEPROM读出数据都必须是半字读写,所以地址必须每次加2.。

飞思卡尔半导体文件编号:AN3291 应用笔记第1版,03/2007Specifications and information herein are subject to change without notice. ©Freescale Semiconductor,Inc., 2007. All rights reserved.General Business Information如何在M68HC08、HCS08和HCS12微控制器上应用IIC模块作者: Stanislav Arendarik应用工程师捷克共和国,罗斯诺夫1 简介此应用笔记是如何在飞思卡尔的微控制器上应用IIC模块的一个示例。

IIC模块可以分别在主模式或从模式下使用。

在这种情况下,由于IIC 总线主要用于在微控制器(MCU)和IIC外设之间的通信,因此在主模式时与串行EEPROM进行通信。

IIC总线可以在两个微控制器(MCU)之间直接进行通信,然而SPI总线却更适用于这种应用。

此应用笔记总结了通用IIC总线状态和定义,并提供了如何与串行EEPROM进行通信的示例(24C16和24C512)。

您可以轻松地用另外一个IIC器件取代EEPROM,但是必须改变将其标识为从器件的IIC地址字节。

目录1 简介…………… . . . . . . . . . . . . . . . . . . . . . . . .. . . . . . . . . . . . . . . 12 IIC 总线摘要………….. . . . …. . . . . . . . . . . . . . . . . . . . . . . . . . . . 22.1 IIC总线术语.. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22.2 位传输. ………….. . . . . . . . . . . . . . . . . . . . . .. . . . . . . . . . . . 22.3 起始条件和停止条件(START and STOP Conditions)...... . 32.4 总线通信. . ……………………….. . . . . . . . . . . . . . . . . . . . 32.5 控制字节………………………. . . . . . . . . . . . . . . . . . . . .. . . 32.6 地址字节……….... . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42.7 应答………… . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .. . . . 42.8 读/写格式………………………………......…..…... . . . . . . .. 53 用于微控制器的IIC软件程序. ………. . . . . . . . . . . . . . . . . . . . . . . 53.1 IIC的初始化. … . . . …….. . . . . . . . . .. .. . . . .. .. .. . . . . . . . 63.2 写入功能. . . . . . . . . . . . . . . . . . . . . .. . . . . . .. . . . . . . . . . . 73.3 读取功能 .. . . . . . . . . . . . . . . . . . . . .. . .. . . . . .. . . . . . . . . 93.4 中断应用举例. . . . . . ……………. . . . . . . . . . . .. . . . . . . . . 133.4.1 MCU作为主机.. . . . . . . . . . . .. .. . . . . . . . . . . . . . . 133.4.2 MCU作为从机. . . . . . .. . . . . . . .. . . . . . .. . . . . . . 164 结论. . . ……... . . . . . . . . . . . . . . . . . . . . . . . . . . .. . . .. . . . . . . .. . . 17IIC总线摘要2 IIC 总线摘要IIC总线是基于主机和从机间线与(开漏)连接的双向、两线式总线。

68HC08系列单片机片内Flash的在线写入方法

徐洋;程安宇;向敏

【期刊名称】《重庆邮电大学学报(自然科学版)》

【年(卷),期】2005(017)005

【摘要】68HC08系列单片机在运行程序时往往需要保存某些参数使其掉电不丢失,为节约成本提高可靠性,可以将这些参数保存在片内Flash中.片内Flash主要是用来保存用户程序的,为避免在程序运行时往Flash中写入数据所导致的单片机复位,因此采用了调用芯片内部监控ROM中自带的Flash操作子程序的方法.该方法适用于所有68HC08系列片内含Flash芯片的单片机,具有很高的实用性和应用前景.

【总页数】3页(P633-635)

【作者】徐洋;程安宇;向敏

【作者单位】重庆邮电学院,重庆,400065;重庆邮电学院,重庆,400065;重庆邮电学院,重庆,400065

【正文语种】中文

【中图分类】TP368.1

【相关文献】

1.基于 CH376实现 TMS320 LF240 x片内Flash在线编程 [J], 熊金

2.TMS320LF240x系列DSP片内FLASH的在线编程 [J], 李兴建;曹五顺;李琨

3.MC68HC908系列单片机片内FLASH在线编程 [J], 王云飞

4.基于现场总线的MPC5xx系列单片机Flash在线编程技术 [J], 方成;李建秋;周明;欧阳明高

Scope嵌入式仿真开发平台讲座(31) TKScope率先发布AVR增强型Flash 组件支持片内/片外Flash在线编程 [J],

因版权原因,仅展示原文概要,查看原文内容请购买。

OverviewThe MC9S08QG8/4 extends the advantages of FreescaleSemiconductor's HCS08 core to low pin count, small-package 8-bitmicrocontrollers. QG devices are low voltage with on-chip in-circuit Flash memory programmable down to 1.8V,and afford the standard features of all HCS08 MCUs includingwait mode and multiple stop modes.The functionality is completed with strong analog capabilities, a complete set of serial modules, a temperature sensor and robust memory options.Target Applications> Wireless sensor applications including SMAC > Watchdog coprocessors > Small appliances> Handheld devices > Secure boot coprocessors > Security systems 8-bit HCS08 Central Processor Unit (CPU)> Up to 10 MHz (bus frequency) HCS08 CPU (central processor unit) at >2.1V operation for 100 ns minimum instruction time and 8 MHz bus frequency at <2.1V operation> HC08 instruction set with added BGND instruction> Support for up to 32 interrupt/reset sources> Offering high performance, even at low voltage levels for battery-operated applications> Backward object-code compatibility with 68HC08and 68HC05 so existing code libraries can still be used > Allows for efficient, compact module coding in assembly or C compiler> Allows for software flexibility and optimization for real-time applicationsIntegrated Third-Generation Flash Memory and RAM> Provides users a single solution for multiple platforms or a single platform that is field reprogrammable in virtually any environment> Does not require additional pin or power supply for Flash programming, simplifying the interface for in-line programming and allowing for more GPIO pins> Helps reduce production programming costs through ultra-fast programming, as well as lowering system power consumption due to shorter writes> Allows EEPROM emulation, reducing system costs and board real estate> Internal clock source module (ICS) containing a frequency-locked loop (FLL) controlled by internal or external reference > Precision trimming of internal reference allows typical 0.1 percent resolution and +0.5 percent to -1 percent deviation over operating temperature and voltage > Internal reference can be trimmed from 31.25 kHz to 39.065 kHz, allowing for 8 MHz to 10 MHz FLL output> Low-power oscillator module (XOSC) with software selectable crystal or ceramic resonator range, 31.25 kHz to 38.4 kHz or 1MHz to 16 MHz, and supports external clock source input up to 20 MHz Flexible Clock Options> Can eliminate the cost of all external clock components, reduce board space and increase system reliability > Provides one of the most accurate internal clock sources on the market for the money> Can use trimming to adjust bus clocks for optimal serial communication baud rates and/or timer intervals > 32 kHz oscillator provides low power option for systems requiring time-keeping functionality (i.e., time and date) while in low power modes12 Bidirectional Input/Output (I/O) Lines; One Input Only and One Output Only Line> High-current I/O allows direct drive of LED and other circuits to virtually eliminate external drivers and reduce system costs > Reduces customer system cost by eliminating need for external resistors > Can configure ports for slower slew rate and weaker drive to minimize noise emissions from the MCU> Keyboard scan with programmable pull-ups/pull-downs virtually eliminate external glue logic wheninterfacing to simple keypads> Outputs 10 mA each; 60 mA max for package> Software selectable pull-ups on ports when used as input; internal pull-up on RESET and IRQ pin > Software selectable slew rate control and drive strength on ports when used as output> 8-pin keyboard interrupt module with software selectable polarity on edge or edge/level modes > Embedded Flash that is in-application reprogrammable over the full operating voltage and temperature range with a single power supply > Extremely fast, byte-writable programming; as fast as 20 us/byte > Up to 100,000 write/erase cycles at typical voltage and temperature (10k minimum write/erase); 100 years typical data retention (15 years minimum)Learn More: For more information about Freescale products, please visit .Freescale™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners.These products incorporate SuperFlash technology licensed from SST.© Freescale Semiconductor, Inc. 2005MC9S08Q684FS REV 0Cost-Effective Development Tools For more information on development tools,please refer to the Freescale Development Tool Selector Guide (SG1011).DEMO9S08QG8 $50*Cost-effective demonstration board with potentiometer, LEDs, serial port and built-in USB-BDM cable for debugging and programming.M68CYCLONEPRO $99*HC08/HCS08/HC12/HCS12 stand-alone Flash programmer or in-circuit emulator,debugger, Flash programmer; USB, serial or Ethernet interface BMULTILINKBDM $99*Universal HC08 in-circuit debugger and Flash programmer; USB PC interface.CWX-H08-SE Free**CodeWarrior™ Special Edition for HC(S)08MCUs; includes integrated development environment (IDE), linker, debugger,unlimited assembler, Processor Expert™auto-code generator, full-chip simulation and 16 KB C compiler.Data SheetsMC9S08QG8Data Sheet for QG8/QG4Integrated Analog Peripherals> Easy interface to analog inputs, such as sensors > Used to set conversion complete and generate interrupt only when result matches condition> Can be used to run ADC when MCU clocks are off, such as in STOP3 low-power mode> Calculates temperature without any external components and saves an ADC input channel for other use > Constant voltage source for calibrating ADC results requires no external components> Takes periodic measurements without CPU involvement; can be used in STOP3 with compare function to take measurement and wake MCU from STOP3 only when compare level is reached> Flexible configuration to meet high performance and low power requirements> Requires only single pin for input signal> Allows other components in system to see results of comparator with minimal delay> Can be used for single slope ADC and RC time constant measurements> 8-channel, 10-bit analog-to-digital converter (ADC)• Automatic compare function, software programmable for greater than/equal to or less than conditions• Asynchronous clock source • Temperature sensor• Internal bandgap reference channel • Hardware triggerable using the RTI counter• Low-power and high-speed options> Analog comparator module (ACMP)• Option to compare to internal reference• Option to route comparator output directly to pin • Output can be optionally routed to TPM module as input capture triggerTwo Timer Modules> Programmable 16-bit timer/PWM module (TPM)> 8-bit modulo timer module (MTIM) with 8-bit prescalerSystem Protection> Resets device in instance of runaway or corrupted code, and independent clock source provides additional protection in case of loss of clock > Allows system to write/save important variables beforevoltage drops to low> Can hold device in reset until reliable voltage levels are reapplied to the part> Resets device in instance of runaway or corrupted code > Secures code sections so that it cannot be accidentally corrupted by runaway code > Option to protect various block sizes> Option to put bootloader code in protected space and clear Flash for reprogramming> Prevents unauthorized access to memory to protect a customer's valuable software IP> Significantly reduces risk of code runaway due to brownout situations> Watchdog computer operating properly (COP) reset with option to run from dedicated 1 kHz internal clock source or bus clock > Low-voltage detection with reset or interrupt> Illegal opcode detection with reset > Flexible block protection> Security feature for Flash and RAM > Always-on POR circuitry> SCI—serial communications interface module withoption for 13-bit break capabilities and double-buffered transmit and receive> SPI—serial peripheral interface module > I 2C—inter-integrated circuit bus moduleMultiple Serial Communication Options> All serial peripherals available for use in parallel on 16-pin devices> On-chip in-circuit emulation (ICE)Background Debugging System and On-Chip In-Circuit Emulation (ICE) with Real-Time Bus Capture> Provides single wire debugging and emulation interface; eliminates need for expensive emulation tools > Provides circuit emulation without the need for additional, expensive development hardware> One of the most flexible timer modules for the money; each channel can be independently programmable for input capture, output compare or buffered edge-aligned pulse width modulation (PWM) or buffered center-aligned PWM> Timer overflow interrupt can be enabled to generate periodic interrupts for time-based software loops*Prices indicated are MSRP.**Subject to license agreement and registration.Package OptionsPart Number Package Temp. Range MC9S08QG4CPAE 8-pin DIP -40°C to +85°C MC9S08QG4CDNE 8-pin SOIC-NB -40°C to +85°CMC9S08QG4CFQE 8-pin DFN -40°C to +85°C MC9S08QG4CDTE 16-pin TSSOP -40°C to +85°C MC9S08QG4CFFE 16-pin QFN -40°C to +85°C MC9S08QG8CDNE 8-pin SOIC-NB -40°C to +85°CMC9S08QG8CFQE 8-pin DFN -40°C to +85°C MC9S08QG8CPBE 16-pin DIP -40°C to +85°C MC9S08QG8CFFE 16-pin QFN -40°C to +85°C MC9S08QG8CDTE16-pin TSSOP-40°C to +85°CMC9S08QG Family available at -40°C to +125°C in 2H, 2006。

第13章Flash存储器Flash存储器具有电可擦除、无需后备电源来保护数据、可在线编程、存储密度高、低功耗、成本较低等特点,这使得Flash存储器在嵌入式系统中的使用迅速增长。

本章主要以HC08系列中的GP32为例阐述Flash存储器的在线编程方法,也简要阐述了HCS08系列中GB60的在线编程方法。

本章首先概述了Flash存储器的基本特点,并介绍其编程模式,随后给出M68HC908GP32的Flash存储器编程的基本操作及汇编语言和C语言的在线编程实例。

最后讨论MC9S08GB60的Flash存储器编程方法。

Flash存储器编程方法有写入器模式与在线模式两种,本章讨论的是在线模式。

有的芯片内部ROM中,包含了Flash擦除与写入子程序,在本章的进一步讨论中给出了调用方法,使Flash编程相对方便。

有的芯片内部ROM中没有固化Flash擦除与写入子程序,只能自己编写Flash擦除与写入子程序。

而编写Flash擦除与写入子程序需要较严格的规范,所以这是比较细致的工作,读者应仔细分析本章的例程,并参照例程编程。

掌握了GP32芯片的Flash编程方法后,可以把此方法应用于整个系列的Flash编程。

Flash在线编程对初学者有一定难度,希望通过实例分析学习。

本章给出Flash在线编程的C语言实例,对于训练C语言与汇编联合编程技巧很有帮助。

13.1 Flash存储器概述与编程模式理想的存储器应该具备存取速度快、不易失、存储密度高(单位体积存储容量大)、价格低等特点,但一般的存储器只具有这些特点中的一个或几个。

近几年Flash存储器(有的译为:闪速存储器或快擦型存储器)技术趋于成熟,它结合了OTP存储器的成本优势和EEPROM的可再编程性能,是目前比较理想的存储器。

Flash存储器具有电可擦除、无需后备电源来保护数据、可在线编程、存储密度高、低功耗、成本较低等特点。

这些特点使得Flash存储器在嵌入式系统中获得广泛使用。

在HCS08微控制器上使用FLASH存储器模拟EEPROM飞思卡尔半导体北京分公司师英(jerry.shi@)在微控制器应用的很多场合,EEPROM被用来保存要求掉电仍然保持的数据,包括系统配置数据、过程数据、测量或运算结果等。

虽然HCS08系列微控制器并不包含片上EEPROM,然而它所拥有的高性能FLASH存储器可以方便地实现数据存储功能。

在本文中,提供了4个封装好的函数来实现EEPROM的模拟功能,屏蔽了复杂的底层操作,可以很方便地集成到应用程序中去。

HCS08微控制器片上FLASH的性能HCS08的程序存储器为0.25um工艺FLASH,以512bytes为一个页组织。

表1给出了HCS08片上FLASH存储器的大部分特性。

HCS08在150 kHz到200 kHz之间。

假如f FCLK被设置为200 kHz,则编程一个字节的时间为:9 × (1/200 kHz) = 45 us使用突发模式编程,每编程一个字节的时间为:4 × (1/200 kHz) = 20 us而擦除一页的时间为:4000 × (1/200 kHz) = 20 ms全部擦除的时间为:20000× (1/200 kHz) = 100 ms更多擦写周期,100,000次在室温下,HCS08片上FLASH存储器的典型擦写次数为10万次。

在全温度范围内,昀小值为1万次。

另外可以采用数学办法来循环使用FLASH存储器的一个页面,从而成倍扩展FLASH的擦写次数。

内建擦除和编程算法,全工作电压范围内可以工作HCS08微控制器的工作电压有两种,分别是1.8V~3.6V和2.7V~5.5V。

由于采用内部的电荷泵来产生编程电压,绝大部分HCS08微控制器的FLASH存储器都可以在整个工作电压范围之内完成编程和擦除操作。

FLASH存储器的编程和擦除操作都有由内建的算法逻辑完成,用户程序只要向FLASH命令寄存器写入相应的命令即可调用这些算法逻辑。

由于编程电压的打开、关闭以及其时序都由内部算法完成,使得FLASH操作变得更加简单和安全。

灵活的FLASH块保护功能灵活的FLASH块保护功能使得FLASH可以按页被保护,被保护的页不会被误擦除或者误编程。

当应用程序中包含FLASH编程和擦除代码的时候,这种安全性的考虑尤其重要。

以上特点使EEPROM的模拟非常方便和可靠。

FLASH控制和状态寄存器HCS08微控制器用于FLASH的寄存器一共6个。

FLASH Clock Divider Register (FCDIV, 地址0x1820)DIVLD: 分频系数写入标志FCDIV是一个只写一次的寄存器,这一位用来表示自从昀近一次复位后,FCDIV 是否已经被写过。

复位清除该位;向FCDIV第一次写入数据设置该位。

0 – FCDIV从复位后还没有被写过,FLASH的擦除和编程操作被禁止;1 – FCDIV从复位后已经被写过,FLASH的擦除和编程操作被使能。

PRDIV8: FCLK预分频选择0 –输入到FLASH Clock分频器的时钟源为总线频率;1 –输入到FLASH Clock 分频器的时钟源为总线频率的1/8。

DIV: FCLK的分频系数FCLK可以用下面的公式计算:FCLK = bus frequency ÷ (8exp( PRDIV8)×(DIV +1))FLASH Options Register (FOPT和NVOPT,地址0x1821和0xFFBF)复位后,NVOPT的内容被自动复制到FOPT。

其中的4个有效位用于设置FLASH和RAM的安全机制。

KEYEN:后门密钥使能0 –后门密钥禁止;1 –后门密钥机制使能。

如果固件程序向FLASH地址NVBACKKEY~NVBACKKEY7写正确的密钥,则安全机制被暂时关闭,直到下一次复位。

FNORED:中断向量表重定位使能0 –正常中断向量表;1 –中断向量表被重新定位。

SEC[1:0]:安全机制选择这两位用于选择FLASH和RAM的安全机制。

在所有4种可能的取值中,只有1:0禁止安全机制,其它的3种取值都启用安全机制。

FLASH Configuration Register (FCNFG,地址0x1823)KEYACC:使能后门密钥比较0 –向地址NVBACKKEY的写操作被作为编程或者擦除的开始; 1 –向地址NVBACKKEY的写操作被作为比较密钥。

FLASH Protection Register (FPROT和NVPROT,地址0x1824和0xFFBD)FPS:FLASH保护选择当FPDIS为0,FPS的内容为FLASH的昀后一个不受保护的单元的地址的高7位。

FPDIS:FLASH保护禁止0 –由FPS设定的地址以后的页面都被保护,无法进行编程和擦除操作; 1 – FLASH保护未打开。

FLASH Status Register (FSTAT,地址0x1825)FCBEF:FLASH命令缓冲器为空标志0 –命令缓冲器非空,此时不能执行新的命令;1 – FLASH访问错误。

可能的原因有:FDIV没有初始化之前写FLASH,在FCBEF置位(命令缓冲空)前写FLASH,在完成前一个命令前重复写一个FLASH地址,在完成前一个命令前重复写FCMD,在写FLASH地址时写除FCMD之外的其它FLASH控制寄存器,向FCMD写非法的命令编码,在向FCMD写命令之后试图访问(读或写)除FSTAT之外的FLASH控制寄存器,在编程或者擦除命令执行过程中进入休眠模式(命令终止),在MCU被加密时通过背景调试命令写字节编程、突发编程或者页擦除命令,向FCBEF写0以取消未执行完成的命令,等等。

FBLANK:FLASH为空(0xFF)标志0 –完成检查空命令后,此标志表示FLASH单元非空; 1 –完成检查空命令后,此标志表示FLASH单元为空。

FLASH Command Register (FCMD,地址0x1826)FCMD寄存器用来接收FLASH操作命令。

合法的命令定义如表2所列。

FLASH操作流程在5种FLASH操作命令中,全部擦除命令只有调试或者烧录工具才会用到。

检查空命令只在解除加密机制时才能用到。

突发模式字节编程省去了更新目标地址的操作流程,从而可以节省编程时间。

在本文的例程中,暂时没有使用突发模式。

如果需要尽可能减少FLASH编程的时间以节约CPU资源,或者节省电流,则应采用突发编程模式。

图1描述了字节编程和页擦除操作的流程。

图1:FLASH字节编程和页擦除流程需要注意的是,流程中描述的部分操作代码必须在RAM中运行,因为FLASH阵列被加上编程电压后,从中取指是不安全的。

在这个API中,这些代码首先被复制到一个局部变量的数组中,亦即栈中运行。

当编程或擦除程序退出后,栈空间的内容被自动摧毁。

下面3个静态函数仅供API 内部使用:static void flash_byte_prog(unsigned int_addr, unsigned char_data);static void flash_page_erase(unsigned int _addr);static unsigned charflash_byte_read(unsigned int _addr);flash_byte_prog()向FLASH的指定地址写入一个字节的数据;flash_page_erase()擦除指定的一页;而flash_byte_read()读取FLASH指定地址的1字节数据。

EEPROM 模拟的实现在 API 中,使用了 FLASH 的两个单独的页(共 1024字节)来实现 EEPROM 的模拟。

应用程序必须定义需要的 EEPROM 的长度(以字节为单位)EEPROM_DATA_LEN 。

EEPROM 数据被打包为一种简化的定长记录格式,每次写入操作时,首先根据标志 FLAG_CURRENT_PAGE 找出当前页,然后遍历当前页中的已有记录,直到找出下一个空记录地址,向下一个空的地址写入标志 FLAG_RECORD_USED 来标志该 N+1个单元被使用,然后写入 N 字节的用户数据。

读取时,首先找出当前页,顺序遍历当前页中的记录的标志字节,直到找到昀后一个记录,然后读取它的数据空间。

0x55 N 字节数据FLAG_RECORD_USED = 0x55 EEPROM_DATA_LEN = N 图 2:定长记录格式的 EEPROM 数据 写入时,如果当前页面剩余的空间不足写入一个新的记录,则新记录被写入另一页,并且在该页的昀后一个单元写入标志 FLAG_CURRENT_PAGE ,标志该页为当前页。

这样的实现模型交替使用 FALSH 的两页来保存 EEPROM 数据,并且在每一页中,都交替使用几乎所有空间,在保证数据可靠性的同时,也有效地延长了 FLASH 的擦写周期。

此时的擦写周期取决于 EEPROM 数据长度。

模拟 EEPROM 的擦写周期 = ((512 - 1) ÷ (EEPROM_DATA_LEN + 1)) × 100,000 × 2次HCS08_EEPROM_API 函数说明 这个 API 提供给用户 5个接口函数,可以方便地实现EEPROM 的模拟,屏蔽了底层的操作,并且适用于所有 HCS08系列微控制器。

在使用这些函数之前,必须定义一些宏。

预定义• EEPROM_DATA_LEN- 6 - 2006年 10月 10日 Reversion 0.10x55 N 字节数据 0x55 N 字节数据 0x55N 字节数据每页 X 个记录……0x55N 字节数据剩余的字节单元0xAAFLAG_RECORD_USED = 0x55 FLAG_CURRENT_PAGE = 0xAA EEPROM_DATA_LEN = N PAGE_REUSE_TIMES = X图 2:重复使用一页中的空间使用的EEPROM的大小。

昀大为510字节。

但是当此值比较小时,程序占用的资源比较经济,因为在进行模拟的EEPROM读、写和更新操作时,都占用了以该值为大小的栈空间。

因此也要仔细分配工程的栈空间大小,在工程的链接器参数PRM文件中指定适当的STACKSIZE。

•HCS08_FLASH_START_ADDR定义为控制器的片上FLASH的起始地址。

每个不同的微控制器该值可能不同。

模拟的EEPROM 的空间被分配在FLASH空间的头两页中。

在PRM文件中可以找到这个地址。

注意,在PRM 文件中,ROM的分配空间也要做相应修改,使其起始地址为原来值+1024。

•HCS08_FLASH_PAGE_SIZE FLASH页面大小。