CCS6.0 Graph display set 显示波形设置实例

- 格式:doc

- 大小:742.00 KB

- 文档页数:10

开发一个波形显示程序一. 开发目标及软件功能开发一个波形显示程序,要求采用基于对话框模式的应用程序,能够将一个正弦波形以静态和动态两种模式显示出来,同时波形曲线的参数能够进行调节。

(1)了解图片控件(Picture)和滑动条(Slider)等控件的编程方法。

(2)了解内存绘图和屏幕显示的一般方法。

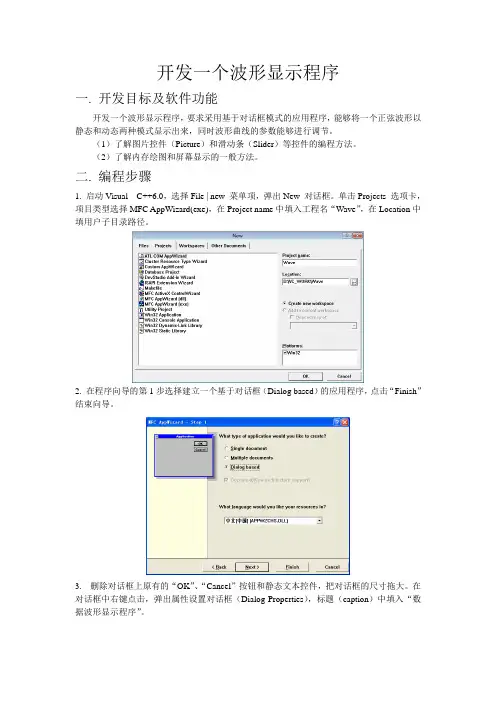

二. 编程步骤1. 启动Visual C++6.0,选择File | new 菜单项,弹出New 对话框。

单击Projects 选项卡,项目类型选择MFC AppWizard(exe),在Project name中填入工程名“Wave”,在Location中填用户子目录路径。

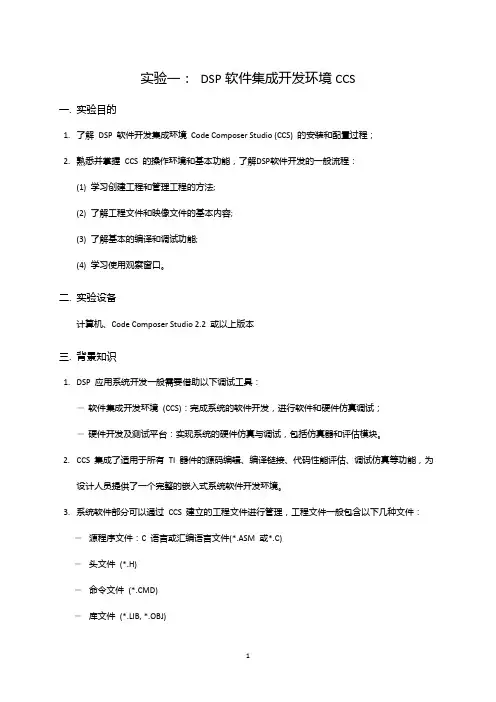

2. 在程序向导的第1步选择建立一个基于对话框(Dialog based)的应用程序,点击“Finish”结束向导。

3. 删除对话框上原有的“OK”、“Cancel”按钮和静态文本控件,把对话框的尺寸拖大。

在对话框中右键点击,弹出属性设置对话框(Dialog Properties),标题(caption)中填入“数据波形显示程序”。

4. 将左侧工作区切换到ResourceView,在Dialog上右键点击,选择“Insert Dialog”,插入一个对话框资源,这个对话框将来作为波形曲线的显示窗口。

在对话框上右键点击,弹出属性对话框,设定其ID号为IDD_W A VE_DISPLAY,设定其标题Caption为“波形显示”。

然后在对话框上添加控件如下图所示,为每一个控件指定ID号。

控件类型ID号Caption 其它Picture IDC_COORDRadio IDC_LEVEL1 0.25V选中group属性Radio IDC_LEVEL2 0.5VRadio IDC_LEVEL3 1.0VRadio IDC_LEVEL4 2.0VRadio IDC_TIME1 0.5选中group属性Radio IDC_TIME2 1Radio IDC_TIME3 2Radio IDC_TIME4 4Slider IDC_SLIDER_HSlider IDC_SLIDER_V 属性“Styles”中,方向选为“Vertical”Button IDC_BTN_STA TIC 静态波形5. 为对话框添加一个类:在对话框的空白区域处双击鼠标,弹出ClassWizard窗口,在添加一个新类对话框中点击OK按钮,将新类命名为CWaveDisplay,其余选择默认值,点击OK 按钮确定。

实验一:DSP软件集成开发环境CCS一. 实验目的1.了解DSP 软件开发集成环境Code Composer Studio (CCS) 的安装和配置过程;2.熟悉并掌握CCS 的操作环境和基本功能,了解DSP软件开发的一般流程:(1) 学习创建工程和管理工程的方法;(2) 了解工程文件和映像文件的基本内容;(3) 了解基本的编译和调试功能;(4) 学习使用观察窗口。

二. 实验设备计算机、Code Composer Studio 2.2 或以上版本三. 背景知识1.DSP 应用系统开发一般需要借助以下调试工具:―软件集成开发环境(CCS):完成系统的软件开发,进行软件和硬件仿真调试;―硬件开发及测试平台:实现系统的硬件仿真与调试,包括仿真器和评估模块。

S 集成了适用于所有TI 器件的源码编辑、编译链接、代码性能评估、调试仿真等功能,为设计人员提供了一个完整的嵌入式系统软件开发环境。

3.系统软件部分可以通过CCS 建立的工程文件进行管理,工程文件一般包含以下几种文件:―源程序文件:C 语言或汇编语言文件(*.ASM 或*.C)―头文件(*.H)―命令文件(*.CMD)―库文件(*.LIB, *.OBJ)四. 实验步骤1.创建工程文件双击CCStudio 图标,启动CCS,CCS 的初始界面包括工程管理区和工作区两部分。

在菜单中选择“Project—>New…”,弹出“Project Create”窗口:若标题栏显示xxxx Emulator,则需要先运行Setup CCS,选择合适的软件仿真环境在“Project”编辑框内填入项目名称,例如“hello1”;有必要的话,可以更改项目文件夹位置(Location);“Project”下拉框用以确定输出文件类型;目标硬件类型在“Target”下拉框中指定。

点击“完成”后,CCS 自动在指定目录下生成“hello1.pjt”工程文件。

工程文件中保存了对应工程的设置信息和内部文件的引用情况。

CCS Graph观察变量的方法

2812使用CCS Graph观察变量时,首先要将所需要观察的变量放在一个长度一定的数组里面,一般情况下我们设数组的长度至少能够放下一个周期的长度,便于观察波形。

例如我们现在要观察Sine和Cosin的波形,由于这两个变量的一个周期为256个数据,因此我们可以设两个长度为256的浮点型数组:

float32 Temp0[256],Temp1[256];//用于CCS Graph观察变量用到的数组

并把上面的程序变为:

即把Sine和Cosin分别赋给数组Temp0[256],Temp1[256],下面我们就可以使用CCS Graph 观察变量Sine和Cosin的波形了:

打开Graph:

作如下设置:

点击OK,这会出现下图:

设置上上一个图中的Graph Title项修改虚拟示波器的名称:Graph Title :Sine和Cosin的波形

则上图变为(看到图形左上角的名称了吧):

看其他的参数,都是一样的方法。

如下图:

文件夹中有一个2812的测试程序,可以用于CCS Graph观察变量测试。

如有错误或者修改的地方,或者疑问,请联系作者QQ:546847771

主要讲解技术,非诚勿扰!。

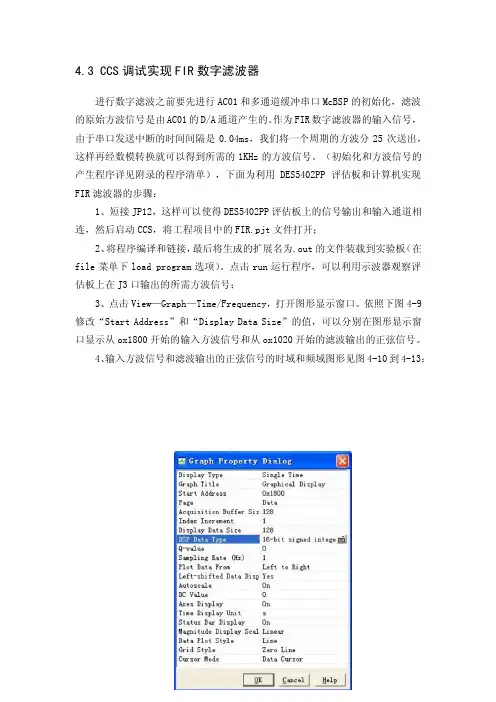

4.3 CCS调试实现FIR数字滤波器进行数字滤波之前要先进行AC01和多通道缓冲串口McBSP的初始化,滤波的原始方波信号是由AC01的D/A通道产生的。

作为FIR数字滤波器的输入信号,由于串口发送中断的时间间隔是0.04ms,我们将一个周期的方波分25次送出,这样再经数模转换就可以得到所需的1KHz的方波信号。

(初始化和方波信号的产生程序详见附录的程序清单),下面为利用DES5402PP评估板和计算机实现FIR滤波器的步骤:1、短接JP12,这样可以使得DES5402PP评估板上的信号输出和输入通道相连,然后启动CCS,将工程项目中的FIR.pjt文件打开;2、将程序编译和链接,最后将生成的扩展名为.out的文件装载到实验板(在file菜单下load program选项)。

点击run运行程序,可以利用示波器观察评估板上在J3口输出的所需方波信号;3、点击View—Graph—Time/Frequency,打开图形显示窗口。

依照下图4-9修改“Start Address”和“Display Data Size”的值,可以分别在图形显示窗口显示从ox1800开始的输入方波信号和从ox1020开始的滤波输出的正弦信号。

4、输入方波信号和滤波输出的正弦信号的时域和频域图形见图4-10到4-13:图4-11 滤波输出的时域波形图4-12 滤波输入的频域波形图4-13 滤波输出的频域波形结论本课题研究的主要任务是以DES5402PP评估板上的TMS320C5402芯片为核心,以话带模数接口电路AC01作为模拟信号的接口,提供一个模数和数模通道,然后通过合理初始化多通道缓冲串口、AC01以及合理的编写串口的中断服务程序,利用汇编语言来实现基于DSP的FIR低通滤波器设计。

在设计的过程中所做的主要工作包括以下一个方面:1、利用信号与系统中的知识了解滤波的工作原理和实现方法,确定FIR数字滤波器的设计方案,利用Matlab辅助软件自行设计符合要求的FIR数字低通滤波器的系数,通过响应串口中断的方法产生滤波输入所需的方波信号;2、FIR数字低通滤波器整体结构设计:了解TMS320C54X的硬件结构和主要的引脚功能,掌握实现FIR数字滤波的系统硬件电路结构(其中包括复位电路、电源电路、时钟电路、AC01以及片外存储器电路的设计);3、FIR数字滤波器的软件实现:包括实现FIR数字滤波器程序的设计和开发过程,使用集成开发环境CCS调试程序以及显示滤波器输入和输出的时域和频域波形。

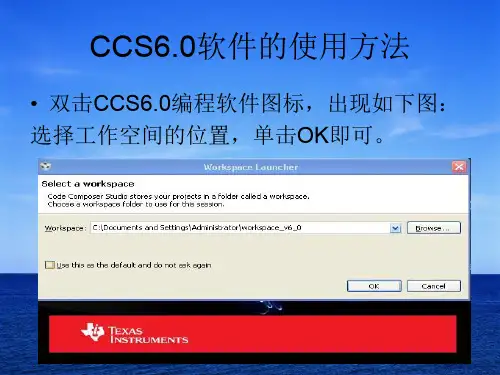

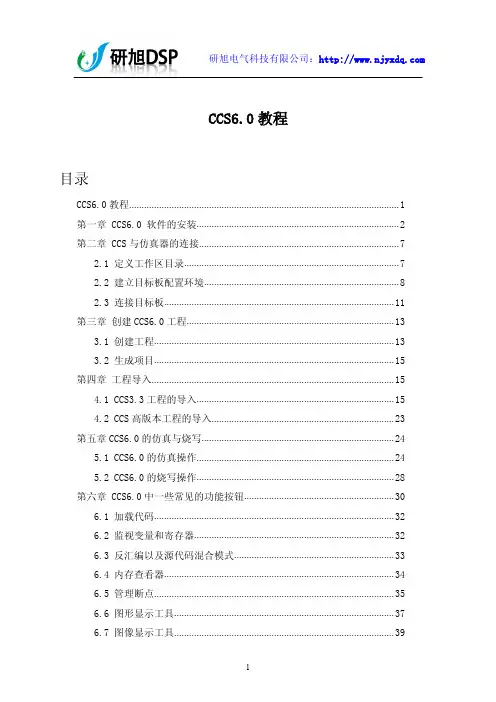

CCS6.0教程目录CCS6.0教程 (1)第一章CCS6.0软件的安装 (2)第二章CCS与仿真器的连接 (7)2.1定义工作区目录 (7)2.2建立目标板配置环境 (8)2.3连接目标板 (11)第三章创建CCS6.0工程 (13)3.1创建工程 (13)3.2生成项目 (15)第四章工程导入 (15)4.1CCS3.3工程的导入 (15)4.2CCS高版本工程的导入 (23)第五章CCS6.0的仿真与烧写 (24)5.1CCS6.0的仿真操作 (24)5.2CCS6.0的烧写操作 (28)第六章CCS6.0中一些常见的功能按钮 (30)6.1加载代码 (32)6.2监视变量和寄存器 (32)6.3反汇编以及源代码混合模式 (33)6.4内存查看器 (34)6.5管理断点 (35)6.6图形显示工具 (37)6.7图像显示工具 (39)第一章CCS6.0软件的安装首先我们需要来安装TI DSP的软件开发环境CCS(Code Composer Studio)。

如果您曾经使用过其他公司的仿真器产品。

我们推荐使用CCS6.0版本,因为暂时合众达公司的XDS510PLUS和XDS560PLUS仿真器只支持CCS6.0,再高版本兼容性不是很好。

另外我们选用XDS100V2仿真器也只能适用于CCS4.0及以上版本的开发环境,XDS100V3仿真器只适用于CCS5.0及以上版本的开发环境。

注意:安装前先关闭杀毒软件和360、电脑管家等安全防护软件,否则点击安装程序会出现警告,强行安装会出现文件丢失。

双击ccs_setup_6.0.0.00190.exe文件,出现如下图1-1所示界面:图1-1选择“I accept the terms of the license agreement”,点击“Next”如下图1-2所示:图1-2点击“Browse”选择安装路径(注意:路径不可以有中文),但推荐默认路径,点击“Next”见下图1-3所示:图1-3根据自己的需求选择索要安装的内容,这里选择“Select All”,然后点击“Next”见下图1-4所示:图1-4依旧根据自己的需求选择仿真设备驱动类型,这里选择“Select All”,然后点击“Next”见下图1-5所示:图1-5根据自己的需求选择,这里全不选,然后点击“Finish”。

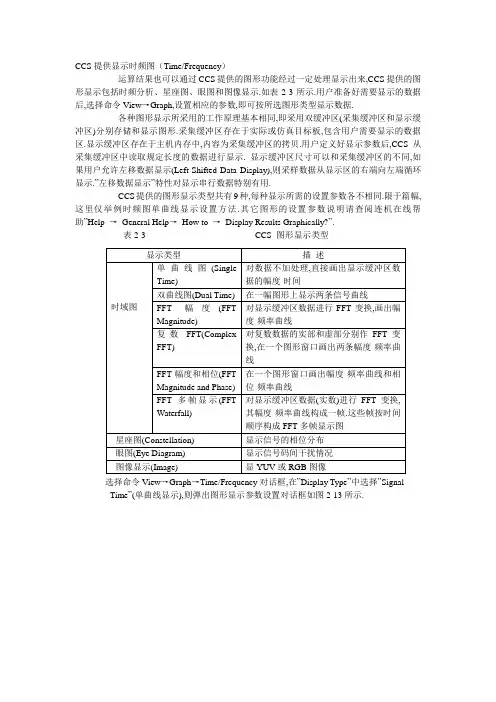

CCS提供显示时频图(Time/Frequency)运算结果也可以通过CCS提供的图形功能经过一定处理显示出来,CCS提供的图形显示包括时频分析、星座图、眼图和图像显示.如表2-3所示.用户准备好需要显示的数据后,选择命令View→Graph,设置相应的参数,即可按所选图形类型显示数据.各种图形显示所采用的工作原理基本相同,即采用双缓冲区(采集缓冲区和显示缓冲区)分别存储和显示图形.采集缓冲区存在于实际或仿真目标板,包含用户需要显示的数据区.显示缓冲区存在于主机内存中,内容为采集缓冲区的拷贝.用户定义好显示参数后,CCS从采集缓冲区中读取规定长度的数据进行显示. 显示缓冲区尺寸可以和采集缓冲区的不同,如果用户允许左移数据显示(Left-Shifted Data Display),则采样数据从显示区的右端向左端循环显示.”左移数据显示”特性对显示串行数据特别有用.CCS提供的图形显示类型共有9种,每种显示所需的设置参数各不相同.限于篇幅,这里仅举例时频图单曲线显示设置方法.其它图形的设置参数说明请查阅连机在线帮助”Help →General Help→How to →Display Results Graphically?”.表2-3 CCS 图形显示类型选择命令View→Graph→Time/Frequency对话框,在”Display Type”中选择”SignalTime”(单曲线显示),则弹出图形显示参数设置对话框如图2-13所示.图2-13 单曲线显示属性设置参数需要设置的参数解释如下:(1)显示类型(Display Type)单击” Display Type ”栏区域,则出现显示类型下拉菜单,内容如表2-3所示.点击所需的显示类型,则Time/Frequency 对话框(参数设置)相应随之变化.(2)视图标题(Grph Title):定义图形视图标题.(3)起始地址(Start Address)定义采样缓冲区的起始地址.当图形被更新时,采样缓冲区内容亦更新显示缓冲区内容.此对话栏允许输入符号和C 表达式.当显示类型为”Dual Time ”时,需要输入两个采样缓冲区首地址.(4)数据页(Data Page):指明选择的采样缓冲区来自程序、数据还是I/O 空间.(5)采用缓冲区尺寸(Acquisition Buffer Size)用户可以根据所需定义采样缓冲区的尺寸.例如当一次显示一帧数据时,则缓冲区尺寸为帧的大小.若用户希望观察串行数据,则定义缓冲区尺寸为1,同时允许左移数据显示.(6)索引递增(Index Increment)定义在显示缓冲区中每隔几个数据取一个采样点.(7)显示数据尺寸(Display Data Size)此参数用来定义显示缓冲区大小.一般地,显示缓冲区的尺寸取决于”显示类型”选项.对时域图形,显示缓冲区尺寸等于要显示的采样点数目,并且大于等于采样缓冲区尺寸.若显示缓冲区尺寸大于采样缓冲区尺寸,则采样数据可以左移到显示缓存显示.对频域图形,显示缓冲区尺寸等于FF帧尺寸,取整为2的幂次.(8)DSP数据类型(DSP Data Type)DSP数据类型可以为:·32比特有符号整数;·32比特元符号整数;·32比特浮点数;·32比特IEEE浮点数;·16比特有符号整数;·16比特无符号整数;·8比特有符号整数;·8比特无符号整数.(9)Q值(Q-Value)采样缓冲区中的数始终为16进制数,但是它表示的实际数取值范围由Q值确定.Q 值为定点数定标值,指明小数点所在的位置.Q值取值范围为0~15,假定Q值为xx,则小数点所在的位置为从最低有效位向左数的xx位.(10)采样频率(Sampling Rate(Hz))对时域图形,此参数指明在每个采样时刻定义对同一数据的采样数.假定采样频率为xx,则一个采样数据对应xx个显示缓冲区单元.由于显示缓冲区尺寸固定,因此时间轴取值范围为0~(显示缓冲区尺寸/采样频率).对时域图形, 此参数定义频率分析的样点数.频率范围为0~采样率/2.(11)数据绘出顺序(Plot Data From)此参数定义从采样缓冲区取数的顺序:·从左到右:采样缓冲区的第一个数被认为是最新或最近到来数据;·从右到左: 采样缓冲区的第一个数被认为是最旧数据.(12)左移数据显示(Left-Shifted Data Display)此选项确定采样缓冲区与显示缓冲区的哪一边对齐.用户可以选择此特性允许或禁止.若允许,则采样数据从右端填入显示缓冲区.每更新一次图形,则显示缓存数据左移,留出空间填入新的采样数据.注意显示缓冲区初始化为0.若此特性被禁止,则采样数据简单覆盖显示缓存.(13)自动定标(Autoscale)此选项允许Y轴最大值自动调整.若此选项设置为允许,则视图被显示缓冲区数据最大值归一化显示.若此选项设置为禁止,则对话框中出现一新的设置项”Maximum Y-Value”,设置Y轴显示最大值.(14)直流量(DC V alue)此参数设置Y轴中点的值,即零点对应的数值.对FFT幅值显示,此区域不显示.(15)坐标显示(Axes Display)此选项设置X,Y坐标轴是否显示.(16)时间显示单位(Time Display Unit)定义时间轴单位.可以为秒(s),毫秒(ms),微秒(μs)或采样点.(17)状态条显示(Status Bar Display)此选项设置图形窗口的状态条是否显示.(18)幅度显示比例(Magnitude Display Scale)有两类幅度显示类型:线性或对数显示(公式为20log(X)).(19)数据标绘风格(Data Plot Style)此选项设置数据如何显示在图形窗口中.·Line:数据点之间用直线相连;·Bar:每个数据点用竖直线显示.(20)栅格类型(Grid Style)此选项设置水平或垂直方向底线显示.有三个选项:·No Grid:无栅格;·Zero Line:仅显示0轴;·Full Grid:显示水平和垂直栅格.(21)光标模式(Cursor Mode)此选项设置光标显示类型.有3个选项:·No Cursor:无光标;·Data Cursor:在视图状态栏显示数据和光标坐标;·Zoom Cursor:允许放大显示图形.方法:按住鼠标左键,拖动,则定义的矩形框被放大.图2-14为一正弦波数据显示图的例子.。

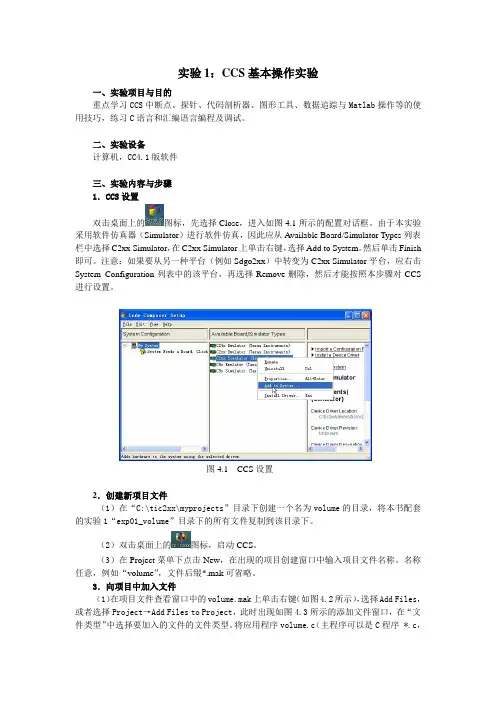

实验1:CCS基本操作实验一、实验项目与目的重点学习CCS中断点、探针、代码剖析器、图形工具、数据追踪与Matlab操作等的使用技巧,练习C语言和汇编语言编程及调试。

二、实验设备计算机,CC4.1版软件三、实验内容与步骤1.CCS设置双击桌面上的图标,先选择Close,进入如图4.1所示的配置对话框。

由于本实验采用软件仿真器(Simulator)进行软件仿真,因此应从Available Board/Simulator Types列表栏中选择C2xx Simulator,在C2xx Simulator上单击右键,选择Add to System。

然后单击Finish 即可。

注意:如果要从另一种平台(例如Sdgo2xx)中转变为C2xx Simulator平台,应右击System Configuration列表中的该平台,再选择Remove删除,然后才能按照本步骤对CCS 进行设置。

图4.1 CCS设置2.创建新项目文件(1)在“C:\tic2xx\myprojects”目录下创建一个名为volume的目录,将本书配套的实验1“exp01_volume”目录下的所有文件复制到该目录下。

(2)双击桌面上的图标,启动CCS。

(3)在Project菜单下点击New,在出现的项目创建窗口中输入项目文件名称。

名称任意,例如“volume”,文件后缀*.mak可省略。

3.向项目中加入文件(1)在项目文件查看窗口中的volume.mak上单击右键(如图4.2所示),选择Add Files,或者选择Project→Add Files to Project,此时出现如图4.3所示的添加文件窗口,在“文件类型”中选择要加入的文件的文件类型。

将应用程序volume.c(主程序可以是C程序 *.c,也可以是汇编程序 *.asm)、命令链接文件 *.cmd(volume.cmd)等分别加入。

如果需要用到中断向量,加入中断向量文件vectors.asm;如果用到了C程序,还需加入实时运行支持库文件rts2xx.lib。

目录1 绪论1.1 课题背景1.2 波形显示控件实现的功能2 主要开发技术介绍2.1 .NET用户控件介绍2.2 GDI+技术介绍3 波形显示控件整体设计3.1 数据存储结构的设计3.2 控件界面模块的设计3.3 控件工作流程的设计4 波形显示控件各细节的实现4.1 坐标值和标尺的实现4.1.1 坐标相关的成员变量4.1.2 坐标标定权值的概念4.1.3 坐标标尺的绘制4.1.4 子标尺线的选择性显示4.2 数据点的描绘4.2.1 数据值转换为坐标值4.2.2 溢出坐标范围的数据点的处理4.2.3 遍历所有数据线并绘制出4.3 波形显示区域网格的实现4.3.1 网格相关的成员变量4.3.2 网格的绘制4.4 工具栏按钮的实现4.4.1 工具栏按钮相互关系4.4.2 工具栏提示标签的实现4.5 波形放大功能的实现4.5.1 局部放大选择框的实现4.5.2 放大选择框的鼠标操作4.5.3 放大选择框的按钮操作4.5.4 更新数据显示范围为放大的范围4.6 坐标自动调整及恢复默认坐标的实现4.6.1 坐标自动调整功能4.6.2 恢复默认坐标范围功能4.7 波形显示控件接口的实现4.7.1 控件基本属性4.7.2 控件外观样式4.7.3 控件绘图接口4.8 波形显示控件其他细节的处理4.8.1 坐标值产生遮盖时的处理4.8.2 波形显示控件大小改变时的处理4.8.3 按钮点击时进行禁用操作4.8.4 右键菜单的显示4.8.5 XML注释以及智能提示5 波形显示控件功能的演示和使用5.1 波形显示控件演示程序的设计5.2 波形显示控件功能的演示5.2.1 外观样式的更改5.2.2 波形显示演示5.2.3 波形显示控件在实际项目中的使用6 课题总结参考文献1 绪论1.1 课题背景波形显示控件广泛见于监控测量,图像数据显示等自动化相关软件中,更是组态软件必不可少的一部分。

例如美国国家仪器有限公司(National Instruments)的NI Measurement Studio 集成式套件以及LabView图形化程序开发环境等,都包含技术成熟的波形显示控件,功能丰富且强大。

CCS 提供显示时频图(Time/Frequency运算结果也可以通过CCS 提供的图形功能经过一定处理显示出来,CCS 提供的图形显示包括时频分析、星座图、眼图和图像显示.如表2-3所示.用户准备好需要显示的数据后,选择命令View →Graph,设置相应的参数,即可按所选图形类型显示数据.各种图形显示所采用的工作原理基本相同,即采用双缓冲区(采集缓冲区和显示缓冲区分别存储和显示图形.采集缓冲区存在于实际或仿真目标板,包含用户需要显示的数据区.显示缓冲区存在于主机内存中,内容为采集缓冲区的拷贝.用户定义好显示参数后,CCS 从采集缓冲区中读取规定长度的数据进行显示. 显示缓冲区尺寸可以和采集缓冲区的不同,如果用户允许左移数据显示(Left-Shifted Data Display,则采样数据从显示区的右端向左端循环显示.”左移数据显示”特性对显示串行数据特别有用.CCS 提供的图形显示类型共有9种,每种显示所需的设置参数各不相同.限于篇幅,这里仅举例时频图单曲线显示设置方法.其它图形的设置参数说明请查阅连机在线帮助”Help → General Help → How to → Display Results Graphically?”. 表2-3 CCS 图形显示类型选择命令View →Graph →Time/Frequency 对话框,在”Display Type”中选择”SignalTime”(单曲线显示,则弹出图形显示参数设置对话框如图2-13所示.显示类型描述单曲线图(Single Time 对数据不加处理,直接画出显示缓冲区数据的幅度-时间双曲线图(Dual Time在一幅图形上显示两条信号曲线 FFT 幅度(FFT Magnitude 对显示缓冲区数据进行FFT 变换,画出幅度-频率曲线复数FFT(Complex FFT 对复数数据的实部和虚部分别作FFT 变换,在一个图形窗口画出两条幅度-频率曲线 FFT 幅度和相位(FFT Magnitude and Phase在一个图形窗口画出幅度-频率曲线和相位-频率曲线时域图 FFT 多帧显示(FFT Waterfall 对显示缓冲区数据(实数进行FFT 变换,其幅度-频率曲线构成一帧.这些帧按时间顺序构成FFT 多帧显示图星座图(Constellation显示信号的相位分布眼图(Eye Diagram显示信号码间干扰情况图像显示(Image显YUV 或RGB 图像图2-13 单曲线显示属性设置参数需要设置的参数解释如下:(1显示类型(Display Type单击” Display Type”栏区域,则出现显示类型下拉菜单,内容如表2-3所示.点击所需的显示类型,则Time/Frequency对话框(参数设置相应随之变化.(2视图标题(Grph Title:定义图形视图标题.(3起始地址(Start AddressA:当监控的为数组时,一般我们用数组来存变量的值,也就是自己做了个变量的缓冲区,缓冲区的长度即为数组的长度,变量的值先存到数组形式的缓冲区中。

今天早上花了半天的时间,帮一个朋友调试出了波形图,自己以前弄过,后来忘记了,在此记录下来,方便以后的查阅。

也给不会的同学做使用方法上一个参考。

调出波形图,有以下几个步骤:1)View -> Graph -> Time/Frequency。

完成这几步之后,就会出来一个表格,如果什么都不填写,能看进一个基本的坐标图。

2)要明确自己需要的图是什么图,输出关于时间变量的图还是关于频率变量的图,如果不明白这两个的意思,好,那就做一个简单的说明吧。

我们一般在示波器上看见的图就是时间图,那什么是频率图呢?比方说,我们需要看一个频率为5HZ的正弦信号,那么看到的正弦波是时间图,频率图就是在横坐标等于5的地方有一个竖线,表示只有频率等于5HZ的时候有值,其他的频率都没有值。

如果你明白什么是FFT的话就更好理解了。

好了开始修改各个参数了。

明确自己要看的是什么图了之后,在第一栏Display Type中选择,Single Time就是时间图,FFT Magnitude 就是频率图,还有一些其他的选型,可以自己去理解一下,比方说眼图Eye Diagram。

根据需要查看。

3)Graph Title,是修改图的名称的,比方说你画了好几个时间图,你怎么知道哪一幅图是哪一个呢?就在这个时候用名字分开吧。

4)Start Address,是填写你的输入地址的,可以写输入的名字,也可以写地址,一般情况都是写名字的,比方说很多时候会用INPUT来命名输入信号,大家都不太关心编译之后生成出来存储块地址。

5)DSP Data Type,这个是填写数据类型的,不然的话是出不来图形的,如果你不知道的话,那肯定不是自己写的程序,对于别人的程序就好好好的研读一番了,看一下数据类型。

6)把这几个主要的改好了之后,基本上就没有什么问题了。

选择OK后,就退出了表格填写部分。

然后在程序中将断点打在输出的语句上,运行,当程序运行到这里的时候,就会有波形图出来了。

CCS6.0Graphdisplayset显⽰波形设置实例CCS6.0显⽰AD波形利⽤CCS6.0 实时显⽰两路AD转换结果,⽤波形的显⽰的设置步骤如下:1、打开CCS6.0, 打开AD⼯程,如图:程序如下:#include "myapp.h"#include "csedu.h"#include "scancode.h"void InitADC();void wait( unsigned int cycles );void EnableAPLL( );unsigned int nADC0[256],nADC1[256];main(){int i;unsigned int uWork;EnableAPLL();SDRAM_init();InitADC();PLL_Init(132);while ( 1 ){for ( i=0;i<256;i++ ){ADCCTL=0x8000; // 启动AD转换,通道0do{uWork=ADCDATA;} while ( uWork&0x8000 );nADC0=uWork&0x0fff;}for ( i=0;i<256;i++ ){ADCCTL=0x9000; // 启动AD转换,通道1do{uWork=ADCDATA;} while ( uWork&0x8000 );nADC1=uWork&0x0fff;}asm( " nop"); // break point}}void InitADC(){ADCCLKCTL=0x23; // 4MHz ADCLKADCCLKDIV=0x4f00;}void wait( unsigned int cycles ){int i;for ( i = 0 ; i < cycles ; i++ ){ }}void EnableAPLL( ){*( ioport volatile unsigned short* )0x1f00 = 4; wait( 25 );*( ioport volatile unsigned short* )0x1f00 = 0;// MULITPLY*( ioport volatile unsigned short* )0x1f00 = 0x3000;// COUNT*( ioport volatile unsigned short* )0x1f00 |= 0x4F8; wait( 25 );//*( ioport volatile unsigned short* )0x1f00 |= 0x800 // MODE*( ioport volatile unsigned short* )0x1f00 |= 2; wait( 30000 ); // APLL Select *( ioport volatile unsigned short* )0x1e80 = 1; // DELAYwait( 60000 );}2、点击菜单project->build all,编译,如图,没错误。

CCS中的graph详细使用说明(2009-04-28 08:04:16)转载▼分类:DSP标签:itCCS提供显示时频图(Time/Frequency)运算结果也可以通过CCS提供的图形功能经过一定处理显示出来,CCS提供的图形显示包括时频分析、星座图、眼图和图像显示.如表2-3所示.用户准备好需要显示的数据后,选择命令View→Graph,设置相应的参数,即可按所选图形类型显示数据.各种图形显示所采用的工作原理基本相同,即采用双缓冲区(采集缓冲区和显示缓冲区)分别存储和显示图形.采集缓冲区存在于实际或仿真目标板,包含用户需要显示的数据区.显示缓冲区存在于主机内存中,内容为采集缓冲区的拷贝.用户定义好显示参数后,CCS从采集缓冲区中读取规定长度的数据进行显示. 显示缓冲区尺寸可以和采集缓冲区的不同,如果用户允许左移数据显示(Left-Shifted Data Display),则采样数据从显示区的右端向左端循环显示.”左移数据显示”特性对显示串行数据特别有用.CCS提供的图形显示类型共有9种,每种显示所需的设置参数各不相同.限于篇幅,这里仅举例时频图单曲线显示设置方法.其它图形的设置参数说明请查阅连机在线帮助”Help → General Help→ How to → Display Results Graphically?”.表2-3 CCS 图形显示类型选择命令View→Graph→Time/Frequency对话框,在”Display Type”中选择”SignalTime”(单曲线显示),则弹出图形显示参数设置对话框如图2-13所示.图2-13 单曲线显示属性设置参数需要设置的参数解释如下:(1)显示类型(Display Type)单击” Display Type”栏区域,则出现显示类型下拉菜单,内容如表2-3所示.点击所需的显示类型,则Time/Frequency对话框(参数设置)相应随之变化.(2)视图标题(Grph Title):定义图形视图标题.(3)起始地址(Start Address)定义采样缓冲区的起始地址.当图形被更新时,采样缓冲区内容亦更新显示缓冲区内容.此对话栏允许输入符号和C表达式.当显示类型为”Dual Time”时,需要输入两个采样缓冲区首地址.(4)数据页(Data Page):指明选择的采样缓冲区来自程序、数据还是I/O空间.(5)采用缓冲区尺寸(Acquisition Buffer Size)用户可以根据所需定义采样缓冲区的尺寸.例如当一次显示一帧数据时,则缓冲区尺寸为帧的大小.若用户希望观察串行数据,则定义缓冲区尺寸为1,同时允许左移数据显示.(6)索引递增(Index Increment)定义在显示缓冲区中每隔几个数据取一个采样点.(7)显示数据尺寸(Display Data Size)此参数用来定义显示缓冲区大小.一般地,显示缓冲区的尺寸取决于”显示类型”选项.对时域图形,显示缓冲区尺寸等于要显示的采样点数目,并且大于等于采样缓冲区尺寸.若显示缓冲区尺寸大于采样缓冲区尺寸,则采样数据可以左移到显示缓存显示.对频域图形,显示缓冲区尺寸等于FF帧尺寸,取整为2的幂次.(8)DSP数据类型(DSP Data Type)DSP数据类型可以为:·32比特有符号整数;·32比特元符号整数;·32比特浮点数;·32比特IEEE浮点数;·16比特有符号整数;·16比特无符号整数;·8比特有符号整数;·8比特无符号整数.(9)Q值(Q-Value)采样缓冲区中的数始终为16进制数,但是它表示的实际数取值范围由Q值确定.Q值为定点数定标值,指明小数点所在的位置.Q值取值范围为0~15,假定Q 值为xx,则小数点所在的位置为从最低有效位向左数的xx位.(10)采样频率(Sampling Rate(Hz))对时域图形,此参数指明在每个采样时刻定义对同一数据的采样数.假定采样频率为xx,则一个采样数据对应xx个显示缓冲区单元.由于显示缓冲区尺寸固定,因此时间轴取值范围为0~(显示缓冲区尺寸/采样频率).对时域图形, 此参数定义频率分析的样点数.频率范围为0~采样率/2.(11)数据绘出顺序(Plot Data From)此参数定义从采样缓冲区取数的顺序:·从左到右:采样缓冲区的第一个数被认为是最新或最近到来数据;·从右到左: 采样缓冲区的第一个数被认为是最旧数据.(12)左移数据显示(Left-Shifted Data Display)此选项确定采样缓冲区与显示缓冲区的哪一边对齐.用户可以选择此特性允许或禁止.若允许,则采样数据从右端填入显示缓冲区.每更新一次图形,则显示缓存数据左移,留出空间填入新的采样数据.注意显示缓冲区初始化为0.若此特性被禁止,则采样数据简单覆盖显示缓存.(13)自动定标(Autoscale)此选项允许Y轴最大值自动调整.若此选项设置为允许,则视图被显示缓冲区数据最大值归一化显示.若此选项设置为禁止,则对话框中出现一新的设置项”Maximum Y-Value”,设置Y轴显示最大值.(14)直流量(DC Value)此参数设置Y轴中点的值,即零点对应的数值.对FFT幅值显示,此区域不显示.(15)坐标显示(Axes Display)此选项设置X,Y坐标轴是否显示.(16)时间显示单位(Time Display Unit)定义时间轴单位.可以为秒(s),毫秒(ms),微秒(μs)或采样点.(17)状态条显示(Status Bar Display)此选项设置图形窗口的状态条是否显示.(18)幅度显示比例(Magnitude Display Scale)有两类幅度显示类型:线性或对数显示(公式为20log(X)).(19)数据标绘风格(Data Plot Style)此选项设置数据如何显示在图形窗口中.·Line:数据点之间用直线相连;·Bar:每个数据点用竖直线显示.(20)栅格类型(Grid Style)此选项设置水平或垂直方向底线显示.有三个选项:·No Grid:无栅格;·Zero Line:仅显示0轴;·Full Grid:显示水平和垂直栅格.(21)光标模式(Cursor Mode)此选项设置光标显示类型.有3个选项:·No Cursor:无光标;·Data Cursor:在视图状态栏显示数据和光标坐标;·Zoom Cursor:允许放大显示图形.方法:按住鼠标左键,拖动,则定义的矩形框被放大.图2-14为一正弦波数据显示图的例子.。

CCS6。

0 使用教程新建一个工程1、新建一个项目工程:Project/New CCS Project,如下图:2、单击之后,出现如下对话框:设置工程名,路径,设备型号,仿真器型号(可以后需仿真时设置)。

高级设置中的内容直接使用默认设置就可以。

设置完成后单击Finish.3、完成上步后,建立的工程如下图:不选择仿真器型号时,targetConfigs不会生成新建源文件1、新建源文件File-〉New—>Source File,如下图:2、设置源文件名称和源文件的类型添加已有的源文件1、右击工程选择Add Files2、选择需要添加进工程的文件Properties设置1、进入properties设置2、添加头文件,可点击添加按钮添加头文件路径和具体的头文件,3、添加库文件上面添加具体文件,下面添加搜索路径编译当所有的文件都添加完成后,现在就是对源文件进行编译了。

1、Project->Build All,如下图:CCS6.0教程2、点击build all之后,出现如下对话框:3、编译结束后,会在 Console 窗口显示编译结果信息,而在 Problems窗口中显示错误、告警等信息,如下图:配置仿真器当编译完成后,开始进行调试1、File-〉New—〉TargetConfigurationFile,如下图:2、选择Target Configuration File之后出现如下对话框:3、设置文件名之后,单击Finish,出现如下对话框:Connection选择仿真器型号;device选择设备型号。

设置完毕后单击save。

4、连接仿真器将仿真器 xds100v2 与 TMS320F28035 开发板连接好,并通电,然后点击右边的TestConnection按钮。

会出现连接目标板信息,在信息最后当有“The JTAG DR Integrity scan—test has succeeded"指示时,说明连接成功.烧录RAM进行调试1、Run-〉Debug,如下图:2、单击Debug后,出现如下调试界面3、下载程序到 RAM4、点击Load Program后,出现如下对话框5、点击OK后,返回如下界面,然后鼠标点击使其处于选中状态,如下图:6、在自己需要观察的位置设置断点:鼠标指向行号的左侧,然后双击鼠标,即可设置一个断点,如下图示:7、点击这时调试全速运行,使其执行到断点,如下图:8、点击(或按 F5)单步运行,如下图:烧录Flash1、View—〉Project Explorer,如下图:2、显示的Project Explore窗口如下图:3、删除文件,如下图:4、弹出确认删除对话框,选择OK5、把用于烧录Flash的。

Ccs6.0检测xds100v3时,完整、正确的显示内容Ccs6.0 检测xds100v3时,完整、正确的显示内容:[Start: Texas Instruments XDS100v3 USB Debug Probe_0]Execute the command:%ccs_base%/common/uscif/dbgjtag -f %boarddatafile% -rv -o -F inform,logfile=yes -S pathlength -S integrity[Result]-----[Print the board config pathname(s)]------------------------------------C:\Users\ADMINI~1\AppData\Local\TEXASI~1\CCS\ti\0\0\BrdDat\testBoard.dat-----[Print the reset-command software log-file]-----------------------------This utility has selected a 100- or 510-class product.This utility will load the adapter 'jioserdesusbv3.dll'.The library build date was 'Sep 4 2015'.The library build time was '21:59:23'.The library package version is '6.0.14.5'.The library component version is '35.35.0.0'.The controller does not use a programmable FPGA.The controller has a version number of '4' (0x00000004).The controller has an insertion length of '0' (0x00000000).This utility will attempt to reset the controller.This utility has successfully reset the controller.-----[Print the reset-command hardware log-file]-----------------------------The scan-path will be reset by toggling the JTAG TRST signal.The controller is the FTDI FT2232 with USB interface.The link from controller to target is direct (without cable).The software is configured for FTDI FT2232 features.The controller cannot monitor the value on the EMU[0] pin.The controller cannot monitor the value on the EMU[1] pin.The controller cannot control the timing on output pins.The controller cannot control the timing on input pins.The scan-path link-delay has been set to exactly '0' (0x0000).-----[The log-file for the JTAG TCLK output generated from the PLL]----------Test Size Coord MHz Flag Result Description~~~~ ~~~~ ~~~~~~~ ~~~~~~~~ ~~~~ ~~~~~~~~~~~ ~~~~~~~~~~~~~~~~~~~1 64 - 01 00 500.0kHz O good value measure path length2 64 + 00 00 1.000MHz [O] good value apply explicit tclkThere is no hardware for measuring the JTAG TCLK frequency.In the scan-path tests:The test length was 2048 bits.The JTAG IR length was 6 bits.The JTAG DR length was 1 bits.The IR/DR scan-path tests used 2 frequencies.The IR/DR scan-path tests used 500.0kHz as the initial frequency.The IR/DR scan-path tests used 1.000MHz as the highest frequency.The IR/DR scan-path tests used 1.000MHz as the final frequency.-----[Measure the source and frequency of the final JTAG TCLKR input]-------- There is no hardware for measuring the JTAG TCLK frequency.-----[Perform the standard path-length test on the JTAG IR and DR]----------- This path-length test uses blocks of 64 32-bitwords.The test for the JTAG IR instruction path-length succeeded.The JTAG IR instruction path-length is 6 bits.The test for the JTAG DR bypass path-length succeeded.The JTAG DR bypass path-length is 1 bits.-----[Perform the Integrity scan-test on the JTAG IR]------------------------This test will use blocks of 64 32-bit words.This test will be applied just once.Do a test using 0xFFFFFFFF.Scan tests: 1, skipped: 0, failed: 0Do a test using 0x00000000.Scan tests: 2, skipped: 0, failed: 0Do a test using 0xFE03E0E2.Scan tests: 3, skipped: 0, failed: 0Do a test using 0x01FC1F1D.Scan tests: 4, skipped: 0, failed: 0Do a test using 0x5533CCAA.Scan tests: 5, skipped: 0, failed: 0Do a test using 0xAACC3355.Scan tests: 6, skipped: 0, failed: 0All of the values were scanned correctly.The JTAG IR Integrity scan-test has succeeded.-----[Perform the Integrity scan-test on the JTAG DR]------------------------This test will use blocks of 64 32-bit words.This test will be applied just once.Do a test using 0xFFFFFFFF.Scan tests: 1, skipped: 0, failed: 0Do a test using 0x00000000.Scan tests: 2, skipped: 0, failed: 0Do a test using 0xFE03E0E2.Scan tests: 3, skipped: 0, failed: 0Do a test using 0x01FC1F1D.Scan tests: 4, skipped: 0, failed: 0Do a test using 0x5533CCAA.Scan tests: 5, skipped: 0, failed: 0Do a test using 0xAACC3355.Scan tests: 6, skipped: 0, failed: 0All of the values were scanned correctly.The JTAG DR Integrity scan-test has succeeded. [End: Texas Instruments XDS100v3 USB Debug Probe_0]。

CCS6.0显示AD波形

利用CCS6.0 实时显示两路AD转换结果,用波形的显示的设置步骤如下:1、打开CCS6.0, 打开AD工程,如图:

程序如下:

#include "myapp.h"

#include "csedu.h"

#include "scancode.h"

void InitADC();

void wait( unsigned int cycles );

void EnableAPLL( );

unsigned int nADC0[256],nADC1[256];

main()

{

int i;

unsigned int uWork;

EnableAPLL();

SDRAM_init();

InitADC();

PLL_Init(132);

while ( 1 )

{

for ( i=0;i<256;i++ )

{

ADCCTL=0x8000; // 启动AD转换,通道0

do

{

uWork=ADCDATA;

} while ( uWork&0x8000 );

nADC0=uWork&0x0fff;

}

for ( i=0;i<256;i++ )

{

ADCCTL=0x9000; // 启动AD转换,通道1

do

{

uWork=ADCDATA;

} while ( uWork&0x8000 );

nADC1=uWork&0x0fff;

}

asm( " nop"); // break point

}

}

void InitADC()

{

ADCCLKCTL=0x23; // 4MHz ADCLK

ADCCLKDIV=0x4f00;

}

void wait( unsigned int cycles )

{

int i;

for ( i = 0 ; i < cycles ; i++ ){ }

}

void EnableAPLL( )

{

*( ioport volatile unsigned short* )0x1f00 = 4; wait( 25 );

*( ioport volatile unsigned short* )0x1f00 = 0;

// MULITPLY

*( ioport volatile unsigned short* )0x1f00 = 0x3000;

// COUNT

*( ioport volatile unsigned short* )0x1f00 |= 0x4F8; wait( 25 );

//*( ioport volatile unsigned short* )0x1f00 |= 0x800 // MODE

*( ioport volatile unsigned short* )0x1f00 |= 2; wait( 30000 ); // APLL Select

*( ioport volatile unsigned short* )0x1e80 = 1; // DELAY

wait( 60000 );

}

2、点击菜单project->build all,编译,如图,没错误。

3、选中工程,点击“DEBUG"按钮,如图:

4、让光标停在:asm( " nop"); // break pointz这一行,

点击菜单RUN->Toggle breakpoint,设断点,如图:

5、按F8键,程序运行到断点处,如图:

6、选择菜单TOOL->GRAPH->SINGLE TIME,弹出如图窗口:

7、将上述窗口参数配置成如图所示:

8、点击OK按钮,显示波形界面如下图:

9、选中断点,右键单击,选中breakpoint properties,如图:

10、把ACTION一栏,Remain Halted改为Refresh all windows,如图:

11、点击OK按钮。

点击运行按钮(绿色小箭头),运行程序。

可以看到波形连续刷新显示,本次实验结束。