S3C2440A中文手册【八】

- 格式:pdf

- 大小:216.48 KB

- 文档页数:11

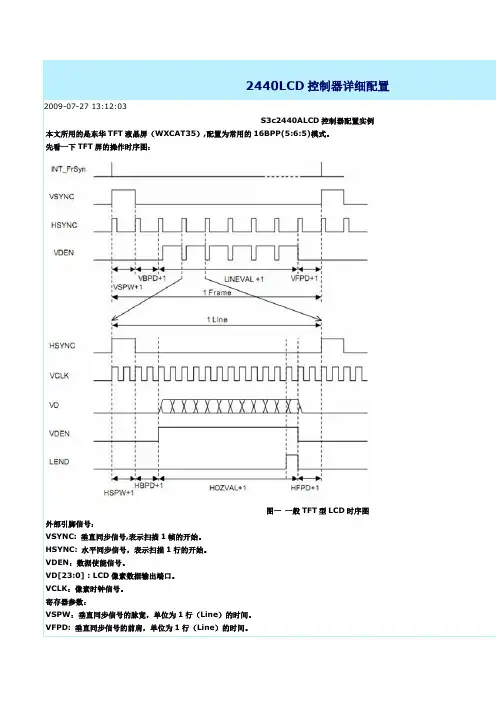

VBPD: 垂直同步信号的后肩,单位为1行(Line)的时间。

LINEVAL :垂直显示尺寸-1,即屏行宽-1。

HBPD:水平同步信号的后肩,单位为1VCLK的时间。

HFPD:水平同步信号的前肩,单位为1VCLK的时间。

HSPW:水平同步信号的脉宽,单位为1VCLK的时间。

HOZVAL:水平显示尺寸-1,即屏列宽-1。

由上图可知:扫描一帧所需的时间:=((VSPW+1)+(VBPD+1)+( LINEVAL+1)+(VFPD+1))个行时间。

扫描一行所所需的时间:=((HSPW+1)+(HSPD+1)+(HFPD+1)+ (HOZVAL+1))个VCLK时间。

而一个VCLK时间由LCD寄存器LCDCON1内的CLKVAL决定:=HCLK/[2*(CLKVAL+1)]因此扫描一帧所需的时间:T=[(VSPW+1)+(VBPD+1)+( LINEVAL+1)+(VFPD+1)]*[(HSPW+1)+(HSPD+1)+(HFPD+1)+ (HOZVAL+1)]* HCLK/[2*(CLKVAL+1)]即帧频率为:1/T注意:以上的时序图为一般TFT的时序图。

实际TFT对应的时序图时序可能不一样(比如极性,符号等)。

下文中详述。

图2东华TFT型LCD(WXCAT35)时序图//2440A寄存器参数#define MVAL (13)#define MVAL_USED (0) //0=each frame 1=rate by MVAL#define INVVDEN (1) //0=normal 1=inverted#define BSWP (0) //Byte swap control#define HWSWP (1) //Half word swap control#define PNRMODE (3) // 设置为TFT屏#define BPPMODE (12) // 设置为16bpp模式//东华屏参数#define VBPD (3-1) //12 垂直同步信号的后肩参数见东华pdf #define VFPD (14-1) //4 垂直同步信号的前肩#define VSPW (15-1) //5垂直同步信号的脉宽#define HBPD (38-1) //(22)水平同步信号的后肩#define HFPD (20-1) //(33)水平同步信号的前肩#define HSPW (30-1) //(44)水平同步信号的脉宽#define CLKVAL_TFT (6)//屏大小#define LCD_XSIZE_TFT (240)//屏实际列数#define LCD_YSIZE_TFT (320)// 屏实际行数#define SCR_XSIZE_TFT (240) //虚拟屏列数#define SCR_YSIZE_TFT (320) //虚拟屏行数#define HOZVAL_TFT (LCD_XSIZE_TFT-1)#define LINEVAL_TFT (LCD_YSIZE_TFT-1)以上有关东华屏参数设置,在PDF中如下所示:7. LCDSADDR2寄存器rLCDSADDR2=M5D( ((U32)LCD_BUFFER+(SCR_XSIZE_TFT*LCD_YSIZE_TFT*2))>>1 );//单位为字节一个点16bit=2字节8. LCDSADDR3寄存器rLCDSADDR3=(((SCR_XSIZE_TFT-LCD_XSIZE_TFT)/1)<<11)|(LCD_XSIZE_TFT/1);// 1=*16bit/半字=16/16LCD初始化程序:void Lcd_Init(void){//引脚功能初始化rGPCUP = 0x00000000;rGPCCON = 0xaaaa02a9;rGPDUP = 0x00000000;rGPDCON=0xaaaaaaaa; //Initialize VD[15:8]rLCDCON1=(CLKVAL_TFT<<8)|(MVAL_USED<<7)|(PNRMODE<<5)|(BPPMODE<<1)|0;// TFT LCD panel,16bpp TFT,ENVID=off(Disable the video output and the LCD control signal) rLCDCON2=(VBPD<<24)|(LINEVAL_TFT<<14)|(VFPD<<6)|(VSPW);rLCDCON3=(HBPD<<19)|(HOZVAL_TFT<<8)|(HFPD);rLCDCON4=(MVAL<<8)|(HSPW);rLCDCON5 = (1<<11) | (1<<10) | (1<<9) | (1<<8) | (0<<7) | (0<<6) | (1<<3) |(BSWP<<1) | (HW //5:6:5rLCDSADDR1=(((U32)LCD_BUFFER>>22)<<21)|M5D((U32)LCD_BUFFER>>1);rLCDSADDR2=M5D( ((U32)LCD_BUFFER+(SCR_XSIZE_TFT*LCD_YSIZE_TFT*2))>>1 );//单位为字节一个rLCDSADDR3=(((SCR_XSIZE_TFT-LCD_XSIZE_TFT)/1)<<11)|(LCD_XSIZE_TFT/1);// 1=*16bit/半字= rLCDINTMSK|=(3); // MASK LCD Sub InterruptrTCONSEL &= (~7) ; // Disable LPC3480rTPAL=0; // Disable Temp Palette}16BPP模式特点:内存数据格式:。

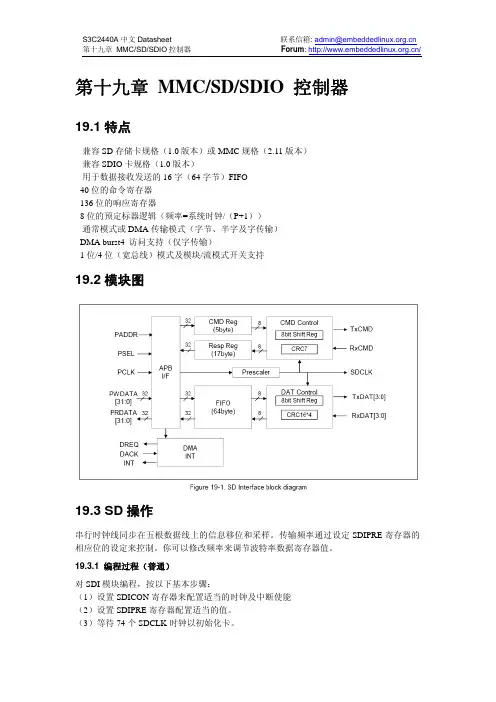

第十九章MMC/SD/SDIO控制器19.1特点-兼容SD存储卡规格(1.0版本)或MMC规格(2.11版本)-兼容SDIO卡规格(1.0版本)-用于数据接收发送的16字(64字节)FIFO-40位的命令寄存器-136位的响应寄存器-8位的预定标器逻辑(频率=系统时钟/(P+1))-通常模式或DMA传输模式(字节、半字及字传输)-DMA burst4访问支持(仅字传输)-1位/4位(宽总线)模式及模块/流模式开关支持19.2模块图19.3SD操作串行时钟线同步在五根数据线上的信息移位和采样。

传输频率通过设定SDIPRE寄存器的相应位的设定来控制。

你可以修改频率来调节波特率数据寄存器值。

19.3.1编程过程(普通)对SDI模块编程,按以下基本步骤:(1)设置SDICON寄存器来配置适当的时钟及中断使能(2)设置SDIPRE寄存器配置适当的值。

(3)等待74个SDCLK时钟以初始化卡。

19.3.2CMD路径编程(1)写命令参数32位到SDICmdArg(2)决定命令类型并通过设置SDICmdCon开始命令传输(3)当SDICmdSta的特殊标志被置位,确认SDICMD路径操作的结束。

(4)如果命令类型是不相应,标志是CmdSent。

(5)如果命令类型是相应,标志是RspFin。

(6)通过对相应位写1,清除SDICmdStaD的标志。

19.3.3数据路径编程(1)写数据超时期间到SDIDTimer(2)写模块大小(模块长度)到SDIBSize(通常是0x80字)(3)确定模块模式,宽总线,DMA等且通过社子SDIDatCon来开始数据传输(4)发送数据->写数据到数据寄存器(SDIDAT),当发送FIFO有效(TFDET置位),或一半(TFHalf置位),或空(TFEmpty置位)。

(5)接收数据->从数据寄存器(SDIDAT)读数据,当接收FIFO有效(RFDET置位),或满(RFFull置位)。

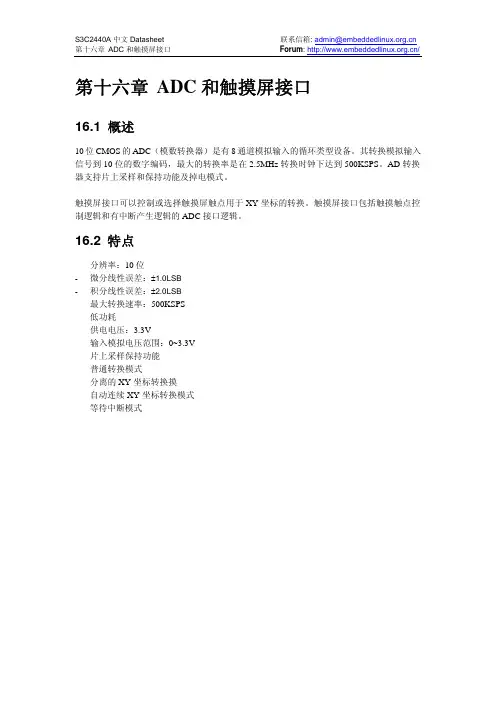

第十六章ADC和触摸屏接口16.1概述10位CMOS的ADC(模数转换器)是有8通道模拟输入的循环类型设备。

其转换模拟输入信号到10位的数字编码,最大的转换率是在2.5MHz转换时钟下达到500KSPS。

AD转换器支持片上采样和保持功能及掉电模式。

触摸屏接口可以控制或选择触摸屏触点用于XY坐标的转换。

触摸屏接口包括触摸触点控制逻辑和有中断产生逻辑的ADC接口逻辑。

16.2特点-分辨率:10位-微分线性误差:±1.0LSB-积分线性误差:±2.0LSB-最大转换速率:500KSPS-低功耗-供电电压:3.3V-输入模拟电压范围:0~3.3V-片上采样保持功能-普通转换模式-分离的XY坐标转换摸-自动连续XY坐标转换模式-等待中断模式16.3ADC及触摸屏接口操作模块图如图16-1所示AD转换器和触摸屏接口的功能模块图。

注意AD转换器设备是一个循环类型。

注意(图标)当触摸屏接口使用时,XM或PM应该接触摸屏接口的地。

当触摸屏设备不使用时,XM或PM应该连接模拟输入信号作为普通ADC转换用。

16.4功能描述16.4.1AD转换时间当GCLK频率为50MHz和预分频器(预定标器)值为49,总共10位转换时间如下:AD转换器频率=50MHz/(49+1)=1MHz转换时间=1/(1MHz/5cycles)=1/200KHz=5us注:AD转换器设计在最大2.5MHz时钟下工作,所以转换率最高达到500KSPS。

16.4.2触摸屏接口模式(1)正常转换模式单个转换模式可能多数是使用在通用目的的ADC转换。

该模式可以通过设置ADCCON(ADC控制寄存器)来初始化并且完成对ADCDAT0的读写操作(ADC数据寄存器0)。

(2)分离XY坐标转换模式触摸屏控制器可以在两种转换模式中的一种模式下操作。

分离的XY坐标转换模式由以下方法操作。

X坐标模式写X坐标转换数据到ADCDAT0,触摸屏接口产生中断源到中断控制器。

以下程序在Keil4中建立项目,芯片选S3C 2410A无论是S3C2410A还是S3C2440A,其IO口B都是11位二进制数,xxx xxxx xxxx,现在控制第5、6、7、8为做输出点亮LED灯(共阳极,输出0点亮),即xx8 765x xxxx,GPBCON equ 0x56000010GPBDAT equ 0x56000014GPBUP equ 0x56000018xport xmainarea Init,code,readonlyentryexportxmainldr r0,=GPBCONldr r1,[r0]bic r1,#0x3fC00 ;r1=xx00 0000 00xx xxxx xxxxorr r1,#0x15400 ;r1=xx01 0101 01xx xxxx xxxxstr r1,[r0] ;r1传给GPBCON设置8765位为输出ldr r0,=GPBUPldr r1,[r0]orr r1,#0x1e0 ;r1=xx1 111x xxxxstr r1,[r0] ;开B口第8、7、6、5位上拉电阻ldr r0,=GPBDATldr r2,[r0] ;把B口最初状态保存在R2 ;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;LOOP dr r1,[r2]orr r1,#0x1c0str r1,[r0]bl delay;BL跳转时将PC+4值自动保存在R14即LR中,也就是将程序的下一个语句地址保存在lr中在跳;转后执行mov pc,lr相当于返回,这样BL相当于调用子程序,pc=lr相当于子程序返回;;;;;;;;;;;;;;;;;;dr r1,[r2]orr r1,#0x1a0str r1,[r0]bl delay;;;;;;;;;;;;;;;;;;;;;ldr r1,[r2]orr r1,#0x160str r1,[r0]bl delay;;;;;;;;;;;;;;;;;;;;;;;;ldr r1,[r2]orr r1,#0x0e0str r1,[r0]bl delay;;;;;;;;;;;;;;;;;;;;;;;;b LOOPdelaymov r3,#3delay1 sub r3,r3,#1cmp r3,#0x0bne delay1mov pc,lr ;这句相当于子程序返回语句 end1. A(*(volatile unsigned *)0x56000010)的意思是把0x48000000强制转换成volatile unsigned long类型的指针,暂记为p,那么就是#define A *p,即A为P指针指向位置的内容了。

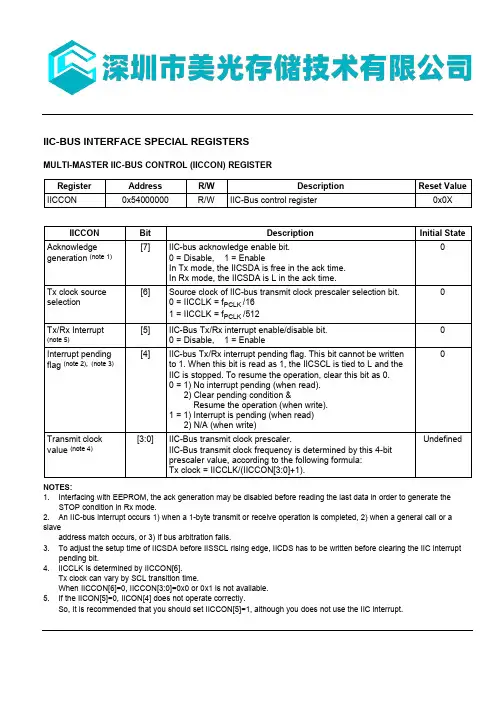

IIC-BUS INTERFACE SPECIAL REGISTERSMULTI-MASTER IIC-BUS CONTROL (IICCON) REGISTERRegister Address R/W DescriptionReset ValueIICCON0x54000000R/WIIC-Bus control register0x0XIICCON Bit DescriptionInitial StateAcknowledge generation (note 1)[7]IIC-bus acknowledge enable bit.0 = Disable, 1 = EnableIn Tx mode, the IICSDA is free in the ack time.In Rx mode, the IICSDA is L in the ack time.Tx clock source selection [6]Source clock of IIC-bus transmit clock prescaler selection bit.0 = IICCLK = f PCLK /161 = IICCLK = f PCLK /512Tx/Rx Interrupt(note 5)[5]IIC-Bus Tx/Rx interrupt enable/disable bit.0 = Disable, 1 = Enable0Interrupt pending flag (note 2), (note 3)[4]IIC-bus Tx/Rx interrupt pending flag. This bit cannot be written to 1. When this bit is read as 1, the IICSCL is tied to L and the IIC is stopped. To resume the operation, clear this bit as 0.0 = 1) No interrupt pending (when read).2)Clear pending condition &Resume the operation (when write).1 = 1) Interrupt is pending (when read)2)N/A (when write)0Transmit clock value (note 4)[3:0]IIC-Bus transmit clock prescaler.IIC-Bus transmit clock frequency is determined by this 4-bit prescaler value, according to the following formula:Tx clock = IICCLK/(IICCON[3:0]+1).UndefinedNOTES:1.Interfacing with EEPROM, the ack generation may be disabled before reading the last data in order to generate theSTOP condition in Rx mode.2.An IIC-bus interrupt occurs 1) when a 1-byte transmit or receive operation is completed, 2) when a general call or a slaveaddress match occurs, or 3) if bus arbitration fails.3.To adjust the setup time of IICSDA before IISSCL rising edge, IICDS has to be written before clearing the IIC interruptpending bit.4.IICCLK is determined by IICCON[6].Tx clock can vary by SCL transition time.When IICCON[6]=0, IICCON[3:0]=0x0 or 0x1 is not available.5.If the IICON[5]=0, IICON[4] does not operate correctly.So, It is recommended that you should set IICCON[5]=1, although you does not use the IIC interrupt.IIC-BUS INTERFACES3C2410XMULTI-MASTER IIC-BUS CONTROL/STATUS (IICSTAT) REGISTERRegister Address R/W DescriptionReset ValueIICSTAT0x54000004R/WIIC-Bus control/status register0x0IICSTAT Bit DescriptionInitial StateMode selection[7:6]IIC-bus master/slave Tx/Rx mode select bits.00: Slave receive mode 01: Slave transmit mode 10: Master receive mode 11: Master transmit mode00Busy signal status /START STOP condition[5]IIC-Bus busy signal status bit.0 = read) Not busy (when read) write) STOP signal generation 1 = read) Busy (when read)write) START signal generation.The data in IICDS will be transferred automatically just after the start signal.0Serial output [4]IIC-bus data output enable/disable bit.0 = Disable Rx/Tx, 1 = Enable Rx/Tx 0Arbitration status flag[3]IIC-bus arbitration procedure status flag bit.0 = Bus arbitration successful1 = Bus arbitration failed during serial I/O 0Address-as-slave status flag[2]IIC-bus address-as-slave status flag bit.0 = Cleared when START/STOP condition was detected1 = Received slave address matches the address value in the IICADDAddress zero status flag[1]IIC-bus address zero status flag bit.0 = Cleared when START/STOP condition was detected.1 = Received slave address is 00000000b.0Last-received bit status flag[0]IIC-bus last-received bit status flag bit.0 = Last-received bit is 0 (ACK was received).1 = Last-received bit is 1 (ACK was not received).S3C2410X IIC-BUS INTERFACEIIC-BUS INTERFACE S3C2410XS3C2410X SPI INTERFACESPI SPECIAL REGISTERSSPI CONTROL REGISTERRegister Address R/W Description Reset Value SPCON00x59000000R/W SPI channel 0 control register0x00 SPCON10x59000020R/W SPI channel 1 control register0x00SPCONn Bit Description Initial StateSPI Mode Select (SMOD)[6:5]Determine how and by what SPTDAT is read/written.00 = polling mode, 01 = interrupt mode10 = DMA mode, 11 = reserved00SCK Enable (ENSCK)[4]Determine whether you want SCK enable or not (for onlymaster).0 = disable, 1 = enableMaster/Slave Select (MSTR)[3]Determine the desired mode (master or slave).0 = slave, 1 = masterNOTE: In slave mode, there should be set up time formaster to initiate Tx/Rx.Clock Polarity Select (CPOL)[2]Determine an active high or active low clock.0 = active high, 1 = active lowClock Phase Select (CPHA)[1]Select one of two fundamentally different transfer formats.0 = format A, 1 = format BTx Auto Garbage Data mode enable (TAGD)[0]Decide whether the receiving data only needs or not.0 = normal mode, 1 = Tx auto garbage data modeNOTE: In normal mode, if you only want to receive data,you should transmit dummy 0xFF data.。

第八章直接存储器存取概述s3c2440支持在系统总线和外围总线之间的4路DMA控制器。

每一路DMA控制器可以自由的执行数据在系统总线和(或)外围总线之间的动作。

换句话说,每一路可以在下列列4种情况下运行:1.源设备和目标设备都在系统总线上2.源设备在系统总线上,目标设备在外围总线上3.源设备在外围总线上,目标数据在系统总线上4.源设备和目标设备都在外围总线上DMA的主要优点是它可以不通过CPU直接调用数据。

DMA工执行可以软件开始,也可以从内部的外设请求或者外部的引脚请求开始。

DMA请求源每一路DMA控制器都可以从4种开始请求中选择一路,如果DCON寄存器选择H/W DAM 请求模式(注意,选择S/W时这个DMA请求源没意义)。

表8--1列出了4种请求和每一路的关系:表8--1.DMA开始请求和每一路关系这里nXDREQ0和nXDREQ1表示两个外部源(Extermal Devices),12SSDO和12SSDI分别表示IIS的传输和接收。

DMA 工作状态DMA应用3态FSN(有限状态机),它可以描述为以下3步:State--1. 作为起始状态,DMA等待DMA请求,一旦请求到来马上转到State--2,在这个状态,DMA ACK和INT REQ是0.State--2. 在这个状态,DMA ACK变为1,计数器(CURR_TC)从DCON[19:0]装载。

DMA ACK保持1,直到它被清0。

State--3. 在这个状态,控制DMA原子操作的子FSM被初始化了。

子FSM从源地址读取数据后把它写入目标地址。

在这个操作中,数据宽度和传输大小(单次或突发)应给与考虑。

在完整服务模式中,这种操作不断重复直到计数器(CURR_TC)变为0。

然而在单一模式中只进行一次,当子FSM完成每个原子操作时,主FSM对CURR_TC倒计时。

另外,当CURR_TC为0和中断设置DCON[29]为1 时,主FSM发出INT REQ信号(中断请求信号)。

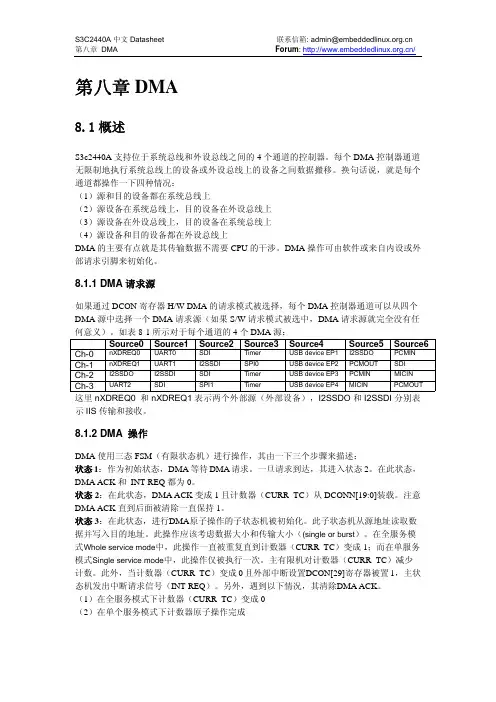

第八章DMA8.1概述S3c2440A支持位于系统总线和外设总线之间的4个通道的控制器。

每个DMA控制器通道无限制地执行系统总线上的设备或外设总线上的设备之间数据搬移。

换句话说,就是每个通道都操作一下四种情况:(1)源和目的设备都在系统总线上(2)源设备在系统总线上,目的设备在外设总线上(3)源设备在外设总线上,目的设备在系统总线上(4)源设备和目的设备都在外设总线上DMA的主要有点就是其传输数据不需要CPU的干涉。

DMA操作可由软件或来自内设或外部请求引脚来初始化。

8.1.1DMA请求源如果通过DCON寄存器H/W DMA的请求模式被选择,每个DMA控制器通道可以从四个DMA源中选择一个DMA请求源(如果S/W请求模式被选中,DMA请求源就完全没有任何意义)。

如表8-1所示对于每个通道的4个DMA源:Source0Source1Source2Source3Source4Source5Source6 Ch-0nXDREQ0UART0SDI Timer USB device EP1I2SSDO PCMIN Ch-1nXDREQ1UART1I2SSDI SPI0USB device EP2PCMOUT SDICh-2I2SSDO I2SSDI SDI Timer USB device EP3PCMIN MICINCh-3UART2SDI SPI1Timer USB device EP4MICIN PCMOUT 这里nXDREQ0和nXDREQ1表示两个外部源(外部设备),I2SSDO和I2SSDI分别表示IIS传输和接收。

8.1.2DMA操作DMA使用三态FSM(有限状态机)进行操作,其由一下三个步骤来描述:状态1:作为初始状态,DMA等待DMA请求。

一旦请求到达,其进入状态2。

在此状态,DMA ACK和INT REQ都为0。

状态2:在此状态,DMA ACK变成1且计数器(CURR_TC)从DCONN[19:0]装载。

第二章处理器工作模式2.1概述S3C2440采用了非常先进的ARM920T内核,它是由ARM(Advanced RISC Machines) 公司研制的。

2.2 处理工作状态从程序员的角度上看,ARM920T可以工作在下面两种工作状态下的一种:● ARM 状态:执行32位字对齐的ARM指令● THUMB 状态:执行16位半字对齐的THUMB指令。

在这种状态下,PC 寄存器的第一位来选择一个字中的哪个半字注意;这两种状态的转换不影响处理模式和寄存器的内容。

2.3 切换状态进入THUMB 状态进入THUMB 状态,可以通过执行BX指令,同时将操作数寄存器的状态位(0位)置1来实现。

当从异常(IRQ,FIQ,UNDEF,ABORT,SWI等)返回时,只要进入异常处理前处理器处于THUMB状态,也会自动进入THUMB状态。

进入ARM状态进入ARM状态,可以通过执行BX指令,并且操作数寄存器的状态位(0位)清零来实现。

当处理进入异常(IRQ,FIQ,RESET,UNDEF,ABORT,SWI等)。

这时,PC值保持在异常模式下的link寄存器中,并从异常向量地址处开始执行处理程序。

存储空间的格式ARM920T将存储器空间视为从0开始由字节组成的线性集合,字节0到3中保存了第一个字节,字节4到7中保存第二个字,以此类推,ARM920T对存储的字,可以按照小端或大端的方式对待。

大端格式:在这种格式中,字数据的高字节存储在低地址中,而字数据的低字节则存放2.4 指令长度指令可以是32位长度(在ARM状态下) 或16位长度(在THUMB状态) 。

数据类型ARM920T支持字节(8位),半字(16位) 和字(32位) 数据类型。

字必须按照4字节对齐,半字必须是2字节对齐。

2.5 操作模式ARM920T支持7种操作模式:● 用户模式(user模式),运行应用的普通模式● 快速中断模式(fiq模式),用于支持数据传输或通道处理● 中断模式(irq模式),用于普通中断处理● 超级用户模式(svc模式),操作系统的保护模式● 异常中断模式(abt模式),输入数据后登入或预取异常中断指令● 系统模式(sys模式),使操作系统使用的一个有特权的用户模式● 未定义模式(und模式),执行了未定义指令时进入该模式]外部中断,异常操作或软件控制都可以改变中断模式。

EMA S3C2440单板机 用户手册V1.0产品型号:EMA-S3C2440-SBC-V1广州英码信息科技有限公司(EMA)是一家从事嵌入式系统以及相关产品设计、制造的专业公司。

公司秉承“为客户利益而努力创新”的理念,为电子产品生产商、开发商提供专业的嵌入式产品解决方案,并为厂家提供ODM和OEM服务。

公司的嵌入式产品涉及动漫游戏机平台、多媒体广告机系统、多媒体便携式产品等当今涉及IT 产业嵌入式领域的新技术、新产品。

公司的研发项目组成员大部分具有硕士学历,在嵌入式系统设计领域拥有多年的经验。

目前我公司已自主研发设计多个嵌入式应用平台方案,并在实际产品中得到应用,并已经具备批量生产能力。

通过EMA的技术与服务,您将获得:1.更低的研发成本针对具有新技术、新产品研发需求的合作伙伴,EMA将致力于新技术、新产品解决方案的研发、服务和技术升级,让合作伙伴更专注于其自身优势领域,从而帮助合作伙伴在节省大量研发成本、降低研发风险的前提下,实现产业升级和产品创新。

2.更高的品质保证EMA所拥有的资深嵌入式研发团队和完善的技术培训体系,将为合作伙伴提供专业级的、高标准的产品品质保证。

3.更优质的服务EMA以专家级的技术手段和服务诚信的敬业精神,为客户提供全方位的技术支持与产品服务,包括技术支持、技术培训、软件升级等增值服务。

4. 更快的市场响应能力EMA针对新的市场需求为客户提供新产品决策支持,并帮助客户进行快速的技术和产品实现,以更快的速度引领市场。

第一章EMA-S3C2440单板机介绍 (5)1.1 EMA-S3C2440单板机简介 (5)1.1.1 前言 (5)1.1.2 EMA-S3C2440单板机外观 (6)1.1.3产品规格 (6)1.1.3EMA-S3C2440板子的特点 (8)1.1.4用户光盘资源说明 (8)1.2 硬件资源分配 (10)1.2.1 地址空间分配和片选信号定义 (10)1.2.2接口资源及按键说明 (11)1.3 linux 特性 (12)1.4 WindowsCE 特性 (13)第二章 EMA-S3C2440单板机的使用 (13)2.1串口连接 (13)2.2 PC 端USB 驱动安装 (16)2.3 启动 LINUX 和WINCE (21)2.3.1 启动LINUX (21)2.3.2 启动 WINCE (22)2.4 嵌入式Linux的应用介绍 (23)2.4.1如何利用剩余的Flash空间 (23)2.4.2如何自动运行应用软件 (24)2.4.3如何升级文件系统 (24)2.4.4铁电功能(可选) (24)2.4.5加密功能(可选) (25)2.4.6 扩展GPIO口的使用 (26)2.4.7 U盘的使用 (28)2.5 非操作系统下的外围资源测试 (28)2.5.1 运行测试程序 (28)2.5.2 相关外围资源测试 (31)2.6 使用SJF烧写文件 (33)2.6.1 烧写BIOS到NOR Flash (34)2.6.2 烧写BIOS到NAND Flash (38)2.7 通过英码bootloader烧写文件 (42)2.7.1 NAND 启动下烧写BIOS 到NAND和NOR (43)2.7.2 NOR启动下烧写BIOS 到NAND和NOR (46)2.7.3 如何使用自己的bootloader (46)第三章烧写和启动Linux (47)3.1 烧写 LINUX 内核 (47)3.2 烧写根文件系统 (48)3.3 运行Linux (50)第四章烧写 WINCE 和启动 WINCE (52)4.1 下载WINCE (52)4.2 烧写Wince (53)4.3 启动运行WINCE (53)附录 (55)vga板扩展插槽与GPIO对照表 (55)第一章EMA-S3C2440单板机介绍1.1 EMA-S3C2440单板机简介1.1.1 前言EMA-S3C2440单板机采用核心板+底板的模式,核心板为6层板,底板为2层板;严格按照3C认证和EMC认证要求,合理的布线使核心板具有最佳的电气性能和抗干扰性能,符合工业级要求。

S3C2410A中⽂数据⼿册第⼀章产品综述1.1特性 (2)体系结构 (2)系统管理器 (3)NAND Flash 启动引导 (3)Cache 存储器 (3)时钟和电源管理 (3)中断控制器 (4)具有脉冲带宽调制功能的定时器 (4)RTC(实时时钟) (4)通⽤I/O端⼝ (4)UART (4)DMA控制器 (5)A/D转换和触摸屏接⼝ (5)LCD控制器STN LCD显⽰特性 (5)TFT彩⾊显⽰屏 (5)看门狗定时器 (5)IIC总线接⼝ (6)IIS总线接⼝ (6)USB主设备 (6)SD主机接⼝ (6)SPI接⼝ (6)⼯作电压 (7)操作频率 (7)封装 (7)1.2内部结构图 (8)表1-1 272-FBGA 引脚分配及顺序 (9)表1-2 272-FBGA封装的引脚分配 (12)信号描述 (21)表1-3 S3C2410A信号描述 (21)表1-4 S3C2410A 专⽤寄存器 (25)Samsung 公司推出的16/32位RISC处理器S3C2410A,为⼿持设备和⼀般类型应⽤提供了低价格、低功耗、⾼性能⼩型微控制器的解决⽅案。

为了降低整个系统的成本,S3C2410A提供了以下丰富的内部设备:分开的16KB的指令Cache和16KB数据Cache,MMU虚拟存储器管理,LCD控制器(⽀持STN&TFT),⽀持NAND Flash系统引导,系统管理器(⽚选逻辑和SDRAM控制器),3通道UART,4通道DMA,4通道PWM定时器,I/O 端⼝,RTC,8通道10位ADC和触摸屏接⼝,IIC-BUS接⼝,IIC-BUS接⼝,USB主机,USB 设备,SD主卡&MMC卡接⼝,2通道的SPI以及内部PLL时钟倍频器。

S3C2410A采⽤了ARM920T内核,0.18um⼯艺的CMOS标准宏单元和存储器单元。

它的低功耗、精简和出⾊的全静态设计特别适⽤于对成本和功耗敏感的应⽤。

S3C2440A32-BIT CMOSMICROCONTROLLERUSER'S MANUALRevision 1Important NoticeThe information in this publication has been carefully checked and is believed to be entirely accurate at the time of publication. Samsung assumes no responsibility, however, for possible errors or omissions, or for any consequences resulting from the use of the information contained herein. Samsung reserves the right to make changes in its products or product specifications with the intent to improve function or design at any time and without notice and is not required to update this documentation to reflect such changes.This publication does not convey to a purchaser of semiconductor devices described herein any license under the patent rights of Samsung or others. Samsung makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does Samsung assume any liability arising out of the application or use of any product or circuit and specifically disclaims any and all liability, including without limitation any consequential or incidental damages."Typical" parameters can and do vary in different applications. All operating parameters, including "Typicals" must be validated for each customer application by the customer's technical experts. Samsung products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, for other applications intended to support or sustain life, or for any other application in which the failure of the Samsung product could create a situation where personal injury or death may occur.Should the Buyer purchase or use a Samsung product for any such unintended or unauthorized application, the Buyer shall indemnify and hold Samsung and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, expenses, and reasonable attorney fees arising out of, either directly or indirectly, any claim of personal injury or death that may be associated with such unintended or unauthorized use, even if such claim alleges that Samsung was negligent regarding the design or manufacture of said product.S3C2440A 32-Bit CMOS MicrocontrollerUser's Manual, Revision 1Publication Number: 21-S3-C2440A-072004© 2004 Samsung ElectronicsAll rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, electric or mechanical, by photocopying, recording, or otherwise, without the prior written consent of Samsung Electronics.Samsung Electronics' microcontroller business has been awarded full ISO-14001certification (BVQ1 Certificate No. 9330). All semiconductor products are designed andmanufactured in accordance with the highest quality standards and objectives.Samsung Electronics Co., Ltd.San #24 Nongseo-Ri, Giheung- EupYongin-City, Gyeonggi-Do, KoreaC.P.O. Box #37, Suwon 449-900TEL:(82)-(031)-209-1490FAX:(82) (331) 209-1909Home-Page URL: /Printed in the Republic of KoreaTable of ContentsChapter 1Product OverviewIntroduction.........................................................................................................................................1-1 Features.............................................................................................................................................1-2 Block Diagram....................................................................................................................................1-5 Pin Assignments.................................................................................................................................1-6 Signal Descriptions..............................................................................................................................1-20 S3C2440A Special Registers................................................................................................................1-26 Chapter 2Programmer's ModelOverview.............................................................................................................................................2-1 Processor Operating States.........................................................................................................2-1 Switching State...........................................................................................................................2-1 Memory Formats.........................................................................................................................2-1 Big-Endian Format.......................................................................................................................2-2 Little-Endian Format....................................................................................................................2-2 Instruction Length........................................................................................................................2-2 Operating Modes.........................................................................................................................2-3 Registers....................................................................................................................................2-3 The Program Status Registers......................................................................................................2-7 Exceptions.................................................................................................................................2-10 Interrupt Latencies.......................................................................................................................2-15 Reset.........................................................................................................................................2-15Table of Contents (Continued)Chapter 3ARM Instruction SetInstruction Set Summay.......................................................................................................................3-1 Format Summary........................................................................................................................3-1 Instruction Summary....................................................................................................................3-2 The Condition Field..............................................................................................................................3-4 Branch and Exchange (Bx)...................................................................................................................3-5 Instruction Cycle Times................................................................................................................3-5 Assembler Syntax.......................................................................................................................3-5 Using R15 as an Operand............................................................................................................3-5 Branch and Branch with Link (B, Bl)......................................................................................................3-7 The Link Bit................................................................................................................................3-7 Instruction Cycle Times................................................................................................................3-7 Assembler Syntax.......................................................................................................................3-8 Data Processing..................................................................................................................................3-9 Cpsr Flags..................................................................................................................................3-11 Shifts.........................................................................................................................................3-12 Immediate Operand Rotates.........................................................................................................3-16 Writing to R15.............................................................................................................................3-16 Using R15 as an Operandy...........................................................................................................3-16 TEQ, TST, Cmp and Cmn Opcodes...............................................................................................3-16 Instruction Cycle Times................................................................................................................3-16 Assembler Syntax.......................................................................................................................3-17 Examples...................................................................................................................................3-17 Psr Transfer (MRS, MSR).....................................................................................................................3-18 Operand Restrictions...................................................................................................................3-18 Reserved Bits..............................................................................................................................3-20 Examples...................................................................................................................................3-20 Instruction Cycle Times................................................................................................................3-20 Assembly Syntax........................................................................................................................3-21 Examples...................................................................................................................................3-21 Multiply And Multiply-Accumulate (MUL, MLA).......................................................................................3-22 Cpsr Flags..................................................................................................................................3-24 Instruction Cycle Times................................................................................................................3-24 Assembler Syntax.......................................................................................................................3-24 Examples...................................................................................................................................3-24 Multiply Long And Multiply-Accumulate Long (MULL, MLAL)...................................................................3-25 Operand Restrictions...................................................................................................................3-26 Cpsr Flags..................................................................................................................................3-26 Instruction Cycle Times................................................................................................................3-26 Assembler Syntax.......................................................................................................................3-27 Examples...................................................................................................................................3-27Table of Contents (Continued)Chapter 3ARM Instruction Set (Continued)Single Data Transfer (LDR, STR)...........................................................................................................3-28 Offsets and Auto-Indexing............................................................................................................3-29 Shifted Register Offset.................................................................................................................3-29 Bytes and Words........................................................................................................................3-29 Use of R15..................................................................................................................................3-31 Example.....................................................................................................................................3-31 Data Aborts................................................................................................................................3-31 Instruction Cycle Times................................................................................................................3-31 Assembler Syntax.......................................................................................................................3-32 Examples...................................................................................................................................3-33 Halfword and Signed Data Transfer (LDRH/STRH/LDRSB/LDRSH)...........................................................3-34 Offsets and Auto-Indexing............................................................................................................3-35 Halfword Load and Stores.............................................................................................................3-36 Use of R15..................................................................................................................................3-37 Data Aborts................................................................................................................................3-37 Instruction Cycle Times................................................................................................................3-37 Assembler Syntax.......................................................................................................................3-38 Examples...................................................................................................................................3-39 Block Data Transfer (LDM, STM)...........................................................................................................3-40 The Register List.........................................................................................................................3-40 Addressing Modes.......................................................................................................................3-41 Address Alignment......................................................................................................................3-41 Use of the S Bit...........................................................................................................................3-43 Use of R15 as The Base..............................................................................................................3-43 Inclusion of the Base in the Register List.......................................................................................3-44 Data Aborts................................................................................................................................3-44 Instruction Cycle Times................................................................................................................3-44 Assembler Syntax.......................................................................................................................3-45 Examples...................................................................................................................................3-46 Single Data Swap (SWP).....................................................................................................................3-47 Bytes and Words........................................................................................................................3-47 Use of R15..................................................................................................................................3-48 Data Aborts................................................................................................................................3-48 Instruction Cycle Times................................................................................................................3-48 Assembler Syntax.......................................................................................................................3-48 Software Interrupt (SWI).......................................................................................................................3-49 Return from the Supervisor...........................................................................................................3-49 Comment Field............................................................................................................................3-49 Instruction Cycle Times................................................................................................................3-49 Assembler Syntax.......................................................................................................................3-50 Coprocessor Data Operations (CDP).....................................................................................................3-51 Coprocessor Instructions..............................................................................................................3-51 Instruction Cycle Times................................................................................................................3-52 Examples...................................................................................................................................3-52Table of Contents (Continued)Chapter 3ARM Instruction Set (Continued)Coprocessor Data Transfers (LDC, STC)................................................................................................3-53 The Coprocessor Fields...............................................................................................................3-54 Addressing Modes.......................................................................................................................3-54 Address Alignment......................................................................................................................3-54 Data Aborts................................................................................................................................3-54 Assembler Syntax.......................................................................................................................3-55 Examples...................................................................................................................................3-55 Coprocessor Register Transfers (MRC, MCR).................................................................................3-56 The Coprocessor Fields...............................................................................................................3-56 Transfers to R15..........................................................................................................................3-57 Transfers from R15......................................................................................................................3-57 Instruction Cycle Times................................................................................................................3-57 Assembler Syntax.......................................................................................................................3-57 Examples...................................................................................................................................3-57 Undefined Instruction...................................................................................................................3-58 Instruction Cycle Times................................................................................................................3-58 Assembler Syntax.......................................................................................................................3-58 Instruction Set Examples.............................................................................................................3-59 Using the Conditional Instructions.................................................................................................3-59 Pseudo-Random Binary Sequence Generator.................................................................................3-61 Multiplication by Constant Using the Barrel Shifter..........................................................................3-61 Loading a Word from an Unknown Alignment.................................................................................3-63 Chapter 4Thumb Instruction SetThumb Instruction Set Format...............................................................................................................4-1 Format Summary........................................................................................................................4-2 Opcode Summary.......................................................................................................................4-3 Format 1: Move Shifted Register...........................................................................................................4-5 Operation....................................................................................................................................4-5 Instruction Cycle Times................................................................................................................4-6 Examples...................................................................................................................................4-6 Format 2: Add/Subtract........................................................................................................................4-7 Operation....................................................................................................................................4-7 Instruction Cycle Times................................................................................................................4-8 Examples...................................................................................................................................4-8 Format 3: Move/Compare/Add/Subtract Immediate.................................................................................4-9 Operations..................................................................................................................................4-9 Instruction Cycle Times................................................................................................................4-10 Examples...................................................................................................................................4-10Table of Contents (Continued)Chapter 4Thumb Instruction Set (Continued)Format 4: ALU Operations....................................................................................................................4-11 Operation....................................................................................................................................4-11 Instruction Cycle Times................................................................................................................4-12 Examples...................................................................................................................................4-12 Format 5: Hi-Register Operations/Branch Exchange...............................................................................4-13 Operation....................................................................................................................................4-13 Instruction Cycle Times................................................................................................................4-14 The BX Instruction.......................................................................................................................4-14 Examples...................................................................................................................................4-15 Using R15 As an Operand............................................................................................................4-15 Format 6: PC-Relative Load..................................................................................................................4-16 Operation....................................................................................................................................4-16 Instruction Cycle Times................................................................................................................4-17 Examples...................................................................................................................................4-17 Format 7: Load/Store With Register Offset.............................................................................................4-18 Operation....................................................................................................................................4-19 Instruction Cycle Times................................................................................................................4-19 Examples...................................................................................................................................4-19 Format 8: Load/Store Sign-Extended Byte/Halfword................................................................................4-20 Operation....................................................................................................................................4-20 Instruction Cycle Times................................................................................................................4-21 Examples...................................................................................................................................4-21 Format 9: Load/Store With Immediate Offset..........................................................................................4-22 Operation....................................................................................................................................4-23 Instruction Cycle Times................................................................................................................4-23 Examples...................................................................................................................................4-23 Format 10: Load/Store Halfword............................................................................................................4-24 Operation....................................................................................................................................4-24 Examples...................................................................................................................................4-25 Format 11: SP-Relative Load/Store.......................................................................................................4-26 Operation....................................................................................................................................4-26 Instruction Cycle Times................................................................................................................4-27 Examples...................................................................................................................................4-27 Format 12: Load Address.....................................................................................................................4-28 Operation....................................................................................................................................4-28 Instruction Cycle Times................................................................................................................4-29 Examples...................................................................................................................................4-29 Format 13: Add Offset to Stack Pointer.................................................................................................4-30 Operation....................................................................................................................................4-30 Instruction Cycle Times................................................................................................................4-30 Examples...................................................................................................................................4-30。

第十七章实时时钟17.1概述实时时钟(RTC)单元在系统电源关闭的情况下可以在备用电池下工作。

RTC可以使用STRB/LDRB ARM操作传输二进制码十进制数的8位数据给CPU。

数据包括秒、分钟、小时、日期、天、月、年的时间信息。

RTC单元可以在32.768KHz的外部晶振下工作,可以可以执行报警功能。

17.2特点-BCD数:秒、分钟、小时、日期、日、月、年-闰年生成器-报警功能:报警中断或从掉电模式中唤醒-已经解决2000年问题-独立电源引脚(RTCVDD)-支持对于实时内核时间节拍的毫秒节拍时间中断17.3实时时钟操作17.3.1闰年发生器闰年发生器可以基于BCDDATE、BCDMON、BCDYEAR的数据,从28、29、30、31中确定每个月的最后一天。

该模块在确定某月最后一天的时候会考虑闰年的因素。

一个8位的计数器仅能代表两个BCD数字,所以它不能确定是否是00年(该年的最后两个数字是00)。

例如,它不能区别1900年和2000年。

为了解决这个问题,S3C2440A的RTC模块有一个硬件逻辑来支持在2000年的闰年。

记录1900年不是闰年而2000年是闰年。

因此两个数字00在S3C2440A中记录的是2000年而不是1900年。

17.3.2读写寄存器为了写RTC模块中的BCD寄存器,RTCCON寄存器的位0必须置1。

为了显示秒分小时星期日月年,CPU应该分别读取在RTC模块中的BCDSEC,BCDMIN,BCDHOUR,BCDDAY,BCDDATE,BCDMON,和BCDYEAR。

但是,因为多寄存器读取可能存在一秒的误差。

例如,当用户读BCDYEAR和BCDMON,结构假定是2059年12月31日23点59分。

当用户读BCDSEC寄存器,值的范围是从1到59(秒)就没有问题,但是如果值是0,年月日就变成了2060年1月1日0时0分因为有刚才提到的1秒误差。

在这种情况下如果BCDSEC为0,用户应该重读BCDYEAR到BCDSEC。

ARM-S3C2410A开发板硬件用户手册 开发板硬件用户手册北京三恒星科技公司北京三恒星科技公司目录前言 (4)一、系统组成 (4)1.1. 开发板资源 (4)1.1.1. 核心板 (5)1.1.2.扩展板 (8)1.2. 配件资源 (9)二、光盘资料 (10)三、ARM-S3C2410A的启动 (12)3.1. 开机画面(预装Linux+QT) (12)3.2. 开机画面(预装WinCE) (14)四、硬件模块详述 (16)4.1. 处理器 (17)4.2. 存储器 (19)4.2.1.SDRAM (20)4.2.2.Nand Flash存储器 (20)4.2.3.Nor Flash存储器 (20)4.3.UART 异步串行口 (21)4.4.USB接口 (22)4.5.以太网接口 (23)4.5.1.CS8900A作为主控芯片的10M以太网模块 (23)4.5.2.占用的系统资源 (24)4.5.3.网线选择 (24)4.6.音频模块 (24)4.6.1.采用IIS接口芯片UDA1314 (24)4.6.2.占用的系统资源 (25)4.6.3.LINE-IN端口定义 (25)4.7.SD/MMC卡接口 (26)4.7.1.SDI接口 (26)4.7.2.占用的系统资源 (26)4.8.IDE接口 (26)4.8.1 占用的系统资源 (27)4.9. 外部中断按键 (27)4.10. JTAG 接口 (27)4.11. LCD接口 (28)4.11.1.ARM-S3C2410A 的 LCD 接口简介 (28)4.11.2.STN屏对比度 (29)4.11.3.接口连线定义 (29)4.12.LCD模块 (30)五、SO-DIMM200接口定义 (32)六、扩展I/O口BUS-A/B接口定义 (34)七、硬件测试 (35)7.1. DNW下载器简介 (35)7.2. 硬件测试步骤 (36)7.2.1.配置DNW (37)7.2.2.连接硬件 (38)7.2.3.安装USB驱动 (40)7.2.4.下载2410Test (40)八、硬件调试环境 (43)8.1.对开发环境的支持 (43)8.2.对仿真器的支持 (44)九、Flash的烧录 (44)9.1. 连接JTAG编程电缆 (44)9.2. 安装giveio.sys (45)9.3. 烧写Nor Flash AM29LV800BB (47)9.4. 烧写Nand Flash K9S1208 (48)十、软件描述 (49)前言欢迎使用北京三恒星电子有限公司提供的ARM-S3C2410A系列嵌入式系统开发板产品!注意:本说明书适用于ARM-S3C2410A开发板。

第八章直接存储器存取概述s3c2440支持在系统总线和外围总线之间的4路DMA控制器。

每一路DMA控制器可以自由的执行数据在系统总线和(或)外围总线之间的动作。

换句话说,每一路可以在下列列4种情况下运行:1.源设备和目标设备都在系统总线上2.源设备在系统总线上,目标设备在外围总线上3.源设备在外围总线上,目标数据在系统总线上4.源设备和目标设备都在外围总线上DMA的主要优点是它可以不通过CPU直接调用数据。

DMA工执行可以软件开始,也可以从内部的外设请求或者外部的引脚请求开始。

DMA请求源每一路DMA控制器都可以从4种开始请求中选择一路,如果DCON寄存器选择H/W DAM 请求模式(注意,选择S/W时这个DMA请求源没意义)。

表8--1列出了4种请求和每一路的关系:表8--1.DMA开始请求和每一路关系这里nXDREQ0和nXDREQ1表示两个外部源(Extermal Devices),12SSDO和12SSDI分别表示IIS的传输和接收。

DMA 工作状态DMA应用3态FSN(有限状态机),它可以描述为以下3步:State--1. 作为起始状态,DMA等待DMA请求,一旦请求到来马上转到State--2,在这个状态,DMA ACK和INT REQ是0.State--2. 在这个状态,DMA ACK变为1,计数器(CURR_TC)从DCON[19:0]装载。

DMA ACK保持1,直到它被清0。

State--3. 在这个状态,控制DMA原子操作的子FSM被初始化了。

子FSM从源地址读取数据后把它写入目标地址。

在这个操作中,数据宽度和传输大小(单次或突发)应给与考虑。

在完整服务模式中,这种操作不断重复直到计数器(CURR_TC)变为0。

然而在单一模式中只进行一次,当子FSM完成每个原子操作时,主FSM对CURR_TC倒计时。

另外,当CURR_TC为0和中断设置DCON[29]为1 时,主FSM发出INT REQ信号(中断请求信号)。

另外,如果发生下列情况之一,DMA ACK将被清零。

1)在整体服务模式中CURR_TC变为02)在单一模式中原子操作完成注:在单一服务模式中,主FSM的三个状态进行然后停止,等待另外的DMA REQ。

如果DMA REQ到来,重复三种状态。

因此,DMA ACK被使能然后被取消后进行每一个原子操作。

相反的,在整体服务模式中,主FSM等待在state-3直到CURR_TC变为0。

所以,在TC到达0时,DMA ACK在传输区间被使能然后被取消。

总之,INT REQ被使能只由CURR_TC是否为0决定,与服务模式无关(单一服务模式或整体服务模式)。

应答((DREQ/DACK)协议外部DMA 请求/应答有三种类型的外部DMA请求/应答协议(单一需求模式、单一同步交换模式和整体同步交换模式)。

每一种类型定义这些协议涉及到什么样的DMA请求和应答信号。

基本DMA 时序图DMA服务意味着在DMA操作中执行一对读、写循环,它可以考试一个DMA操作。

图8--1显示了S3C2440DMA操作中的继电器——XnXDREQ和XnXDACK中的建立时间(serup)和延时时间(delay)在所有模式下都是相同的——如果XnXDREQ完成遇上建立时间,那么它将同步加强为原来的两倍,这是XnXDACK 被声明了——XnXDACK声明以后,DMA请求总线,如果到达总线则执行其操作,DMA操作完成后运行XnXDACK图8--1.基本DMA 时序图需求/同步交换模式比较需求和同步交换模式都涉及到XnXDREQ和XnXDACK协议。

图8--2指出了两种模式之间的不同在操作(单一/突发操作)最后,DMA组织双同步XnXDREQ。

需求模式—如果XnXDREQ尚未使能,那么下一个操作马上开始。

否则它一直等XnXDREQ被设为无效。

同步交换模式—如果XnXDREQ无效,DMA取消XnXDACK两个周期。

否怎,一直等XnXDREQ被设为无效。

注:XnXDREQ只在XnXDACK无效(hugh)后被使能(low)图8—2需求模式和同步交换模式比较传送容量—有两种不同的传输方式,unit和Burst 4—在传输大量数据时,DMA牢牢占据总线,因此其他总线主控不能得到总线Burst 4传输容量有四组连续的读、写操作在Burst 4中分别完成Unit传输型:执行单读、写注Unit图8--3.Burst 4Burst 4传输型举例举例Unit Unit传输容量的单一服务需求模式传输容量的单一服务需求模式传输容量的单一服务需求模式每一个Unit UnitUnit传输(单一服务模式)都需要XnXDREQ使能。

这个操作一直延续到XnXDREQ被使能(需求模式),一对读、写(单一传输容量)操作被执行。

图8--4.Unit Unit Unit传输容量的单一服务需求模式传输容量的单一服务需求模式Unit Unit传输容量的单一服务单同步交换模传输容量的单一服务单同步交换模传输容量的单一服务单同步交换模式式图8--5.Unit Unit传输容量的单一服务单同步交换模式传输容量的单一服务单同步交换模式Unit Unit传输容量的整体服务同步交换模式传输容量的整体服务同步交换模式传输容量的整体服务同步交换模式图8--6.Unit Unit传输容量的整体服务同步交换模式传输容量的整体服务同步交换模式DMA DMA专用寄存器专用寄存器专用寄存器每一路DMA有九个控制寄存器(4路一共有36个)。

其中6个控制寄存器控制DMA传输,另外的3个监听DMA控制器状态。

详细说明如下。

DMA 初始源寄存器DMA INITIAL SOURCE (DISRC) REGISTER DMA INITIAL SOURCE (DISRC) REGISTERDISRCCn DISRCCn Bit Bit 说明初始状态LOC[1]Bit 1用来选择源位置0:源在系统总线(AHB )上 1: 源在外围设备总线(APB )上INC [0] Bit 0用来选择地址增量 0=增加 1=不变如果为0,在突发和单一传出模式传输之后地址随数据量增加。

如果为1,地址在传输后不变。

(在突发模式,地址在传输过程中增加,但是在传输结束后恢复到初始值。

)寄存器寄存器寄存器 地址地址 R/W R/W 说明说明 重新赋值重新赋值 DISRC0 0x4B000000 R/W DMA 0 initial source register 0x00000000 DISRC1 0x4B000000 R/W DMA 1 initial source register 0x00000000 DISRC2 0x4B000000 R/W DMA 2 initial source register 0x00000000 DISRC3 0x4B000000R/WDMA 3 initial source register0x00000000DMA 初始目的寄存器DMA INITIAL DESTINATION (DIDST) REGISTER DMA INITIAL DESTINATION (DIDST) REGISTERDIDSTCn Bit 说明初始状态CHK_INT[2]在自动重装载被设置时,选择中断发生的时间。

0:TC 到达0时发生中断。

1:自动重装载完成后发生中断。

0LOC [1] Bit1用来选择目标文件位置0:目标文件在系统总线上(AHB ) 1:目标文件在外部设备总线上(APB ) 0INC [0] Bit 0用来选择地址增量 0=增加 1=不变如果为0,在所有单一和突发传输模式之后地址随数据量增加。

寄存器寄存器寄存器 地址地址 R/W R/W 说明说明 重新赋值重新赋值 DIDST0 0x4B000008 R/W DMA 0 initial destinationregister 0x00000000 DIDST1 0x4B000048 R/W DMA 1 initial destinationregister 0x00000000 DIDST2 0x4B000088 R/W DMA 2 initial destinationregister 0x00000000 DIDST3 0x4B00000B8R/WDMA 3 initial destinationregister0x00000000如果为1,传输之后地址不变。

(在突发模式中,地址在传输过程中增加,但在传输之后恢复成原来的值。

)DMA 控制寄存器DMA DMA CONTROL (DCON) REGISTER CONTROL (DCON) REGISTER CONTROL (DCON) REGISTER寄存器寄存器寄存器 地址地址 R/W R/W 说明说明 重新赋值重新赋值 DCON0 0x4B000010 R/W DMA 0 source register 0x00000000 DCON1 0x4B000050 R/W DMA1 source register 0x00000000 DCON2 0x4B000090 R/W DMA 2 source register 0x00000000 DCON3 0x4B0000D0R/WDMA 3 source register0x0000000010 = Word 11 = reservedTC[19:0]初始传输个数传输的字节数有下列公式计算:DSZ x TSZ x TC 。

其中DSZ,TSZ (1 or 4)和TC 分别表示DCONn[21:20]数据量,DCONn[28]传输量和初始传输个数。

只有到CURR_TC 为0并且DMA ACK 为1时,这个之被写入CURR_TC00000DMA 状态状态寄存器寄存器 DMA CONTROL (DCON) REGISTER DMA CONTROL (DCON) REGISTERDCSRCn DCSRCn Bit Bit 说明初始状态 CURR_SRC [30:0]适合DMAn 的当前源地址0x00000000寄存器寄存器寄存器 地址地址 R/W R/W 说明说明 重新赋值重新赋值 DCSRC0 0x4B000018 R DMA 0 当前源寄存器 0x00000000 DCSRC1 0x4B000058 R DMA1 当前源寄存器 0x00000000 DCSRC2 0x4B000098 R DMA 2 当前源寄存器 0x00000000 DCSRC3 0x4B0000D8RDMA 3 当前源寄存器 0x00000000当前目的寄存器当前目的寄存器 CURRENT DESTINATION (DCDST) REGISTER CURRENT DESTINATION (DCDST) REGISTER寄存器寄存器寄存器 地址地址 R/W R/W 说明说明 重新赋值重新赋值 DCDST0 0x4B00001C R DMA0 当前目的寄存器 0x00000000 DCDST1 0x4B00005C R DMA1 当前目的寄存器 0x00000000 DCDST2 0x4B00009C R DMA 2 当前目的寄存器 0x00000000 DCDST3 0x4B0000DCRDMA 3 当前目的寄存器0x00000000S3C2440A 数据手册 保定飞凌嵌入式技术有限公司 马志晶 mazhijing@11 9/10/2007 当DCON[22]位是“不自动重启”,这位在CURR_TC 为0时变为0。