Notebook:

[03] 工具Created:

2014/7/12 14:49Updated:2014/7/12 14:49Tags:

仿真URL:https://www.doczj.com/doc/6010588084.html,/s/blog_56defcc301012gl5.html

TINA-TI中仿真非TI公司芯片SPICE的方法

TINA-TI中仿真非TI公司芯片SPICE的方法

(2012-08-04 16:51:42)标签: 仿真工具分类: 模拟电路

TINA是DesignSoft公司仿真软件,能仿真所有厂家芯片SPICE文件,但需要购买,很贵的。而TINA-TI是TI公司的一个定制版本,完全FREE,只是缺省只包含TI公司芯片的仿真SPICE文件。9.0以后版本缺省包括TI和国办所有芯片,只需从库中选择具体型号即可。很方便。但对于其他厂家如ADI,LINEAR,MAXIM等的芯片仿真就没这么简单了,不能直接加载库文件,如ADI公司的anlg_dev.lib,因为还需要TI公司制作的库索引文件XXX.IND和XXX.TLD,如果直接拷贝过来,TINA是编译不过的。但TINA-TI留了一个小口,即可以单个通过创建宏加载【这已经是很大进步了,9.0之前的版本连这个功能都没有,无法仿真非TI公司产品】

下面举例说明仿真过程(以AD8639为例):

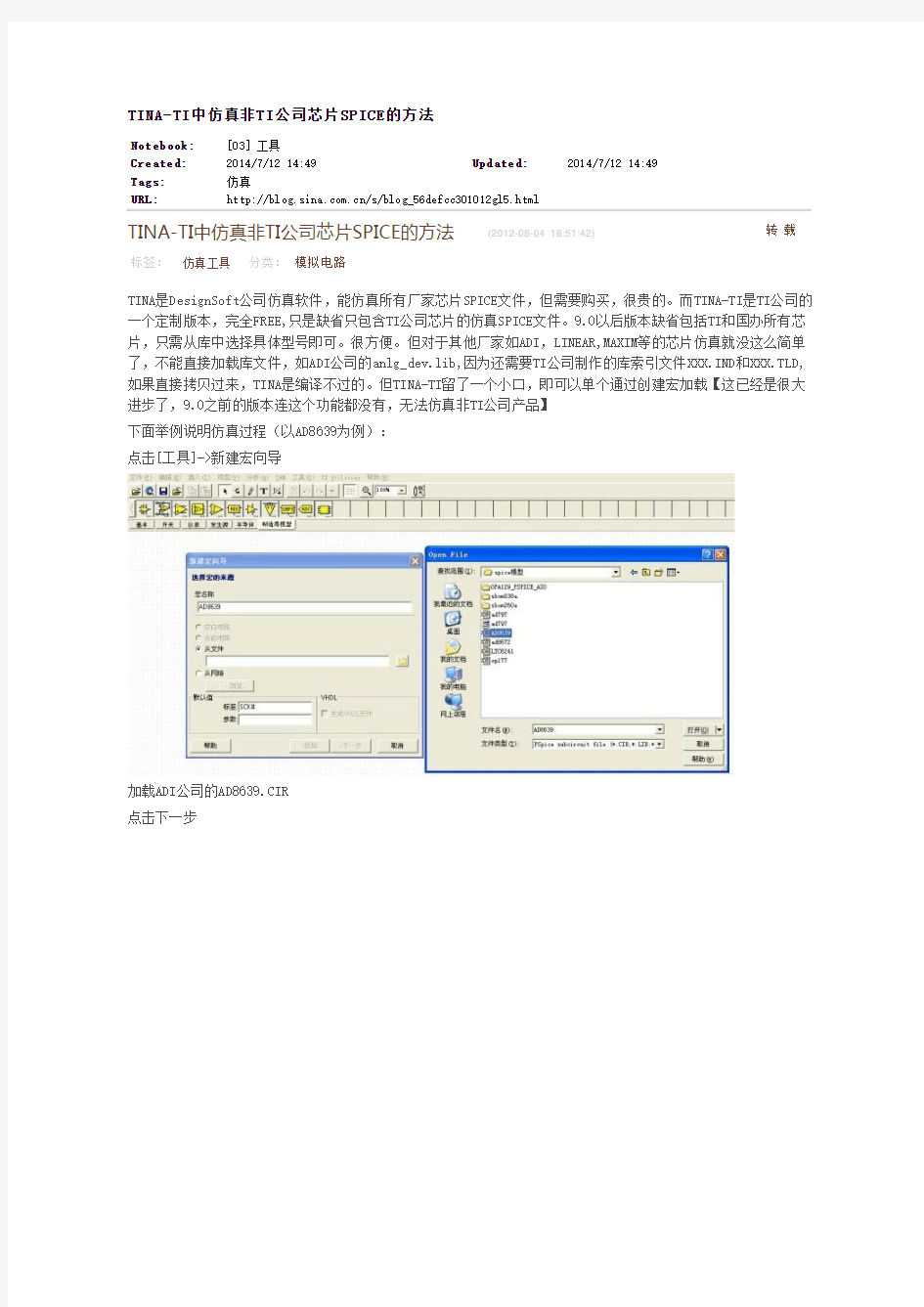

点击[工具]->新建宏向导

加载ADI公司的AD8639.CIR

点击下一步

转载▼

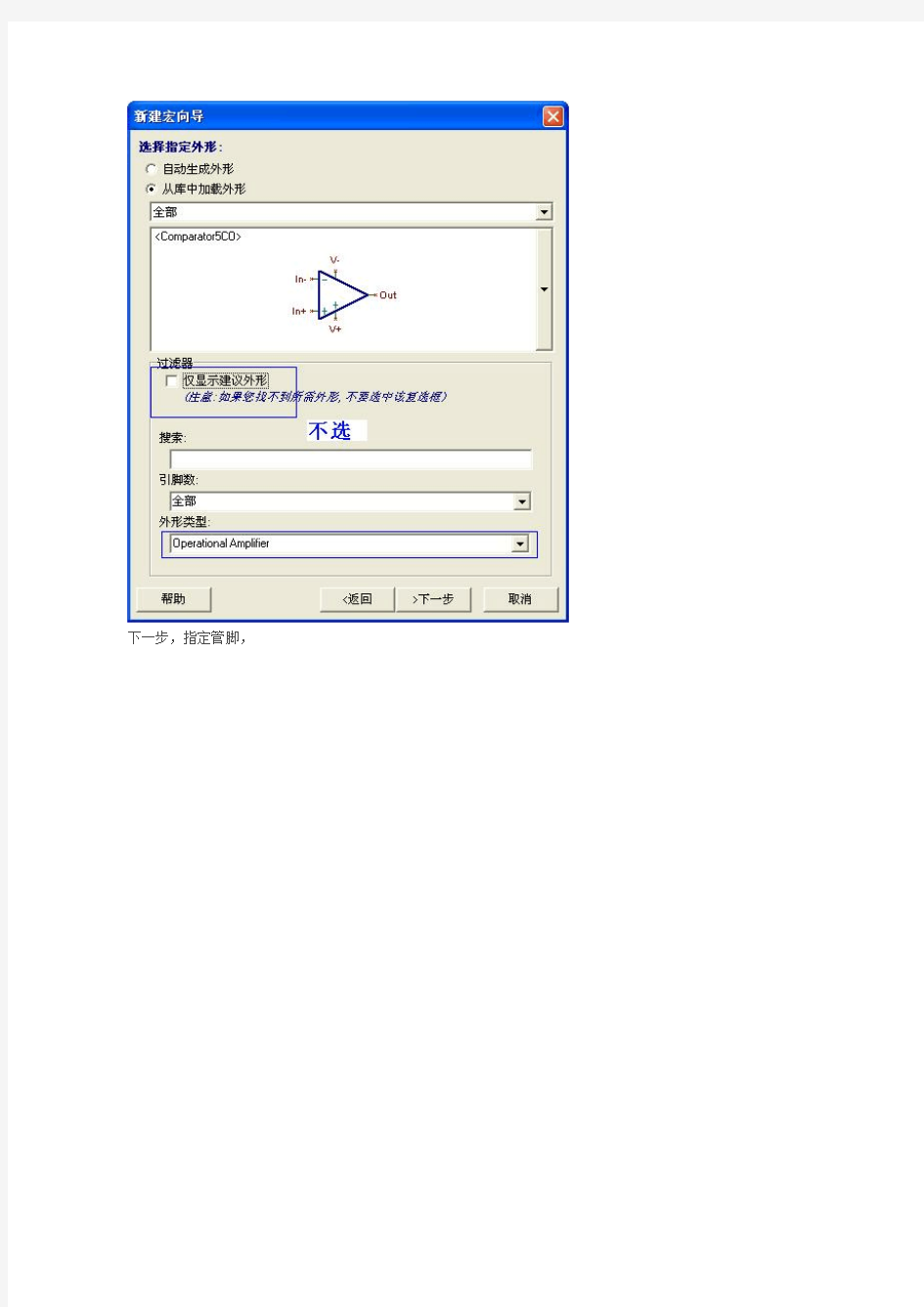

下一步,指定管脚,

接下来保存宏,并选择插入即可

最后,AD8639的SYMBOL就出现了。

体会:

1)对比ORCAD和TINA,对于新的器件(库里没有的),加载过程还是TINA简单一些,ORCAD还要先转换,还得重新命名管脚,往库里手工加载,很麻烦的。【日后有空,把ORCAD的新器件仿真过程写出来】

2)对于时域,频域以及噪声分析,无论从参数设置还是显示效果来看,还是感觉TINA简单一些。(有些主观,这跟使用习惯有关)

3)ORCAD毕竟是第三方通用仿真工具,支持的厂家器件远比TINA-TI多得多。

混频器仿真实验 姓名:贾炜光 学号:20151060042 学院:信息学院 专业:通信工程 指导教师:谢汝生

一、实验目的 (1)加深对混频理论方面的理解,提高用程序实现相关信号处理的能力; (2)掌握multisim实现混频器混频的方法和步骤; (3)掌握用muitisim实现混频的设计方法和过程,为以后的设计打下良好的基础。 二.实验原理 混频器将天线上接收到的射频信号与本振产生的信号相乘,cosαcosβ=[cos(α+ β)+cos(α-β)]/2 可以这样理解,α为射频信号频率量,β为本振频率量,产生和差频。当混频的频率等于中频时,这个信号可以通过中频放大器,被放大后,进行峰值检波。检波后的信号被视频放大器进行放大,然后显示出来。由于本振电路的振荡频率随着时间变化,因此频谱分析仪在不同的时间接收的频率是不同的。 混频是指将信号从一个频率变换到另外一个频率的过程 ,其实质是频谱线性搬移的过程。在超外差接收机中 ,混频的目的是保证接收机获得较高的灵敏度 ,足够的放大量和适当的通频带 ,同时又能稳定地工作。混频电路包括三个组成部分 : 本机振荡器、非线性器件、带通滤波器。[1] 由于非线性元件( 如二极管、三极管、场效应管等) 的作用,混频过程中会产生很多的组合频率分量 : p f L ±qf S 。一般来讲 ,其中满足需要的仅仅是 f I =f L -f S 或者是f I =f S -f L 。前者产生中频的方式称为高差式混频 , 后者称为低差式混频。在这里 ,混频过程中产生的一系列组合频率分量经过带通滤波器即可以选择输出相应的中频 ,而其他的频率分量会得到抑制。

单片机系统测试报告 题目:单片机控制LED数码管显示数字 姓名: 学号: 指导老师: 专业:电子信息工程 院系:计算机与信息工程学院 2015年6月

目录 第一章设计任务及要求 (3) 1.1 设计任务 (3) 1.2 设计要求 (3) 第二章芯片引脚功能图及源程序设计 (3) 2.1 各芯片引脚图 (3) 2.2在Keil软件设计C语言源程序 (4) 第三章 Protues绘制电路原理图及仿真 (6) 3.1 绘制电路原理图 (6) 3.2 Protues仿真 (7) 第四章电路板的焊接与硬件调试 (7) 4.1 电路板的焊接 (7) 4.2 硬件调试 (7) 第五章心得体会 (8)

第一章设计任务及要求 1.1设计任务 利用51单片机、74HC573芯片、2片位4位数码管等器件,设计一个单片机输入显示系统。巩固Proteus软件和Keil软件的使用方法,学习端口输入输出的高级应用。 1.2 设计要求 要求八个数码管按顺序依次显示1~8 第二章芯片引脚功能图及源程序设计 2.1 各芯片引脚图 图2.1-1 AT89C52引脚图图2.1-2 74HC573引脚图

图2.1-3 四位一体数码管引脚图2.2在Keil软件设计C语言源程序 #include

芯片封装方式大全 各种IC封装形式图片 BGA Ball Grid Array EBGA 680L LBGA 160L PBGA 217L Plastic Ball Grid Array SBGA 192L QFP Quad Flat Package TQFP 100L SBGA SC-70 5L SDIP SIP Single Inline Package

TSBGA 680L CLCC CNR Communicatio n and Networking Riser Specification Revision 1.2 CPGA Ceramic Pin Grid Array DIP Dual Inline Package SO Small Outline Package SOJ 32L SOJ SOP EIAJ TYPE II 14L SOT220 SSOP 16L

DIP-tab Dual Inline Package with Metal Heatsink FBGA FDIP FTO220 Flat Pack HSOP28SSOP TO18 TO220 TO247 TO264 TO3

ITO220 ITO3p JLCC LCC LDCC LGA LQFP PCDIP TO5 TO52 TO71 TO72 TO78 TO8 TO92

PGA Plastic Pin Grid Array PLCC 详细规格PQFP PSDIP LQFP 100L 详细规格METAL QUAD 100L 详细规格PQFP 100L 详细规格TO93 TO99 TSOP Thin Small Outline Package TSSOP or TSOP II Thin Shrink Outline Package uBGA Micro Ball Grid Array uBGA Micro Ball Grid

现在常用的SPICE仿真软件为方便用户使用都提供了较好的用户界面,在用仿真库中的元器件连成原理图后就可以进行仿真(当然要设置必要的仿真参数),但实际上只是用原理图自动产生了SPICE的格式语句,还是要通过读取语句来进行仿真,这是历史的遗留问题。 在当时的技术条件下,不能用图形方式输入电路结构,只能通过文本文件来描述,也就是所谓网表。SPICE软件的设计者规范了要进行仿真的电路对应的SPICE网表文件格式,还定义了许多仿真描述语句和分析控制语句等,使仿真软件能通过读取这些特殊信息来进行相关计算和运行,最后获得要求的结果。 因为技术的进步,虽然现在已经不需要手工书写并输入网表了,但了解一些基本语句还是很有用的,不仅可以理解仿真时要设置的那些参数的含义,而且在出错时还易于通过网表来排错。 SPICE网表文件是文本文件,默认的输入文件名为:*.cir 因为目前各个版本的SPICE软件都已图形化,并增加了很多功能,所以产生的语句顺序和格式有了一些变化,但主要是以*开头的注释语句的不同变化,便于阅读和模块化,而基本的语句变化不大,包括以下几种: 1) 标题语句:网表文件第一行为标题语句,由任意字符串和字母组成,软件并不处理,而是直接在输出文件中作为第一行打印出来 2) 注释语句:由*开头的字符串,为文件的说明部分,为方便阅读而在自动产生的SPICE网表文件中大量存在 3) 电路描述语句:定义电路拓扑结构和元器件参数的语句,由元器件描述语句、模型描述语句、电源语句等组成 4) 电路特性分析和控制语句:以.开头的语句,描述要分析的电路特性及控制命令 5) 结束语句:即.END ,标志电路描述语句的结束,在文件最后一行 (最后将会给出SPICE网表文件的例子) 一、电路描述语句:是SPICE网表文件中最多也最复杂的,有以下一些规定: 1) 名称:为字符串,只有前8个字符有效,其中第一个字符必须为A--Z的字符,且有固定含义,对应不同类型的元件 2) 数字:有几种形式,整数、浮点数、整数或浮点数加上整数指数、浮点数或整数后面加上比例因子 常用的比例因子:有T、G、MEG、K、M、U、N、P、F、MIL等,不分大小写 3) 分隔符:有空格、逗号、等号、左括号、右括号等 4) 续行号:“+”,一行最多只能有80字符,如一行无法表达完全,可在第二行起始加+号,表示是前一行的继续 5) 单位:使用国际标准单位制,语句中缺省 6) 规定支路电流的正方向和支路电压的正方向一致 7) 节点编号:可以是任意的数字或字符串,节点0规定为地,不允许有悬浮的节点,即每个节

高频实验报告 班级班级 学号学号 姓名姓名 预习成绩预习成绩 实验成绩实验成绩 实验报告成绩实验报告成绩 总成绩总成绩 2013年 12月

实验一、调幅发射系统实验 一、实验目的与内容: 通过实验了解与掌握调幅发射系统,了解与掌握LC三点式振荡器电路、三极管幅度调制电路、高频谐振功率放大电路。 二、实验原理: 1、LC三点式振荡器电路: 原理:LC三点式振荡器电路是采用LC谐振回路作为相移网络的LC正弦波振荡器,用来产生稳定的正弦振荡。图中5R5,5R6,5W2和5R8为分压式偏置电阻,电容5C7或5C8或5C9或5C10或5C11进行反馈的控制。5R3、5W1、5L2以及5C4构成的回路调节该电路的振荡频率,在V5-1处输出频率为30MHZ 正弦振荡信号。 2、三极管幅度调制电路: 原理:三极管幅度调制电路是通过输入调制信号和载波信号,在它们的共同

作用下产生所需的振幅调制信号。图中7R1,7R4,7W1和7R3为分压式偏置电阻,电容7C10、7C2以及电感7L1构成的谐振滤波网络,7W2控制输出幅度,在信号输出处输出所需的振幅调制信号。 3、高频谐振功率放大电路: 原理:高频谐振功率放大电路是工作频率在几十MHZ 到几百MHZ 的谐振功率放大电路。图中前级高频功放电路中,6R2和6R3分压式偏置电阻,供给三极管6BG1偏置电压,输出采用6C5、6C6、6L1构成的T 型滤波匹配网络,末级高频功放电路中,基极采用由6R4产生偏置电压供给电路,输出采用6C13、6C13、6L3和6L4构成的T 型滤波匹配网络。 4、调幅发射系统: 图1 调幅发射系统结构图 原理:首先LC 振荡电路产生一个频率为30MHZ ,幅度为100mV 的信号源,然后加入频率为1KHZ ,幅度为100mV 的本振信号,通过三极管幅度调制,再经过高频谐振功率放大器输出稳定的最大不失真的正弦波。 本振 功率 放大 调幅 信源

封装有两大类;一类是通孔插入式封装(through-hole package);另—类为表面安装式封装(surface moun te d Package)。每一类中又有多种形式。表l和表2是它们的图例,英文缩写、英文全称和中文译名。图6示出了封装技术在小尺寸和多引脚数这两个方向发展的情况。 DIP是20世纪70年代出现的封装形式。它能适应当时多数集成电路工作频率的要求,制造成本较低,较易实现封装自动化印测试自动化,因而在相当一段时间内在集成电路封装中占有主导地位。 但DIP的引脚节距较大(为2.54mm),并占用PCB板较多的空间,为此出现了SHDIP和SKDIP等改进形式,它们在减小引脚节距和缩小体积方面作了不少改进,但DIP最大引脚数难以提高(最大引脚数为64条)且采用通孔插入方式,因而使它的应用受到很大限制。 为突破引脚数的限制,20世纪80年代开发了PGA封装,虽然它的引脚节距仍维持在2.54mm或1.77mm,但由于采用底面引出方式,因而引脚数可高达500条~600条。 随着表面安装技术(surface mounted technology, SMT)的出现,DIP封装的数量逐渐下降,表面安装技术可节省空间,提高性能,且可放置在印刷电路板的上下两面上。SOP应运而生,它的引脚从两边引出,且为扁平封装,引脚可直接焊接在PCB板上,也不再需要插座。它的引脚节距也从DIP的2.54 mm减小到1.77mm。后来有SSOP和TSOP改进型的出现,但引脚数仍受到限制。 QFP也是扁平封装,但它们的引脚是从四边引出,且为水平直线,其电感较小,可工作在较高频率。引脚节距进一步降低到1.00mm,以至0.65 mm和0.5 mm,引脚数可达500条,因而这种封装形式受到广泛欢迎。但在管脚数要求不高的情况下,SOP以及它的变形SOJ(J型引脚)仍是优先选用的封装形式,也是目前生产最多的一种封装形式。 方形扁平封装-QFP (Quad Flat Package) [特点] 引脚间距较小及细,常用于大规模或超大规模集成电路封装。必须采用SMT(表面安装技术)进行焊接。操作方便,可靠性高。芯片面积与封装面积的比值较大。 小型外框封装-SOP (Small Outline Package) [特点] 适用于SMT安装布线,寄生参数减小,高频应用,可靠性较高。引脚离芯片较远,成品率增加且成本较低。芯片面积与封装面积比值约为1:8 小尺寸J型引脚封装-SOJ (Smal Outline J-lead) 有引线芯片载体-LCC (Leaded Chip Carrier) 据1998年统计,DIP在封装总量中所占份额为15%,SOP在封装总量中所占57%,QFP则占12%。预计今后DIP的份额会进一步下降,SOP也会有所下降,而QFP会维持原有份额,三者的总和仍占总封装量的80%。 以上三种封装形式又有塑料包封和陶瓷包封之分。塑料包封是在引线键合后用环氧树脂铸塑而成,环氧树脂的耐湿性好,成本也低,所以在上述封装中占有主导地位。陶瓷封装具有气密性高的特点,但成本较高,在对散热性能、电特性有较高要求时,或者用于国防军事需求时,常采用陶瓷包封。 PLCC是一种塑料有引脚(实际为J形引脚)的片式载体封装(也称四边扁平J形引脚封装QFJ (quad flat J-lead package)),所以采用片式载体是因为有时在系统中需要更换集成电路,因而先将芯片封装在一种载体(carrier)内,然后将载体插入插座内,载体和插座通过硬接触而导通的。这样在需要时,只要在插座上取下载体就可方便地更换另一载体。 LCC称陶瓷无引脚式载体封装(实际有引脚但不伸出。它是镶嵌在陶瓷管壳的四侧通过接触而导通)。有时也称为CLCC,但通常不加C。在陶瓷封装的情况下。如对载体结构和引脚形状稍加改变,载体的引脚就可直接与PCB板进行焊接而不再需要插座。这种封装称为LDCC即陶瓷有引脚片式载体封装。 TAB封装技术是先在铜箔上涂覆一层聚酰亚胺层。然后用刻蚀方法将铜箔腐蚀出所需的引脚框架;再在聚酰亚胺层和铜层上制作出小孔,将金属填入铜图形的小孔内,制作出凸点(采用铜、金或镍等材料)。由这些凸点与芯片上的压焊块连接起来,再由

常见芯片封装类型的汇总 芯片封装,简单点来讲就是把制造厂生产出来的集成电路裸片放到一块起承载作用的基板上,再把管脚引出来,然后固定包装成为一个整体。它可以起到保护芯片的作用,相当于是芯片的外壳,不仅能固定、密封芯片,还能增强其电热性能。所以,封装对CPU和其他大规模集成电路起着非常重要的作用。 今天,与非网小编来介绍一下几种常见的芯片封装类型。 DIP双列直插式 DIP是指采用双列直插形式封装的集成电路芯片,绝大多数中小规模集成电路均采用这种封装形式,其引脚数一般不超过100个。采用DIP封装的CPU芯片有两排引脚,需要插入到具有DIP结构的芯片插座上。当然,也可以直接插在有相同焊孔数和几何排列的电路板上进行焊接。DIP封装的芯片在从芯片插座上插拔时应特别小心,以免损坏引脚。DIP封装结构形式有多层陶瓷双列直插式DIP,单层陶瓷双列直插式DIP,引线框架式DIP (含玻璃陶瓷封接式,塑料包封结构式,陶瓷低熔玻璃封装式)等。 DIP是最普及的插装型封装,应用范围包括标准逻辑IC,存储器和微机电路等。 DIP封装 特点: 适合在PCB(印刷电路板)上穿孔焊接,操作方便。 芯片面积与封装面积之间的比值较大,故体积也较大。 最早的4004、8008、8086、8088等CPU都采用了DIP封装,通过其上的两排引脚可插到主板上的插槽或焊接在主板上。 在内存颗粒直接插在主板上的时代,DIP 封装形式曾经十分流行。DIP还有一种派生方式SDIP(Shrink DIP,紧缩双入线封装),它比DIP的针脚密度要高六倍。 现状:但是由于其封装面积和厚度都比较大,而且引脚在插拔过程中很容易被损坏,可靠性较差。同时这种封装方式由于受工艺的影响,引脚一般都不超过100个。随着CPU内

电磁场与微波技术 实验报告 院系: 班级: 姓名: 学号: 指导老师:

实验一线驻波比波长频率的测量 一、实验目的 1、熟练认识和了解微波测试系统的基本组成和工作原理。 2、掌握微波测试系统各组件的调整和使用方法。 3、掌握用交叉读数法测波导波长的过程。 二、实验用微波元件及设备简介 1.波导管:本实验所使用的波导管型号为BJ—100,其内腔尺寸为α=22.86mm,b=10.16mm。其主模频率范围为8.20~12.50GHz,截止频率为6.557GHz。2.隔离器:位于磁场中的某些铁氧体材料对于来自不同方向的电磁波有着不同的吸收,经过适当调节,可使其对微波具有单方向传播的特性(见图1)。隔离器常用于振荡器与负载之间,起隔离和单向传输作用。 3.衰减器:把一片能吸收微波能量的吸收片垂直于矩形波导的宽边,纵向插入波导管即成(见图2),用以部分衰减传输功率,沿着宽边移动吸收片可改变衰减量的大小。衰减器起调节系统中微波功率以及去耦合的作用。 图 1 隔离器结构示意图图2 衰减其结构示意图 4.谐振式频率计(波长表): 图3 a 谐振式频率计结构原理图一图3 b 谐振式频率计结构原理图二 1. 谐振腔腔体 1. 螺旋测微机构 2. 耦合孔 2. 可调短路活塞 3. 矩形波导 3. 圆柱谐振腔 4. 可调短路活塞 4. 耦合孔 5. 计数器 5. 矩形波导 6. 刻度 7. 刻度套筒 电磁波通过耦合孔从波导进入频率计的空腔中,当频率计的腔体失谐时,腔里的电磁场极为微弱,此时,它基本上不影响波导中波的传输。当电磁波的频率

满足空腔的谐振条件时,发生谐振,反映到波导中的阻抗发生剧烈变化,相应地,通过波导中的电磁波信号强度将减弱,输出幅度将出现明显的跌落,从刻度套筒可读出输入微波谐振时的刻度,通过查表可得知输入微波谐振频率。(图3a) 或从刻度套筒直接读出输入微波的频率(图3b)。两种结构方式都是以活塞在腔体中位移距离来确定电磁波的频率的,不同的是,图3a读取刻度的方法测试精度较高,通常可做到5×10-4,价格较低。而见图3b直读频率刻度,由于在频率刻度套筒加工受到限制,频率读取精度较低,一般只能做到3×10-3左右且价格较高。 5.驻波测量线:驻波测量线是测量微波传输系统中电场的强弱和分布的精密仪器。在波导的宽边中央开有一个狭槽,金属探针经狭槽伸入波导中。由于探针与电场平行,电场的变化在探针上感应出的电动势经过晶体检波器变成电流信号输出。 6.匹配负载:波导中装有很好地吸收微波能量的电阻片或吸收材料,它几乎能全部吸收入射功率。 7.微波源:提供所需微波信号,频率范围在8.6~9.6GHz内可调,工作方式有等幅、方波、外调制等,实验时根据需要加以选择。 8.选频放大器:用于测量微弱低频信号,信号经升压、放大,选出1kHz附近的信号,经整流平滑后由输出级输出直流电平,由对数放大器展宽供给指示电路检测。 三、实验内容及过程 1.微波信号源的调整: 频率表在点频工作下,显示等幅波工作频率,在扫频工作下显示扫频工作频率,在教学下,此表黑屏。电压表显示体效应管的工作电压,常态时为12.0 0.5V,教学工作下可通过“电压调节钮”来调节。电流表显示体效应管的工作电流,正常情况小于500毫安。 2.测量线探针的调谐: 我们使用的是不调谐的探头,所以在使用中不必调谐,只是通过探头座锁紧螺钉可以将不调谐探头活动2mm。 3.用波长计测频率: (1)在测量线终端接上全匹配负载。 (2)仔细微旋波长计的千分尺,边旋边观测指示器读数。由于波长计的q值非常 高,谐振曲线非常尖锐,千分尺上0.01mm的变化都可能导致失谐与谐振两种状态之间切换,因此,一定慢慢地仔细微旋千分尺。记下指示器读数为最小时(注意:如果检流指示器出现反向指示,按下其底部的按钮,读数即可)的千分尺读数并使波长计失谐。 (3)由读得的千分尺刻度可在该波长计的波长表频率刻度对照表上读得信号源的工作频率。 4.交叉读数法测量波导波长: (1)检查系统连接的平稳,工作方式选择为方波调制,使信号源工作于最佳状态。 (2)用直读式频率计测量信号频率,并配合信号源上的频率调谐旋钮调整信号源的工作频率,使信号源的工作频率为9370MHz。

元器件封装类型: A. Axial轴状的封装(电阻的封装) AGP (Accelerate raphical Port)加速图形接口 AMR(Audio/MODEM Riser) 声音/调制解调器插卡 B BGA(Ball Grid Array) 球形触点阵列,表面贴装型封装之一。在印刷基板的背面按阵列方式制作出球形凸点用以代替引脚,在印刷基板的正面装配LSI 芯片,然后用模压树脂或灌封方法进行密封。也称为凸点阵列载体(PAC) BQFP(quad flat package with bumper) 带缓冲垫的四侧引脚扁平封装。QFP封装之一,在封装本体的四个角设置突(缓冲垫)以防止在运送过程中引脚发生弯曲变形。 C 陶瓷片式载体封装 C-(ceramic) 表示陶瓷封装的记号。例如,CDIP 表示的是陶瓷DIP。 Cerdip 用玻璃密封的陶瓷双列直插式封装,用于ECL RAM,DSP(数字信号处理器)等电路。带有玻璃窗口的Cerdip 用于紫外线擦除型EPROM 以及内部带有EPROM 的微机电路等。 CERQUAD(Ceramic Quad Flat Pack) 表面贴装型封装之一,即用下密封的陶瓷QFP,用于封装DSP 等的逻辑LSI 电路。带有窗口的Cerquad 用于封装EPROM 电路。散热性比塑料QFP 好,在自然空冷条件下可容许1.5~2W 的功率 CGA(Column Grid Array) 圆柱栅格阵列,又称柱栅阵列封装 CCGA(Ceramic Column Grid Array) 陶瓷圆柱栅格阵列

CNR是继AMR之后作为INTEL的标准扩展接口 CLCC 带引脚的陶瓷芯片载体,引脚从封装的四个侧面引出,呈丁字形。带有窗口的用于封装紫外线擦除型EPROM 以及带有EPROM 的微机电路等。此封装也称为QFJ、QFJ-G COB(chip on board) 板上芯片封装,是裸芯片贴装技术之一,半导体芯片交接贴装在印刷线路板上,芯片与基板的电气连接用引线缝合方法实现,芯片与基板的电气连接用引线缝合方法实现,并用树脂覆 盖以确保可靠性。 CPGA(Ceramic Pin Grid Array) 陶瓷针型栅格阵列封装 CPLD 复杂可编程逻辑器件的缩写,代表的是一种可编程逻辑器件,它可以在制造完成后由用户根据自己的需要定义其逻辑功能。CPLD 的特点是有一个规则的构件结构,该结构由宽输入逻辑单元组成,这种逻辑单元也叫宏单元,并且CPLD 使用的是一个集中式逻辑互连方案。CQFP 陶瓷四边形扁平封装(Cerquad),由干压方法制造的一个陶瓷封装家族。两次干压矩形或正方形的陶瓷片(管底和基板)都是用丝绢网印花法印在焊接用的玻璃上再上釉的。玻璃然后被加热并且引线框被植入已经变软的玻璃底部,形成一个机械的附着装置。一旦半导体装置安装好并且接好引线,管底就安放到顶部装配,加热到玻璃的熔点并冷却。 fly_shop 2008-6-19 14:07 D.陶瓷双列封装 DCA(Direct Chip Attach) 芯片直接贴装,也称之为板上芯片技术(Chip-on-Board 简称COB),是采用粘接剂或自动带焊、丝焊、倒装焊等方法,将裸露的集成电路芯片直接贴装在电路板上的一项技术。倒装芯片是COB中的一种(其余二种为引线键合和载带自动键合),它将芯片有源区面对基板,通过芯片上呈现阵列排列的焊料凸点来实现芯片与衬底的互连。 DICP(dualtape carrier package) 双侧引脚带载封装。TCP(带载封装)之一。引脚制作在绝缘带上并从封装两侧引出。

实验报告 实验目的: 1. 静态测试555的逻辑功能。 2. 动态测试555的电压传输特性曲线。 3. 用555设计一个数字定时器,每启动一次,电路产生一个宽度大约为5s 左右 的脉冲。 实验器材: 实验箱、示波器、555芯片、万用表。 实验资料: 实验内容: (1) 静态测试555的逻辑功能 1. 根据555的管脚图,2、6接入5V 可调电压,7、3接二极管显示灯,4、8接 5V 电压端,5悬空,1接地,连接好电路。 学号: 班级: 姓名:

2.改变触发端的电压大小,观察二极管指示灯的状态。记录输入端和输出以及二 极管两端的电压,记录下二极管指示灯由低变高的输入输出电压。 3.整理实验数据,分析实验结果。、 (2)动态测试555电压传输特性曲线 1.设计好积分电路,用示波器调出三角波。 2.2、6接入三角波,通道2接输出,调整直至出现合适的波形。 3.读数记录相关参数,分析数据整理数据。 (3)用555设计一个数字定时器,每启动一次,电路产生一个宽度大约为5s左右的脉冲。 1.设计出合适的电路,连接电路。 2.用示波器调整出正确的波形。 3.读数,整理数据并分析数据。 实验电路图: (1)静态测试555逻辑功能 (2)动态测试555电压传输特性曲线 积分电路: Ch1通道接电阻旁边的黑色节点,CH2接输出。 (3)定时电路电路图

(1)静态测试555的逻辑功能 1.用示波器和积分电路作出的三角波

2.将三角波加入到输入端 由动态测试出电压从0~5V变化时二极管状态发生跳变的电压是1.76V。电压从5V~0V变化时二极管状态发生跳变的是3.44V。如图数据显示。两组数据与静态测试的数据大致符合,实验得证。 (3)定时电路

大连理工大学 本科实验报告 课程名称:电子系统仿真实验 学院(系):信息与通信工程学院 专业:电子与信息工程 班级: 学号: 学生姓名: 2014年月日

一、 实验目的和要求 使用电路分析软件,运用所学知识,设计一个晶体管混频器。要求输入频率为10MHz ,本振频率为16.485MHz 左右,输出频率为6.485MHz 。本振电路为LC 振荡电路。 二、实验原理和内容 混频电路是一种频率变换电路,是时变参量线性电路的一种典型应用。如一个振幅较大的振荡电压(使器件跨导随此频率的电压作周期变化)与幅度较小的差频或和频,完成变频作用。它是一个线性频率谱搬电路。图2.1是其组成模型框图。 中频 图2.1 本地振荡器产生稳定的振荡信号(设其频率为L f )通过晶体管混频电路和输入的高频调幅波信号(设其频率为s f ),由于晶体管的非线性特性,两个信号混合后会产生L f +s f L f -s f 频率的信号,然后通过中频滤波网络,取出L f -s f 频率的信号,调节好L f -s f 的大 小使其差为中频频率,即所需要的中频输出信号。图 2.2调幅前后的频谱图。 图2.2 本次试验本振电路采用LC 振荡电路。其等效原理图为西勒振荡电路,如图2.3所示。 本振电路 非线性器件 输入 中频滤波 输出

图2.3 混频器采用晶体混频电路,其等效电路图如图2.4。 图2.4 三、主要仪器设备 名称型号主要性能参数 电子计算机宏碁V-531,Windows 7 AMD A10-4600M 2.3GHz,2GB 内存 电路分析软件 Multisim.12 多种电路元件,多种虚拟仪 器多种分析方法 表3.1

混频器实验(虚拟实验) 姓名:郭佩学号:04008307 (一)二极管环形混频电路 傅里叶分析 得到的频谱图为 分析:可以看出信号在900Hz和1100Hz有分量,与理论相符 (二)三极管单平衡混频电路 直流分析

傅里叶分析 一个节点的傅里叶分析的频谱图为 两个节点输出电压的差值的傅里叶分析的频谱图为:

分析:同样在1K的两侧有两个频率分量,900Hz和1100Hz 有源滤波器加入电路后 U IF的傅里叶分析的频谱图为: U out节点的傅里叶分析的频谱图为:

分析:加入滤波器后,会增加有2k和3k附近的频率分量 (三)吉尔伯特单元混频电路 直流分析 傅里叶分析 一个节点的输出电压的傅里叶分析的参数结果与相应变量的频谱图如下: 两个节点输出电压的差值的傅里叶分析的参数结果与相应变量的频谱图为:

分析:1k和3k两侧都有频率分量,有IP3失真 将有源滤波器加入电路 U IF的傅里叶分析的参数结果与相应变量的频谱图为: U out节点的傅里叶分析的参数结果与相应变量的频谱图为:

分析:有源滤波器Uout节点的傅里叶分析的频谱相对于Uif的傅里叶分析的频谱来说,其他频率分量的影响更小,而且Uout节点的输出下混频的频谱明显减小了。输出的电压幅度有一定程度的下降。 思考题: (1)比较在输入相同的本振信号与射频信号的情况下,三极管单平衡混频电路与吉尔伯特混频器两种混频器的仿真结果尤其是傅里叶分析结果的差异,分析其中的原因。若将本振信号都设为1MHz,射频频率设为200kHz,结果有何变化,分析原因。 答:没有改变信号频率时 三极管 吉尔伯特 吉尔伯特混频器没有1k、2k、3k处的频率分量,即没有本振信号的频率分量,只有混频后的频率分量。因为吉尔伯特混频器是双平衡对称电路结果,有差分平衡。 将本振信号频率和射频频率改变后:

实验三 MOS管参数仿真及Spice学习 刘翔 10214070 一、实验内容和要求。 实验内容: (1)使用S-Edit绘制电路图,将其转换成Spice文件。 (2)利用T-Spice的对话框添加仿真命令。 (3)利用W-Edit观察波形。 实验要求: (1)利用Tanner软件中的S-Edit、T-Spice和W-Edit,对NMOS管的参数进行仿真。NMOS器件的T-Spice参数仿真内容如下: a. MOS管转移特性曲线(给定VDS、W、L,扫描VGS)。 b. MOS管输出特性曲线(给定VGS、W、L,扫描VDS)。 c. 温度对MOS管输入/输出特性的影响(给定VGS、VDS、W、L,扫描Temp)。 d. MOS管W对输入/输出特性的影响(给定VGS、VDS、W/L,扫描W)。 e. MOS管L对输入/输出特性的影响(给定VGS、VDS、W/L,扫描L)。 f. MOS管W/L对输入/输出特性的影响(给定VGS、VDS、L,扫描W)。 g. MOS管开关电路输入/输出波形(输入一定频率的方波)。 h. 在MOS管开关电路输入/输出波形中找出传输时间、上升时间和下降时间。

i. MOS管开关电路传输特性曲线。 j. MOS管W/L对传输特性的影响(给定L、扫描W)。 k. 在MOS管传输特性曲线上找出测量输入、输出电压门限,计算噪声裕度。 (2)记录操作步骤,截取相应图片,完成实验报告。 二、实验环境、Tanner软件简介及SPICE命令。 实验环境: Tanner(S-Edit、T-Spice、W-Edit) SPICE命令的插入: Edit —Insert Command命令或工具栏中的,打开T-Spice Command Tool(T-Spice命令工具)对话框,可以在活动输入文件中插入命令。 三、实验流程框图。 四、实验步骤。 1.在S-Edit中绘制电路原理图,导出SPICE文件。 (1)新建一个文件file-new,新建一个模块,module-new,添加所需要的工艺库。

实验一变频器的面板操作与运行 一、实验目的和要求 1. 熟悉变频器的面板操作方法。 2. 熟练变频器的功能参数设置。 3. 熟练掌握变频器的正反转、点动、频率调节方法。 4.通过变频器操作面板对电动机的启动、正反转、点动、调速控制。 二、实验仪器和用具 西门子MM420变频器、小型三相异步电动机、电气控制柜、电工工具(1套)、连接导线若干等。 三、实验内容和步骤 1.按要求接线 系统接线如图2-1所示,检查电路正确无误后, 合上主电源开关Q S。 图2-1 变频调速系统电气图 2.参数设置 (1)设定P0010=30和P0970=1,按下P键,开始复位,复位过程大约3min,这样就可保证变频器的参数回复到工厂默认值。 (2)设置电动机参数,为了使电动机与变频器相匹配,需要设置电动机参数。电动机参数设置见表2-2。电动机参数设定完成后,设P0010=0,变频器当前处于准备状态,可正常运行。 表2-2 电动机参数设置

(3)设置面板操作控制参数,见表2-3。 3.变频器运行操作 (1)变频器启动:在变频器的前操作面板上按运行键,变频器将驱动电动机升速,并运行在由P1040所设定的20Hz频率对应的560r∕min的转速上。 (2)正反转及加减速运行:电动机的转速(运行频率)及旋转方向可直接通过按前操作面板上的键∕减少键(▲/▼)来改变。 (3)点动运行:按下变频器前操作面板上的点动键,则变频器驱动电动机升速,并运行在由P1058所设置的正向点动10Hz频率值上。当松开变频器前错做面板上的点动键,则变频器将驱动电动机降速至零。这时,如果按下一变频器前操作面板上的换向键,在重复上述的点动运行操作,电动机可在变频器的驱动下反向点动运行。 (4)电动机停车:在变频器的前操作面板上按停止键,则变频器将驱动电动机降速至零。 四、实验思考 1. 怎样利用变频器操作面板对电动机进行预定时间的启动和停止? 答:P0010=30,P0970=1,变频器恢复出厂设置; P701=0,屏蔽原来端子启动功能; P2800=1,使能内部功能自由块; P2802=1,使能内部定时器; P2849=1,连接定时器启动命令; P2850=1,设定延时时间(假设1s); P2851=1,定时器延时动作方式; P0840=2852.0,连接变频器启动命令。 2. 怎样设置变频器的最大和最小运行频率? 答:P0010=30;P0970=1,按下P键(约10秒),开始复位。 一般P1080=0;电动机运行的最低频率(HZ) P1082=50;电动机运行的最高频率(HZ)。

半导体芯片封装及测试技术 价值评估咨询报告书 深华(2004)评字第018号 深圳大华天诚会计师事务所 中国?深圳

目录 评估咨询报告书摘要 (2) 资产评估咨询报告书 (3) 一、 委托方与资产占有方简介 (3) 二、 评估目的 (3) 三、 评估范围和对象 (3) 四、 评估基准日 (5) 五、 评估原则 (5) 六、 评估依据 (5) (一) 主要法律法规 (5) (二) 经济行为文件 (5) (三) 重大合同协议、产权证明文件 (6) (四) 采用的取价标准 (6) 七、 评估方法 (6) 八、 评估过程 (7) 九、 评估结论 (7) 十、 特别事项说明 (7) 十一、 评估报告评估基准日期后重大事项 (8) 十二、 评估报告法律效力 (8) 十三、 评估报告提出日期 (8) 十四、 备查文件 (8)

评估咨询报告书摘要 我所接受PAYTON技术有限公司的委托,根据国家有关资产评估的规定,本着客观、独立、公正、科学的原则,按照公认的资产评估方法,对PAYTON技术有限公司拥有的半导体芯片封装测试专用技术的价值进行了评估工作。本所评估人员按照必要的评估程序对委托评估的资产实施了实地勘测、市场调查与询证,对委估资产在评估基准日2004年6月24日所表现的市场价值作出了较为公允地反映。评估结果为20,500,000.00美元,大写美元贰仟零伍拾万元整。 郑重声明: 以上内容摘自资产评估报告书,欲了解本评估项目的全面情况,应认真阅读资产评估报告书全文。 本评估结论系对评估基准日资产咨询价值的反映。评估结论系根据本报告书所述原则、依据、前提、方法、程序得出,评估结论只有在上述原则、依据、前提存在的条件下,以及委托方和资产占有方所提供的所有原始文件都是真实与合法的条件下成立。 评估报告中陈述的特别事项是指在已确定评估结果的前提下,评估人员揭示在评估过程中己发现可能影响评估结论,但非评估人员执业水平和能力所能评定估算的有关事项,请报告使用者关注。

集成电路封装形式介绍(图解) BGA BGFP132 CLCC CPGA DIP EBGA 680L FBGA FDIP FQFP 100L JLCC BGA160L LCC

LDCC LGA LQFP LQFP100L Metal Qual100L PBGA217L PCDIP PLCC PPGA PQFP QFP SBA 192L TQFP100L TSBGA217L TSOP

CSP SIP:单列直插式封装.该类型的引脚在芯片单侧排列,引脚节距等特征和DIP基本相同.ZIP:Z型引脚直插式封装.该类型的引脚也在芯片单侧排列,只是引脚比SIP粗短些,节距等特征也和DIP基本相同. S-DIP:收缩双列直插式封装.该类型的引脚在芯片两侧排列,引脚节距为1.778mm,芯片集成度高于DIP. SK-DIP:窄型双列直插式封装.除了芯片的宽度是DIP的1/2以外,其它特征和DIP相同.PGA:针栅阵列插入式封装.封装底面垂直阵列布置引脚插脚,如同针栅.插脚节距为2.54mm或1.27mm,插脚数可多达数百脚. 用于高速的且大规模和超大规模集成电路. SOP:小外型封装.表面贴装型封装的一种,引脚端子从封装的两个侧面引出,字母L状.引脚节距为 1.27mm. MSP:微方型封装.表面贴装型封装的一种,又叫QFI等,引脚端子从封装的四个侧面引出,呈I字形向下方延伸,没有向外突出的部分,实装占用面积小,引脚节距为1.27mm. QFP:四方扁平封装.表面贴装型封装的一种,引脚端子从封装的两个侧面引出,呈L字形,引脚节距为 1.0mm,0.8mm,0.65mm,0.5mm,0.4mm,0.3mm,引脚可达300脚以上. SVP:表面安装型垂直封装.表面贴装型封装的一种,引脚端子从封装的一个侧面引出,引脚在中间部位弯成直角,弯曲引脚的端部和PCB键合,为垂直安装的封装.实装占有面积很小.引脚节距为0.65mm,0.5mm. LCCC:无引线陶瓷封装载体.在陶瓷基板的四个侧面都设有电极焊盘而无引脚的表面贴装型封装.用于高 速,高频集成电路封装. PLCC:无引线塑料封装载体.一种塑料封装的LCC.也用于高速,高频集成电路封装. SOJ:小外形J引脚封装.表面贴装型封装的一种,引脚端子从封装的两个侧面引出,呈J字形,引脚节距为 1.27mm. BGA:球栅阵列封装.表面贴装型封装的一种,在PCB的背面布置二维阵列的球形端子,而不采用针脚引脚. 焊球的节距通常为1.5mm,1.0mm,0.8mm,和PGA相比,不会出现针脚变形问题. CSP:芯片级封装.一种超小型表面贴装型封装,其引脚也是球形端子,节距为0.8mm,0.65mm,0.5mm等. TCP:带载封装.在形成布线的绝缘带上搭载裸芯片,并和布线相连接的封装.和其他表面贴装型封装相比,芯片更薄,引脚节距更小,达0.25mm,而引脚数可达500针以上. 介绍:

模拟乘法混频实验报告 姓名: 学号: 班级: 日期:

模拟乘法混频 一、实验目的 1. 进一步了解集成混频器的工作原理 2. 了解混频器中的寄生干扰 二、实验原理及实验电路说明 混频器的功能是将载波为vs (高频)的已调波信号不失真地变换为另一载频(固定中频)的已调波信号,而保持原调制规律不变。例如在调幅广播接收机中,混频器将中心频率为535~1605KHz 的已调波信号变换为中心频率为465KHz 的中频已调波信号。此外,混频器还广泛用于需要进行频率变换的电子系统及仪器中,如频率合成器、外差频率计等。 混频器的电路模型如图1所示。 图1 混频器电路模型 混频器常用的非线性器件有二极管、三极管、场效应管和乘法器。本振用于产生一个等幅的高频信号VL ,并与输入信号 VS 经混频器后所产生的差频信号经带通滤波器滤出。目前,高质量的通信接收机广泛采用二极管环形混频器和由双差分对管平衡调制器构成的混频器,而在一般接收机(例如广播收音机)中,为了简化电路,还是采用简单的三极管混频器。本实验采用集成模拟相乘器作混频电路实验。 图2为模拟乘法器混频电路,该电路由集成模拟乘法器MC1496完成。 V s V

+12 -12 J7J8 J9 C12104 C11104 C7104 C15104 C8104 R101K R11200 R12820 R13820 R71K R14100 R153.3K R163.3K R216.8K R20510 R171k F24.5M D28.2V C16104 TH6 TH7 TH8 TH9 TP5 SIG+ 1 G N A D J 2 G N A D J 3 SIG- 4 B I A S 5 OUT+6NC 7CAR+8 NC 9CAR- 10 NC 11OUT-12 NC 13V E E 14 U1 MC1496 图2 MC1496构成的混频电路 MC1496可以采用单电源供电,也可采用双电源供电。本实验电路中采用+12V ,-8V 供电。R12(820Ω)、R13(820Ω)组成平衡电路,F2为4.5MHz 选频回路。本实验中输入信号频率为 fs =4.2MHz ,本振频率fL =8.7MHz 。 为了实现混频功能,混频器件必须工作在非线性状态,而作用在混频器上的除了输入信号电压VS 和本振电压VL 外,不可避免地还存在干扰和噪声。它们之间任意两者都有可能产生组合频率,这些组合信号频率如果等于或接近中频,将与输入信号一起通过中频放大器、解调器,对输出级产生干涉,影响输入信号的接收。干扰是由于混频器不满足线性时变工作条件而形成的,因此干扰不可避免,其中影响最大的是中频干扰和镜象干扰。 三、 实验仪器与设备 高频电子线路综合实验箱; 高频信号发生器; 双踪示波器; 频率计。 四、实验步骤 1. 打开本实验单元的电源开关,观察对应的发光二极管是否点亮,熟悉电路各部分元件的作用。

载波芯片通信性能测试 技术报告

目录 1.项目背景-----------------------------------------------3 2.项目意义及方案制定-------------------------------------3 3.具体测试实施情况---------------------------------------4 4.测试结果对比------------------------------------------11

0.项目背景 按照国家电网公司要求,将在未来几年内推行低压集中抄表系统,低压电力线载波抄表是主要抄表方式之一。当前的载波抄表芯片厂家,都拥有自己不同的载波通信技术,在载波的调制方式、路由算法、组网等方面都有自己的独特技术,在不同的通信环境下,发挥着各自的优势,促进了载波抄表技术的百花齐放。 1.项目意义及方案制定 为进一步了解各种载波通信技术性能,分析可能影响载波通信的因素,研究各种载波产品的适用环境,比较各种通信产品的优劣,以保证天津市电力公司低压集抄工程采用尽可能优越的技术与产品,故组织进行了此次对几个主流载波芯片厂产品的对比测试工作。以下测试数据除清华力合微电子的第二次测试是2010年10月进行外,其余生产厂家及清华力合微电子的第一次测试时间均为2009年9月份。 测试方案是由天津市电力公司营销部组织,电能计量中心、电费管理中心共同起草制定的,电能计量中心与电费中心负责具体的测试工作。 测试过程是在模拟台区现场的环境下进行测试,在各个时段不同负荷情况下进行抄表测试,对不同条件下的抄表成功率进行统计。此阶段主要测试载波芯片在各种环境下的集中抄表能力、自组网能力,以及主动上报功能。现场模拟测试以电能计量中心办公楼为测试台区,使用电费管理中心的现有主站;对于各厂家自己的独特功能如电费主站无法支持的,可使用厂家自己的测试平台进行,并对测试过程