第26卷 第1期2005年1月

半 导 体 学 报

CHI NESE JOURNA L OF SE MIC ONDUCT ORS

V ol.26 N o.1

Jan.,2005

徐 勇 男,讲师,硕士,研究方向为射频与模数混合集成电路设计.

王志功 男,教授,博士生导师,研究方向包括超高速、微波和毫米波集成电路,光电集成电路设计.李智群 男,副教授,博士,研究方向为射频集成电路设计.

2003212205收到,2004203217定稿

2005中国电子学会

一种新型高速低抖动低功耗双模预分频器

及其在PLL 频率综合器中的应用

徐 勇1,2 王志功1 李智群1 熊明珍1

(1东南大学射频与光电集成电路研究所,南京 210096)

(2解放军理工大学理学院,南京 211101)

摘要:提出了一种零中频两次变频802111a 接收机频率合成方案,降低电路功耗的同时,提高了电路可靠性.改进了双模预分频器的结构,提出了一种新型集成“或”逻辑的SC L 结构D 锁存器.采用0118μm 数模混合C M OS 工艺投片测试表明,双模预分频器在118V 电源下功耗仅5176mW (118V ×312mA ),RMS 抖动小于1%.关键词:双模预分频器;可编程分频器;低功耗;低抖动

EEACC :1265B ;2570D

中图分类号:T N79+1 文献标识码:A 文章编号:025324177(2005)0120176204

1 引言

在无线局域网(W LAN )射频前端电路设计中,作为本振源,锁相环型频率综合器是系统设计中的一个重要模块.由于应用于802.11a 频段频率合成,

压控振荡器(VC O )频率较高,一般采用前置双模预分频与程序分频级联共同完成频率合成.

本设计采用0118μm 数模混合C MOS 工艺实现了频率综合器的双频段高速、低抖动与低功耗输出.分频器最高速度为415G H z ,双模预分频输出均方差相位抖动仅012%,在118V 电源电压作用下消耗电流仅312mA.芯片面积为0162mm ×0105mm.本设计不以最高速度为惟一追求目标,在综合比较芯片的速度、功耗及工艺条件的基础上,本设计性能更为优良[1~4].

2 频率综合器的总体方案

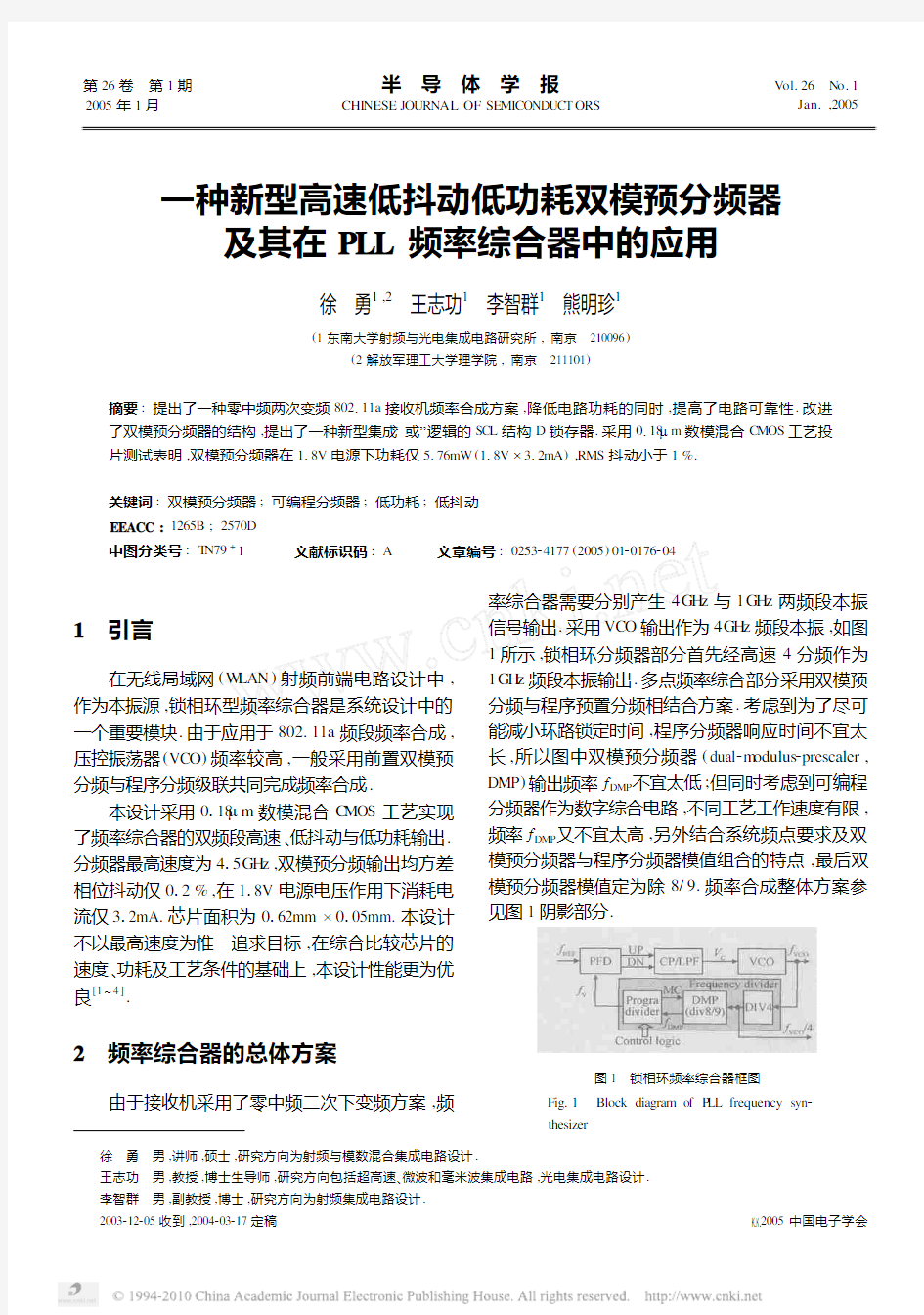

由于接收机采用了零中频二次下变频方案,频

率综合器需要分别产生4G H z 与1G H z 两频段本振

信号输出.采用VC O 输出作为4G H z 频段本振,如图1所示,锁相环分频器部分首先经高速4分频作为1G H z 频段本振输出.多点频率综合部分采用双模预分频与程序预置分频相结合方案.考虑到为了尽可能减小环路锁定时间,程序分频器响应时间不宜太长,所以图中双模预分频器(dual 2m odulus 2prescaler ,DMP )输出频率f DMP 不宜太低;但同时考虑到可编程分频器作为数字综合电路,不同工艺工作速度有限,频率f DMP 又不宜太高,另外结合系统频点要求及双模预分频器与程序分频器模值组合的特点,最后双模预分频器模值定为除8/9.频率合成整体方案参见图1阴影部分

.

图1 锁相环频率综合器框图

Fig.1 Block diagram of P LL frequency syn 2thesizer

3 前置4分频器设计

前置固定4分频器采用了经典两级D 触发器

(DFF )2分频级联构成.每一级D 触发器分别由基于C MOS SC L 结构的主、从锁存器构成,如图2所示.锁

存器电路采用差分结构,提高了射频电路对共模信号的抑制能力.不同于典型差分结构的锁存器设计,本文中的输出级采用了PMOS ,NMOS 互补耦合对结构替代了单纯NMOS 耦合对结构,在保证电路速度的条件下,最大可能地提高输出信号(QP ,QN )的摆幅.在输出信号摆幅足够强时,该结构锁存器可以直接驱动后级负载电路而不必另行放大.因此本结构在降低设计复杂性的同时,提高了电路的工作速度[1]

.

图2 锁存器单元结构

Fig.2 Circuit schematic of latch

4 高速8/9双模预分频器设计

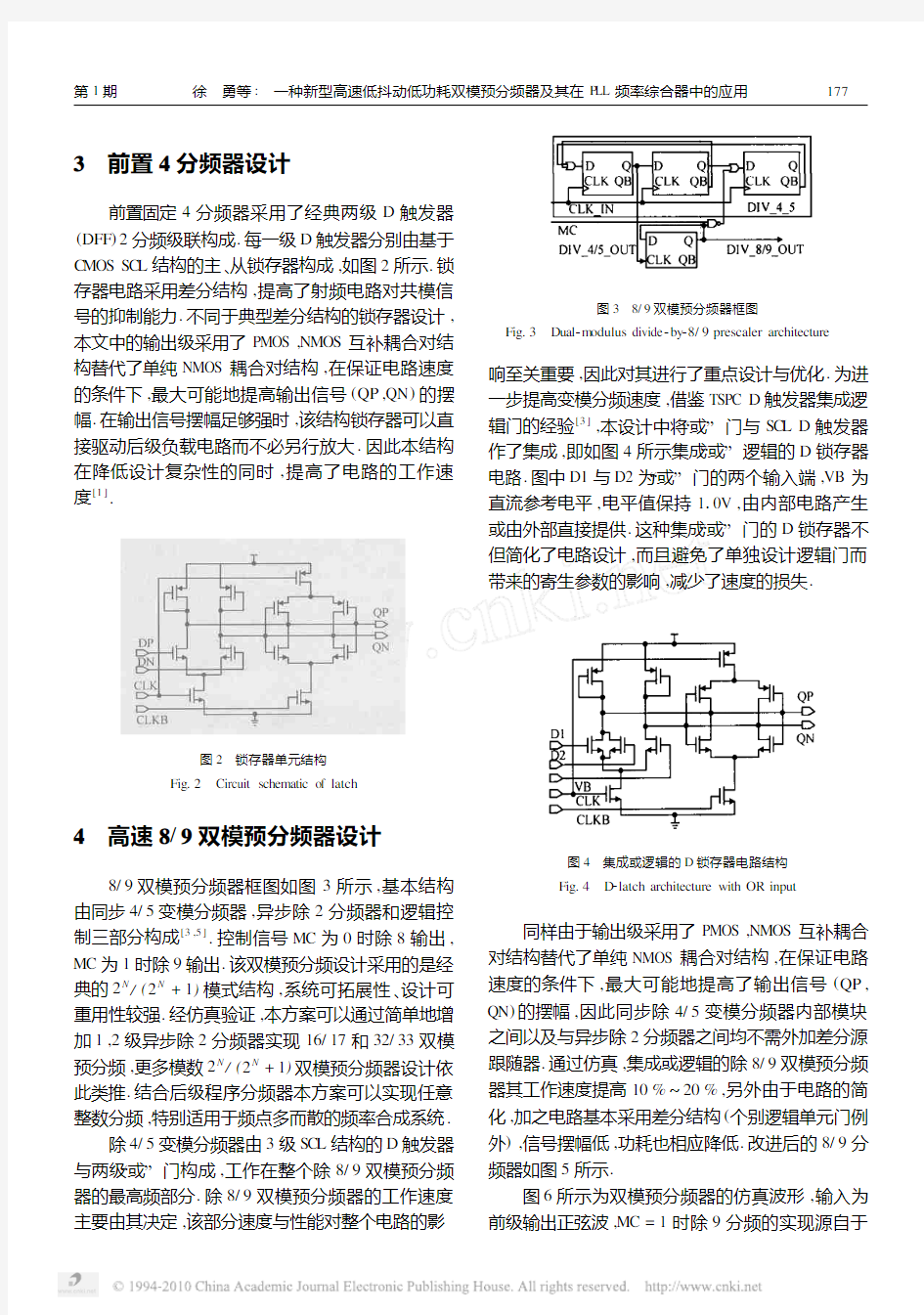

8/9双模预分频器框图如图3所示,基本结构由同步4/5变模分频器,异步除2分频器和逻辑控

制三部分构成[3,5].控制信号MC 为0时除8输出,MC 为1时除9输出.该双模预分频设计采用的是经典的2N /(2N +1)模式结构,系统可拓展性、设计可重用性较强.经仿真验证,本方案可以通过简单地增加1,2级异步除2分频器实现16/17和32/33双模预分频,更多模数2N /(2N +1)双模预分频器设计依此类推.结合后级程序分频器本方案可以实现任意整数分频,特别适用于频点多而散的频率合成系统.

除4/5变模分频器由3级SC L 结构的D 触发器与两级“或”门构成,工作在整个除8/9双模预分频器的最高频部分.除8/9双模预分频器的工作速度主要由其决定,

该部分速度与性能对整个电路的影

图3 8/9双模预分频器框图

Fig.3 Dual 2m odulus divide 2by 28/9prescaler architecture

响至关重要,因此对其进行了重点设计与优化.为进

一步提高变模分频速度,借鉴TSPC D 触发器集成逻辑门的经验[3],本设计中将“或”门与SC L D 触发器作了集成,即如图4所示集成“或”逻辑的D 锁存器电路.图中D1与D2为“或”门的两个输入端,VB 为直流参考电平,电平值保持110V ,由内部电路产生或由外部直接提供.这种集成“或”门的D 锁存器不但简化了电路设计,而且避免了单独设计逻辑门而带来的寄生参数的影响,减少了速度的损失

.

图4 集成或逻辑的D 锁存器电路结构

Fig.4 D 2latch architecture with OR input

同样由于输出级采用了PMOS ,NMOS 互补耦合对结构替代了单纯NMOS 耦合对结构,在保证电路速度的条件下,最大可能地提高了输出信号(QP ,QN )的摆幅,因此同步除4/5变模分频器内部模块

之间以及与异步除2分频器之间均不需外加差分源跟随器.通过仿真,集成或逻辑的除8/9双模预分频器其工作速度提高10%~20%,另外由于电路的简化,加之电路基本采用差分结构(个别逻辑单元门例外),信号摆幅低,功耗也相应降低.改进后的8/9分频器如图5所示.

图6所示为双模预分频器的仿真波形,输入为前级输出正弦波,MC =1时除9分频的实现源自于

7

71第1期徐 勇等: 一种新型高速低抖动低功耗双模预分频器及其在P LL 频率综合器中的应用

图5 改进型差分结构8/9双模预分频器框图

Fig.5 Im proved architecture of divide 2by 28/9DMP

8/9双模预分频器中除4/5变模分频的除4与除5

的周期交叠而成.由于仿真时考虑了测试环境,图中

除4/5输出及除8/9输出端加了测试buffer ,并带上了模拟负载,包括焊盘电容及测试探针50Ω电阻.图中所示输出即为模拟探针上所得

.

图6 双模预分频器仿真波形

Fig.6 S imulation waves of DMP

5 版图与测试结果

为了验证方案的性能,我们使用了0118μm 数模

混合C MOS 工艺实现了该方案,为了先期与P LL 主通道部分实现整合测试,在低速程序分频部分暂时用除8和除32分频器代替.图7给出了芯片的显微照片,芯片面积为112mm ×0147mm ,核心电路面积仅仅为0162mm ×0105mm.为了测试方便,电路内部引出了许多节点,为了准确测试核心电路功耗,版图设计中将核心电路与测试bu ffer 电源分开供电.

测试主要分为功耗测试、抖动测试与分频精度测试.功耗测试表明核功耗(含全部三部分串联模块)与buffer 功耗分别为719mA 与17mA ,

与仿真值

图7 频率合成模块版图

Fig.7 Lay out of frequency synthesizer

7181mA 与20mA 匹配良好.其中双模预分频部分单

独投片测试核心功耗仅5176mW ,基本接近仿真值.4分频最高频率417G H z ,图8为41256G H z 时4分频输出示波器波形,由图读出频率11055G H z ,占空比5015%,均方根(RMS )抖动值为2ps 仅占输出信号周期的012%.对于除8/9双模预分频器测试,用频谱分析仪准确获得了频率在电平MC 的控制下正确切换的信息并且分频精度良好.图9为41256G H z 输入经高速4分频后又由双模预分频器除9后的示波器波形.波形显示占空比为5513%,频率为11813MH z.测试结果表明该电路非常准确地完成了双模分频设计要求

.

图8 高速4分频器测试输出波形

Fig.8 Waveform of high 2speed quarter divider

6 结论

本文阐述了适用于零中频两次变频802111a 接收机方案中频率综合器的分频设计方法.该设计需要同时给系统提供4G H z 频段与1G H z 频段本振信号,因此设计时没有将双模预分频直接接到VC O 之后而是先除4分频后再双模除8/9分频,既提高了电路的稳定性与可靠性,又实现了设计需求的高速、低抖动与低功耗.投片测试结果表明测试与仿真结

871半 导 体 学 报第26卷

图9 8/9双模预分频器除9时输出波形

Fig.9 Divide 2by 29waves form of divide 2by 28/9DMP

果匹配很好.

参考文献

[1] Chi Baoy ong ,Shi Bingxue.A novel C M OS dual m odulus prescaler

based on new optim ized structure and dynam ic circuit technique.Chi 2nese Journal of Sem iconductors ,2002,23:357

[2] Huang C M ,

Floyd B A ,

Park N ,

et al.

Fully

intergrated

5135G H z C M OS VCOs and prescalers.IEEE T rans M icrow Theory T ech ,2001,49(1):17

[3] Y ang C Y,Dehng G K,Hsu J M ,et al.New dynam ic flip 2flips for

high 2speed dual 2m odulus prescaler.IEEE J S olid 2S tate Circuits ,

1998,33(10):1568

[4] Lam C ,Razavi B.A 2162G H z/5122G H z frequency synthesizer in 0142

μm C M OS technology.IEEE J S olid 2S tate Circuits ,2000,35(5):788

[5] Ajjikuttira A B ,Chan W L ,Lian Y.A 515G H z prescaler in 0118/spl

mu/m C M OS technology.2002IEEE Asia 2Pacific C on ference on A 2SIC ,2002:69

A N ovel H igh 2Speed Low er 2Jitter Low er 2Pow er 2Dissipation

Dual 2Modulus 2Prescaler and Applications

in PLL Frequency Synthesizer

Xu Y ong 1,2,Wang Zhig ong 1,Li Zhiqun 1,and X iong Mingzhen 1

(1Institute o f RF 2&OE 2IC s ,Southeast Univer sity ,Nanjing 210096,China )(2College o f Sciences ,P LA Univer sity o f Science and Technology ,Nanjing 211101,China )

Abstract :A scheme of frequency synthesizer applied for 802111a W LAN in zero IF tw o 2step receiver is presented ,and lower power dissipation and m ore stable per formance are gained.The structure of the dual m odulus prescaler is optimized and a novel D 2latch integrated with “OR ”log 2

ic gate is used.I t is fabricated in 0118μm mixed 2signal C M OS process.The measured results show that chip can w ork well with 118V supply ,

and power dissipation of the core part in dual m odulus prescaler is only 5176mW.The rms 2jitter is less than 1%.K ey w ords :dual 2m odulus 2prescaler ;programmable divider ;low power dissipation ;low jitter EEACC :1265B ;2570D

Article I D :025324177(2005)0120176204

Xu Y ong male ,master.His w ork focuses on RF front 2end circuit and m ixed 2signal circuit design.

W ang Zhig ong male ,profess or ,PhD.His research interests include ultra 2speed ,m icrowave and m illimeter wave circuit ,opto 2electronic circuit design.Li Zhiqun male ,ass ociate profess or ,PhD.His research focuses on RF front 2end circuit design.Received 5December 2003,revised manuscript received 17M arch 2004

2005Chinese Institute of E lectronics

9

71第1期徐 勇等: 一种新型高速低抖动低功耗双模预分频器及其在P LL 频率综合器中的应用

Neuron多处理器芯片及其应用摘要:Neuron芯片是美国Mitorola公司和日本Toshiba 公司制造的一种多处理器结构的神经元芯片。它将通信协议和控制用微处理器有效地集成在一起,实现通信、控制、调度和I/O等功能。本文以MC134150为例,介绍有关Neuron芯片的基本结构和组成、LonTalk协议以及应用系统的组成方式等。关键词:神经元芯片多处理器 Neuron固件一、Neuron芯片的基本组成Neuron芯片作为一种多处理器结构的神经元芯片,有着完整的系统资源,如图1所示,其内部集成有三个管线CPU,最高工作频率可达10MHz。它设置有11编程输入、输出引脚(IO1~IO10),编程方法多达34种,方便了实现应用。片内设有EEPROM和RAM,支持有外部扩展多种存储器的接口,最大存储空间允许有64KB。内部含有两个16位定时器/计数器,能够由固件产生15个软件定时器。Neuron芯片的长处还在于它的网络通信功能,引出的五个通信引脚(CP0~CP4)提供了单端、差分和特殊应用模式等三种网络通信方式。 1.处理器单元Neuron芯片集成有三个处理器,其中一个用于执行用户编写的应用程序,另外两个完成网络任务。图2示意了Neuron芯片内三个处理器的功能分配及与内部共享存储器区域之间的关系。(1)MAC处理器是媒体访问控制层处理器。它处理OSI七层网络协议中的1,2层,主要包括驱动通信子系统硬件以及执行冲突回避算法等。MAC 处理器使用位于共享存储器中的网络缓冲区与网络处理器进行通信。(2)网络处理器实现网络协议中的3~6层。它实现网络变量处理、寻址、事务处理、文电鉴别、软件定时器、网络管理和路由等功能。网络处理器通过共享存储器中的网络缓冲区与MAC处理器通信,并采用应用缓冲区与应用处理器进行通信。应用缓冲区也是设置在共享存储器中的。对缓冲区的访问都用硬件信号灯来协调,以便在更新共享数据时消除竞争。(3)应用处理器一方面执行用户编写的应用程序代码,另一方面执行由用户代码所调用的操作系统服务。大多数应用程序均可采用Neuron C语言来编制,使编程工作真正从繁琐的汇编语言中解脱出来。2.存储器分配MC143150的外扩存储器接口总线中,有8位双向数据总线、16位处理器驱动的地址总线以及用于外部存储器存取访问的两个接口信号线R/W和E。总的地址空间为64KB,其中有6KB 的地址空间保留在芯片内,剩余的58KB的地址空间供外扩存储器使用。在外扩存储器中,通常用16KB存放固件,其余的42KB用于存放用户程序和数据信息。3.应用I/O口具有11个引脚的I/O接口提供有34种编程方式,另外,2个16位定时器/计数器可用于频率和定时I/O。由固件产生的15种软件定时器并不占用应用处理器的运算时间,而由完成网络功能的处理器实现。因此,用户可直接使用软件定时器,不必考虑其具体操作。[!--empirenews.page--]Neuron芯片提供的11个I/O引脚(IO0~IO10)可通过编程设定为34种不同的I/O对象,支持电平、脉冲、频率、编码等各种信号模式,有直接I/O对象、定时器/计数器I/O对象、串行I/O对象、并行I/O对象等供用户选择。它们与集成的硬件和固件一起可用于连接马达、阀门、显示驱动器、A/D转换器、压力传感器、热敏电阻、开关量、继电器、可控硅、转速计、其他处理器和调制解调器等,方便了实际应用。表1列举了所有I/O对象的基本类型。表1 I/O对象类型参照表I/O对象类型注释Bit input/output位输入/输出Bitshift input/output位称输入/输出Byte input/output字节输入/输出Dualslope input双积分输入Edgedivide output脉冲沿分离输出Edgelog input边沿跳变时间间隔序列输入Frequency output频率输出I2C input/outputI2C输入/输出Infrared input远红外输入Leveldetect input电平监测输入Magcard input磁卡编码输入Magtrackl input经录入1输入Muxbus input/output多总线输入/输出Neurowire input/output神经元接口输入/输出Nibble input/output半字节输入/输出Oneshot output单稳输出Ontime input逻辑电持续时间输入Parallel input/output并行输入/输出Preiod input周期输入Pulsecount input脉冲计数输入Pulsecount output脉冲计数输出Pulsewidth output脉宽输出Quadrature input位置码盘输入Serial input/output串行输入/输出Totalcount input 累加计数输入Touch input/output触点输入/输出Triac output触发输出Triggeredcount

【对讲机的那点事】无线对讲机写频技术及软件设定方法 对讲机写频技术,是经销商和业余无线电爱好者操作对讲机和电台的一种 必须技能。国产品牌对讲机机型繁多,写频软件是五花八门,要想和其它型号对讲机对频使用,写频难,难写频,对于经销商和无线电爱好者们,都是一个很头疼的问题。国产对讲机软件官网难寻,一般是没有软件下载。就是网上找到写频软件,下载安装后,能不能用都又是一个问题。国内部份生产厂家,网上根本没有相应的软件下载。还有些机型是专用写频线,引角定义不一样,根本不能读写频。 今天小编就和您聊聊关于对讲机写频的那些事: 一、写频线接口定义对讲机写频线和耳机插孔定义是有很多种类,分为常用机型和专用机型。K健伍系列:健伍好易通灵通泉盛特易通等市面上大多数国产机型T系列:A8:适用于摩托罗拉A8,A6,SMP418等机型M系列:TC500:适用于好易通窄口 TC500/TC600/TC700等手台B系列:VX168:适用于威泰克斯系列VX-168,VX-160和部份单孔国产手台F系列:GP88S:适用于摩托罗拉 GP88S/GP2000/GP3688等手台Y系列:V8:适用于 IC-V8/V82/V85/F21/IC2720/F26等手台R系列:八重州3R/6R/7R等相关机型水晶头系列:特别注意:摩托GP88、北峰、健伍271、GM300等部份机型是专用写频线,写频线接口线定义不一样,不能通用的。 二、写频软件的安装 安装方法,直接双击写频软件压缩包,解压软件,根据界面提示操作,点击下一步,安装到桌面和C盘,部份软件只能按装到C盘,安装到其它盘无效。 健伍等部份系列写频软件解压安装过程中,还要输入软件序列号。在解压界面上最下一个就是安装软件序列号,直接把它复制、粘贴到那个安装框内,点击下一步安装完成。 国产大部份写频软件是一次直接解压,自动安装到位。软件安装完成后,桌面和C盘区,有一个写频软件相应的界面。 双击打开写频软件操作界面,就可以进入写频模式。有部份软件安装完成后,需要重启电脑,电脑才能正常识别运行这个软件。 三、驱动程序的安装写频线接口分为二种型式,串口和USB二种方式,串口写频线一般安装好相应的写频软件后,就可以进入写频模式。 四、对用USB写频数据线的一定先要安装相对应的驱动程序,这一点和九针串口是不同的。 五、有些朋友把写频软件和驱动程序混为一谈,这是错误地,USB不装驱动软件,USB 端口将不识别USB写频线。用USB写频线时,一定要先安装驱动,在接上写频线。安装时还要注意,不同的USB写频线用的芯片不同,驱动程序也不相同,最常用的一种是 PL2303\HL340\HL0108等芯片,安装驱动程序时点击相应驱动程序安装就可以了。

pll是锁相环(Phase-Locked Loop)的英文简称,用来使外部的输入信号和内部的振荡信号同步。pll是用于振荡器中的反馈控制电路。 目录 pll的原理 pll的构成 pll的应用 pll的动作机理 pll的原理 pll是无线电发射中使频率较为稳定的一种方法,主要有VCO (压控振荡器)和PLL IC ,压控振荡器给出一个信号,一部分作为输出,另一部分通过分频和PLL IC所产生的本振信号作相位比较,为了保持频率不变,就要求相位差不发生改变,如果有相位差的变化,则PLL IC的电压输出端的电压发生变化,去控制VCO,直到相位差恢复达到锁频的目的。能使受控振荡器的频率和相位均和输入信号保持确定关系的闭环电子电路。 pll的构成 锁相环由鉴相器、环路滤波器和压控振荡器组成。鉴相器用来鉴别输入信号Ui 和输出信号Uo之间的相位差,并输出误差电压Ud 。Ud 中的噪声和干扰成分被低通性质的环路滤波器滤除,形成压控振荡器(VCO)的控制电压Uc。Uc作用于压控振荡器的结果是把它的输出振荡频率f。拉向环路输入信号频率fi ,当二者相等时,环路被锁定,称为入锁。维持锁定的直流控制电压由鉴相器提供,因此鉴相器的两个输入信号间留有一定的相位差。锁相环最初用于改善电视接收机的行同步和帧同步,以提高抗干扰能力。 pll的应用 1.锁相环在调制和解调中的应用载波信号的参数有幅度、频率和位相,所以,调制有调幅(AM)、调频(FM)和调相(PM)三种。调幅波的特点是频率和载波信号的频率相等,幅度随输入信号幅度的变化而变化;调频波的特点是幅度和载波信号的幅度相等,频率随输入信号幅度的变化而变化。 2.锁相环在调频和解调电路中的应用调频波的特点是频率随调制信号幅度的变化而变化。压控振荡器的振荡频率取决于输入电压的幅度。当载波信号的频率和锁相环的固有振荡频率ω0 相等时,压控振荡器输出信号的频率将保持ω0 不变。若压控振荡器的输入信号除了有锁相环低通滤波器输出的信号uc 外,还有调制信号ui,则压控振荡器输出信号

-.背景说明 早期手机的功能较为阳春,主要提供语音通话及文字短讯的传送,当时的基频零组件也较为单纯,主要含括有类比基频(Analog Baseband)、数位基频(Digital Baseband)、记忆体(Memory)、功率管理(Power Management)四大部分。但随着手机应用不断的扩充下,基频零组件数目也越来越多,多媒体处理器(Multimedia Coprocessor)提供和弦铃声、CMOS/CCD感光元件(CMOS/CCD Sensor)及影像处理器(Image Processor)提供照相功能等,手机基频零组件元件数随着手机应用功能扩充也不断的增加。 手机基频零组件数目,随着应用的扩充而不断增加,应用处理器的出现,形成手机基频双处理器的概念,此概念让数位讯号处理器负责语音讯号的处理,应用处理器负责影音应用的处理。 二、基频新架构:应用处理器概念 由于手机上影音功能不断的扩充,在影像方面,彩色萤幕的色阶越来越高,由早期的4096色阶到现在的262k色阶(实际为262,144色阶);在相机模组上,由早期搭载11万画素的CMOS/CCD相机模组,到现在百万画素以上的CMOS/CCD相机模组。而音乐方面,手机铃声的发展上,由16和弦、32和弦到64和弦,还能将录音的内容当作铃声,再来则是转为音乐的播放,支援MIDI、MP3形式的播放,还有强调立体声的喇叭。除了上述的影音功能,还有许多无线传输与应用,如:蓝芽传输、Wi-Fi、GPS及FM收音机纷纷加在手机上。 表一手机多媒体功能规格的演进 资料来源:工研院IEK(2005.02) 这些影音加在手机上,大量资料讯号的处理势必增加在基频上,在这样的趋势下,手机基频不但要处理既有的语音讯号,还要加入大量的资料讯号,对于原先的数位讯号处理器来说,无疑是一大负担。在影音发展的初期,简单的影音传送,资料的处理还是落在数位讯号处理器上,但随着影音规格不断提升,处理和弦铃声相关,必须多一颗和弦铃声IC(Melody IC),处理照相功能相关,必须再多一颗影像处理器(Image Processor),基频的零组件越加越多,所占的面积也越来越大。 为了整合这些影音元件,应用处理器(Application Processor;AP)的概念因应而生,让手机基本的语音讯号处理由原先的数位讯号处理器负责,而影音方面的资料处理就交由应用处理器负责。

健伍TK-868G(1)写频器DIY及改业余电台频率方法 来源:《专业无线通信》杂志作者:BD3PS 刘聚兵发表时间:2010-3-4 15:06:18 浏览次数: 185 健伍TK-868G(1)是健伍公司生产的专业车载无线电通讯电台,广泛用于国内银行、金融保卫、公安边防巡逻、野外地矿通讯等环境。8个半双工信道;射频输出功率:25W;工作频率范围450—490MHz;内置CTCSS/DQT/2 TONE/DTMF 编解码器,SmarTrunk Omni兼容,可安装marTrunkOmni数码集群片,采用Flash ROM 存储器,Comparndor语音压扩技术,独有的紧急报警功能。现在好多单位已经更新换代,淘汰闲置。但是广大的业余无线电爱好者淘来使用,功能还绰绰有余,迫于年久,该机器需要写频改到业余频率才能工作。配套软件使用KPG-56D健伍公司提供的专用软件,但是配套的KPG-56D写频器购买困难,价格昂贵。下面我就该机器配套的写頻器DIY办法介绍如下。 元件需要MAX232CEP一个,16V10UF共4个;DB9电脑串口一个,1/8W12k电阻一个;导线若干。电子元件按照下面原理图搭焊或用一附铜板制作线路更好。注意几点:电解电容10UF电容的长脚是电解电容的+脚,短脚为—脚,—极一般正冲电容外包装皮上的长直线。水晶头金属触点向上,上面为1脚,下面为8脚。原理接线图如下:

按原理图连接正确后,DB9接口接电脑COM1上,水晶头接TK-868G(1)话筒口,开机,安装KPQ-56D软件到电脑,软件支持WINDOWS2000 2003,XP,该写频器同时也可对健伍TK-768G(1)、TK-768(3)、TK-868G(3)、TK-760G、TK-762G、TK860G、TK-862G,手持机TK-260G、TK-270G、TK-272G、TK-278G、TK-360G、TK362、TK-378G、TK-388G等写频。 运行KPG-56D,进入该软件后,点机型—进入机型信息,选择车载台—U段频率—机型—TK-868(1)(8CH),点“确定”,编辑频道信息。例如:1信道输入438.50000,点“确定”,会提示频率超出范围,不要理会,继续点“确定”,2信道输入431.0000,把常用的频率依次输入8个信道,如需要模拟哑音或数字哑音直接点小箭头下拉菜单输入皆可,最后点击编程—向通讯机写入数据—听到滴滴长音,及完成数据写入。

综合课程设计 频率合成器的设计与仿真

前言 现代通信系统中,为确保通信的稳定与可靠,对通信设备的频率准确率和稳定度提出了极高的要求. 随着电子技术的发展,要求信号的频率越来越准确和越来越稳定,一般的振荡器已不能满足系统设计的要求。晶体振荡器的高准确度和高稳定度早已被人们认识,成为各种电子系统的必选部件。但是晶体振荡器的频率变化范围很小,其频率值不高,很难满足通信、雷达、测控、仪器仪表等电子系统的需求,在这些应用领域,往往需要在一个频率范围内提供一系列高准确度和高稳定度的频率源,这就需要应用频率合成技术来满足这一需求。 本次实验利用SystemView实现通信系统中锁相频率合成器的仿真,并对结果进行了分析。 一、频率合成器简介 频率合成是指以一个或少量的高准确度和高稳定度的标准频率作为参考频率,由此导出多个或大量的输出频率,这些输出频率的准确度与稳定度与参考频率是一致的。用来产生这些频率的部件就成为频率合成器或频率综合器。频率合成器通过一个或多个标准频率产生大量的输出频率,它是通过对标准频率在频域进行加、减、乘、除来实现的,可以用混频、倍频和分频等电路来实现。其主要技术指标包括频率范围、频率间隔、准确度、频率稳定度、频率纯度以及体积、重量、功能和成本。 频率合成器的合成方法有直接模拟合成法、锁相环合成法和直接数字合成法。直接模拟合成法利用倍频、分频、混频及滤波,从单一或几个参数频率中产生多个所需的频率。该方法频率转换时间快(小于100ns),但是体积大、功耗大,成本高,目前已基本不被采用。锁相频率合成器通过锁相环完成频率的加、减、乘、除运算,其结构是一种闭环系统。其主要优势在于结构简化、便于集成,且频率纯度高,目前广泛应用于各种电子系统。直接式频率合成器中所固有的那些缺点,在锁相频率合成器中大大减少。 本次实验设计的是锁相频率合成器。

Software Power Measurement Dushyanth Narayanan dnarayan@https://www.doczj.com/doc/6610315284.html, April26,2005 Technical Report MSR-TR-2005-51 Microsoft Research Microsoft Corporation One Microsoft Way Redmond,WA98052 https://www.doczj.com/doc/6610315284.html,

Abstract E?ective system-level power management requires cheap,accurate and?ne-grained power measurement and accounting.Unfortunately current portable hardware does not provide this capability.We advocate software power measure-ment:estimation of power consumption by modelling it as a function of device state.The approach requires no additional hardware,and allows?ne-grained, per-device and per-application power measurement.We describe a design and implementation of software power measurement,and a feasibility study showing signi?cantly better accuracy than power pro?ling based on time averaging.We conclude with design recommendations for OS designers and portable hardware vendors to improve the ease and accuracy of power measurement. 1Introduction Energy is a critical resource for many computing systems.While battery life is especially relevant to portable and hand-held computers,peak power consump-tion a?ects fan noise on desktops and cooling costs for server farms.There is an increasingly recognised need to manage and account energy as a?rst-class resource within the operating system[13]. Energy management requires accurate measurement and accounting.Adap-tive tuning of device parameters such as disk spin-down timeouts[3]requires accurate estimates of per-device power consumption.Per-device measurements at?ne time granularity—when combined with existing OS accounting of de-vices such as CPU,disk,and network—also enable per-application accounting of energy consumption.This is of great value both for end-users(“Outlook is responsible for80%of your battery drain,maybe you should kill it”)and for application-level adaptation[5]. Unfortunately,current approaches to energy measurement have several draw-backs,especially when applied to laptop and hand-held computers.Accurate measurement with?ne time granularity requires external hardware such as sam-pling digital multimeters,making the approach unwieldy and hard to deploy in the?eld.Unmodi?ed laptop hardware typically o?ers nothing more than Smart-Battery measurements,which are only accurate at coarse time granularities and measure the power consumption of the entire system but not of individual de-vices. We propose a novel technique known as software power measurement(SPM), which correlates infrequent,coarse-grained measurements of power with?ne-grained observations of device state and activity.The result of the correlation is a predictor that estimates the energy consumption over arbitrarily short time interval from from the observed device state and activity. The remainder of this paper is organised as follows.Section2describes current approaches to the problem and their drawbacks.Section3describes the design and prototype implementation of software power measurement on Windows XP.Section4presents a quantitative evaluation of the prototype, 1

TG-UV2 就是建武的接口,和建武的是完全相同的,接口如下 2.5 根部是GND 2.5的中部是TX 3.5的根部是RX 国产com写频线基本全是一个芯片的,就是接口不一样罢了 自制通用电台写频器 其实给对讲机写频时,写频器起到的作用就是对电平的转换,通俗点讲就是把电脑发出的信息转换成对讲机能读懂的信息,就如翻译一样. 下面我们来看看两张写频器的电路图,这两个图都是用了MAX232这个电脑串口电平转换专用芯片,它有着兼容性好、稳定性好、外围电路简单、容易制作等优点。

图一:这个是给部分要接4条线的手台、车台写频的电路。如TK3107等要接TXD(发送)、RXD(接收)、GEN(接地)、+5V,这四条线的机器。 图二:这个是写需要接DATA(总线)、GEN(接地)、+5V 这三条线的机器,如GP88、GP88S等。(其中发射和接收就用一个二极管或者三极管进行切换)

首先大家需要采购回以下配件: MAX232芯片一片约6元 18脚IC座一个约4毛钱 50伏10微法的电解电容4个约1毛一个 RS232母头一个(插到电脑COM口上的) 约2.5元一套(带外壳) 1N4148二极管一个约1毛一个 USB延长线一条(1.5米或者更长)约2元一条 万能板一小块(半个巴掌大足够)约1块钱 便宜的配件可以多买几个,以备掉了、坏了或者猫叼了、狗啃了等等,呵呵!! (以上价格是本地的零售价格,也许和你们当地有差异,但出入不大,小心上JS的当。) 同时自己还需要准备些工具如烙铁,焊锡,松香,起子等工具

和材料。 关于芯片等配件的引脚请看下面的几张图片,只要细心的对照着焊接,不出错的话不用调试(也没有什么调试的)就可以使用。 这个就是"传说"中的MAX232芯片啦 IN4148的正负极判别: 电容的正负极判别:

锁相环(PLL)频率合成调谐器 调谐器俗称高频头,是对接收来的高频电视信号进行放大(选频放大)并通过内部的变频器把所接收到的各频道电视信号,变为一固定频率的图像中频(38MHz)和伴音中频以利于后续电路(声表面滤波器、中放等)对信号进行处理。 调谐器(高频头)原理: 高频放大:把接收来的高频电视信号进行选频放大。 本机振荡器:产生始终高于高频电视信号图像载频38MHz的等幅载波,送往混频器。 混频器:把高频放大器送来的电视信号和本机振荡器送来的本振等幅波,进行混频产生38MHz的差拍信号(即所接收的中频电视信号)输出送往预中放及声表面滤波器。 结论:简单的说:只要改变本机振荡器的频率即可达到选台的目的) 一、电压合成调谐器:早期彩色电视接收机大部分均采用电压合成高频调谐器,其调谐器的选台及波段切换均由CPU输出的控制电压来实现(L、H、U波段切换电压及调谐选台电压),其中调谐选台电压用来控制选频回路和本振回路的谐振频率,调谐选台电压的任何变化都将导致本机振荡器频率偏移,选台不准确、频偏、频漂。为了保证本机振荡器频率频率稳定,必须加上AFT系统。由于AFT系统中中放限幅调谐回路和移相网络一般由LC谐振回路构成,这个谐振回路是不稳定的,这就造成了高频调谐器本机振荡器频率不稳,也极易造成频偏、频漂。

二、频率合成调谐器 1、频率合成的基本含义:是指用若干个单一频率的正弦波合成多个新的频率分量的方法(频率合成调谐器的本振频率是由晶振分频合成的)。 频率合成的方法有很多种。下图为混频式频率合成器方框图 以上图中除了三个基频外还有其“和频”及“差频”输出(还有各个频率的高次谐波输出)。 输出信号的频率稳定性由基准信号频率稳定性决定,而且输出信号频率误差等于各基准信号误差之和,因此要想减少误差除了要提高基准信号稳定度之外还应减少基准信号的个数。 2、锁相环频率合成器: 其方框图类似于彩色电视接收机中的副载波恢复电路,只是在输入回路插入了一个基准信号分频器(代替色同步信号输入)而在反馈支路插入一个可编程分频器(代替900移相)。当环路锁定时存在如下关系: ∵ fk=f0 / K 式中:fvco为压控振荡器输出信号频率。 fn=fvco / N f0 为晶振基准频率。 fk=fn K为分频系数。 ∴ fvco=N?fo / K N为可变分频器的分频系数(分频比) 彩色电视机幅载波恢复电路

第16卷 第6期V ol.16 N o.6重庆工学院学报 Journal of Chongqing Institute of T echnology 2002年12月 Dec.2002 文章编号:1671—0924(2002)06—0045—05 频率合成技术及其实现 Ξ 张 建 斌 (常州技术师范学院电信系,江苏常州 213001) 摘要:综述了两种频率合成技术的原理、特点、工程设计应注意的问题及各种实现方法。关键 词:频率合成;锁相环;直接数字频率合成;FPG A ;DSP 中图分类号:T N925+16 文献标识码:A 0 引言 高性能频率源是通信、广播、雷达、电子侦察和对抗、精密测量仪器的重要组成部分。现代通信技术的飞速发展对频率源提出了越来越高的要求。性能卓越的频率源均通过频率合成技术来实现。频率合成技术是指将一个高稳定度和高精确度的标准频率经过一定变换,产生同样稳定度和精确度的大量离散频率的技术。按频率合成技术的发展过程,可将频率合成的方法按其型式分为三大类:直接式频率合成器、锁相式频率合成器和直接数字式频率合成器。在直接式频率合成器中,基准信号直接经过混频、分频、倍频、滤波等频率变换,最后产生大量离散频 率的信号。这种方法虽然频率转换时间短、并能产生任意 小数值的频率间隔,但由于其频率范围有限,而更重要的是由于其中采用了大量的混频、分频、倍频、滤波等电路,使频率合成器不仅带来了庞大的体积和重量,耗电多、成本高,而且输出的谐波、噪声及寄生频率多且难以抑制,因而现在已很少使用。 1 频率合成器的原理 1.1 锁相频率合成器[1] 锁相频率合成器基于锁相环(P LL )进行工作,其基本组成如图1所示 : 图1 P LL 的基本组成 图1中,f r 为标准频率,发射系统中为晶体振荡器产生的标准频率信号,接收系统中为收到的标准频率信号。 f 0为锁相环路输出信号的频率。当环路锁定时,则有f 0=Nf r 。因此,通过频率选择开关改变分频比N ,可使压控振 荡器的输出信号频率被控制在不同的频道上,其频道间隔即频率分辨率为f r 。这便是锁相频率合成器的基本工作原理,图1所示也称为单环频率合成器。图1的单环频率合成器存在一些缺陷,以致于难于同时满足合成器在频带宽 度、频率分辨率和频率转换时间等多方面的性能要求。因此,实际常采用多环频率合成器、双模分频频率合成器或小数分频频率合成器等方法来解决这些矛盾。 1.2 直接数字频率合成器(Direct Digital Frequency Synthesis ———DDS )1. 2.1 DDS 的基本原理 直接数字式频率合成技术是根据周期信号的波形特点(一个周期内不同的相位处对应不同的电压幅度)、 Nyquist 取样定律及数字计算技术,把一系列事先对模拟周 Ξ收稿日期:2002-09-03 作者简介:张建斌(1966-),男(汉族),陕西人,副教授,主要从事频率合成、无线通信研究.

降低功耗的方法:软件和硬件两方面。 1 硬件设计 1.1 选用尽量简单的CPU内核。 单片机的运行速度越快,功耗越大。复杂的CPU内部集成度高,工功能亲强大,但片内晶体管多。漏电电流过大。 1.2选用低电压系统 低电压供电系统可以降低系统的工作电流,从而降低功耗。 1.3 选择带有低功耗模式的系统 1.4 选择合适的时钟方案 1)系统总线频率尽量低。 单片机内部总电流消耗分为:运行电流和漏电流。 单片机集成度越高环境温度越高,漏电流越大。 单片机的运行电流几乎和他的时钟频率成正比。所以子啊满足系统要求的前提下时钟频率尽量小。 2)时钟设计方案 是否使用锁相环。使用内部晶振还是外部晶振。单片机时钟频率可以由软件控制。单片机使用外部较低的振荡器,通过软件控制,系统可以在一个很大的范围内部调整,得到较高的总线时钟。使用外部晶振且不使用锁相环是功耗最小的一种。 可以根据系统需求使用双时钟:一个高速时钟一个低速时钟。处理事件时使用高速时钟,空闲时使用低速时钟。可以有有效降低功耗。

2 应用软件设计 2.1 中断代替查询服务。中断方式CPU在无任务是可进入待机模式。而查询模式CPU必须不断地访问IO口,故功耗较大。 2.2 用宏代替用子程序。调用子程序需要在RAM中进行入栈出栈的操作,带来不必要的功耗。宏在编译时展开,程序顺序执行,功耗低。但代码量大。 2.3 减少CPU的运算量 1)用查表的方法代替实时计算。 2)避免计算过程中的过度运算。 3)尽量使用短的数据类型。 2.4 让IO口间歇运行。不用的IO口设置成输入或输出,用上拉电阻拉高。 低功耗动态时钟实现 MSP430基础时钟模块包含以下3个时钟输入源。 1)LFXT1CLK 低频时钟源:由LFXT1振荡器产生(如图2所示)。通过软件将状态寄存器中OSCOff复位后,LFXT1开始工作,即系统采用低频工作。如果LFXT1CLK没有用作SMCLK或MCLK信号,则可以用软件将OSCOff置位,禁止LFXT1工作。 2)XT2CLK高频时钟源:由XT2振荡器产生。它产生时钟信号XT2CLK,其工作特性与LFXT1振荡器工作在高频模式时类似。可简单地通过软件设置XT2振荡器是否工作,当XT2CLK没有用作SMCLK或

■TK2118-3118调频率方法 1.按住MONI键+DIAL键开机至显示SELF; 2.按一下LOW显CH1,转动频道旋钮"ENC"选择所需信道; 3.按一下PTT键显------2,按一下LOW键显示接收频率,按住 "1"键转动频道旋钮"ENC"调整数,松开 "1"键转动频道旋钮 "ENC"调小数,按PTT键直到显示-------4,按一下LOW显示出发射频率,调整方法与调整接收频率相同。按PTT键直到显示CH2 。此时一信道已存好。 4.选择其他信道的设置,请重复以上的步骤。按FUNC显示SELF,关机---ok! ■TK3118调选呼方法 写完频率,调至(可选信令),选择DTMF,调至于》》3 符号,显示频道编辑---频道1。选择第六项,XP不静音选择(载波+DTMF)点击确认。点击编缉,选择DTMF(双音多频) (D),点击编缉,选择DTMF键制式或(12键或16键)点确认。点解码,选择: DTMF信令。选择呼叫 中间代码 # 组代码关:选择(ABCD*#) 呼叫报警常规或连续 自动应答 自动复位定时器(妙) ID代码输入自身码 ■TK3118调VOX方法 1.开机; 2.长按FUNC两秒至"F"闪烁; 3.按"LOW"---VOX闪烁; 4.旋钮选择等级,建议设置为1,不然延时过长。 ■TK208-308调频方法 1. 清频:按住PTT+CSET+开机; 2. 写频:按MONI,液晶板上显示的频点大数150.00闪动,此时调出所需的频点,按一下CSET选择信道数,为第一频01开始) ,按一下CSET存入接收频点; 3. 若发射为异频时再按一下MONI先调出发射频点,按住PTT键不放,按两下CSET和REV显示+.- 4. 显示CH状态:按住PTT键和REV键开机; 5. 查看频:按住PTT+CTCSS开机,再按一下LOW即可进入维修模式。 ■TK-308的功能设置方法 TK208/308对讲机有三大模式即频率设置模式,维修模式和用户使用模式,进行功能设置时应进入频率设置模式。打开盖后,

频率合成实验(虚拟实验) (一)锁相环频率合成器 示波器1‐6波形

由示波器1的波形可以看出前置分频器输出频率为1Mhz,通过计算输出方波波形的频率,可得出fout=fr*synN/SynM的关系。通过示波器3的波形可看出,低通滤波器滤除了鉴相器输出的无用的高频成分和其它干扰分量。通过环路的调节,输入参考信号和下分频器的输出信号之间相位差达到最小。当环路趋近于锁定,滤波器输出稳定的控制电压用这个电压去控制VCO,最终使其输出频率稳定不再变化,此时输入参考时钟信号和下分频模块的输出信号之间频率相等,相位差不随时间变化,达到锁定状态。由上图可得各节点输出信号的幅度相同,频率为f1=fr/M=3Mhz/3=1MHz;f2=2MHz;f4=fo=10MHz;f5=1MHz;f6=fr=3MHz。各理论值与实验值相等. 示波器 3中的 VCO的控制电压的变化曲线,其从开始阶跃到固定值间经历的时间为1.4× 10^(-4) s,即为环路的锁定时间。稳定值为1.75V。

分析:(将synSen的初始值为3e6与5e6与初始情况作比较) (1)改变synSen的初始值,无论是增大还是减小,除示波器3外,其余示波器波形的周期幅度均没有变化,说明改变压控振荡器的压控灵敏度不会改变输出信号的频率。 (2)synSen的初始值为3e6,即相对4e6减小,示波器3中的电压最大值增大,稳定值也增大,环路锁定时间增大。synSen的初始值为5e6,即相对4e6增大,示波器3中的电压最大值减小,稳定值也减小,环路锁定时间1.2×10﹣4 s,减小。 (3)对于基本单环频率合成器,捕获时间tp=4/ζwn=8Nτ1/τ2K0K d,压控灵敏度K0增大,捕获时间减小。

LD27L2 双通道精密运算放大电路 1、概述 LD27L2是一款有极低失调电压、高输入阻抗、轨对轨的运算放大器电路。主要应用于各种需要使用精密运算放大器的领域,其特点如下: z极低的输入失调电压,典型条件下小于1mV; z超低功耗,静态工作电流小于3uA z宽电压工作范围,1.8V~6.0V z高输入阻抗,典型为1013Ω; z超低的失调点偏移 z单位增益带宽14KHz z封装形式:SOP8 2、功能框图与引脚说明 2. 1、功能框图

2. 2、引脚排列图 2. 3、引脚说明与结构原理图 序号管脚名功能描述 1 OUT1 运放1的输出端 2 IN1‐ 运放1的反向输入端 3 IN1+ 运放1的正向输入端 4 GND 电源地 5 IN2+ 运放2的正向输入端 6 IN2‐ 运放2的反向输入端 7 OUT2 运放2的输出端 8 VDD 电源输入端

3、电特性 3. 1、极限参数 参 数 名 称 符 号 额 定 值 单 位 最大电源电压 IVsmax 6 V 输入电压范围 V I GND-0.3~VDD V 差分输入电压 VDD-GND V 工作环境温度 T amb -40~+85 ℃ 贮存温度 T stg -55~+125 ℃ 3. 2、电特性(VDD=2.2~5V ,T A =25℃) 参 数 名 称 符 号 测 试 条 件规 范 值 单 位最小 典型最大 工作电压 V DD 1.8 - 6.0 V 静态工作电流 I DD - 0.8 3 uA 输入失调电压 V OS - 1 2 mV 输入失调温度系数 -40℃~+85℃ - 1.3 - uV/℃电源抑制 V PSRR - 85 90 dB 输入偏置电流 I B - 1 - pA 输入失调电流 I OS - 1 - pA 共模输入阻抗 Z CM - 1013- Ω 差模输入阻抗 Z DIFF - 1013- Ω 共模输入电压 V CMR GND-0.3- VDD+0.3 V 共模抑制比 CMRR VDD=5V 60 90 - dB 单位增益带宽 B I VI=10mV 14 KHz 输出短路电流 I SC VDD=2.2V - 3 - mA VDD=5V - 20 - mA

写频软件: 信令 Siganling + Basic + PTT ID : 12345678 (8位) + PTT ID Type : 可选Pre (前发), Post (后发), Both (前后发), + Advanced + Pretime(ms) (发射前时间) + DTMF Tx Duration(ms) (双音多频的发射音调的持续时间) + DTMF Tx Tone Iinterval(ms) (双音多频发射音的间隔时间) 再到你要发射的信道 Conventional Personality + Option + PTT ID 前打勾 从“销售商设置”切换到用户设置: 关闭对讲机,同时按下PTT和MOMITOR和+键,并打开对讲机,此时LCD显示屏显示PROTEC(保护)的字样,按下PTT键切换到“用户设置”, 按任何键则取消切换,关闭对讲机,此时对讲机以“用户设置”运行. 从用户设置切换到销售商设置 关闭对讲机,同时按下PTT和M0NITOR和+键,并打开对讲机,此时LCD显示屏显示PRO-CLR(保护撤销)的字样,按下PTT键确认切换到销售商,按下其它任何键撤销切换,关闭对讲机,此时对讲机以销售商设置运行. 2.进入编程模式 关闭对讲机,按着MON键开机,对讲机发出一声振钤声音,进入编程模式,□指示显示出现3.退出编程模式 要退出编号模式,请直接关闭对讲机. 4.调出编程模式参数 在销售商设置中,编程模式参数分三类:RW(本机通用),信道(001----099)和VFO(可变频操作).利用+或---键,可以在各类别中移动:RW---CH001-----CHXXX-----VFO,选定类别后,按PTT或MON键在各参数中移动. 5.信道参数编辑表: 信道参数说明范围出厂默认备注 CH—XXX信道开/关CH—OFF CH—ONCH--ON按+ 或–选择开或关 RX--XXXX接收频率本机确定的频率利用键盘输入 TX--XXXX发射频率本机确定的频率利用键盘输入 RPL--XXX接收PL/DPLRPL--OFF TPL--XXX发射PL/DPL TOC-XXX关闭代码/反向字串TOC---ON使接收方的对讲机静音以探测载波的损失 XXX---POWER功率电平HI.LOW.ECO.RX ONLYHI POWERECO功率小于500mw:rx only 仅作为接收信道 BCL--XXX繁忙信道锁定BCL-OFF

描述: GS8551/GS8552/GS8554放大器是单/双/四电源,微功耗,零漂移CMOS运算放大器,这些放大器提供1.8MHz的带宽,轨至轨输入和输出以及1.8V至5.5V的单电源供电。 GS855X使用斩波稳定技术来提供非常低的失调电压(最大值小于5μV),并且在整个温度范围内漂移接近零。每个放大器的静态电源电流低至180μA,输入偏置电流极低,仅为20pA,因此该器件是低失调,低功耗和高阻抗应用的理想选择。 GS855X提供了出色的CMRR,而没有与传统的互补输入级相关的分频器。该设计为驱动模数转换器带来了卓越的性能 转换器(ADC),而不会降低差分线性度。 GS8551提供SOT23-5和SOP-8封装。 GS8552提供MSOP-8和SOP-8封装。GS8554 Quad具有绿色SOP-14和TSSOP-14封装。在所有电源电压下,-45oC至+ 125oC的扩展温度范围提供了额外的设计灵活性。 特点: + 1.8V?+ 5.5V单电源供电?嵌入式RF抗EMI滤波器 ?轨到轨输入/输出?小型封装: ?增益带宽乘积:1.8MHz(典型@ 25°C)GS8551采用SOT23-5和SOP-8封装?低输入偏置电流:20pA(典型值@ 25°C)GS8552采用MSOP-8和SOP-8封装?低失调电压:30μV(最大@ 25°C)GS8554采用SOP-14和TSSOP-14封装?静态电流:每个放大器180μA(典型值) ?工作温度:-45°C?+ 125°C ?零漂移:0.03μV / oC(典型值) 应用: 换能器应用 ?手持测试设备 ?温度测量 ?电池供电的仪器 ?电子秤