基于FPGA技术实现62256 Sram芯片的读写控制及校验器的Quartus II程序设计

- 格式:docx

- 大小:235.98 KB

- 文档页数:12

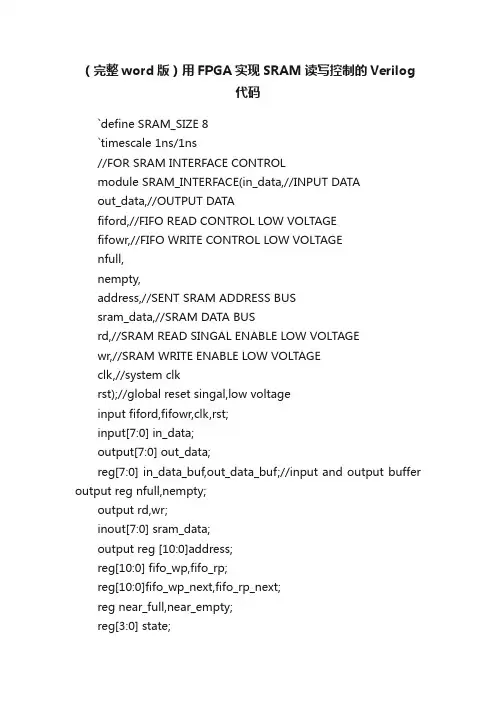

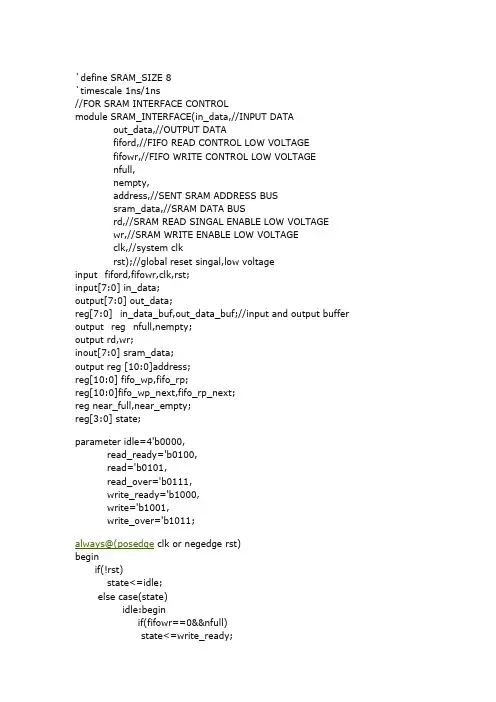

(完整word版)用FPGA实现SRAM读写控制的Verilog代码`define SRAM_SIZE 8`timescale 1ns/1ns//FOR SRAM INTERFACE CONTROLmodule SRAM_INTERFACE(in_data,//INPUT DATAout_data,//OUTPUT DATAfiford,//FIFO READ CONTROL LOW VOLTAGEfifowr,//FIFO WRITE CONTROL LOW VOLTAGEnfull,nempty,address,//SENT SRAM ADDRESS BUSsram_data,//SRAM DATA BUSrd,//SRAM READ SINGAL ENABLE LOW VOLTAGEwr,//SRAM WRITE ENABLE LOW VOLTAGEclk,//system clkrst);//global reset singal,low voltageinput fiford,fifowr,clk,rst;input[7:0] in_data;output[7:0] out_data;reg[7:0] in_data_buf,out_data_buf;//input and output buffer output reg nfull,nempty;output rd,wr;inout[7:0] sram_data;output reg [10:0]address;reg[10:0] fifo_wp,fifo_rp;reg[10:0]fifo_wp_next,fifo_rp_next;reg near_full,near_empty;reg[3:0] state;parameter idle=4'b0000,read_ready='b0100,read='b0101,read_over='b0111,write_ready='b1000,write='b1001,write_over='b1011;always@(posedge clk or negedge rst) beginif(!rst)state<=idle;else case(state)idle:beginif(fifowr==0&&nfull)state<=write_ready;else if(fiford==0&&nempty)state<=read_ready;elsestate<=idle;endread_ready:state<=read;read:beginif(fiford==1)state<=read_over;elsestate<=read;endread_over:state<=idle;write_ready:state<=write;write:beginif(fifowr==1)state<=write_over;elsestate<=write;endwrite_over:state<=idle;default:state<=idle;endcaseendassign rd=~state[2];assign wr=(state==write)?fifowr:1'b1;always@(posedge clk)beginif(~fifowr)in_data_buf<=in_data;end//===================================== ========== ==============always@(state or fiford or fifowr or fifo_wp or fifo_rp)beginif(state[2]||~fiford)address=fifo_rp;else if(state[3]||~fifowr)elseaddress='bz;end//===================================== ========== ==================assign out_data=(state[2])?sram_data:8'bz;always@(posedge clk)beginif(state==read)out_data_buf<=sram_data;end//===================================== ========== ===always@(posedge clk or negedge rst)beginif(!rst)fifo_rp<=0;else if(state==read_over)fifo_rp<=fifo_rp_next;end//===================================== ========== ====always@(fifo_rp)beginif(fifo_rp==`SRAM_SIZE-1)fifo_rp_next=0;elsefifo_rp_next=fifo_rp+1;end//===================================== ========== ======always@(posedge clk or negedge rst)beginif(!rst)fifo_wp<=0;else if(state==write_over)fifo_wp<=fifo_wp_next;end//===================================== ========== ===always@(fifo_wp)beginif(fifo_wp==`SRAM_SIZE-1)elsefifo_wp_next=fifo_wp+1;end//===================================== ========== ====always@(posedge clk or negedge rst)beginif(!rst)near_empty<=1'b0;else if(fifo_wp==fifo_rp_next)near_empty<=1'b1;elsenear_empty<=1'b0;end//===================================== ========== ========always@(posedge clk or negedge rst)beginif(!rst)nempty<=1'b0;else if(near_empty&&state==read)nempty<=1'b0;else if(state==write)nempty<=1'b1;end//===================================== ========== =======always@(posedge clk or negedge rst)beginif(!rst)near_full<=1'b0;else if(fifo_rp==fifo_wp_next)near_full<=1'b1;elsenear_full<=1'b0;end//===================================== ========== =====always@(posedge clk or negedge rst)beginif(!rst)nfull<=1'b1;else if(near_full&&state==write)nfull<=1'b0;else if(state==read)nfull<=1'b1;end//===================================== ========== ============endmodule。

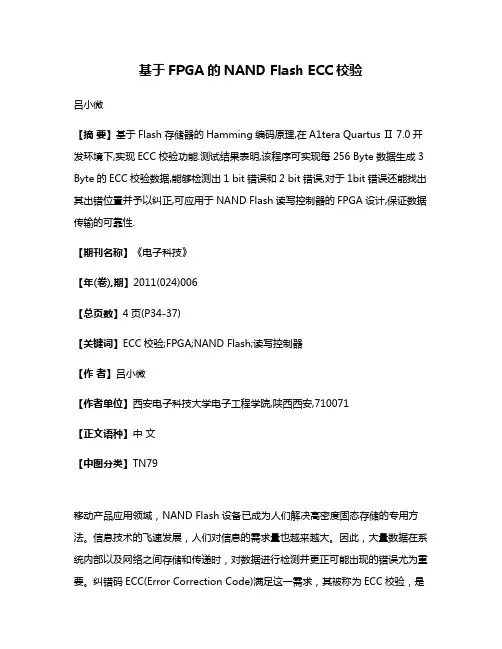

基于FPGA的NAND Flash ECC校验吕小微【摘要】基于Flash存储器的Hamming编码原理,在A1tera Quartus Ⅱ 7.0开发环境下,实现ECC校验功能.测试结果表明,该程序可实现每256 Byte数据生成3 Byte的ECC校验数据,能够检测出1 bit错误和2 bit错误,对于1bit错误还能找出其出错位置并予以纠正,可应用于NAND Flash读写控制器的FPGA设计,保证数据传输的可靠性.【期刊名称】《电子科技》【年(卷),期】2011(024)006【总页数】4页(P34-37)【关键词】ECC校验;FPGA;NAND Flash;读写控制器【作者】吕小微【作者单位】西安电子科技大学电子工程学院,陕西西安,710071【正文语种】中文【中图分类】TN79移动产品应用领域,NAND Flash设备已成为人们解决高密度固态存储的专用方法。

信息技术的飞速发展,人们对信息的需求量也越来越大。

因此,大量数据在系统内部以及网络之间存储和传递时,对数据进行检测并更正可能出现的错误尤为重要。

纠错码ECC(Error Correction Code)满足这一需求,其被称为ECC校验,是一种常用于NAND Flash读写控制器的校验编码[1-2]。

ECC校验负责检测错误、维护ECC信息、更正由原数值改变了的单比特错误。

所有ECC的操作处理都可由一个ECC模块来控制,其作为一种简单地存储—映射接口,放置在NAND器件和处理器接口之间。

该模块一般包含Hamming编码产生模块和出错位置模块,分别用于产生ECC校验码和计算出错位置[3-5]。

1 Hamming编码Hamming编码计算简单。

广泛用于NAND Flash的Hamming算法,通过计算块上数据包得到2个ECC值。

为计算ECC值,数据包中的比特数据要先进行分割,如1/2组、1/4组、1/8组等,直到其精度达到单个比特为止,以8 bit即1 Byte 的数据包为例进行说明,如图1所示。

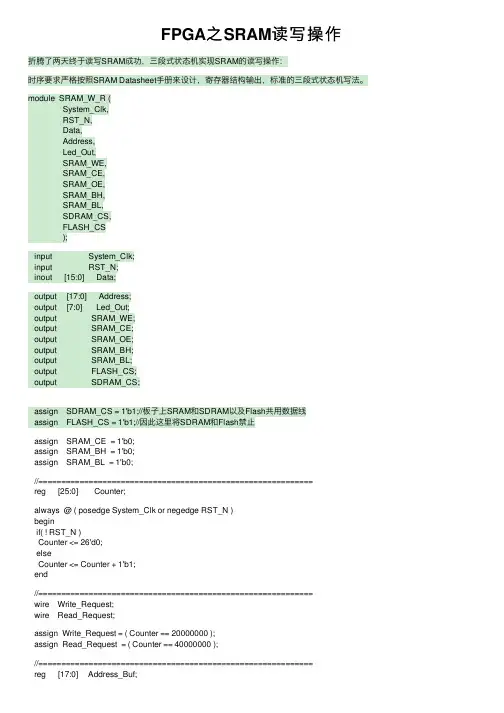

FPGA之SRAM读写操作折腾了两天终于读写SRAM成功,三段式状态机实现SRAM的读写操作:时序要求严格按照SRAM Datasheet⼿册来设计,寄存器结构输出,标准的三段式状态机写法。

module SRAM_W_R (System_Clk,RST_N,Data,Address,Led_Out,SRAM_WE,SRAM_CE,SRAM_OE,SRAM_BH,SRAM_BL,SDRAM_CS,FLASH_CS);input System_Clk;input RST_N;inout [15:0] Data;output [17:0] Address;output [7:0] Led_Out;output SRAM_WE;output SRAM_CE;output SRAM_OE;output SRAM_BH;output SRAM_BL;output FLASH_CS;output SDRAM_CS;assign SDRAM_CS = 1'b1;//板⼦上SRAM和SDRAM以及Flash共⽤数据线assign FLASH_CS = 1'b1;//因此这⾥将SDRAM和Flash禁⽌assign SRAM_CE = 1'b0;assign SRAM_BH = 1'b0;assign SRAM_BL = 1'b0;//============================================================reg [25:0] Counter;always @ ( posedge System_Clk or negedge RST_N )beginif( ! RST_N )Counter <= 26'd0;elseCounter <= Counter + 1'b1;end//============================================================wire Write_Request;wire Read_Request;assign Write_Request = ( Counter == 20000000 );assign Read_Request = ( Counter == 40000000 );//============================================================reg [17:0] Address_Buf;always @ ( posedge System_Clk or negedge RST_N )beginif( ! RST_N )Address_Buf <= 18'd0;elsebeginif( Counter == 26'd5******* )Address_Buf <= Address_Buf + 1'b1;elseAddress_Buf <= Address_Buf;endend//============================================================= reg [15:0] Data_Buf;always @ ( posedge System_Clk or negedge RST_N )beginif( ! RST_N )Data_Buf <= 16'd0;elsebeginif( Counter == 26'd5******* )Data_Buf <= Data_Buf + 1'b1;elseData_Buf <= Data_Buf;endend//============================================================= reg Link;assign Data = Link ? Data_Buf : 16'hzzzz;//============================================================= reg [2:0] Next_State;reg [2:0] Current_State;parameter IDLE = 3'b000;parameter READ_1 = 3'b001;parameter READ_2 = 3'b010;parameter WRITE_1 = 3'b011;parameter WRITE_2 = 3'b100;//============================================================= reg [15:0] Led_Buf;always @ ( posedge System_Clk or negedge RST_N )beginif( ! RST_N )Current_State <= IDLE;elseCurrent_State <= Next_State;end///////////////////////////////////////////////////////////////reg [17:0] Address;always @*beginNext_State = 3'bx;Address = 18'bx;case( Current_State )IDLE:beginAddress = Address_Buf;if( Write_Request )Next_State = WRITE_1;else if( Read_Request )Next_State = READ_1;elseNext_State = IDLE;endWRITE_1:beginNext_State = WRITE_2;endWRITE_2:beginNext_State = IDLE;endREAD_1:beginNext_State = READ_2;endREAD_2:beginNext_State = IDLE;enddefault : Next_State = IDLE;endcaseend///////////////////////////////////////////////////////////////reg SRAM_WE;reg SRAM_OE;always @ ( posedge System_Clk or negedge RST_N ) beginif( !RST_N )beginLink <= 1'b0;SRAM_OE <= 1'b1;SRAM_WE <= 1'b1;endelsebeginLink <= 1'b0;SRAM_OE <= 1'b1;SRAM_WE <= 1'b1;case ( Next_State )IDLE:beginSRAM_OE <= 1'b1;endWRITE_1:beginLink <= 1'b1;SRAM_WE <= 1'b0;endWRITE_2:beginSRAM_WE <= 1'b0; Link <= 1'b1;endREAD_1:beginSRAM_OE <= 1'b0; endREAD_2:beginSRAM_OE <= 1'b0;Led_Buf <= Data;endendcaseendendassign Led_Out = Led_Buf[7:0]; endmodule。

一种QuartusII软件编程的数字鉴相器摘要:本文介绍常用的cpld芯片max7128s和开发工具quar- tusii的功能及使用方法,并用该软件设计编程了基于cpld的数字鉴相器。

该鉴相器可实现移相信号与基准信号的相位差鉴别,对信号在周期内进行检测。

通过软件仿真,可以满足信号相位差鉴别的需求。

关键词:cpld quartusii 数字鉴相器0 引言目前的鉴相器,测量相位差通常采用置位复位触发器或者异或电路[1],也有用单片机组成的数字测量电路[2]。

这种类型的鉴相器分立元件多,电路布线复杂,而且工作频率低。

采用cpld的数字式鉴相器只用到一块芯片,且这块芯片还可以提供额外器件的编程,方便与电路的整合,并且工作频率高。

本文用quartusii软件设计了一种采用复杂可编程逻辑器件的数字鉴相器,适合特殊需要的系统,经仿真得到结果满足设计要求。

1 cpld芯片epm7128slc简介为了弥补pal、gal等器件只能实现规模较小的电路这种缺陷,在上个世纪80年代,世界上主流芯片制造厂商xilinx公司和altera公司分别改进了原有芯片的结构及功能,推出了类似于pal 结构的cpld,即扩展型复杂可编程逻辑器件[3](complex programmable logic device)。

这类产品兼容了可编程逻辑器件d 和通用门阵列的优点,同时又增加了自身的特点,比如体系结构灵活,集成度非常高,编程方法十分灵活,可实现更大规模的集成电路等等。

基于以上优点,自从复杂可编程逻辑器件问世以来,该类产品在设计产品试验电路和样机的生产中应用十分普遍。

目前,大部分中规模甚至大规模的数字集成电路都采取cpld器件来进行试验及应用。

经过几十年的发展,主流芯片制造厂商altera公司相继开发了多款复杂可编程逻辑器件产品,形成了自己的产品系列,在复杂可编程逻辑器件市场上占有了很大份额。

altera公司生产了诸如max3000、max7000、max9000等系列产品。

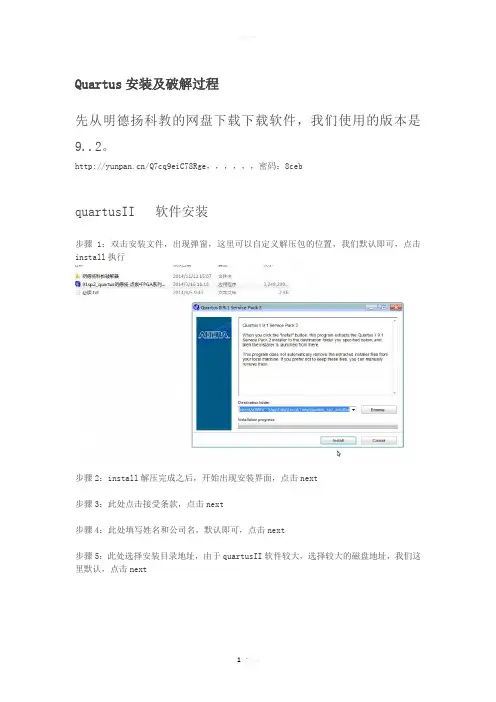

Quartus安装及破解过程先从明德扬科教的网盘下载下载软件,我们使用的版本是9..2。

/Q7cq9eiC78Rge,,,,,,密码:8cebquartusII 软件安装步骤1:双击安装文件,出现弹窗,这里可以自定义解压包的位置,我们默认即可,点击install执行步骤2:install解压完成之后,开始出现安装界面,点击next步骤3:此处点击接受条款,点击next步骤4:此处填写姓名和公司名,默认即可,点击next步骤5:此处选择安装目录地址,由于quartusII软件较大,选择较大的磁盘地址,我们这里默认,点击next步骤6:以后几步全部默认即可,直到出现进度条,开始安装步骤7:安装完成之后会提示是否创建快捷键,我们点击是步骤8:quartus II talkback弹窗上,点击取消步骤9:单击完成finishquartusII 软件破解步骤1:我们打开刚安装好的quartus软件,会提示软件没有破解,我们点击取消步骤2:打开破解必读文档,按照文档里面的步骤进行破解步骤3:打开命令行,输入ipconfig/all,找到本地连接地址记录下来,注意笔记本要选择本地连接,不能选择无线网卡的地址步骤4:我们将破解器文件夹中的license.DAT文件找到,以记事本打开,将里面的hostid 改成步骤3记录的本地连接地址,一共有两个地方,然后另存到 c:/altrera/91sp2文件夹下,文件名默认即可。

步骤5:我们再次确认下c:/altrera/91sp2这个文件夹有没有license.DAT修改后的文件,查看下里面的网卡地址是否和我们的计算机本地连接地址一致。

步骤6:打开未破解的quartus软件,选择菜单栏的tool———>License setup步骤7:在出现的license setup弹窗上,取消勾选Use LM_LICENSE_FILE variable步骤8:点击上面的浏览按键,来选择之前创建的license.DAT文件,之前创建的license.DAT目录地址是c:/altrera/91sp2,选好之后,点击打开,打开之后,下面会出现版本以及到期日期等,点击ok,关掉quartus。

`define SRAM_SIZE 8`timescale 1ns/1ns//FOR SRAM INTERFACE CONTROLmodule SRAM_INTERFACE(in_data,//INPUT DATAout_data,//OUTPUT DATAfiford,//FIFO READ CONTROL LOW VOLTAGEfifowr,//FIFO WRITE CONTROL LOW VOLTAGEnfull,nempty,address,//SENT SRAM ADDRESS BUSsram_data,//SRAM DATA BUSrd,//SRAM READ SINGAL ENABLE LOW VOLTAGEwr,//SRAM WRITE ENABLE LOW VOLTAGEclk,//system clkrst);//global reset singal,low voltageinput fiford,fifowr,clk,rst;input[7:0] in_data;output[7:0] out_data;reg[7:0] in_data_buf,out_data_buf;//input and output buffer output reg nfull,nempty;output rd,wr;inout[7:0] sram_data;output reg [10:0]address;reg[10:0] fifo_wp,fifo_rp;reg[10:0]fifo_wp_next,fifo_rp_next;reg near_full,near_empty;reg[3:0] state;parameter idle=4'b0000,read_ready='b0100,read='b0101,read_over='b0111,write_ready='b1000,write='b1001,write_over='b1011;always@(posedge clk or negedge rst)beginif(!rst)state<=idle;else case(state)idle:beginif(fifowr==0&&nfull)state<=write_ready;else if(fiford==0&&nempty)state<=read_ready;elsestate<=idle;endread_ready:state<=read;read:beginif(fiford==1)state<=read_over;elsestate<=read;endread_over:state<=idle;write_ready:state<=write;write:beginif(fifowr==1)state<=write_over;elsestate<=write;endwrite_over:state<=idle;default:state<=idle;endcaseendassign rd=~state[2];assign wr=(state==write)?fifowr:1'b1;always@(posedge clk)beginif(~fifowr)in_data_buf<=in_data;end//=============================================== ==============always@(state or fiford or fifowr or fifo_wp or fifo_rp)beginif(state[2]||~fiford)address=fifo_rp;else if(state[3]||~fifowr)elseaddress='bz;end//=============================================== ==================assign out_data=(state[2])?sram_data:8'bz;always@(posedge clk)beginif(state==read)out_data_buf<=sram_data;end//=============================================== ===always@(posedge clk or negedge rst)beginif(!rst)fifo_rp<=0;else if(state==read_over)fifo_rp<=fifo_rp_next;end//=============================================== ====always@(fifo_rp)beginif(fifo_rp==`SRAM_SIZE-1)fifo_rp_next=0;elsefifo_rp_next=fifo_rp+1;end//=============================================== ======always@(posedge clk or negedge rst)beginif(!rst)fifo_wp<=0;else if(state==write_over)fifo_wp<=fifo_wp_next;end//=============================================== ===always@(fifo_wp)beginif(fifo_wp==`SRAM_SIZE-1)elsefifo_wp_next=fifo_wp+1;end//=============================================== ====always@(posedge clk or negedge rst)beginif(!rst)near_empty<=1'b0;else if(fifo_wp==fifo_rp_next)near_empty<=1'b1;elsenear_empty<=1'b0;end//=============================================== ========always@(posedge clk or negedge rst)beginif(!rst)nempty<=1'b0;else if(near_empty&&state==read)nempty<=1'b0;else if(state==write)nempty<=1'b1;end//=============================================== =======always@(posedge clk or negedge rst)beginif(!rst)near_full<=1'b0;else if(fifo_rp==fifo_wp_next)near_full<=1'b1;elsenear_full<=1'b0;end//=============================================== =====always@(posedge clk or negedge rst)beginif(!rst)nfull<=1'b1;else if(near_full&&state==write)nfull<=1'b0;else if(state==read)nfull<=1'b1;end//=============================================== ============endmodule。

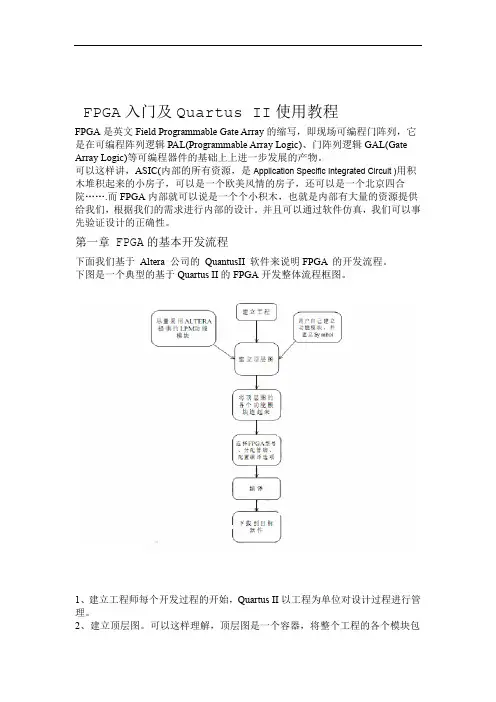

FPGA入门及Quartus II使用教程FPGA是英文Field Programmable Gate Array的缩写,即现场可编程门阵列,它是在可编程阵列逻辑PAL(Programmable Array Logic)、门阵列逻辑GAL(Gate Array Logic)等可编程器件的基础上上进一步发展的产物。

可以这样讲,ASIC(内部的所有资源,是Application Specific Integrated Circuit )用积木堆积起来的小房子,可以是一个欧美风情的房子,还可以是一个北京四合院…….而FPGA内部就可以说是一个个小积木,也就是内部有大量的资源提供给我们,根据我们的需求进行内部的设计。

并且可以通过软件仿真,我们可以事先验证设计的正确性。

第一章 FPGA的基本开发流程下面我们基于Altera 公司的QuantusII 软件来说明FPGA 的开发流程。

下图是一个典型的基于Quartus II的FPGA开发整体流程框图。

1、建立工程师每个开发过程的开始,Quartus II以工程为单位对设计过程进行管理。

2、建立顶层图。

可以这样理解,顶层图是一个容器,将整个工程的各个模块包容在里边,编译的时候就将这些模块整合在一起。

也可以理解为它是一个大元件,比如一个单片机,内部包含各个模块,编译的时候就是生成一个这样的大元件。

3、采用ALTERA公司提供的LPM功能模块。

Quartus软件环境包含了大量的常用功能模块,比如计数器、累加器、比较器等等。

4、自己建立模块。

由于有些设计中现有的模块功能不能满足具体设计的要求,那就只能自己设计。

使用硬件描述语言,当然也可以用原理图的输入方法,可以独立的把它们当成一个工程来设计,并且生成一个模块符号(Symbol),类似于那些LPM功能模块。

这里可以理解为,如果我们需求的滤波器,没有现成的合适的,那我们可以通过LC自己来搭建一个滤波器。

5、将顶层图的各个功能模块连线起来。

一、设计原理1. 引言随着数字信号处理技术的不断发展,大容量可编程逻辑器件的不断涌现,FPGA技术越来越多地应用在大规模集成电路设计中。

在此硬件系统设计中,经常会遇到需要大容量的数据存储的情况,针对FPGA中内部Block RAM 有限的缺点,提出了将FPGA与外部SRAM相结合来改进设计的方法。

2.SRAM2.1 SRAM是英文Static RAM的缩写,中文含义为静态随机访问存储器,它是一种类型的半导体存储器。

“静态”是指只要不掉电,存储在SRAM 中的数据就不会丢失。

SRAM是一种易失性存储器,它只有在电源保持连续供应的情况下才能够保持数据。

“随机访问”是指存储器的内容可以以任何顺序访问,而不管前一次访问的是哪一个位置。

它是一种具有静止存取功能的内存,不需要刷新电路即能保存它内部存储的数据。

SRAM具有较高的性能,但是SRAM也有它的缺点,即它的集成度较低,相同容量的DRAM内存可以设计为较小的体积,但是SRAM却需要很大的体积。

SRAM中的每一位均存储在四个晶体管当中,这四个晶体管组成了两个交叉耦合反向器。

这个存储单元具有两个稳定状态,通常表示为0和1。

另外还需要两个访问晶体管用于控制读或写操作过程中存储单元的访问。

因此,一个存储位通常需要六个MOSFET。

对称的电路结构使得SRAM的访问速度要快于DRAM。

SRAM比DRAM访问速度快的另外一个原因是SRAM可以一次接收所有的地址位,而DRAM则使用行地址和列地址复用的结构。

2.2 SRAM的工作原理:假设准备往图2的6T存储单元写入“1”,先将某一组地址值输入到行、列译码器中,选中特定的单元,然后使写使能信号WE有效,将要写入的数据“1”通过写入电路变成“1”和“0”后分别加到选中单元的两条位线BL,BLB上,此时选中单元的WL=1,晶体管N0,N5打开,把BL,BLB 上的信号分别送到Q,QB点,从而使Q=1,QB=0,这样数据“1”就被锁存在晶体管P2,P3,N3,N4构成的锁存器中。

一种BCH(63,56)译码方法及其FPGA实现

刘道明; 白云飞

【期刊名称】《《微计算机信息》》

【年(卷),期】2011(027)009

【摘要】BCH码是很好的线性纠错码类,具有严格的代数结构、构造方便、编码简单。

本文提出一种符合CCSDS的BCH(63,56)译码方法,译码方法相对简单,便于硬件实现译码,并具有计算速度快、占用资源少的特点。

译码采用Xilinx的Spar-tan3XC3S1500FPGA来实现,满足航天分包遥控的标准。

【总页数】3页(P88-90)

【作者】刘道明; 白云飞

【作者单位】

【正文语种】中文

【中图分类】TP919.3

【相关文献】

1.一种BCH码的新型译码方法及其FPGA器件实现 [J], 柯炜;殷奎喜

2.DTMB系统中BCH译码算法及其FPGA实现 [J], 吴子静;苏凯雄

3.可变码率BCH码编译码的FPGA实现 [J], 刘冀;孙玲

4.一种纠3错BCH译码器的FPGA设计 [J], 张国华;王菊花

5.并行高效BCH译码器设计及FPGA实现 [J], 张湘贤;杨涛;魏东梅;向玲

因版权原因,仅展示原文概要,查看原文内容请购买。

基于FPGA的AMI编解码设计作者:左磊程煜洋赵晓东方圆来源:《现代信息科技》2020年第20期摘要:在基于FPGA的基带传输系统研究中,通过对AMI码型的研究,提出了一种通过Altera公司Cyclone Ⅱ系列EP2C35F672C6芯片实现AMI编解码设计的方法。

使用Quartus Ⅱ和ModelSim仿真平台对设计方法进行仿真,结果符合AMI编解码原理,解码输出与基带信号一致,最终结果符合预期。

AMI编解码能够实现在电路相对简单的情况下,即使码元极性与发端相反,接收端也能正确接收,为信号传输带来了一种可靠的方法。

关键词:FPGA;AMI;编解码中图分类号:TN912.3 文献标识码:A 文章编号:2096-4706(2020)20-0085-03AMI CODEC Design Based on FPGAZUO Lei,CHENG Yuyang,ZHAO Xiaodong,FANG Yuan(North China University of Technology,Beijing 100144,China)Abstract:In the research of FPGA-based baseband transmission system,through the study of AMI code pattern,a method to realize AMI CODEC fun ction through Altera’s Cyclone Ⅱ series EP2C35F672C6 chip is proposed. Using Quartus Ⅱ and ModelSim simulation platform to simulatethe design method,the result conforms to the AMI CODEC principle,the decoding output is consistent with the baseband signal,and the final result is in line with expectations. AMI CODEC can realize that under the condition that the circuit is relatively simple and the polarity of the code is opposite to that of the originator,the receiver can receive it correctly,which brings a reliable method for signal transmission.Keywords:FPGA;CMI;CODEC0 引言AMI碼全称是传号交替反转码,其对应的波形正负脉冲交替,无直流成分,且具有很小的低频成分,在不允许直流、低频成分通过的信道传输中大量使用。

EDA实验报告

基于FPGA技术实现62256 Sram芯片的读写控制及校

验器的Quartus II程序设计

指导教师:

学号姓名:

实验小组成员:

一、实验目的及程序设计性能要求:

如右图所示,为62256芯片关键图,管脚功能介绍如下:

A0 – A14 地址总线(Address)

D0 /D7 输入/输出口(Input/output)

CS 端口选择(Chip select)

WE 输入始能(Write enable)

OE 输出始能(Output enable)

VCC 电源始能(Power supply)

VSS 接地(Ground)

性能要求:进行芯片进行工作室,CS,OE端口应置低电平。

进行写操作时,WE端口信号应为负脉冲,进行读操作时WE端口应置高电平。

所需设计的控制校验功能如下:正确输出62256芯片所需的使能端信号。

在进行校验工作时,正确的控制读写控制端口WE的电平状态,并顺利输入与输出地址信号及数据信号,并进行实时校验。

校验的具体要求是,共分为两步:第一,向62256芯片中输入地址与数据信号,其中奇数地址输入55,偶数地址输入AA。

直到向所有内存(32KB)中写入数据后,进行读操作。

此时将读入的数据与芯片内实时运算的,内存中应该有的数值进行比较,若值相同则输出为1,否则输出为0。

第二步基本与第一步相同,只需改变奇地址输入为AA,偶地址输入为55。

二、程序设计部分

1.设计方案框图:

2.程序状态转移图:

3.程序流程图:

4.Verilog HDL程序源代码:

module wyw(clk, addr , wr, ce, oe, data, dout,areset,data_reg, realaddr);

inout[7:0] data;

input areset;

input clk;

output wr,oe,ce;

output[14:0] addr;

output dout;

output [7:0] data_reg;

reg[14:0] addr;

output[14:0] realaddr;

reg[14:0] realaddr;

wire[7:0] data;

wire ce=0;

wire oe=0;

reg wr;

reg dout;

parameter Idle=3'h0,

Write_begin=3'h1,

Write_end =3'h2,

Read_begin =3'h3,

Read_end =3'h4;

reg qiuyu;

reg quan;

reg[2:0] STATE;

reg[7:0] data_reg; //程序输入输出端口及状态定义assign data=wr?data_reg:8'hzz; //定义双向数据端口data的值always @(posedge areset or posedge clk ) //时钟上升沿激励及异步复位begin

if (areset) //异步复位设置

begin

wr<=1'b0;

data_reg<=8'h00;

addr<=15'b0;

dout<=1'b0;

STATE<=Idle;

end

else

begin

case(STATE) //非复位情况下程序运行,状态判断Idle: //第一状态Idle的定义

begin

wr<=1;

addr<=15'b0;

realaddr<=15'b0;

data_reg<=8'h00;

STATE=Write_begin;

dout<=1'b0;

qiuyu<=1'b0;

quan<=~quan; //校验步数设定,1,2循环

end

Write_begin: //第二状态Write_begin的定义

begin

addr=addr+15'h1; //地址自加一

realaddr=addr-15'h1; //由于波形显示时直接显示地址自

加一结果,因此加入一个真实地址

的显示

wr<=~wr; //We输出负脉冲的设定

if (quan) //校验步数判断,并输入不同数据

begin

qiuyu<=addr%2; //奇偶地址判断,并存入不同数据

if(qiuyu)

begin

data_reg<=8'h55;

end

else

begin

data_reg<=8'h0AA;

end

STATE=Write_end;

end

else

begin

qiuyu<=addr%2;

if(qiuyu)

begin

data_reg<=8'h0AA;

end

else

begin

data_reg<=8'h55;

end

STATE=Write_end;

end

end

Write_end: //第三状态Write_end定义begin

wr<=~wr; //We输出负脉冲的设定

if(addr==15'h02f) //内存地址满后转入读校验begin

STATE=Read_begin;

addr<=15'h0;

qiuyu<=1'b0;

end

else

STATE=Write_begin; //内存地址未满时继续写数据end

Read_begin: //第三状态Read_begin定义begin //与写入时同理,校验器内部

data_reg寄存器产生正确的地

址数据

addr=addr+15'h1;

realaddr=addr-15'h1;

wr=0;

if (quan)

begin

qiuyu<=addr%2;

if(qiuyu)

begin

data_reg<=8'h55;

STATE=Read_end;

end

else

begin

data_reg<=8'h0AA;

STATE=Read_end;

end

end

else

begin

qiuyu<=addr%2;

if(qiuyu)

begin

data_reg<=8'h0AA;

STATE=Read_end;

end

else

begin

data_reg<=8'h55;

STATE=Read_end;

end

end

end

Read_end : //第五状态Read_end定义

begin

if(addr==15'h02f) //校验完毕后转入第一状态执

行下一步读写校验

begin

STATE=Idle;

addr<=15'h0;

end

else

begin

if(data==data_reg) //从内存中读入数据,与寄存器

内此地址的正确数据进行比较

begin

dout<=1'b1; //比较相同,结果输出1

STATE=Read_begin;

end

else

begin

dout<=1'b0; //比较不同,结果输出0

STATE=Read_begin;

end

end

end

default: STATE=Idle;

endcase

end

end

endmodule

三、程序仿真及验证。

1.功能波形仿真

2.时序波形仿真

4.RTL级电路模拟

四、实验心得及总结:

本实验逻辑复杂,程序编写难度大,要求实现功能多。

本实验编写时曾参考网上的类似程序流程,但程序整体经过大幅修改及优化。

在程序编写过程中,曾出现如下问题:

1.逻辑关系及变量过于复杂使得程序编写陷入困境。

2.关于阻塞赋值与非阻塞赋值的方式选择失误,曾长时间引起程序仿

真时结果错误。

3.网上下载的程序有先天不足级错误。

以上问题的解决方法:

1.从最外层逻辑关系入手,一步一步细化逻辑关系以及程序运行流程,

通过形象的流程图及状态转移图来使程序结构清晰简化,大大加快

编程进度。

2.认真阅读了书本上关于阻塞赋值与非阻塞赋值的相关内容,并结合

仿真时的直观错误,对每一个变量进行筛选,最后通过修改地址赋

值语句为阻塞赋值,成功解决错误。

3.借鉴有用的流程部分,舍弃大部分代码部分,从新设计优化程序。

本次实验中,由于方法得当,加上本学期对《现代电子技术》的认真学习,加上组员的配合,本次试验得以相当高效与成功的完成。

(全实验室第一个完成)同时,我在本次实验中学习到了很多仅仅从书本上学不到的东西,比如实验时的各种技巧与策略,对书本上知识的灵活应用,及在真实实验中必需的严谨精神,相信在今后的学习生活中会帮助我取得更大的进步。

同时也非常感谢王凯老师对我组的认真指导与提出的意见及建议。

2011年12月21日。