布线时的阻抗匹配问题

电路2010-11-07 16:28:22 阅读48 评论0 字号:大中小订阅

特性阻抗

根据传输线理论和信号的传输理论,信号不仅仅是时间变量的函数,同时

还是距离变量的函数,所以信号在

连线上的每一点都有可能变化。因此定义连线的交流阻抗,即变化的电压和变化

的电流之比为传输线的特性阻

抗。

Z(w):理想传输线的特性阻抗,单位Ω;L: 理想传输线的电感,H/mm;C:理

想传输线的电容,F/mm。

传输线的特性阻抗只与信号连线本身的特性相关,在实际电路中,导线本

身电阻值小于系统的分布阻抗,特

别是在高频电路中,特性阻抗主要取决于连线的单位分布电容和单位分布电感带

来的分布阻抗。理想传输线的

特性阻抗只取决于连线的单位分布电容和单位分布电感。

对于确定的传输线而言,其特性阻抗为一个常数。信号的反射现象就是因为信号的驱动端和传输线的特性阻抗以及接收端的阻抗不一致所造成的。信号在传输的过程中,如果传输路径上的特征阻抗发生变化,信号就会在阻抗不连续的结点产生反射(关于为什么在不连续点产生反射的解释详见附录)。

要格外注意的是,这个特征阻抗是对交流(AC)信号而言的,对直流(DC)信号,传输线的电阻并不是特性阻抗值Z0,而是远小于这个值。

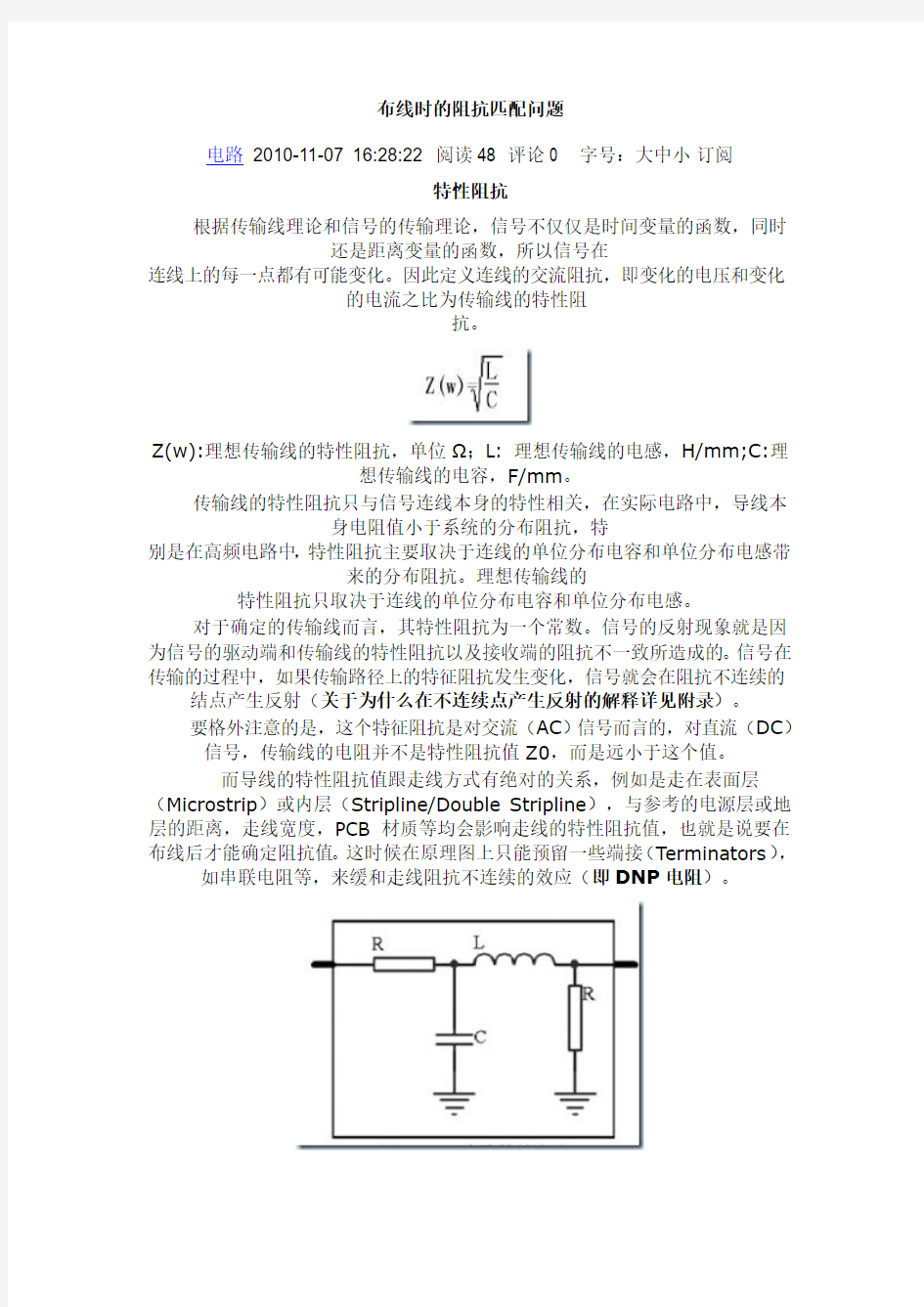

而导线的特性阻抗值跟走线方式有绝对的关系,例如是走在表面层(Microstrip)或内层(Stripline/Double Stripline),与参考的电源层或地层的距离,走线宽度,PCB 材质等均会影响走线的特性阻抗值,也就是说要在布线后才能确定阻抗值。这时候在原理图上只能预留一些端接(Terminators),如串联电阻等,来缓和走线阻抗不连续的效应(即DNP电阻)。

PCB走线等效电路PCB 板上的走线可等效为上图所示的串联和并联的电容、电阻和电感结构。串联电阻的典型值为0.25——0.55ohms/foot,因为绝缘层的缘故,并联电阻阻值通常很高。将寄生电阻、电容和电感加到实际的PCB 连线中之后,连线上的最终阻抗称为特征阻抗Z0 。线径越宽,距电源/地越近,或隔离层的介电常数越高,特征阻抗就越小。如果传输线和接收端的阻抗不匹配,那么输出的电流信号和信号最终的稳定状态将不同,这就引起信号在接收端产生反射,这个反射信号将传回信号发射端并再次反射回来。随着能量的减弱反射信号的幅度将减小,直到信号的电压和电流达到稳定。这种效应被称为振荡,信号的振荡在信

号的上升沿和下降沿经常可以看到。

阻抗不匹配对电路设计带来以下效应:

1.反射信号(Reflected Signals);

2.延时和时序错误(Delay &Timing Errors);

3.多次跨越逻辑电平门限错误(False Switching);

4.过冲与下冲(Overshoot and Undershoot);

5.串扰(Induced Noise);

6.地弹(Ground Noise);

7.电磁辐射(EMI Radiation)。

因此印制电路板上导线的特性阻抗是电路板设计的一个重要指标,特别是在高频电路的PCB 设计中,必须考虑导线的特性阻抗和器件或信号所要求的特性

阻抗是否一致,是否匹配。

阻抗匹配

阻抗匹配(Impedance Matching),在线路板中,若有信号传递时,希望有电源的发出端起,在能量损失最小的情形下,能顺利的传送到接受端,而且接受端将其完全吸收而不作任何反射。要达到这种传输,线路中的阻抗必须和发出端内部的阻抗相等才行称为“阻抗匹配”。

阻抗匹配是指信号源或者传输线跟负载之间的一种合适的搭配方式。阻抗匹配则传输功率大,对于一个电源来讲,当它的内阻等于负载时,输出功率最大,此时阻抗匹配。如果是高频的话,就是无反射波,指在能量传输时,要求负载阻抗要和传输线的特征阻抗相等,此时的传输不会产生反射,这表明所有能量都被负载吸收了。反之则在传输中有能量损失。阻抗匹配分为低频和高频两种情况讨

论:

在低频电路中,我们一般不考虑传输线的匹配问题,只考虑信号源跟负载之间的情况,因为低频信号的波长相对于传输线来说很长,传输线可以看成是“短线”,反射可以不考虑(可以这么理解:因为线短,即使反射回来,跟原信号还

是一样的)。

在高频电路中,我们还必须考虑反射的问题。当信号的频率很高时,则信号的波长就很短,当波长短得跟传输线长度可以比拟时,反射信号叠加在原信号上将会改变原信号的形状。如果传输线的特征阻抗跟负载阻抗不匹配(相等)时,在负载端就会产生反射(为什么阻抗不匹配时会产生反射以及特征阻抗的求解方法,可参看电磁场与微波方面书籍中的传输线理论)。

如果阻抗不匹配,则会形成反射,能量传递不过去,降低效率;会在传输线上形成驻波(简单的理解,就是有些地方信号强,有些地方信号弱),导致传

输线的有效功率容量降低;功率发射不出去,甚至会损坏发射设备。如果是电路板上的高速信号线与负载阻抗不匹配时,会产生震荡,辐射干扰等。

当阻抗不匹配时,有哪些办法让它匹配呢?第一,可以考虑使用变压器来做阻抗转换;第二,可以考虑使用串联/并联电容或电感的办法,这在调试射频电路时常使用;第三,可以考虑使用串联/并联电阻的办法。一些驱动器的阻抗比较低,可以串联一个合适的电阻来跟传输线匹配,例如高速信号线,有时会串联一个几十欧的电阻。而一些接收器的输入阻抗则比较高,可以使用并联电阻的方法,来跟传输线匹配,例如,485总线接收器,常在数据线终端并联120欧

的匹配电阻。

通常所采用的阻抗匹配端接方式有两种,一种是使负载阻抗与传输线阻抗匹配,即并行端接;另一种是使源阻抗与传输线阻抗匹配,即串行端接。一般应采用并行端接,因其是在信号能量反射回源端之前在负载端消除反射,这样可以减少噪声、电磁干扰以及射频干扰。下面介绍这两种主要的端接技术及其优缺点。

并行端接

并行端接理论出发点是在信号源端阻抗很小的情况下,通过增加并联电阻使负载端输入阻抗与传输线的特征阻抗相匹配,达到消除负载端反射的目的。主要是在尽量靠近负载端的位置加上拉或下拉电阻来实现终端的阻抗匹配,实现形式分为单电阻和双电阻两种形式,简单并行端接和RC并行端接为单电阻形式,

戴维宁端接为双电阻形式。

简单的并行端接

这种方式是简单地在负载端加入一下拉到地的电阻R(R = Z0 )来实现匹配,以消除信号的反射。采用这种端接的条件是驱动端必须能够提供输出高电平时的驱动电流,以保证通过端接电阻的高电平能满足门限电压的要求。在数字电路系统中,返回通路上的电流通常都大于系统中供电电源提供的电流,终端匹配到地可以提高电流的吸收能力。如下图所示:其中term4为源端,term3为负载端。

简单的并行端接的优点是设计和应用简单易行,只需要增加一个元件,是最简单的并行端接技术。其缺点是匹配电阻RT 会有直流功率消耗,在输出为高电平状态时,对于50Ω 的端接电阻,维持TTL高电平时消耗电流高达48mA,这是因为驱动器的最小高电平输出VOH (min) = 2. 4V,因此一般器件很难可靠的支持这种端接电路。另外这种端接技术也会使信号的逻辑高输出电平下降。将TTL 输出终端匹配到地会降低VOH的电平值,从而降低了负载输入端的噪声容

限。

戴维宁并行端接

戴维宁端接即分压器型端接,采用上拉电阻R6 和下拉电阻R5 来构成端接电阻, R5和R6的并联与Z0 相匹配。R6 的作用是帮助驱动器更加容易到达逻

辑高状态,这就需要通过V_DC向负载注入电流来实现。R5 的作用是帮助驱动器更加容易到达逻辑低状态,这通过R5 向地释放电流来实现。电阻R5、R6的

选择满足下列条件:

1、两电阻的并联值与传输线的特征阻抗相等;

2、与电源连接的电阻值不能太小,以免信号为低电平时驱动电流过大;

3、与地连接的电阻值不能太小,以免信号为高电平时驱动电流过大。

戴维宁并行端接如下图所示:

戴维宁端接的优点是提高了系统的噪声容限,降低了对源端器件驱动能力的要求,能很好的解决过冲问题。缺点在于匹配电阻R5 和R6上一直有一个常量的直流电流存在,因此直流功耗比较大。

RC并行端接

RC并行端接使用电阻和电容网络作为端接阻抗。电阻R的值要与传输线的特征阻抗相匹配,而电容值的选择比较复杂,电容值太小会导致RC时间常数过小,这样RC电路就类似于一个尖锐的信号沿发生器,从而导致信号的过冲与下冲;

另一方面,较大的电容会带来更大的功率消耗。

这种端接方式的优点是电容有阻低频、通高频的作用,因此电阻RT 驱动器的直流负载,没有直流损耗。恰当地选取电容值可确保负载端波形接近理想方波,而信号的过冲和下冲又都很小。缺点在于电容的状态与前一时间信号的数据类型有关,所以数据会出现时间上的抖动。由于这种方式的效果与传输线的长度有关,当传输线上分布多个驱动器时会降低匹配的效果。另外这种方式不能用于电流模

式的驱动器。

串行端接

理论出发点是在信号源端阻抗低于传输线特征阻抗的条件下,在信号的源端和传输线之间串接一个电阻R,使源端的输出阻抗与传输线的特征阻抗相匹配,抑制从负载端反射回来的信号发生再次反射。

不同于以上介绍的并行端接技术,串行端接是信号源端的端接技术,它是在

驱动器和源端之间加入一个电阻R1。驱动器的输出阻抗ZS 与电阻R1的串联必须与传输线的特征阻抗Z0 相匹配,即R1= Z0 – ZS 。这种方式通过使源端的反射系数为零来抑制从负载反射回来的信号,消除了信号的二次反射,所以只有在两倍于信号在传输线上的传输延时后,才能在驱动端看到变化后完整的信号

幅度。如下图所示:

串行端接的优点在于每个驱动器只需要一个端接电阻,无须与电源相连,消耗功率小。而且不会给驱动器增加额外的直流负载,也不会在信号线与地之间引入额外的阻抗。缺点是很难将匹配电阻R1调整到一个非常合适的值,因为许多驱动器都是非线性的,输出阻抗会有所变化,所以R1只能选择一个适中的值。另外由于在信号通路上增加了电阻,增加了RC时间常数,从而减缓了负载端信号的上升时间,因而不适合于高频信号通路。

综上所述:

并联终端匹配后的信号传输具有以下特点:

A 驱动信号近似以满幅度沿传输线传播;

B 所有的反射都被匹配电阻吸收;

C 负载端接受到的信号幅度与源端发送的信号幅度近似相同。

串联终端匹配后的信号传输具有以下特点:

A 由于串联匹配电阻的作用,驱动信号传播时以其幅度的50%向负载端传播;

B 信号在负载端的反射系数接近+1,因此反射信号的幅度接近原始信号幅度的

50%。

C 反射信号与源端传播的信号叠加,使负载端接受到的信号与原始信号的幅度

近似相同;

D 负载端反射信号向源端传播,到达源端后被匹配电阻吸收;

E 反射信号到达源端后,源端驱动电流降为0,直到下一次信号传输。

相对并联匹配来说,串联匹配不要求信号驱动器具有很大的电流驱动能力。

并联终端匹配优点是简单易行;显而易见的缺点是会带来直流功耗:单电阻方式的直流功耗与信号的占空比紧密相关;双电阻方式则无论信号是高电平还是低电平都有直流功耗。因而不适用于电池供电系统等对功耗要求高的系统。另外,单电阻方式由于驱动能力问题在一般的TTL、CMOS系统中没有应用,而双电阻方式需要两个元件,这就对PCB的板面积提出了要求,因此不适合用于

高密度印刷电路板。

串联匹配是最常用的终端匹配方法。它的优点是功耗小,不会给驱动器带来额外的直流负载,也不会在信号和地之间引入额外的阻抗;而且只需要一个电

阻元件。

附录:

特性阻抗不连续时产生反射的解释:

信号在传输线传播时,其路径上的每一步都有相应的瞬态阻抗。如果互连线的阻抗是可控的,那么瞬态阻抗就等于线的特性阻抗。无论什么原因使瞬态阻抗发生了改变,部分信号都将沿着与原传播方向相反的方向反射,而另一部分将继续传播,但幅度有所变化。反射的量由瞬态阻抗的突变量决定,

如图1所示。

如果第一个区域的瞬态阻抗是Z1 ,第二个区域的是Z2 ,则反射信号与入射信号

的幅值之比为:

其中, Vreflected:反射电压; Vincident:入射电压;Z2:信号进入区域2 时的瞬态阻抗; Z1:信号最初所在区域的瞬态阻抗; ρ:反射系数。

两个区域的阻抗差异越大,反射信号量越大。

产生反射信号是为了协调两个重要的边界条件。信号到达瞬态阻抗不同的两个区域(区域1和2)的交界面时,在信号和返回回路的导体中仅存在一个电压和电流回路,而在交界面两侧的电压和电流都是相同的。边界面处不可能出现电压不连续,否则此处会有一个无限大的电场;也不可能出现电流不连续,否则会有一个无限大的磁场。当交界面两侧阻抗不一致

时,V1=V2,I1=I2,I1=V1/Z1,I2=V2/Z2不可能同时成立。

为了使整个系统协调稳定,区域1产生了一个反射回源端的电压。反射的唯一目的就是吸收入射信号和传输信号之间不匹配的电压和电流。如此,交界面两侧的电压和电流才可以相等,交界面处的电压和电流才是连续的,整个系统才是平衡的。只要在信号传输路径上出现瞬态阻抗改变,信号就会发生反射。

目錄 第一章傳輸線理論 一傳輸線原理 二微帶傳輸線 三微帶傳輸線之不連續分析第二章被動元件之電感設計與分析一電感原理 二電感結構與分析 三電感設計與模擬 四電感分析與量測

第一章 傳輸線理論 傳輸線理論與傳統電路學之最大不同,主要在於元件之尺寸與傳導電波之波長的比值。當元件尺寸遠小於傳輸線之電波波長時,傳統的電路學理論才可以使用,一般以傳輸波長(Guide wavelength )的二十分之ㄧ(λ/20)為最大尺寸,稱為集總元件(Lumped elements );反之,若元件的尺寸接近傳輸波長,由於元件上不同位置之電壓或電流的大小與相位均可能不相同,因而稱為散佈式元件(Distributed elements )。 由於通訊應用的頻率越來越高,相對的傳輸波長也越來越小,要使電路之設計完全由集總元件所構成變得越來越難以實現,因此,運用散佈式元件設計電路也成為無法避免的選擇。 當然,科技的進步已經使得集總元件的製作變得越來越小,例如運用半導體製程、高介電材質之低溫共燒陶瓷(LTCC )、微機電(MicroElectroMechanical Systems, MEMS )等技術製作集總元件,然而,其中電路之分析與設計能不乏運用到散佈式傳輸線的理論,如微帶線(Microstrip Lines )、夾心帶線(Strip Lines )等的理論。 因此,本章以討論散佈式傳輸線的理論開始,進而以微帶傳輸線為例介紹其理論與公式,並討論微帶傳輸線之各種不連續之電路,以作為後續章節之被動元 1.1(a)。其中的集總元件電路模型描述,其中 (a) (b) i (z, t ) v z, t ) z

微波技术与天线实验报

(1)负载开路,负载短路,与负载匹配 负载开路与短路即为令终端负载L Z 为∞或0,而对于功率输出,当负载匹配时会得到最大的功率输出;对于电源电压输出,指电源内阻越小在内阻上的压降越小,会得到最大的电压输出,就是说电源的效率最大,当内阻r=0,电源的效率等于1(100%)。 (1)传输线的工作状态 传输线的工作状态取决于传输线终端所接的负载,有三种状态。其中负载开路与短路即为令终端负载L Z 为∞或0导致传输线工作于驻波状态,Z L =Z 0时传输线工作于行波状态。 行波状态:传输线上无反射波出现,只有入射波的工作状态。 当传输线终端负载阻抗等于传输线的特性阻抗,即Z L =Z 0时,线上只有入射波(反射系数为零)。此时 z z e U e Z I U z U '' =+= 'γγ20222 )( z z e I e Z Z I U z I ' +'=+= 'γγ20 0222)( 对于无损耗线=γj β,则

本实验用微带传输线模块模拟测量线。利用驻波测量技术测量传输线上的波,可以粗略地观察波腹、波节和波长,进而测量反射系数|Γ|和驻波比ρ。若条件允许可以使用反射测量电桥以较精确地测量反射损耗。 (1)实验仪器 RZ9908综合实验箱频率合成信号发生器电场探头频谱分析仪反射测量电桥终端负载(2)实验思路 用驻波分布法测量微带传输线上电磁波的波长。观测微带传输线上驻波分布,测量驻波的波腹、波节、反射系数和驻波比。 (3)实验过程 实验装置大致如下,应用实验箱固定模块可简化操作。 原理如下: 实验连接图如下:

微带传输线模块测量端开路(不接负载)。 把频率合成信号发生器设置成为:CENTER FREQUENCY=1000MHz,SPAN=1MHz,参考电平-30dBm,在保证信号不超出屏幕顶端的情况下,参考电平越小越好,尽量使信号谱线的峰值显示在屏幕的第一格和第二格之间。 频率合成信号发生器设置为输出频率1000MHz和最小衰减量。 如图1连接,逐次移动探头。记录探头位置刻度读数和频谱分析仪读数,必要时可调节信号发生器的输出功率或频谱分析仪的参考电平。 改变频率合成信号发生器的输出频率为800MHz,再重复进行驻波分布测试。 用反射测量电桥来测量驻波损耗,按图2连接好实验装置

功率放大器设计的关键:输出匹配电路的性能 2008-05-15 17:51:20 作者:未知来源:电子设计技术 关键字:功率放大器匹配电路匹配网络s参数串联电阻输出功率Cout耗散功率网络分析仪高Q值对于任何功率放大器(功率放大器)设计,输出匹配电路的性能都是个关键。但是,在设计过程中,有一个问题常常为人们所忽视,那就是输出匹配电路的功率损耗。这些功率损耗出现在匹配网络的电容器、电感器,以及其他耗能元件中。功率损耗会降低功率放大器的工作效率及功率输出能力。 因为输出匹配电路并不是一个50Ω的元件,所以耗散损失与传感器增益有很大的区别。输出匹配的具体电路不同,损耗也不一样。对于设计者而言,即使他没有选择不同技术的余地,在带宽和耗散损失之间,在设计方面仍然可以做很多折衷。 匹配网络是用来实现阻抗变化的,就像是功率从一个系统或子系统传送另一个系统或者子系统,RF设计者们在这上面下了很大的功夫。对于功率放大器,阻抗控制着传送到输出端的功率大小,它的增益,还有它产生的噪声。因此,功率放大器匹配网络的设计是性能达到最优的关键。 损耗有不同的定义,但是这里我们关心的是在匹配网络中,RF功率以热量的形式耗散掉的损耗。这些损耗掉的功率是没有任何用途。依据匹配电路功能的不同,损耗的可接受范围也不同。对功率放大器来讲,输出匹配损耗一直是人们关注的问题,因为这牵涉到很大的功率。效率低不仅会缩短通话时间,而且还会在散热和可靠性方面带来很大的问题。 例如,一个GSM功率放大器工作在3.5V电压时,效率是55%,能够输出34dBm的功率。在输出功率为最大时,功率放大器的电流为1.3A。匹配的损耗在0.5dB到1dB的数量级,这与输出匹配的具体电路有关。在没有耗散损失时,功率放大器的效率为62%到69%。尽管损耗是无法完全避免的,但是这个例子告诉我们,在功率放大器匹配网络中,损耗是首要问题。 耗散损失 现在我们来看一个网络,研究一个匹配网络(图1a)中的耗散损失。电源通过无源匹配网络向无源负载传输功率。在电源和负载阻抗之间没有任何其他的限制。把匹配网络和负载合在一起考虑,电源输出一个固定量的功率Pdel 到这个网络(图1b)。输出功率的一部分以热量的形式耗散在匹配网络中。而其余的则传输到负载。Pdel是传输到匹配网络和负载(图1c)上的总功率,PL是传输到负载的那部分功率。 了解了这两个量,我们就可以知道,实际上到底有多大的一部分功率是作为有用功率从电源传输到了负载,其比例等于PL/Pdel。 这是对功率放大器输出匹配的耗散损失的正确测量,因为它只考虑了实际传输功率以及耗散功率。反射功率没有计算进去。 由此可知,这个比例就等于匹配网络工作时的功率增益GP。而工作时的功率增益完整表达式为: 这里,是负载反射系数,是匹配网络的s参数, 损失就是增益的倒数。因此,耗散损失可以定义为: Ldiss = 1/GP。 对于功率放大器而言,我们为它设计的负载一般是50Ω。通常,我们用来测量s参数的系统阻抗也是50Ω。如果系统阻抗和负载都是50Ω,那么就为0,于是,上面的表达式就可以简化为: 在计算一个匹配网络的耗散损失时,只需要知道它的传输值和反射散射参数的大小,这些可以很容易地从s参数的计算过程中得到,因为网络分析仪通常都会采用线性的方式来显示s参数的值。在评估输入和级间耗散损失时,负载的阻抗不是50Ω,但是上述的规律依然适用。 因为反射和耗散损失很容易混淆,射频工程师有时就会采用错误的方法来计算耗散损失。而最糟糕的方法就是采用未经处理的s21来进行计算。一个典型的匹配网络在1GHz(图2)时,对功率放大器而言,是数值为4+j0Ω的负载阻抗。匹配网络采用的是无损耗元件来进行模拟的,所以在匹配网络中不存在功率的耗散问题。然而,s21却是-6dB,因为在50Ω的源阻抗和4Ω的负载之间存在着巨大的不匹配问题。作为一个无损耗网络,除了一些数字噪音外,模拟的耗散损失为0dB。 在电路的模拟当中,我们可能可以采用s21来求出正确的耗散损失。这一过程包括采用复杂模拟负载线的共轭

电子系统综合设计实验报告

正弦波产生电路设计报告 一、实验设计目的和作用 1. 进行基本技能训练,如基本仪器仪表的使用,常用元器件的 识别、测量、熟练运用的能力,掌握设计资料、手册、标准 和规范以及使用仿真软件、实验设备进行调试和数据处理 等。 2. 学习较复杂的电子系统设计的一般方法,提高基于模拟、数 字电路等知识解决电子信息方面常见实际问题的能力,由学 生自行设计、自行制作和自行调试。 3. 培养理论联系实际的正确设计思想,训练综合运用已学过的 理论和生产实际知识去分析和解决工程实际问题的能力。 4.通过学员的独立思考和解决实际问题的过程,培养学员的创 新能力 二、设计的具体实现 实验要求用TL084设计正弦波产生电路。正弦波产生方式有多种,本次试验采用较为简单的文氏桥振荡电路。通过图书馆和上网查阅有关资料,确定如下电路。 Multisim原理图:

sch图 调节w1使电路起振,w2调节幅度 仿真结果:频率162Hz,幅度范围0.8—10V

三、实际制作调试和结果分析

频率:133.33Hz 幅度范围:1~9V 四、总结 第一次进行电路设计,遇到了很多麻烦。Multisim、Protel等软件不熟悉,第一次焊电路焊工也不行。通过实验,基本学会了这些软件的操作,制作过程中,自己的焊工有了很大进步。虽然做了好几次才把电路调出来,但还是很满意。 五、参考文献 1.于红珍.通信电子电路【M】.北京:清华大学出版社,2005 2.康华光,陈大钦.电子技术基础模拟部分(第四版). 北京:高等教育出版社,1999.6 3.黄智伟.全国大学生电子设计竞赛【M】.北京:北京航空航天大学出版社,2006

关于阻抗匹配的理解 阻抗匹配是指信号源或者传输线跟负载之间的一种合适的搭配方式。阻抗匹配分为低频和高频两种情况讨论。 我们先从直流电压源驱动一个负载入手。实际的电压源总是有内阻的,我们可以把一个实际电压源,等效成一个理想的电压源跟一个电阻r串联的模型。假设负载电阻为R,电源电动势为U,内阻为r,那么我们可以计算出流过电阻R的电流为:I=U/(R+r),可以看出,负载电阻R越小,则输出电流越大。负载R上的电压为:Uo=IR=U*[1+(r/R)],可以看出,负载电阻R越大,则输出电压Uo越高。再来计算一下电阻R消耗的功率为: P="I"*I*R=[U/(R+r)]*[U/(R+r)]*R=U*U*R/(R*R+2*R*r+r*r) =U*U*R/[(R-r)*(R-r)+4*R*r] =U*U/{[(R-r)*(R-r)/R]+4*r} 对于一个给定的信号源,其内阻r是固定的,而负载电阻R则是由我们来选择的。注意式中[(R-r)*(R-r)/R],当R=r时,[(R-r)*(R-r)/R]可取得最小值0,这时负载电阻R上可获得最大输出功率Pmax=U*U/(4*r)。即,当负载电阻跟信号源内阻相等时,负载可获得最大输出功率,这就是我们常说的阻抗匹配之一。对于纯电阻电路,此结论同样适用于低频电路及高频电路。当交流电路中含有容性或感性阻抗时,结论有所改变,就是需要信号源与负载阻抗的的实部相等,虚部互为相反数,这叫做共轭匹配。在低频电路中,我们一般不考虑传输线的匹配问题,只考虑信

号源跟负载之间匹配的情况,因为低频信号的波长相对于传输线来说很长,传输线可以看成是“短线”,反射可以不考虑(可以这么理解:因为线短,即使反射回来,跟原信号还是一样的)。从以上分析我们可以得出结论:如果我们需要输出电流大,则选择小的负载R;如果我们需要输出电压大,则选择大的负载R,如果我们需要输出功率最大,则选择跟信号源内阻匹配的电阻R。有时阻抗不匹配还有另外一层意思,例如一些仪器输出端是在特定的负载条件下设计的,如果负载条件改变了,则可能达不到原来的性能,这时我们也会叫做阻抗失配。 在高频电路中,我们还必须考虑反射的问题。当信号的频率很高时,则信号的波长就很短,当波长短得跟传输线长度可以比拟时,反射信号叠加在原信号上将会改变原信号的形状。如果传输线的特征阻抗跟负载阻抗不匹配(相等),在负载端就会产生反射。为什么阻抗不匹配时会产生反射以及特征阻抗的求解方法,牵涉到二阶偏微分方程的求解,在这里我们不细说了,有兴趣的朋友可参看电磁场与微波方面书籍中的传输线理论。传输线的特征阻抗(也叫做特性阻抗)是由传输线的结构以及材料决定的,而与传输线的长度,以及信号的幅度、频率等均无关。例如,常用的闭路电视同轴电缆特性阻抗为75欧,而一些射频设备上则常用特征阻抗为50欧的同轴电缆。另外还有一种常见的传输线是特性阻抗为300欧的扁平平行线,这在农村使用的电视天线架上比较常见,用来做八木天线的馈线。因为电视机的射频输入端输入阻抗为75欧,所以300欧的馈线将与其不能匹配。实际中是如何解决这个问题的呢?不知道大家有没有留意到,电视机的附件中,有一个300欧到75

阻抗匹配和阻抗变换是什么?阻抗变换和阻抗匹配的详细概述阻抗匹配是无线电技术中常见的一种工作状态,它反映了输入电路与输出电路之间的功率传输关系。当电路实现阻抗匹配时,将获得最大的功率传输。反之,当电路阻抗失配时,不但得不到最大的功率传输,还可能对电路产生损害。阻抗匹配常见于各级放大电路之间、放大器与负载之间、测量仪器与被测电路之间、天线与接收机或发信机与天线之间,等等。例如,扩音机的输出电路与扬声器之间必须做到阻抗匹配,不匹配时,扩音机的输出功率将不能全部送至扬声器。如果扬声器的阻抗远小于扩音机的输出阻抗,扩音机就处于过载状态,其末级功率放大管很容易损坏。反之,如果扬声器的阻抗高于扩音机的输出阻抗过多,会引起输出电压升高,同样不利于扩,音机的工作,声音还会产生失真.因此扩音机电路的输出阻抗与扬声器的阻抗越接近越好。又例如,无线电发信机的输出阻抗与馈线的阻抗、馈线与天线的阻抗也应达到一致。如果阻抗值不一致,发信机输出的高频能量将不能全部由天线发射出去。这部分没有发射出去的能量会反射回来,产生驻波,严重时会引起馈线的绝缘层及发信机末级功放管的损坏。为了使信号和能量有效地传输,必须使电路工作在阻抗匹配状态,即信号源或功率源的内阻等于电路的输人阻抗,电路的输出阻抗等于负载的阻抗。在一般的输入、输出电路中常含有电阻、电容和电感元件,由它们所组成的电路称为电抗电路,其中只含有电阻的电路称为纯电阻电路. 下面对纯电阻电路和电抗电路的阻抗匹配问题分别进行简要的分。1、纯电阻电路在中学物理电学中曾讲述这样一个问题:把一个电阻为R的用电器,接在一个电动势为E、内阻为r的电池组上(见图1),在什么条件下电源输出的功率最大呢?当外电阻等于内电阻时,电源对外电路输出的功率最大,这就是纯电阻电路的功率匹配。假如换成交流电路,同样也必须满足R=r这个条件电路才能匹配。 2、电抗电路电抗电路要比纯电阻电路复杂,电路中除了电阻外还有电容和电感.元件,并工作于低频或高频交流电路。在交流电路中,电阻、电容和电感对交流电的阻碍作用叫阻抗,用字母Z表示.其中,电容和电感对交流电的阻碍作用,分别称为容抗及和感抗而.容

传输线阻抗匹配方法 匹配阻抗的端接有多种方式,包括并联终端匹配、串联终端匹配、戴维南终端匹配、AC终端匹配、肖特基二极管终端匹配。 1.并联终端匹配 并联终端匹配是最简单的终端匹配技术,通过一个电阻R将传输线的末端接到地或者接到V CC上。电阻R的值必须同传输线的特征阻抗Z0匹配,以消除信号的反射。终端匹配到V CC可以提高驱动器的源的驱动能力,而终端匹配到地则可以提高电流的吸收能力。 并联终端匹配技术突出的优点就是这种类型终端匹配技术的设计和应用简便易行,在这种终端匹配技术中仅需要一个额外的元器件;这种技术的缺点在于终端匹配电阻会带来直流功率消耗。另外并联终端匹配技术也会使信号的逻辑高输出电平的情况退化。将TTL输出终端匹配到地会降低V OH的电平值,从而降低了接收器输入端对噪声的免疫能力。 对长走线进行并联终端匹配后仿真,波形如下: 2.串联终端匹配 串联终端匹配技术是在驱动器输出端和信号线之间串联一个电阻,是一种源

端的终端匹配技术。驱动器输出阻抗R0以及电阻R值的和必须同信号线的特征阻抗Z0匹配。对于这种类型的终端匹配技术,由于信号会在传输线、串联匹配电阻以及驱动器的阻抗之间实现信号电压的分配,因而加在信号线上的电压实际只有一半的信号电压。 而在接收端,由于信号线阻抗和接收器阻抗的不匹配,通常情况下,接收器的输入阻抗更高,因而会导致大约同样幅度值信号的反射,称之为附加的信号波形。因而接收器会马上看到全部的信号电压(附加信号和反射信号之和),而附加的信号电压会向驱动端传递。然而不会出现进一步的信号反射,这是因为串联的匹配电阻在接收器端实现了反射信号的终端匹配。 串联终端匹配技术的优点是这种匹配技术仅仅为系统中的每一个驱动器增加一个电阻元件,而且相对于其它的电阻类型终端匹配技术来说,串联终端匹配技术中匹配电阻的功耗是最小的,而且串联终端匹配技术不会给驱动器增加任何额外的直流负载,也不会在信号线与地之间引入额外的阻抗。 由于许多的驱动器都是非线性的驱动器,驱动器的输出阻抗随着器件逻辑状态的变化而变化,从而导致串联匹配电阻的合理选择更加复杂。所以,很难应用某一个简单的设计公式为串联匹配电阻来选择一个最合适的值。 对长走线进行串联终端匹配后仿真,波形如下: 3.戴维南终端匹配

传输线的特性阻抗分析 传输线的基本特性是特性阻抗和信号的传输延迟,在这里,我们主要讨论特性阻抗。传输线是一个分布参数系统,它的每一段都具有分布电容、电感和电阻。传输线的分布参数通常用单位长度的电感L和单位长度的电容C以及单位长度上的电阻、电导来表示,它们主要由传输线的几何结构和绝缘介质的特性所决定的。分布的电容、电感和电阻是传输线本身固有的参数,给定某一种传输线,这些参数的值也就确定了,这些参数反映着传输线的内在因素,它们的存在决定着传输线的一系列重要特性。 一个传输线的微分线段l可以用等效电路描述如下: 传输线的等效电路是由无数个微分线段的等效电路串联而成,如下图所示: 从传输线的等效电路可知,每一小段线的阻抗都是相等的。传输线的特性阻抗就是微分线段的特性阻抗。

传输线可等效为:

Z0 就是传输线的特性阻抗。 Z0描述了传输线的特性阻抗,但这是在无损耗条件下描述的,电阻上热损耗和介质损耗都被忽略了的,也就是直流电压变化和漏电引起的电压波形畸变都未考虑在内。实际应用中,必须具体分析。 传输线分类 当今的快速切换速度或高速时钟速率的PCB 迹线必须被视为传输线。传输线可分为单端(非平衡式)传输线和差分(平衡式)传输线,而单端应用较多。 单端传输线路 下图为典型的单端(通常称为非平衡式)传输线电路。 单端传输线是连接两个设备的最为常见的方法。在上图中,一条导线连接了一个设备的源和另一个设备的负载,参考(接地)层提供了信号回路。信号跃变时,电流回路中的电流也是变化的,它将产生地线回路的电压降,构成地线回路噪声,这也成为系统中其他单端传输线接收器的噪声源,从而降低系统噪声容限。 这是一个非平衡线路的示例,信号线路和返回线路在几何尺寸上不同 高频情况下单端传输线的特性阻抗(也就是通常所说的单端阻抗)为: 其中:L为单位长度传输线的固有电感,C为单位长度传输线的固有电容。 单端传输线特性阻抗与传输线尺寸、介质层厚度、介电常数的关系如下: ?? 与迹线到参考平面的距离(介质层厚度)成正比 ?? 与迹线的线宽成反比

摘要 射频设计的主要工作之一,就是使电路的某一部分与另一部分相匹配,在这两部分之间实现最大功率传输,这就需要在射频电路中加入阻抗变换器从而达到阻抗匹配的目的。本文介绍了一种中心频率为400MHz、频宽为40MHz的50~75欧姆T型阻抗变换器的设计与仿真过程。文中概述了射频阻抗变换器的种类、用途及发展。在分析了阻抗匹配理论基本知识的基础上,论述了射频阻抗变换器的设计过程,然后通过ADS软件进行设计和仿真,并对仿真结果进行了分析总结。 关键词:射频;阻抗匹配;阻抗圆图;VSWR(电压驻波比);ADS 目录 摘要 (1) ABSTRACT................................................ 错误!未定义书签。第一章引言 (2) 1.1 概述 (2) 1.2 射频阻抗变换电路的类型 (2) 1.3 射频阻抗变换器的用途 (2) 1.4射频阻抗变换器设计的发展 (3) 第二章基本原理 (3) 2.1 阻抗匹配 (3) 2.2 史密斯圆图 (4) 2.2.1 等反射圆 (4) 2.2.2 等电阻圆图和等电抗圆图 (5) 2.2.3 Smith圆图(阻抗圆图) (7) 2.3 电压驻波比 (8) 第三章 T型阻抗变换器的设计 (9) 3.1 T型阻抗变换器(R S 怎样理解阻抗匹配 阻抗匹配是指信号源或者传输线跟负载之间的一种合适的搭配方式。阻抗匹配分为低频和高频两种情况讨论。 我们先从直流电压源驱动一个负载入手。由于实际的电压源,总是有内阻的(请参看输出阻抗一问),我们可以把一个实际电压源,等效成一个理想的电压源跟一个电阻r串联的模型。假设负载电阻为R,电源电动势为U,内阻为r,那么我们可以计算出流过电阻R的电流为:I=U/(R+r),可以看出,负载电阻R越小,则输出电流越大。负载R上的电压为:Uo=IR=U/[1+(r/R)],可以看出,负载电阻R 越大,则输出电压Uo越高。再来计算一下电阻R消耗的功率为:P=I2×R=[U/(R+r)]2×R=U2×R/(R2+2×R×r+r2) =U2×R/[(R-r)2+4×R×r] =U2/{[(R-r)2/R]+4×r} 对于一个给定的信号源,其内阻r是固定的,而负载电阻R则是由我们来选择的。注意式中[(R-r)2/R],当R=r时,[(R-r)2/R]可取得最小值0,这时负载电阻R上可获得最大输出功率Pmax=U2/(4×r)。即,当负载电阻跟信号源内阻相等时,负载可获得最大输出功率,这就是我们常说的阻抗匹配之一。对于纯电阻电路,此结论同样适用于低频电路及高频电路。当交流电路中含有容性或感性阻抗时,结论有所改变,就是需要信号源与负载阻抗的的实部相等,虚部互为相反数,这叫做共扼匹配。在低频电路中,我们一般不考虑传输线的 匹配问题,只考虑信号源跟负载之间的情况,因为低频信号的波长相对于传输线来说很长,传输线可以看成是"短线",反射可以不考虑(可以这么理解:因为线短,即使反射回来,跟原信号还是一样的)。从以上分析我们可以得出结论:如果我们需要输出电流大,则选择小的负载R;如果我们需要输出电压大,则选择大的负载R;如果我们需要输出功率最大,则选择跟信号源内阻匹配的电阻R。有时阻抗不匹配还有另外一层意思,例如一些仪器输出端是在特定的负载条件下设计的,如果负载条件改变了,则可能达不到原来的性能,这时我们也会叫做阻抗失配。 在高频电路中,我们还必须考虑反射的问题。当信号的频率很高时,则信号的波长就很短,当波长短得跟传输线长度可以比拟时,反射信号叠加在原信号上将会改变原信号的形状。如果传输线的特征阻抗跟负载阻抗不相等(即不匹配)时,在负载端就会产生反射。为什么阻抗不匹配时会产生反射以及特征阻抗的求解方法,牵涉到二阶偏微分方程的求解,在这里我们不细说了,有兴趣的可参看电磁场与微波方面书籍中的传输线理论。传输线的特征阻抗(也叫做特性阻抗)是由传输线的结构以及材料决定的,而与传输线的长度,以及信号的幅度、频率等均无关。 例如,常用的闭路电视同轴电缆特性阻抗为75Ω,而一些射频设备上则常用特征阻抗为50Ω的同轴电缆。另外还有一种常见的传输线是特性阻抗为300Ω的扁平平行线,这在农村使用的电视天线架上 ADS软件学习及阻抗匹配电路的仿真设计 专业班级:电子信息科学与技术3班 姓名: 学号: 一、实验内容 用分立LC设计一个L型阻抗匹配网络,实现负载阻抗(30+j*40)(欧姆) 到50(欧姆)的匹配,频率为1GHz。 二、设计原理 阻抗匹配是指负载阻抗与激励源内部阻抗互相适配,得到最大功率输出的一种工作状态,它反映了输入电路与输出电路之间的功率传输关系。 要实现最大的功率传输,必须使负载阻抗与源阻抗匹配,这不仅仅是为了减小功率损耗,还具有其他功能,如减小噪声干扰、提高功率容量和提高频率响应的线性度等。通常认为,匹配网络的用途就是实现阻抗变换,就是将给定的阻抗值变换成其他更合适的阻抗值。 基本阻抗匹配理论: ——(1) ——(2),由(1)与(2)可得:——(3) 当RL=Rs时可获得最大输出功率,此时为阻抗匹配状态。无论负载电阻大于还是小于信号源内阻,都不可能使负载获得最大功率,且两个电阻值偏差越大,输出功率越小。 广义阻抗匹配: 阻抗匹配概念可以推广到交流电路,当负载阻抗ZL与信号源阻抗Zs共轭时,即ZL=Zs,能够实现功率的最大传输,称作共轭匹配或广义阻抗匹配。 如果负载阻抗不满足共轭匹配条件,就要在负载和信号源之间加一个阻抗变换网络N,将负载阻抗变换为信号源阻抗的共轭,实现阻抗匹配。 三设计过程 1、新建ADS工程,新建原理图。在元件面板列表中选择“Simulation S--param”,在原理图中放两个Term和一个S-Parameters控件,分别把Term1设置成Z=5Oohm,Term2 设置成Z=30+j*40ohm,双击S-Parameters控件,弹出设置对话框,分别把Start设置成10MHz,Stop设置成2GHz,Step-size设置成1MHz。 2、在原理图里加入Smith Chart Matching 控件,并设置相关的频率和输入输出阻抗等参数。 3、连接电路。 4、在原理图设计窗口,执行菜单命令tools->Smith Chart,弹出Smart Component,选择“Update SmartComponent from Smith Chart Utility”,单击“OK”。 5、设置Freq=0.05GHz,Z0=50ohm。单击DefineSource /load Network terminations 按钮,弹出“Network Terminations”对话框,设置源和负载阻抗,然后依次单击“Apply”和“OK”。 6、采用LC分立器件匹配。 7、单击“Build ADS Circuit”按钮,即可以生成相应的电路。 8、进行仿真,要求其显示S(1,1)和S(2,1)单位为dB的曲线。 变压器和其阻抗 理想变压器是一个端口的电压与另一个端口的电压成正比,且没有功率损耗的一种互易无源二端口网络。它是根据铁心变压器的电气特性抽象出来的一种理想电路元件。 理想变压器阻抗变换作用的性质由以上的全部叙述可见,理想变压器既能变换电压和电流,也能变换阻抗,因此,人们更确切地称它为变量器。 在电子线路中,常利用理想变压器的阻抗变换作用来实现阻抗匹配,使负载获得最大功率。 1.在电子设备中,往往要求负载能获得最大输出功率。负载若要获得最大功率,必须满足负载电阻与电源电阻相等的条件,称为阻抗匹配。但在一般情况下,负载电阻是一定的,不能随意改变。而利用变压器可以进行阻抗变换,适当选择变压器的匝数比,把它接在电源与负载之间,就可实现阻抗匹配,使负载获得最大的输出功率。 如图,从变压器原绕组两端点看进去的阻抗为 从变压器副绕组两端点看进去的阻抗为 因为 表明:变比为K的变压器,可以把其副绕组的负载阻抗,变换成为对电源来说扩大到K2倍的等效阻抗。 2. 假说变压器初级/次级的匝数比为n:1,根据变压器的特性,次级电压为初级的1/n,电流为初级的n倍。 初级阻抗=初级电压/初级电流 次级阻抗=次级电压/次级电流=(1/n)初级电压/(n初级电流)=[1/(nn)]初级阻抗。或者说初级阻抗=(nn)次级阻抗。 这说明,变压器各线圈的阻抗,与线圈匝数的平方成正比。利用这一特点,可以用变压器不同匝数的线圈来变换阻抗。最简单的,就是电视机天线,用扁馈线时阻抗是300Ω,接电视机的天线输入端是75Ω,必须用一个阻抗变换插座,其中就是一个铁氧体磁芯的2:1的变压器,将300Ω与75Ω进行阻抗匹配。 3. 变压器除了可变压外还可作为一个阻抗变换器件,这在有线广播中经常用到。变压器的初次级的匝数比n=n1/n2=V1/V2,V1、V2分别是初、次级的电压,n1、n2分别为初、次级的绕组匝数。又有V1V1=PZ1、V2V2=PZ2 式中P是变压器的功率,Z1、Z2分别是初次的阻抗, 所以有Z1/Z2=V1V1/V2/V2=n1n1/n2n2 即变压器的初次级阻抗比等于初次级电压比的平方和等于匝数比的平方。 阻抗匹配定义 阻抗匹配是指负载阻抗与激励源内部阻抗互相适配,得到最大功率输出的一种工作状态。对于不同特性的电路,匹配条件是不一样的。 在纯电阻电路中,当负载电阻等于激励源内阻时,则输出功率为最大,这种工作状态称为匹配,否则称为失配。 当激励源内阻抗和负载阻抗含有电抗成份时,为使负载得到最大功率,负载阻抗与内阻必须满足共扼关系,即电阻成份相等,电抗成份只数值相等而符号相反。这种匹配条件称为共扼匹配。 阻抗匹配(Impedance matching)是微波电子学里的一部分,主要用于传输线上,来达至所有高频的微波信号皆能传至负载点的目的,不会有信号反射回来源点,从而提升能源效益。史密夫图表上。电容或电感与负载串联起来,即可增加或减少负载的阻抗值,在图表上的点会沿著代表实数电阻的圆圈走动。如果把电容或电感接地,首先图表上的点会以图中心旋转180度,然后才沿电阻圈走动,再沿中心旋转180度。重覆以上方法直至电阻值变成1,即可直接把阻抗力变为零完成匹配。 大体上,阻抗匹配有两种,一种是透过改变阻抗力(lumped-circuit matching),另一种则是调整传输线的波长(transmission line matching)。 要匹配一组线路,首先把负载点的阻抗值,除以传输线的特性阻抗值来归一化,然后把数值划在史密夫图表上。 1. 改变阻抗力 把电容或电感与负载串联起来,即可增加或减少负载的阻抗值,在图表上的点会沿著代表实数电阻的圆圈走动。如果把电容或电感接地,首先图表上的点会以图中心旋转180度,然后才沿电阻圈走动,再沿中心旋转180度。重覆以上方法直至电阻值变成1,即可直接把阻抗力变为零完成匹配。 2. 调整传输线 由负载点至来源点加长传输线,在图表上的圆点会沿著图中心以逆时针方向走动,直至走到电阻值为1的圆圈上,即可加电容或电感把阻抗力调整为零,完成匹配。 阻抗匹配则传输功率大,对于一个电源来讲,单它的内阻等于负载时,输出功率最大,此时阻抗匹配。最大功率传输定理,如果是高频的话,就是无反射波。对于普通的宽频放大器,输出阻抗50Ω,功率传输电路中需要考虑阻抗匹配,可是如果信号波长远远大于电缆长度,即缆长可以忽略的话,就无须考虑阻抗匹配了。阻抗匹配是指在能量传输时,要求负载阻抗要和传输线的特征阻抗相等,此时的传输不会产生反射,这表明所有能量都被负载吸收了.反之则在传输中有能量损失。高速PCB布线时,为了防止信号的反射,要求是线路的阻抗为50欧姆。这是个大约的数字,一般规定同轴电缆基带50欧姆,频带75欧姆,对绞线则为 100欧姆,只是取个整而已,为了匹配方便。 阻抗从字面上看就与电阻不一样,其中只有一个阻字是相同的,而另一个抗字呢?简单地说,阻抗就是电阻加电抗,所以才叫阻抗;周延一点地说,阻抗就是电阻、电容抗及电感抗在向量上的和。在直流电的世界中,物体对电流阻碍的作用叫做电阻,世界上所有的物质都有电阻,只是电阻值的大小差异而已。电阻小的物质称作良导体,电阻很大的物质称作非导体,而最近在高科技领域中称的超导体,则是一种电阻值几近于零的东西。但是在交流电的领域中则除了电阻会阻碍电流以外,电容及电感也会阻碍电流的流动,这种作用就称之为电抗,意即抵抗电流的作用。电容及电感的电抗分别称作电容抗及电感抗,简称容抗及感抗。它们的计量单位与电阻一样是奥姆,而其值的大小则和交流电的频率有关系,频率愈高则容抗愈小感抗愈大,频率愈低则容抗愈大而感抗愈小。此外电容抗和电感抗还有相位角度的问题,具有向量上的关系式,因此才会说:阻抗是电阻与电抗在向量上的和。 阻抗匹配是指负载阻抗与激励源内部阻抗互相适配,得到最大功率输出的一种工作状态。对于不同特性的电路,匹配条件是不一样的。 在纯电阻电路中,当负载电阻等于激励源内阻时,则输出功率为最大,这种工作状态称为匹配,否则称为失配。 当激励源内阻抗和负载阻抗含有电抗成份时,为使负载得到最大功率,负载阻抗与内阻必须满足共扼关系,即电阻成份相等,电抗成份只数值相等而符号相反。这种匹配条件称为共扼匹配。 第 1 页 一、50ohm特征阻抗 终端电阻的应用场合:时钟,数据,地址线的终端串联,差分数据线终端并联等。 终端电阻示图 B.终端电阻的作用: 1、阻抗匹配,匹配信号源和传输线之间的阻抗,极少反射,避免振荡。 2、减少噪声,降低辐射,防止过冲。在串联应用情况下,串联的终端电阻和信号线的分布电容以及后级电路的输入电容组成RC滤波器,消弱信号边沿的陡峭程度,防止过冲。 C.终端电阻取决于电缆的特性阻抗。 D.如果使用0805封装、1/10W的贴片电阻,但要防止尖峰脉冲的大电流对电阻的影响,加30PF的电容. E.有高频电路经验的人都知道阻抗匹配的重要性。在数字电路中时钟、信号的数据传送速度快时,更需注意配线、电缆上的阻抗匹配。 高频电路、图像电路一般都用同轴电缆进行信号的传送,使用特性阻抗为Zo=150Ω、75Ω的同轴电缆。 同轴电缆的特性阻抗Zo,由电缆的内部导体和外部屏蔽内径D及绝缘体的导电率er 决定: 另外,处理分布常数电路时,用相当于单位长的电感L和静电容量C的比率也能计算,如忽略损耗电阻,则 图1是用于测定同轴电缆RG58A/U、长度5m的输入阻抗ZIN时的电路构成。这里研究随着终端电阻RT的值,传送线路的阻抗如何变化。 图1 同轴传送线路的终端电阻构成 只有当同轴电缆的特性阻抗Zo和终端阻抗RT的值相等时,即ZIN=Zo=RT称为阻抗匹配。 Zo≠RT时随着频率f,ZIN变化。作为一个极端的例子,当RT=0、RT=∞时可理解其性质(阻抗以,λ/4为周期起伏波动)。 图2是RT=50Ω(稍微波动的曲线)、75Ω、dOΩ时的输人阻抗特性。当Zo≠RT时由于随着频率,特性阻抗会变化,所以传送的电缆的频率特上产生弯曲. 传输线阻抗匹配的方法 传输线简介传输线(transmission line)输送电磁能的线状结构的设备。它是电信系统的重要组成部分,用来把载有信息的电磁波,沿着传输线规定的路由自一点输送到另一点。 以横电磁(TEM)模的方式传送电能和(或)电信号的导波结构。传输线的特点是其横向尺寸远小于工作波长。主要结构型式有平行双导线、平行多导线、同轴线、带状线,以及工作于准TEM模的微带线等,它们都可借助简单的双导线模型进行电路分析。各种传输TE模、TM模,或其混合模的波导都可认为是广义的传输线。波导中电磁场沿传播方向的分布规律与传输线上的电压、电流情形相似,可用等效传输线的观点分析。 传输线的特性传输线的均匀性 传输导体横截面的形状、使用的材料、导体间的间隔和导体周围的介质,在线路的全部长度上都保持均匀不变的,称为均匀传输线。否则便叫做不均匀传输线。均匀传输线的一次参数均匀地分布于整个传输线上,其数值不随考察点的位置而变化。 传输线在制造和建筑过程中可能出现的偏差,都规定有必要的允许范围。如果出现的不均匀性偏差不超过这些规定,都可以看作是均匀传输线。 性能参数 通常用衰减系数、相移系数、特性阻抗,或与之相对应的其它参数来描述。其数值仅与传输线的结构、几何尺寸、制造传输线使用的材料、工作波长(或工作频率)有关,见表。 传输线阻抗匹配的方法匹配阻抗的端接有多种方式,包括并联终端匹配、串联终端匹配、戴维南终端匹配、AC终端匹配、肖特基二极管终端匹配。 1、并联终端匹配 并联终端匹配是最简单的终端匹配技术,通过一个电阻R将传输线的末端接到地或者接到VCC上。电阻R的值必须同传输线的特征阻抗Z0匹配,以消除信号的反射。终端匹配到VCC可以提高驱动器的源的驱动能力,而终端匹配到地则可以提高电流的吸收能力。 我来大概概括一下ADC输入阻抗的问题: 1:SAR型ADC这种ADC内阻都很大,一般500K以上。即使阻抗小的ADC,阻抗也是固定的。所以即使只要被测源内阻稳定,只是相当于电阻分压,可以被校正。 2:开关电容型,如TLC2543之类。他要求很低的输入阻抗用于对内部采样电容快速充电。这时最好有低阻源,否则会引起误差。实在不行,可以外部并联一很大的电容,每次被取样后,大电容的电压下降不多。因此并联外部大电容后,开关电容输入可以等效为一个纯阻性阻抗,可以被校正。 3:FLASH.html">FLASH型(直接比较型)。大多高速ADC都是直接比较型,也称闪速型(FLASH),一般都是低阻抗的。要求低阻源。对外表现纯阻性,可以和运放直接连接 4:双积分型大多输入阻抗极高,几乎不用考虑阻抗问题 5:Sigma-Delta型。这是目前精度最高的ADC类型,也是最难伺候的一种ADC。重点讲一下要注意的问题: a.内部缓冲器的使用。SigmaDelta型ADC属于开关电容型输入,必须有低阻源。所以为了简化外部设计,内部大多集成有缓冲器。缓冲器打开,则对外呈现高阻,使用方便。但要注意了,缓冲器实际是个运放。那么必然有上下轨的限制。大多数缓冲器都是下轨50mV,上轨AVCC-1.5V。在这种应用中,共莫输入范围大大的缩小,而且不能到测0V。一定要特别小心!一般用在电桥测量中,因为共模范围都在1/2VCC附近。不必过分担心缓冲器的零票,通过内部校零寄存器 很容易校正的。 b.输入阻抗问题。SigmaDelta型ADC属于开关电容型输入,在低阻源上工作良好。但有时候为了抑制共模或抑制乃奎斯特频率外的信号,需要在输入端加RC滤波器,一般DATASHEET上会给一张最大允许输入阻抗和C和Gain的关系表。这时很奇怪的一个特性是,C越大,则最大输入阻抗必须随之减小!刚开始可能很多人不解,其实只要想一下电容充电特性久很容易明白的。还有一个折衷的办法是,把C取很大,远大于几百万倍的采样电容Cs(一般4~20PF),则输入等效纯电阻,分压误差可以用GainOffset寄存器校正。 c.运放千万不能和SigmaDelta型ADC直连!前面说过,开关电容输入电路电路周期用采样电容从输入端采样,每次和运放并联的时候,会呈现低阻,和运放输出阻抗分压,造成电压下降,负反馈立刻开始校正,但运放压摆率(SlewRate)有限,不能立刻响应。于是造成瞬间电压跌落,取样接近完毕时,相当于高阻,运放输出电压上升,但压摆率使运放来不及校正,结果是过冲。而这时正是最关键的采样结束时刻。 所以,运放和SD型ADC连接,必须通过一个电阻和电容连接(接成低通)。而RC的关系又必须服从5.c里面所述规则。 d.差分输入和双极性的问题。SD型ADC都可以差分输入,都支持双极性输入。但这里的双极性并不是指可以测负压,而是Vi+Vi-两脚之间的电压。假设Vi-接AGND,那么负压测量范围不会超过-0.3V。正确的接法是Vi+Vi-共模都在-0.3~VCC之间差分输入。一个典型的 正弦波产生及阻抗匹配 摘要:本系统主要由两大模块构成:正弦信号发生器和低频放大电路。其中正弦信号发生器采用uA741芯片作为主要芯片,配合RC串并联网络产生5kHz稳定的信号,再经电阻分压,得到幅值为0.25V 的正弦信号,将信号通过低频放大电路后,得到幅值为10V的正弦信号,最后加上阻抗匹配网络,实现50 的输出阻抗,此时输出幅值为5V。 关键字:RC正弦振荡;低频放大;阻抗匹配 一、系统总体方案 正弦信号发生器采用uA741运放作为主要芯片,配合RC 串并联网络产生5kHz 稳定的信号,再经电阻分压,得到幅值为0.25V 的正弦信号,将信号通过低频放大电路后,得到幅值为10V 的正弦信号,最后加上阻抗匹配网络,实现50Ω的 二、方案论证与比较 1.正弦信号发生电路 方案一:采用由RC 电路,三极管和石英晶体组成的正弦波振荡电路,但电路成本较高且较为复杂,所以不选。 方案二:采用由RC 串并联网络和同相比例电路组成的正弦波振荡器,因其电路简单且所需器件实验室均具备,所以选方案二。 2.低频放大电路 方案一:采用晶体三极管组成放大电路,但其器件种类多,不利于后面的检测,所以不选。 方案二:采用运放741组成的比例放大电路进行放大,使用滑阻进行增益的调节,易于实现和检测,所以选方案二。 三、电路设计 1. 正弦信号发生模块 基本电路如图1,采用RC 串并联网络,由公式RC f π210= 可计算出当 F C R n 68468=Ω=,时,Hz f 50000=,调节10k 的滑阻使其起振并输出不失真的 正弦波,调节100Ω的滑阻,可以改变输出幅值,使输出峰值为0.25V 。输出波形如图2(输出为通道A ): 图1 正弦波、方波、三角波 信号电路设计 本系统以ICL8038集成块为核心器件,制作一种函数信号发生器,只需要个别的外部元件就能产生从0.001Hz ~30KHz 的低失真正弦波、三角波、矩形波等脉冲信号。 一、电源: 根据设计所要求的性能指标,选择集成三端稳压器。 因为要求输出电压可调,所以选择三端可调式集成稳压器。可调式集成稳压器,常见的主要有CW317、CW337、LM317、LM337。317系列稳压器输出连续可调的正电压,337系列稳压器输出连可调的负电压,可调围为1.2V~37V ,最大输出电流m ax O I 为1.5A 。稳压部含有过流、过热保护电路,具有安全可靠,性能优良、不易损坏、使用方便等优点。其电压调整率和电流调整率均优于固定式集成稳压构成的可调电压稳压电源。LM317系列和LM337系列的引脚功能相同,管脚图和典型电路如图4-5和图4-6。 图4-5 管脚 图4-6典型电路 输出电压表达式为: ? ?? ? ? +=11125.1R RP U o 式中,1.25是集成稳压块输出端与调整端之间的固有参考电压REF V ,此电压加于给定电阻1R 两端,将产生一个恒定电流通过输出电压调节电位器1RP ,电阻1R 常取值 ΩΩ240~120,1RP 一般使用精密电位器,与其并联的电容器 C 可进一步减小输出电压的纹 波。图中加入了二极管D ,用于防止输出端短路时10μF 大电容放电倒灌入三端稳压器而被损坏。 LM317其特性参数: 输出电压可调围:1.2V ~37V 输出负载电流:1.5A 输入与输出工作压差ΔU=U i -U o :3~40V 能满足设计要求,故选用LM317组成稳压电路。 整体稳压电路原理图 二、主电路 〖方案一〗 由文氏电桥产生正弦振荡,这一方案为一开环电路,结构简单,产生的正弦波和方波的波形失真较小 文氏电桥振荡器正弦波发生器: 又称文氏电桥振荡器,如图1-3-1所示,其中A 放大器由同相运放电路组成,图3-4-2, 因此, )1(1 2R R V V A d o v +==怎样理解阻抗匹配,很难得的资料

(完整版)ADS软件学习及阻抗匹配电路的仿真设计

阻抗变换变换的方法和计算

阻抗匹配定义

阻抗匹配的原理与方法

传输线阻抗匹配的方法

ADC阻抗以及阻抗匹配

正弦波产生及阻抗匹配

正弦波信号电路设计说明