第2章习题

一、单选题

1.若在编码器中有50个编码对象,则输出二进制代码位数至少需要(B )位。

A)5 B)6 C)10 D)50

2.一个16选1的数据选择器,其选择控制(地址)输入端有(C )个,数据输入端有(D )个,输出端有( A )个。

A)1 B)2 C)4 D)16

3.一个8选1的数据选择器,当选择控制端S2S1S0的值分别为101时,输出端输出(D )的值。

A)1 B)0 C)D4D)D5

4.一个译码器若有100个译码输出端,则译码输入端至少有(C )个。

:

A)5 B)6 C)7 D)8

5.能实现并-串转换的是(C )。

A)数值比较器B)译码器C)数据选择器D)数据分配器

6.能实现1位二进制带进位加法运算的是(B )。

A)半加器B)全加器C)加法器D)运算器

7.欲设计一个3位无符号数乘法器(即3×3),需要()位输入及(D )位输出信号。A)3,6 B)6,3 C)3,3 D)6,6

8.欲设计一个8位数值比较器,需要()位数据输入及(B )位输出信号。

A)8,3 B)16,3 C)8,8 D)16,16

9. 4位输入的二进制译码器,其输出应有(A )位。

—

A)16 B)8 C)4 D)1

二、判断题

1. 在二——十进制译码器中,未使用的输入编码应做约束项处理。()

2. 编码器在任何时刻只能对一个输入信号进行编码。()

3. 优先编码器的输入信号是相互排斥的,不容许多个编码信号同时有效。()

4. 编码和译码是互逆的过程。()

5. 共阴发光二极管数码显示器需选用有效输出为高电平的七段显示译码器来驱动。()

6. 3位二进制编码器是3位输入、8位输出。()

7. 组合逻辑电路的特点是:任何时刻电路的稳定输出,仅仅取决于该时刻各个输入变量的取值,与电路原来的状态无关。()

《

8. 半加器与全加器的区别在于半加器无进位输出,而全加器有进位输出。()

9. 串行进位加法器的优点是电路简单、连接方便,而且运算速度快。()

10. 二进制译码器的每一个输出信号就是输入变量的一个最小项。()

11. 竞争冒险是指组合电路中,当输入信号改变时,输出端可能出现的虚假信号。()

三、综合题

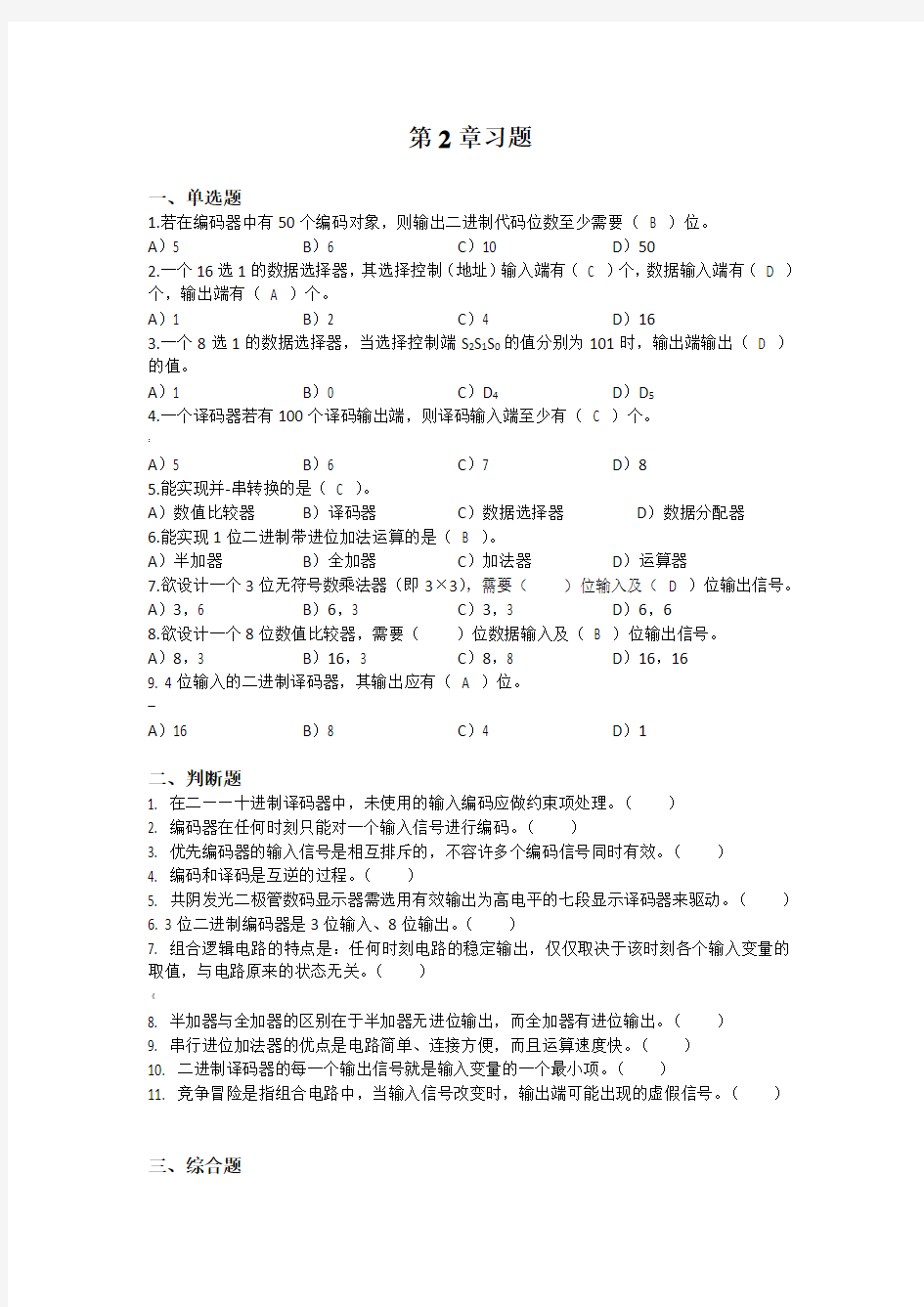

1.如图所示逻辑电路是一个什么电路,当A 3~A 0输入0110,B 3~B 0输入1011,Cin 输入1时,Cout 及S 3~S 0分别输出什么 +A 3B 3C in S 3C out +++A 2B 2A 1B 1A 0B 0S 2S 1S 0

答:图中所示电路是4位串行进位全加器电路

]

C out =1,S 3S 2S 1S 0=0001

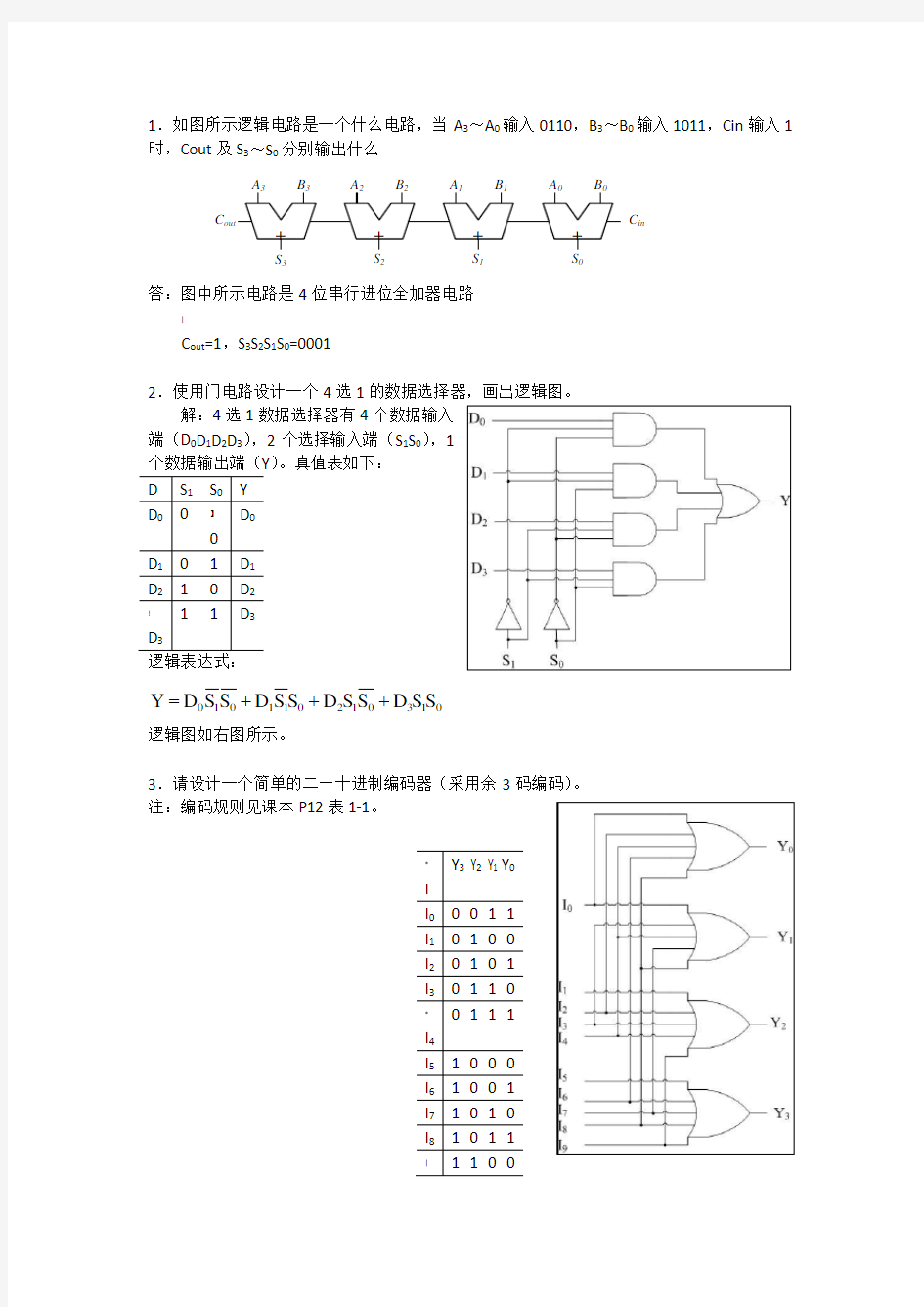

2.使用门电路设计一个4选1的数据选择器,画出逻辑图。

解:4选1数据选择器有4个数据输入

端(D 0D 1D 2D 3),2个选择输入端(S 1S 0),1

个数据输出端(Y )。真值表如下:

D S 1 S 0 Y

D 0 0 】 0

D 0

D 1 0

1 D 1 D

2 1

0 D 2 ! D 3 1

1 D 3

逻辑表达式:

013012011010S S D S S D S S D S S D Y +++=

逻辑图如右图所示。

3.请设计一个简单的二—十进制编码器(采用余3码编码)。

注:编码规则见课本P12表1-1。

*

I

Y 3 Y 2 Y 1 Y 0 I 0 0011

I 1 0100

I 2 0101

I 3 0110

* I 4

0111

I 5 1000

I 6 1001

I 7 1010

I 8 1011

| 1100

解:设10个信号输入端分别为

(I 0~I 9),4个编码输出端分别为

(Y 3~Y 0),根据余3码编码表:

可得输出表达式:

Y 3 = I 5+ I 6+ I 7+ I 8+ I 9

Y 2 = I 1+ I 2+ I 3+ I 4+ I 9

Y 1 = I 0+ I 3+ I 4+ I 7+ I 8

Y 0 = I 0+ I 2+ I 4+ I 6+ I 8

.

逻辑图如右图所示。

4.利用门电路设计一个1路-4路数据分配器。数据分配器的功能与数据选择器功能相反,相当于一个1路-多路的开关,可以实现数据的串-并转换。1路-4路数据分配器的结构示意图如下图,其功能是将输入的数据选通送至4个输出中的一个。当S 1S 0=00时,Y 0=D ;当S 1S 0=01时,Y 1=D ;当S 1S 0=10时,Y 2=D ;当S 1S 0=11时,Y 3=D 。

D S 1 ] S 0

Y 0 Y 1 Y 2 Y 3

D 0 0 D 0 · 0

D 0

1 0 D 0 0 D #

1

0 0 0 D 0 D 1 1 0 < 0

0 D

表达式:0130

120

110

10S DS Y S DS Y S S D Y S S D Y ====

逻辑图如右图所示。

I 9

5.利用与门(74HC08)及4位加法器(74HC283)设计一个3×2乘法器,画出逻辑图。

1

1

1

1

2

0 0

1

2

B

A

B

A

B

A

B A

B

A

B

A

(对应的芯片引脚略)