基于FPGA的串口通信电路设计与实现

发表时间:2018-11-07T09:39:41.587Z 来源:《防护工程》2018年第17期作者:马龙[导读] 由于现代工业企业中在线监测的日益增长。需要PC机与更多设备进行通信,串口通信具有实现简单,使用灵活。数据传输准确等优点。

陕西烽火电子股份有限公司陕西宝鸡 721000

摘要:由于现代工业企业中在线监测的日益增长。需要PC机与更多设备进行通信,串口通信具有实现简单,使用灵活。数据传输准确等优点。在工业监控和实时监控系统中得到了广泛应用。由于监测设备的增加。PC机原有的串口不能再满足通信的需求,传统的设计方法是使用硬件扩展八个串口,但是额外增加了硬件设计成本和实际编程的难度。然而FPGA的UARTIP可灵活定制的优点使得基于黜的设计方法无需额外的硬件串口扩展,减少了硬件开发调试的难度,同时满足串行传输的要求。基于此,本文主要对基于FPGA的串口通信电路设计与实现进行分析探讨。

关键词:基于FPGA;串口通信;电路设计;实现

1、前言

FPGA(Field-Programmable Gate Array),即现场可编程门阵列,它是作为专用集成电路领域中一种半定制电路出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。FPGA中具有丰富的触发器和I/O口,采用描述语言(VHDL和VerilogHDL)进行设计,用户可以根据需要,描述出具有各种功能的电路。基于以上原因,我们可以利用FPGA实现多串口通信中的数据转换和中断控制功能,从而简化电路、缩小PCB面积,也可以很方便的进行升级改动和模块移植。

2、设计要求

整个设计的硬件电路以DSP和FPGA为主构架,DSP和FPGA之间通过DSP的EMIF接口连接。其中,DSP是主处理器,用于实现串口数据的处理,FPGA作为DSP的外围电路,实现UART模块的串行数据的接收和发送、数据的串并/并串转换及接收中断的产生,同时,实现多串口的中断控制功能。当有接收数据时,FPGA通过中断方式通知DSP。 UART模块的数据格式:波特率可以按标准波特率设置;按字节接收,每个字节前包含一个起始位(低电平,逻辑值0),无校验位,最后是一位停止位和不定长度的空闲位(高电平,逻辑值1);接收到一个完整字节后产生一个中断(高电平,逻辑值1),当数据被读取后,中断信号复位(低电平,逻辑值0)。中断控制器应能实现8路UART模块的中断接收和处理,最后给DSP输出一个中断信号,输入的各中断信号之间无优先级设定。

3、设计方案

完整的设计由时钟管理模块、接口模块、UART模块和中断控制器组成。时钟管理模块产生设计中所需各种时钟,包括主处理时钟和接收与发送的波特率时钟;接口模块实现DSP和FPGA之间的中断、读写功能;UART模块由接收和发送子模块组成,实现数据的串行接收和串行发送功能;中断控制器由中断采样子模块和中断处理子模块组成,实现8路UART中断接收和处理功能。下面分别对这些模块的设计给予描述。

3.1 时钟管理模块

设输入FPGA的时钟为50MHz,则主处理时钟设计为50MHz。U A R T 的接收和发送采用相同的波特率进行,本设计中采用115200b/s进行收发,这就需要对50MHz时钟进行分频以产生所需的波特率。

3.2 接口模块

接口模块连接时钟管理模块、UART模块和中断处理器,并与DSP采用EMIF总线相连接。与DSP相关的信号有:wr_n、rd_n、cs_n、addrs、data_bus和dsp_int,在cs_n和wr_n有效时,DSP通过addrs选通不同的UART模块,将需要发送的并行数据发送给发送寄存器,执行发送功能。DSP响应外部中断时,在cs_n和rd_n有效时,通过addrs读取中断控制器的中断矢量和UART模块接收的数据。

3.3 UART模块

3.3.1 发送模块

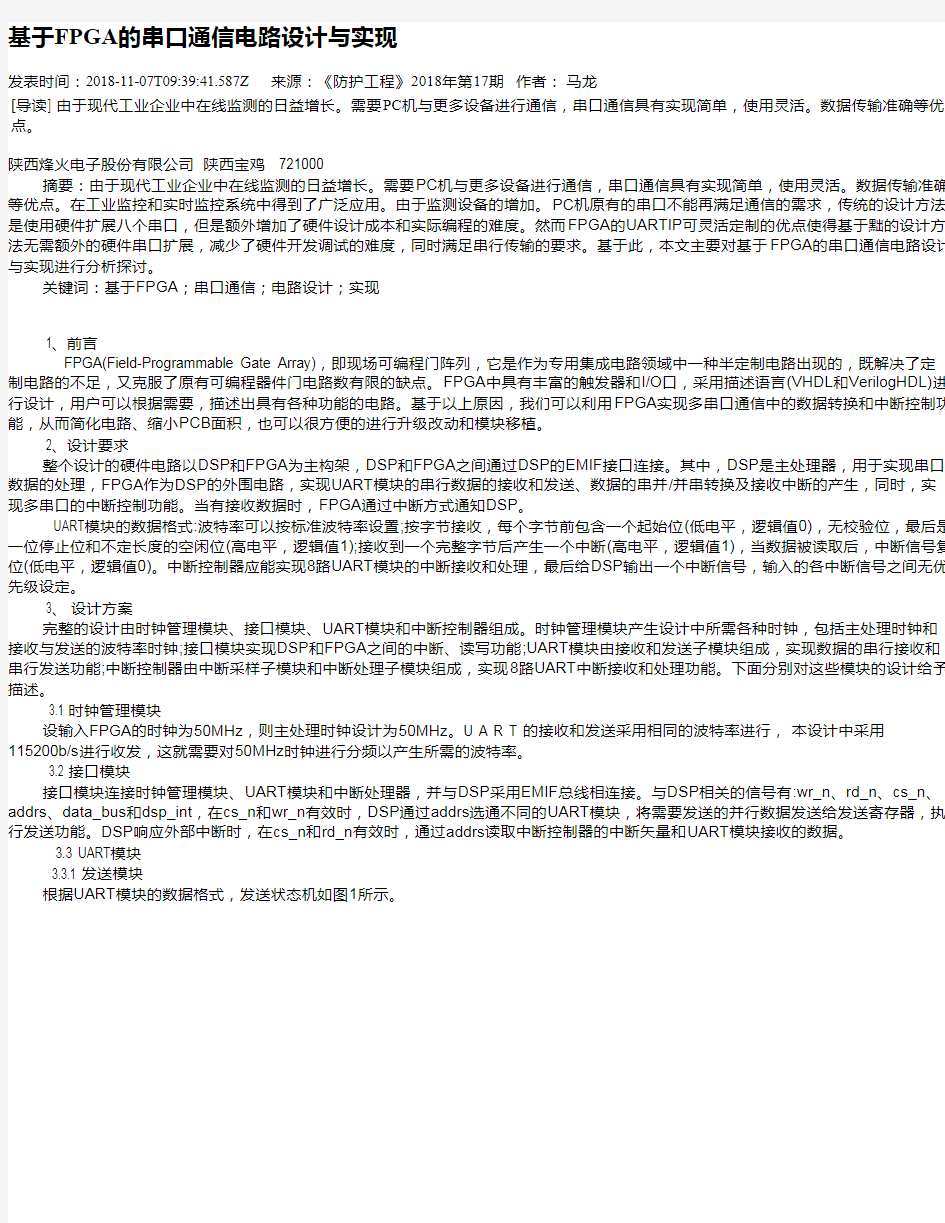

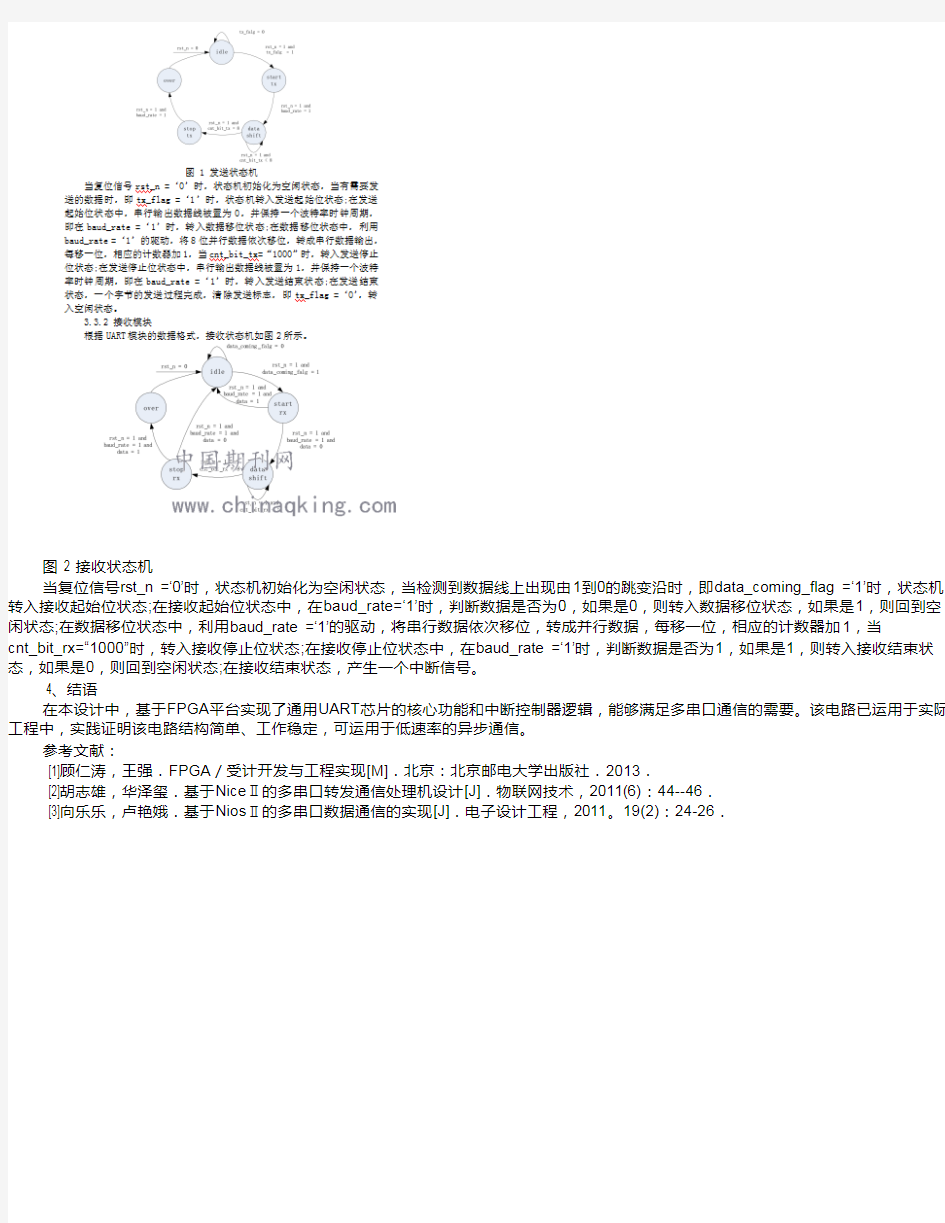

根据UART模块的数据格式,发送状态机如图1所示。