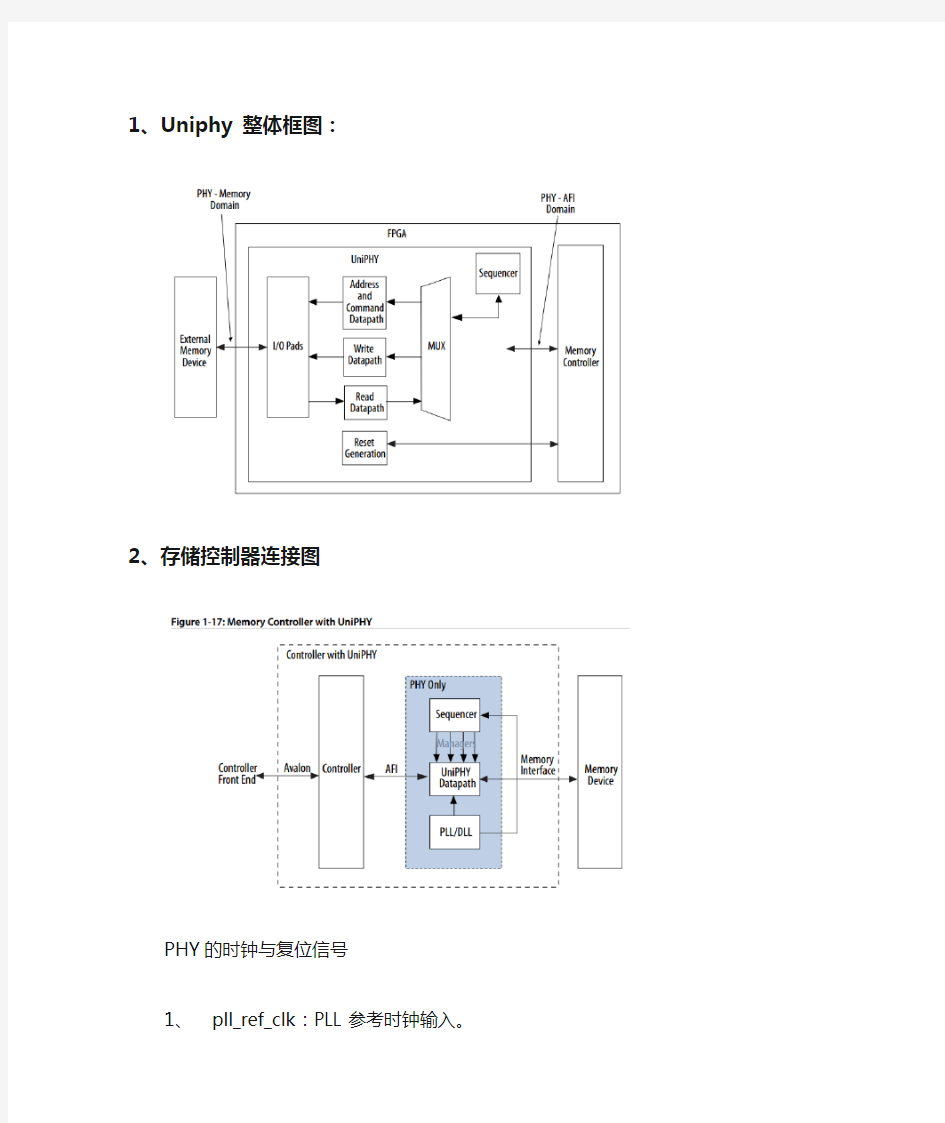

1、Uniphy整体框图:

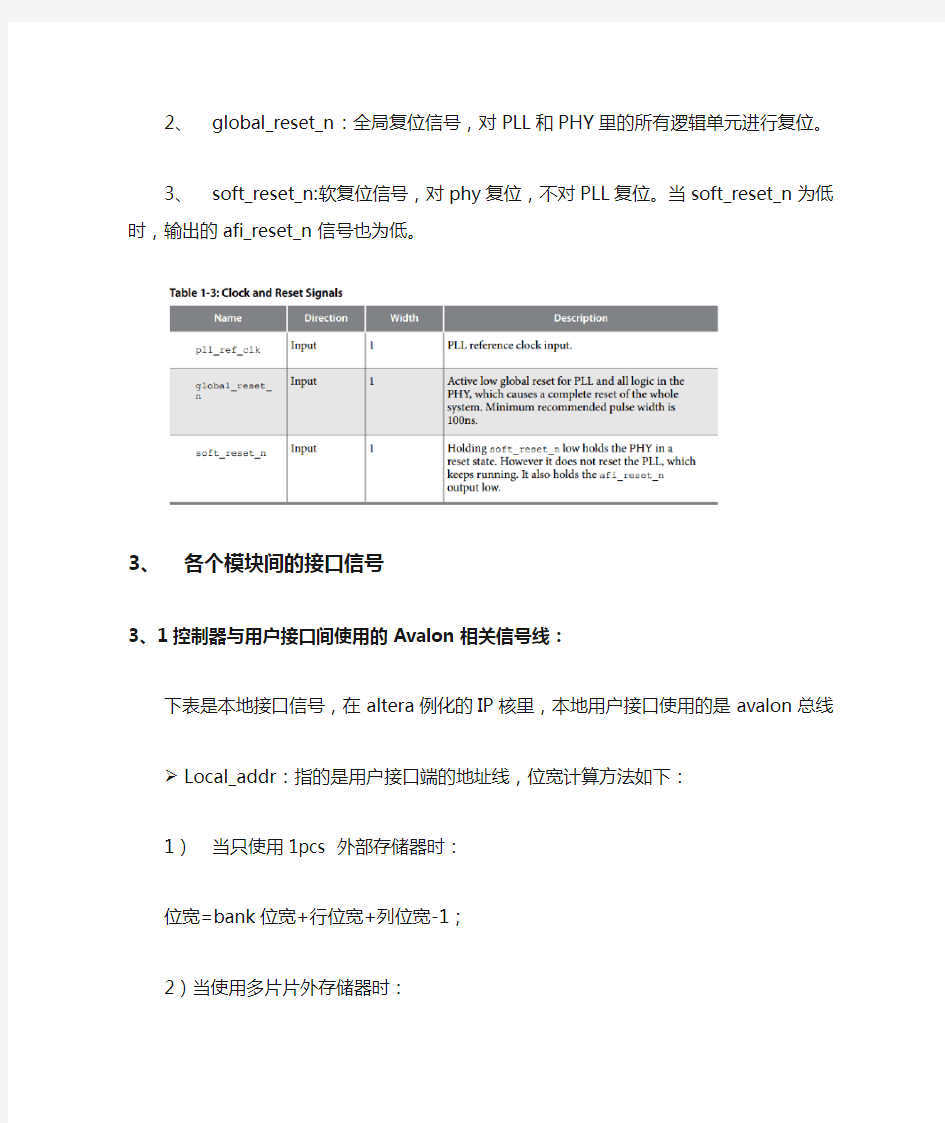

2、存储控制器连接图

PHY的时钟与复位信号

1、pll_ref_clk:PLL参考时钟输入。

2、global_reset_n:全局复位信号,对PLL和PHY里的所有逻辑单元进行复位。

3、soft_reset_n:软复位信号,对phy复位,不对PLL复位。当soft_reset_n为低时,输出的

afi_reset_n信号也为低。

3、各个模块间的接口信号

3、1控制器与用户接口间使用的Avalon相关信号线:

下表是本地接口信号,在altera例化的IP核里,本地用户接口使用的是avalon总线 Local_addr:指的是用户接口端的地址线,位宽计算方法如下:

1)当只使用1pcs 外部存储器时:

位宽=bank位宽+行位宽+列位宽-1;

2)当使用多片片外存储器时:

位宽=芯片位宽+bank位宽+行位宽+列位宽-1;

计算位宽时减1 是因为用户数据接口宽度是memory侧数据宽度的两倍(memory 侧是在时钟的上升和下降沿都收发数据,而用户侧只在时钟的上升沿收发数据,假如用户读写数据的时钟频率与memory侧的数据频率相同,那么,在时钟上升沿来时,用户侧发送的数据位宽应是memory侧数据位宽的两倍)。

local_be:字节使能信号(用于向控制器写数据时),与memory侧的DM(data mask )信号作用一样,比如,当想使local_data的某8位数据无效,将local_be

的对应位置0即可。

local_burstbegin:本地突发开始信号,当avalon总线开始突发读写时,将此信号置位‘1’。(使用条件:本地接口是avalon总线,且memory侧的突发长度大

于2)

local_size:本地突发长度,即连续读或写的local_data个数。长度不能超过ddrip 核里配置的maximum avalon- mm burst length的长度。

local_wdata:本地写数据。

local_write_req:写请求信号。只有当local_ready信号为高时,才能发起写请求。

local_rdata:本地读数据。

local_read_req:读请求信号。只有当local_ready信号为高时,才能发起读请求。

local_rdata_valid:本地读数据有效标志,当其为高时,表示此时local_rdata数据有效。

local_ready:为‘1’时表示此时控制器可以接受读写请求信号。

local_refresh_req:刷新控制器请求信号。

local_refresh_ack:刷新请求确认标志,表示一次刷新完成标志。

local_init_done:本地初始化memory完成标志。

local_wdata_req:写数据请求信号。在avalon-mm模式时不使用该信号。

3、2controller与PHY间的接口信号线

时钟与复位信号

afi_clk:AFI接口的所有数据变化都是与该时钟同步的。

地址和控制信号

写数据相关信号

读数据相关信号

afi校准状态信号

跟踪管理信号

3、3PHY与外部memory间的接口信号线

ddr_dq:数据线接口,位宽是local_wdata,local_rdata的1/2(因为memory是双边沿读写数据)。

ddr_dqs:探测ddr_dq上的数据信号。读操作时,ddr_dqs边沿与读数据边沿对齐;写操作时,ddr_dqs边沿与写数据中间对齐。

clk_to_sdram,clk_to_sdram_n:memory的差分时钟输入。

ddr_a[]:memory的地址总线。

ddr_ba[]:memory的bank地址总线。

ddr_cas_n:memory列地址有效信号。

ddr_cke[]:memory的时钟使能信号。

ddr_cs_n[]:memory的片选信号。

ddr_dm:data mask写数据到memory时,ddr_dq上的数据是否屏蔽。(ddr_dm 为‘1’时,对应ddr_dq数据无效;为‘0’时数据有效)。

ddr_odt:memory内部终结电阻器控制信号。(memory在内部集成了终结电阻,以减少反射的干扰信号)

ddr_cas_n:memory行地址有效信号。ddr_we_n:memory写数据使能信号。

4、ddr2sdram的half-rate ,full-rate读写时序。

full-rate时:afi_clk与mem_ck频率相同。avl_data数据位宽是mem_data的2倍

half-rate时:afi_clk是mem_ck频率的一半。avl_data数据位宽是mem_data的4倍

4、4half-rate ddr2 sdram read时序

5、altera例化ddr2 sdramip核参数设置

首先肯定是在quartusii里新建一个工程,然后选择tools->Megawizard Plug-in Manager 选择创建一个新的IP核,然后在interface->external memory里找到ddr2 sdram选中,命名。然后点击next就出来ddr2 ip核的配置界面。

fpga芯片选用的是Cyclone V :5CEFA5F23C8。速度等级是8

5.1 Interface Type

勾选此项表示使能硬核外部存储器接口。不勾选表示用逻辑单元去生成ddr2 ip核。

硬核与软核的区别。

1、硬核是固化在FPGA内部的专用硬件电路,而软核是用逻辑单元去构建的;

1、硬核的可工作频率比软核更高;

2、硬核的外接memory引脚只能用指定的引脚,而软核可以自己指定。

5.2 PHY Settings

Speed_Grade: 8 (fpga芯片选用的是Cyclone V :5CEFA5F23C8。速度等级是8。

Generate phy only:勾选此选项的话,就只会生成PHY模块,不会生成控制模块。 Memory clock frequency:memory工作的时钟频率,此值不能超过min{fpga芯片指定的工作频率,Memory device speed grade}。本工程中设置的Memory clock frequency为200Mhz。

PLL reference clock frequency: 25 Mhz 给IP核锁相环输入的时钟频率。

Rate on Avalon-MM interface:有Half 和Full两个选项。Half:指本地用户接口的时钟频率afi_clk为memory侧时钟的1/2。Full:则本地用户接口的时钟频率afi_clk 与memory侧时钟频率相同。

Advanced PHY Settings

PLL,DLL,OCT sharing mode 设置其PLL,DLL,OCT是否输出给其他的UniPHY模块使用。

Enable AFI half rate clock:表示使能输出AFI half rate clock,频率为AFI rate clock的一半

5、2 Memory Parameters

Memory的参数设置,根据memory的datasheet 设置。

Memory vendor:选择memory的器件厂家,本工程选择Micron

Memory format:选择memory的形式,本工程选择Discrete device

Discrete device: 分立器件。就是单片的memory

DIMM:Dual-Inline-Memory-Modules,即双列直插式存储模块。

Unbuffered DIMM: 不带缓存的内存,也就是说在内存条PCB上没有缓存(buffer)或寄存器(register)的内存条。这类内存条主要定位于桌面PC市场,是我们常见

的低价内存模组。它的主要工作原理是所有的信号都是从内存控制器直通到DRAM

芯片颗粒上,信号传输延迟小性能较高。但也正是这个原因Unbuffered DIMM并不

如带寄存器的内存模组工作稳定,因而Unbuffered DIMM一般不在服务器上应用,可以应用在要求不高的桌面PC上。

Registered DIMM:最常见的内存模块类型。RDIMM使用寄存器,从电力上将内存模

块从剩余主板中隔离出来。积极的一方面是,只需更少的电力负载支持,系统能够

填充更多RDIMM,支撑内存容量。不好的是缓冲组件增加了对内存转换的延迟,

稍微降低了性能并增加了能耗需求。

Memory device speed grade: memory的速度等级,根据memory手册选择,本工程选333.333Mhz

Total Interface width:memroy数据总线(DQ)的宽度,本工程选择16位宽。

DQ/DQS group size:指每一组DQS对应的DQ位宽。自动生成位8

Number of DQS groups:DQS的组数,自动生成为2

Number of chip selects: memory芯片的个数本工程用了1pcsmemroy,选择1

Number of clocks:memory使用的时钟个数。本工程为1。

Row address width:memory的行地址宽度,本工程为13。

Column address width:memory的列地址宽度,本工程为10。

Bank-addres width:memory的bank宽度。

Enable DM pins:使能memory的DM(data mask)pins 。

DQS # Enable:使能DQS(DQ strobe)引脚。

Burst length:设置memory的突发长度,即memory一次读写的数据(DQ)个数。 Read Burst Type:设置突发读的方式一般都是用Sequential。

Sequential:顺序读,即给一个初始地址,读的下一个数据的地址就是初始地址+1。

Interleaved:交叉模式。下面截图是美光ddr2 spec里Interleaved的工作模式。

DLL precharge power down:DLL在预充电下电时,DDL选择“fast exit”or “slow txit”,选择默认fast exit。

Memory CAS latency setting:指设置CAS(列地址选通脉冲)潜伏周期,从CAS与读取命令发出到第一个数据输出的时间。从memory datasheet查找,本处为4。

Output drive strength setting:输出驱动阻抗设置,选择默认的full。

Memory additive CAS latency setting:选择默认设置0。

ODT setting: 终结电阻值设置。

SRT Enable:刷新速率设置。0°到85°时选择1x refresh rate,大于85°选2X;此处选择1X。

5、3 Memory Timing

该部分主要是设置memory的一些时序参数,具体参数值可以查询memory对应的datasheet。或者从下图的Preset里选择对应你使用的memory器件型号,双击就会设置好memorytiming里的参数。

下面几个截图就是从美光memory型号MICRON MT47H64M16HR-3IT里边查找到的时序参数。

tRP=15ns

tRCD=15ns,

tRRD=10ns

tRFC=127.5ns

tDQSCK=400ps tDQSS=0.25cycle tDQSH=0.35 cycle tDSS=0.2 cycle tDSH=0.2 cycle

tDQSQ=240ps tQHS=340ps tDSb=100ps tDHb=175ps

tISb=200ps tIHb=275ps tRAS=40ps tFAW=50ps

全面教你认识内存参数 内存热点 Jany 2010-4-28

内存这样小小的一个硬件,却是PC系统中最必不可少的重要部件之一。而对于入门用户来说,可能从内存的类型、工作频率、接口类型这些简单的参数的印象都可能很模糊的,而对更深入的各项内存时序小参数就更摸不着头脑了。而对于进阶玩家来说,内存的一些具体的细小参数设置则足以影响到整套系统的超频效果和最终性能表现。如果不想当菜鸟的话,虽然不一定要把各种参数规格一一背熟,但起码有一个基本的认识,等真正需要用到的时候,查起来也不会毫无概念。 内存种类 目前,桌面平台所采用的内存主要为DDR 1、DDR 2和DDR 3三种,其中DDR1内存已经基本上被淘汰,而DDR2和DDR3是目前的主流。 DDR1内存 第一代DDR内存 DDR SDRAM 是 Double Data Rate SDRAM的缩写,是双倍速率同步动态随机存储器的意思。DDR内存是在SDRAM内存基础上发展而来的,仍然沿用SDRAM生产体系,因此对于内存厂商而言,只需对制造普通SDRAM 的设备稍加改进,即可实现DDR内存的生产,可有效的降低成本。 DDR2内存 第二代DDR内存

DDR2 是 DDR SDRAM 内存的第二代产品。它在 DDR 内存技术的基础上加以改进,从而其传输速度更快(可达800MHZ ),耗电量更低,散热性能更优良。 DDR3内存 第三代DDR内存 DDR3相比起DDR2有更低的工作电压,从DDR2的1.8V降落到1.5V,性能更好更为省电;DDR2的4bit 预读升级为8bit预读。DDR3目前最高能够1600Mhz的速度,由于目前最为快速的DDR2内存速度已经提升到800Mhz/1066Mhz的速度,因而首批DDR3内存模组将会从1333Mhz的起跳。 三种类型DDR内存之间,从内存控制器到内存插槽都互不兼容。即使是一些在同时支持两种类型内存的Combo主板上,两种规格的内存也不能同时工作,只能使用其中一种内存。 内存SPD芯片 内存SPD芯片

SDRAM内存详解(经典) 我们从内存颗粒、内存槽位接口、主板和内存之间的信号、接口几个方面来详细阐述SDRAM内存条和主板内存系统的设计思路... 虽然目前SDRAM内存条价格已经接底线,内存开始向DDR和Rambus内存过渡。但是由于DDR内存是在SDRAM基础上发展起来的,所以详细了解SDRAM内存的接口和主板设计方法对于设计基于DDR内存的主板不无裨益。下面我们就从内存颗粒、内存槽位接口、主板和内存之间的信号接口几个方面来详细阐述SDRAM内存条和主板内存系统的设计思路。 内存颗粒介绍 对于DRAM(Dynamic Random Access Memory)内存我想凡是对于计算机有所了解的读者都不会陌生。这种类型的内存都是以一个电容是否充有电荷来作为存储状态的标志,电容冲有电荷为状态1,电容没有电荷为状态0。其最大优点是集成度高,容量大,但是其速度相对于SRAM (Static Random Access Memory) 内存来说慢了许多。目前的内存颗粒封装方式有许多种,本文仅仅以大家常见的TSSOP封装的内存颗粒为例子。 其各个管脚的信号定义和我们所使用的DIMM插槽的定义是相同的,对于不同容量的内存,地址信号的位数有所不同。另外一个需要注意的地方就是其供电电路。Vcc和Vss是为内存颗粒中的存储队列供电,而VccQ和VssQ是为内存颗粒中的地址和数据缓冲区供电。两者的作用不同。 我们对内存颗粒关心的问题主要是其颗粒的数据宽度(数据位数)和容量(寻址空间大小)。而对于颗粒自检、颗粒自刷新等等逻辑并不需要特别深入的研究,所以对此我仅仅是一笔带过,如果读者有兴趣的读者可以详细研究内存颗粒的数据手册。虽然内存颗粒有这么多的逻辑命令方式,但是由于目前北桥芯片和内存颗粒的集成度非常高,只要在布线和元器件的选择上严格按照内存规范来设计和制造,需要使用逻辑分析仪来调试电路上的差错的情况比较少,并且在设计过程中尽量避免出现这种情况。 168线DIMM内存插槽的信号定义 我们目前PC和Server使用的内存大都是168 Pins的SDRAM,区别只是其工作频率有的可能是100MHz频率,有的可能是133MHz频率的。但是只要是SDRAM,其DIMM插槽的信号定义是一样的。而这些引脚得定义就是设计内存条和主板所必须遵从的规范。 内存引脚主要分为如下几类:地址引脚、数据引脚(包含校验位引脚)、片选等控制信号、时钟信号。整个内存时序系统就是这些引脚上的信号配合产生。下面的表中就是内存插槽的引脚数量和引脚定义,对于一些没有定义或者是保留以后使用的信号就没有列出来。 符号功能详细描述 DQ [0-63] I/O 数据输入/输出 CB [0-7] I/O ECC内存的ECC校验输入/输出 A [0-13] I/O 地址选择 BA [0-1] Control Bank选择 CS [0-3] Control 片选信号 RAS Control 行地址选择信号 CAS Control 列地址选择信号 DQMB [0-7] Control 数据掩码控制(DQ Mask)高有效* WE Control 写允许信号 CK [0-3] Clock 时钟信号 CKE [0-1] Clock 时钟允许信号** REGE Control 寄存器 (Registered) 允许信号

举例9-9-9-27,一般1600的条子spd出厂就这么设置的 前面2个9对性能很重要,第2个9又比第1个9重要,比如说 我要超1866或者2133,设置成9-10-X-X基本没有问题,但是 设置成10-9-X-X就开不了机了,很多条子都这样子的,比如说 现在很火的3星金条。 第3位9基本上是打酱油的了,设置成9,10,11都对性能木有太大影响。 第4位数字基本就无视好了,设置21-36对测试都没变化,原来稳定的 还是稳定,原来开不了机的还是开不了。 以前的ddr2时代对内存的小参数很有影响,现在ddr3了,频率才是王道哦。 2133的-11-11-11-30都要比1866的-9-9-9-27测试跑分的多。当然平时用是感觉不出来的。 最后我再鄙视下金士顿的XX神条马甲套装,当年不懂事大价钱买的,就是YY用的, 1.65v上个1866都吃力,还要参数放的烂。 对性能影响最大的是CL 第一个9对性能影响最大。l第二个9对超频稳定性影响最大 最普通的ddr3 1333内存都可以1.5V运行在7-8-6-1666 CR1,77 Z博士: 一般来说,体现内存延迟的就是我们通常说的时序,如DDR2-800内存的标准时序:5-5-5-18,但DDR3-800内存的标准时序则达到了6-6-6-

15、DDR3-1066为7-7-7- 20、而DDR3-1333更是达到了9-9-9-25! 土老冒: 俺想知道博士所说的5-5-5- 18、6-6-6-15等数字每一个都代表什么。 Z博士: 这4个数字的含义依次为: CAS Latency(简称CL值)内存CAS延迟时间,这也是内存最重要的参数之一,一般来说内存厂商都会将CL值印在产品标签上。 第二个数字是RAS-to-CAS Delay(tRCD),代表内存行地址传输到列地址的延迟时间。 第三个则是Row-precharge Delay(tRP),代表内存行地址选通脉冲预充电时间。 第四个数字则是Row-active Delay(tRAS),代表内存行地址选通延迟。 除了这四个以外,在AMD K8处理器平台和部分非Intel设计的对应Intel芯片组上,如NVIDIA nForce 680i SLI芯片组上,还支持内存的CMD 1T/2T Timing 调节,CMD调节对内存的性能影响也很大,其重要性可以和CL相比。 其实这些参数,你记得太清楚也没有太大用处,你就只需要了解,这几个参数越低,从你点菜到上菜的时间就越快。 土老冒: 好吧,俺自己也听得一头雾水,只需要记得它越低越好就行了。那么俺想问,为什么DDR3内存延迟提高了那么多,Intel和众多的内存模组厂商还要大力推广呢?

8086CPU系统、总线操作和时序 第一节 8086的引脚信号与功能 回顾:8086/8088微型计算机的组成、结构及微机系统的工作过程,微机系统的存储器组织及相关概念。 本讲重点:8086/8088CPU的两种工作模式,8086/8088CPU的外部结构,即引脚信号及其功能。 讲授内容: 一、 8086/8088微处理器工作模式及外部结构 1.8086/8088CPU的两种工作模式 为了适应各种使用场合,在设计8088/8086CPU芯片时,就考虑了其应能够使它工作在两种模式下,即最小模式与最大模式。 所谓最小模式,就是系统中只有一个8088/8086微处理器,在这种情况下,所有的总线控制信号,都是直接由8088/8086CPU产生的,系统中的总线控制逻辑电路被减到最少,该模式适用于规模较小的微机应用系统。 最大模式是相对于最小模式而言的,最大模式用在中、大规模的微机应用系统中,在最大模式下,系统中至少包含两个微处理器,其中一个为主处理器,即8086/8086CPU,其它的微处理器称之为协处理器,它们是协助主处理器工作的。 与8088/8086CPU配合工作的协处理器有两类,一类是数值协处理器8087 另一类是输入/输出协处理器8089。 8087是一种专用于数值运算的协处理器,它能实现多种类型的数值运算,如高精度的整型和浮点型数值运算,超越函数(三角函数、对数函数)的计算等,这些运算若用软件的方法来实现,将耗费大量的机器时间。换句话说,引入了8087协处理器,就是把软件功能硬件化,可以大大提高主处理器的运行速度。 8089协处理器,在原理上有点像带有两个DMA通道的处理器,它有一套专门用于输入/输出操作的指令系统,但是8089又和DMA控制器不同,它可以直接为输入/输出设备服务,使主处理器不再承担这类工作。所以,在系统中增加8089协处理器之后,会明显提高主处理器的效率,尤其是在输入/输出操作比较频繁

D D R 系列系列内存内存内存详解及硬件详解及硬件 设计规范 By: Michael Oct 12, 2010 haolei@https://www.doczj.com/doc/5b16021343.html,

目录 1.概述 (3) 2.DDR的基本原理 (3) 3.DDR SDRAM与SDRAM的不同 (5) 3.1差分时钟 (6) 3.2数据选取脉冲(DQS) (7) 3.3写入延迟 (9) 3.4突发长度与写入掩码 (10) 3.5延迟锁定回路(DLL) (10) 4.DDR-Ⅱ (12) 4.1DDR-Ⅱ内存结构 (13) 4.2DDR-Ⅱ的操作与时序设计 (15) 4.3DDR-Ⅱ封装技术 (19) 5.DDR-Ⅲ (21) 5.1DDR-Ⅲ技术概论 (21) 5.2DDR-Ⅲ内存的技术改进 (23) 6.内存模组 (26) 6.1内存模组的分类 (26) 6.2内存模组的技术分析 (28) 7.DDR 硬件设计规范 (34) 7.1电源设计 (34) 7.2时钟 (37) 7.3数据和DQS (38) 7.4地址和控制 (39) 7.5PCB布局注意事项 (40) 7.6PCB布线注意事项 (41) 7.7EMI问题 (42) 7.8测试方法 (42)

摘要: 本文介绍了DDR 系列SDRAM 的一些概念和难点,并分别对DDR-I/Ⅱ/Ⅲ的技术特点进行了论述,最后结合硬件设计提出一些参考设计规范。 关键字关键字::DDR, DDR, SDRAM SDRAM SDRAM, , , 内存模组内存模组内存模组, , , DQS DQS DQS, DLL, MRS, ODT , DLL, MRS, ODT , DLL, MRS, ODT Notes : Aug 30, 2010 – Added DDR III and the PCB layout specification - by Michael.Hao

浅谈运用波士顿矩阵分析李宁的战略选择 吴雅云12 (中国地质大学(北京)(100083)) 【摘要】波士顿矩阵是分析企业市场战略广泛采用的分析工具,对各行业企业战略选择和定位都具有指导意义。李宁公司自创立以来一直都是中国体育事业的领跑者,在产品战略上采用的也是多品牌业务发展策略。文章运用波士顿矩阵对李宁企业的产品战略选择作一简述,并根据分析结果对李宁今后的战略选择提出可行性建议。 【关键词】波士顿矩阵李宁公司企业战略产品战略 中图分类号:文献标识码:A 文章编号 波士顿矩阵又称市场增长率-相对市场份额矩阵。本法将企业所有产品从销售增长率和市场占有率角度进行再组合。在坐标图上,以纵轴表示企业销售增长率,横轴表示市场占有率,各以10%和50%作为区分高、低的中点,将坐标图划分为四个象限,依次为“问号(?)”、“明星(★)”、“金牛(¥)”、“瘦狗(×)”。在使用中,企业可将产品按各自的销售增长率和市场占有率归入不同象限,使企业现有产品组合一目了然,同时便于对处于不同象限的产品作出不同的发展决策。其目的在于通过产品所处不同象限的划分,使企业采取不同决策,以保证其不断地淘汰无发展前景的产品,保持“问号”、“明星”、“金牛”产品的合理组合,实现产品及资源分配结构的良性循环。波士顿战略矩阵分析方法简单易行, 直观性强, 变化灵活, 在国外已被广泛应用于企业经营战略决策, 本文就运用波士顿矩阵对李宁企业的产品战略选择作一简述,并根据分析结果对李宁今后的战略选择提出可行性建议。 李宁公司自创立以来一直都是中国体育事业的领跑者,他拥有品牌营销、研发、设计、制造、经销及零售能力,产品主要包括自有李宁品牌之运动及 1吴雅云,(1990.7—),女,福建晋江人,中共预备党员,中国地质大学(北京)人文经管学院工商管理专业本科生。 2指导教师:陈黎琴,(1975.5—),女,中共党员,博士,讲师,硕士生导师,研究领域:组织行为,市场营销、广告学等。

内存时序 一种参数,一般存储在内存条的SPD上。2-2-2-8 4个数字的含义依次为:CAS Latency(简称CL值)内存CAS延迟时间,他是内存的重要参数之一,某些牌子的内存会把CL值印在内存条的标签上。RAS-to-CAS Delay(tRCD),内存行地址传输到列地址的延迟时间。Row-precharge Delay(tRP),内存行地址选通脉冲预充电时间。Row-active Delay(tRAS),内存行地址选通延迟。这是玩家最关注的4项时序调节,在大部分主板的BIOS中可以设定,内存模组厂商也有计划的推出了低于JEDEC认证标准的低延迟型超频内存模组,在同样频率设定下,最低“2-2-2-5”这种序列时序的内存模组确实能够带来比“3-4-4-8”更高的内存性能,幅度在3至5个百分点。 在一些技术文章里介绍内存设置时序参数时,一般数字“A-B-C-D”分别对应的参数是 “CL-tRCD-tRP-tRAS”,现在你该明白“2-3-3-6”是什么意思了吧?!^_^下面就这几个参数及BIOS设置中影响内存性能的其它参数逐一给大家作一介绍: 一、内存延迟时序“CL-tRCD-tRP-tRAS”的设置 首先,需要在BIOS中打开手动设置,在BIOS设置中找到“DRAM Timing Selectable”,BIOS设置中可能出现的其他描述有:Automatic Configuration、DRAM Auto、Timing Selectable、Timing Configuring By SPD等,将其值设为“Menual”(视BIOS的不同可能的选项有:On/Off或Enable/Disable),如果要调整内存时序,应该先打开手动设置,之后会自动出现详细的时序参数列表: Command Per Clock(CPC) 可选的设置:Auto,Enable(1T),Disable(2T)。 Command Per Clock(CPC:指令比率,也有翻译为:首命令延迟),一般还被描述为DRAM Command Rate、CMD Rate等。由于目前的DDR内存的寻址,先要进行P-Bank的选择(通过DIMM上CS片选信号进行),然后才是L-Bank/行激活与列地址的选择。这个参数的含义就是指在P-Bank选择完之后多少时间可以发出具体的寻址的L-Bank/行激活命令,单位是时钟周期。 显然,也是越短越好。但当随着主板上内存模组的增多,控制芯片组的负载也随之增加,过短的命令间隔可能会影响稳定性。因此当你的内存插得很多而出现不太稳定的时间,才需要将此参数调长。目前的大部分主板都会自动设置这个参数。 该参数的默认值为Disable(2T),如果玩家的内存质量很好,则可以将其设置为Enable(1T)。CAS Latency Control(tCL) 可选的设置:Auto,1,1.5,2,2.5,3,3.5,4,4.5。 一般我们在查阅内存的时序参数时,如“3-4-4-8”这一类的数字序列,上述数字序列分别对应的参数是“CL-tRCD-tRP-tRAS”。这个3就是第1个参数,即CL参数。 CAS Latency Control(也被描述为tCL、CL、CAS Latency Time、CAS Timing Delay),CAS latency是“内存读写操作前列地址控制器的潜伏时间”。CAS控制从接受一个指令到执行指令之间的时间。因为CAS主要控制十六进制的地址,或者说是内存矩阵中的列地址,所以它是最为重要的参数,在稳定的前提下应该尽可能设低。 内存是根据行和列寻址的,当请求触发后,最初是tRAS(Activeto Precharge Delay),预充电后,内存才真正开始初始化RAS。一旦tRAS激活后,RAS(Row Address Strobe )开始进行需要数据的寻址。首先是行地址,然后初始化tRCD,周期结束,接着通过CAS访问所需数据的精确十六进制地址。期间从CAS开始到CAS结束就是CAS延迟。所以CAS是找到数据的最后一个步骤,也是内存参数中最重要的。 这个参数控制内存接收到一条数据读取指令后要等待多少个时钟周期才实际执行该指令。同时该参数也决定了在一次内存突发传送过程中完成第一部分传送所需要的时钟周期数。这个参数越小,则内存的速度越快。必须注意部分内存不能运行在较低的延迟,可能会丢失数据,因此在提醒大家把CAS延迟设为2或2.5的同时,如果不稳定就只有进一步提高它了。而且提高延迟能使内存运行在更高的频率,所以需要对内存超频时,应该试着提高CAS延迟。

波士顿矩阵法运用于公立医院战略管理的探讨 作者:林铭 来源:《中国卫生产业》2020年第20期 [摘要] 面对竞争日趋激烈的医疗市场,要想赢得优势,吸引更多的患者,公立医院应该转变传统的管理理念,将现代企业管理中的波士顿矩阵法引入到自身的管理方法之中。以大型公立医院C医院为例,通过阐述利用波士顿矩阵法对其部分科室进行分类,并实行不同的管理方法,分析了使用该法前后对C医院的不同效果,以及在使用中应注意的问题,同时也阐明了它的局限性,为公立医院引入此法进行战略管理提供参考与借鉴。 [关键词] 波士顿矩阵法;公立医院;战略管理 [中图分类号] R197 [文献标识码] A [文章编号] 1672-5654(2020)07(b)-0045-03 Discussion on the Application of Boston Matrix Method in the Strategic Management of Public Hospitals LIN Ming Finance Department, Second Affiliated Hospital of Bengbu Medical College, Bengbu,Anhui Province, 233040 China [Abstract] Facing the increasingly competitive medical market, in order to gain advantages and attract more patients, public hospitals should change their traditional management concepts and introduce the Boston matrix method in modern corporate management into their own management methods. Ttaking Hospital C of a large public hospital as an example, by explaining the use of the Boston matrix method to classify some of its departments and implementing different management methods, the different effects on Hospital C before and after using this method are analyzed, and the points that should be paid attention to in use. The problem also clarifies its limitations, and provides reference for public hospitals to introduce this method for strategic management. [Key words] Boston matrix method; Public hospitals; Strategic management 波士頓矩阵法(BCG法)是由战略管理咨询领域的先驱波士顿咨询公司提出的一种规划企业整体业务组合的方法,它把企业的业务按照一定标准划分成4种类型,从而形成不同的发展前景,以此来分析投资各种业务是否合理,方便于将企业有限的资源在各个业务之间合理分配,这种分析方法对生产、销售等策略的制定起到很强的方向指引作用,它是保证企业获得较

内存时序设置详解 内容概要 关键词:内存时序参数设置 导言:是否正确地设置了内存时序参数,在很大程度上决定了系统的基本性能。本文详细介绍了内存时序相关参数的基本涵义及设置要点。 与传统的SDRAM相比,DDR(Dual date rate SDRSM:双倍速率SDRAM),最重要的改变是在界面数据传输上,其在时钟信号上升缘与下降缘时各传输一次数据,这使得DDR 的数据传输速率为传统SDRAM的两倍。同样地,对于其标称的如DDR400,DDR333,DDR266数值,代表其工作频率其实仅为那些数值的一半,也就是说DDR400 工作频率为200MHz。 FSB与内存频率的关系 首先请大家看看FSB(Front Side Bus:前端总线)和内存比率与内存实际运行频率的关系。 FSB/MEM比率实际运行频率 1/1 200MHz 1/2 100MHz 2/3 133MHz 3/4 150MHz 3/05 120MHz 5/6 166MHz 7/10 140MHz 9/10 180MHz 对于大多数玩家来说,FSB和内存同步,即1:1是使性能最佳的选择。而其他的设置都是异步的。同步后,内存的实际运行频率是FSBx2,所以,DDR400的内存和200MHz的FSB正好同步。如果你的FSB为240MHz,则同步后,内存的实际运行频率为240MHz x 2 = 480MHz。

FSB与不同速度的DDR内存之间正确的设置关系 强烈建议采用1:1的FSB与内存同步的设置,这样可以完全发挥内存带宽的优势。内存时序设置 内存参数的设置正确与否,将极大地影响系统的整体性能。下面我们将针对内存关于时序设置参数逐一解释,以求能让大家在内存参数设置中能有清晰的思路,提高电脑系统的性能。 涉及到的参数分别为: ?CPC : Command Per Clock ?tCL : CAS Latency Control ?tRCD : RAS to CAS Delay ?tRAS : Min RAS Active Timing ?tRP : Row Precharge Timing ?tRC : Row Cycle Time ?tRFC : Row Refresh Cycle Time ?tRRD : Row to Row Delay(RAS to RAS delay) ?tWR : Write Recovery Time ?……及其他参数的设置 CPC : Command Per Clock 可选的设置:Auto,Enable(1T),Disable(2T)。 Command Per Clock(CPC:指令比率,也有翻译为:首命令延迟),一般还被描述为DRAM Command Rate、CMD Rate等。由于目前的DDR内存的寻址,先要进行P-Bank的选择(通过DIMM上CS片选信号进行),然后才是L-Bank/行激活与列地址的选择。这个参数的含义就是指在P-Bank选择完之后多少时间可以发出具体的寻址的L-Bank/行激活命令,单位是时钟周期。

SDRAM的时序控制 一、SDRAM的外在物理结构 (1)P-Bank 为保证CPU的正常工作,SDRAM必须一次传输完CPU在一个传输周期内所需要的数据量,也就是CPU数据总线的位宽(bit),这个位宽也就是物理Bank(Physical Bank, P-Bank)的位宽,所以内存需要组成P-Bank来与CPU打交道。 (2)芯片位宽与芯片数量 然而每个内存芯片都有自己的位宽,即每个传输周期能提供的数据量。由于技术要求、成本和实用性等方面限制,内存芯片的位宽一般都小于P-Bank的位宽,这就需要多颗内存芯片并联工作,以提供CPU正常工作时一个传输周期内所需要的数据量。所以,P-Bank实际上就是一组内存芯片的集合,这个集合的位宽总和=P-Bank的位宽=CPU数据位宽,但这个集合的数据容量没有限制。 一个SDRAM只有一个P-Bank已经不能满足容量的需要,所以,多个芯片组可以支持多个P-Bank,一次选择一个P-Bank工作。 (3)SDRAM的封装 SIMM: Single In-line Memory Module,单列内存模组,内存模组就是我们常说的内存条,所谓单列是指模组电路板与主板插槽的接口只有一列引脚(虽然两侧都有金手指pin)DIMM: Double In-line Memory Module, 双列内存模组,所谓双列是指模组电路板与主板插槽的接口有两列引脚,模组电路板的每侧金手指对应一列引脚。 DIMM是SDRAM集合形式的最终体现。前文讲过P-Bank对芯片集合的位宽有要求,对芯片集合的容量则没有任何限制。高位宽的芯片可以让DIMM的设计简单一些(因为所用的芯片少),但在芯片容量相同时,这种DIMM的容量就肯定比不上采用低位宽芯片的模组,因为后者在一个P-Bank中可以容纳更多的芯片。 SDRAM的引脚与封装: 二、SDRAM内部逻辑结构 (1)L-Bank SDRAM的内部实际上是一个存储阵列,就如同表格一样,而每个单元格就称为存储单元,这张表格就成为逻辑Bank(Logical Bank, L-Bank)。考虑到技术、成本、执行效率等方面原因,不可能只需要一个全容量的L-Bank,所以人们在SDRAM内部分割多个L-Bank,目前基本都是4个,内存访问时,一次只能是一个L-Bank。

一种参数,一般存储在内存条的SPD上。2-2-2-8 4个数字的含义依次为:CAS Latency(简称CL值)内存CAS延迟时间,他是内存的重要参数之一,某些牌子的内存会把CL值印在内存条的标签上。RAS-to-CAS Delay(tRCD),内存行地址传输到列地址的延迟时间。Row-precharge Delay(tRP),内存行地址选通脉冲预充电时间。Row-active Delay(tRAS),内存行地址选通延迟。这是玩家最关注的4项时序调节,在大部分主板的BIOS中可以设定,内存模组厂商也有计划的推出了低于JEDEC认证标准的低延迟型超频内存模组,在同样频率设定下,最低“2-2-2-5”这种序列时序的内存模组确实能够带来比“3-4-4-8”更高的内存性能,幅度在3至5个百分点。 在一些技术文章里介绍内存设置时序参数时,一般数字“A-B-C-D”分别对应的参数是“CL-tRCD-tRP-tRAS”,现在你该明白“2-3-3-6”是什么意思了吧?!^_^下面就这几个参数及BIOS设置中影响内存性能的其它参数逐一给大家作一介绍: 一、内存延迟时序“CL-tRCD-tRP-tRAS”的设置 首先,需要在BIOS中打开手动设置,在BIOS设置中找到“DRAM Timing Selectable”,BIOS设置中可能出现的其他描述有:Automatic Configuration、DRAM Auto、Timing Selectable、Timing Configuring By SPD等,将其值设为“Menual”(视BIOS的不同可能的选项有:On/Off 或Enable/Disable),如果要调整内存时序,应该先打开手动设置,之后会自动出现详细的时序参数列表: Command Per Clock(CPC) 可选的设置:Auto,Enable(1T),Disable(2T)。 Command Per Clock(CPC:指令比率,也有翻译为:首命令延迟),一般还被描述为DRAM Command Rate、CMD Rate等。由于目前的DDR内存的寻址,先要进行P-Bank的选择(通过DIMM上CS片选信号进行),然后才是L-Bank/行激活与列地址的选择。这个参数的含义就是指在P-Bank选择完之后多少时间可以发出具体的寻址的L-Bank/行激活命令,单位是时钟周期。 显然,也是越短越好。但当随着主板上内存模组的增多,控制芯片组的负载也随之增加,过短的命令间隔可能会影响稳定性。因此当你的内存插得很多而出现不太稳定的时间,才需要将此参数调长。目前的大部分主板都会自动设置这个参数。 该参数的默认值为Disable(2T),如果玩家的内存质量很好,则可以将其设置为Enable(1T)。 CAS Latency Control(tCL) 可选的设置:Auto,1,1.5,2,2.5,3,3.5,4,4.5。 一般我们在查阅内存的时序参数时,如“3-4-4-8”这一类的数字序列,上述数字序列分别对应的参数是“CL-tRCD-tRP-tRAS”。这个3就是第1个参数,即CL参数。 CAS Latency Control(也被描述为tCL、CL、CAS Latency Time、CAS Timing Delay),CAS latency 是“内存读写操作前列地址控制器的潜伏时间”。CAS控制从接受一个指令到执行指令之间的时间。因为CAS主要控制十六进制的地址,或者说是内存矩阵中的列地址,所以它是最为重要的参数,在稳定的前提下应该尽可能设低。 内存是根据行和列寻址的,当请求触发后,最初是tRAS(Activeto Precharge Delay),预充电后,内存才真正开始初始化RAS。一旦tRAS激活后,RAS(Row Address Strobe )开始进行需要数据的寻址。首先是行地址,然后初始化tRCD,周期结束,接着通过CAS访问所需数据的精确十六进制地址。期间从CAS开始到CAS结束就是CAS延迟。所以CAS是找到数据的最后一个步骤,也是内存参数中最重要的。 这个参数控制内存接收到一条数据读取指令后要等待多少个时钟周期才实际执行该指令。同时该参数也决定了在一次内存突发传送过程中完成第一部分传送所需要的时钟周期数。这个参数越小,则内存的速度越快。必须注意部分内存不能运行在较低的延迟,可能会丢失

内存这样小小的一个硬件,却是PC系统中最必不可少的重要部件之一。而对于入门用户来说,可能从内存的类型、工作频率、接口类型这些简单的参数的印象都可能很模糊的,而对更深入的各项内存时序小参数就更摸不着头脑了。而对于进阶玩家来说,内存的一些具体的细小参数设置则足以影响到整套系统的超频效果和最终性能表现。如果不想当菜鸟的话,虽然不一定要把各种参数规格一一背熟,但起码有一个基本的认识,等真正需要用到的时候,查起来也不会毫无概念。 内存种类 目前,桌面平台所采用的内存主要为DDR 1、DDR 2和DDR 3三种,其中DDR1内存已经基本上被淘汰,而DDR2和DDR3是目前的主流。 DDR1内存 第一代DDR内存 DDR SDRAM 是Double Data Rate SDRAM的缩写,是双倍速率同步动态随机存储器的意思。DDR内存是在SDRAM内存基础上发展而来的,仍然沿用SDRAM生产体系,因此对于内存厂商而言,只需对制造普通SDRAM的设备稍加改进,即可实现DDR内存的生产,可有效的降低成本。 DDR2内存

第二代DDR内存 DDR2 是DDR SDRAM 内存的第二代产品。它在DDR 内存技术的基础上加以改进,从而其传输速度更快(可达800MHZ ),耗电量更低,散热性能更优良。 DDR3内存 第三代DDR内存

DDR3相比起DDR2有更低的工作电压,从DDR2的1.8V降落到1.5V,性能更好更为省电;DDR2的4bit预读升级为8bit预读。DDR3目前最高能够1600Mhz的速度,由于目前最为快速的DDR2内存速度已经提升到800Mhz/1066Mhz的速度,因而首批DDR3内存模组将会从1333Mhz的起跳。 三种类型DDR内存之间,从内存控制器到内存插槽都互不兼容。即使是一些在同时支持两种类型内存的Combo主板上,两种规格的内存也不能同时工作,只能使用其中一种内存。 内存SPD芯片 内存SPD芯片 SPD(Serial Presence Detect): SPD是一颗8针的EEPROM(Electrically Erasable Programmable ROM 电可擦写可编程只读存储器), 容量为256字节,里面主要保存了该内存的相关资料,如容量、芯片厂商、内存模组厂商、工作速度等。SPD的内容一般由内存模组制造商写入。支持SPD的主板在启动时自动检测SPD中的资料,并以此设定内存的工作参数。 启动计算机后,主板BIOS就会读取SPD中的信息,主板北桥芯片组就会根据这些参数信息来自动配置相应的内存工作时序与控制寄存器,从而可以充分发挥内存条的性能。上述情况实现的前提条件是在BIOS设置界面中,将内存设置选项设为“By SPD”。当主板从内存条中不能检测到SPD信息时,它就只能提供一个较为保守的配置。 从某种意义上来说,SPD芯片是识别内存品牌的一个重要标志。如果SPD内的参数值设置得不合理,不但不能起到优化内存的作用,反而还会引起系统工作不稳定,甚至死机。因此,很多普通内存或兼容内存厂商为了避免兼容性问题,一般都将SPD中的内存工作参数设置得较为保守,从而限制了内存性能的充分发挥。更有甚者,一些不法厂商通过专门的读

内存参数的设置正确与否,将极大地影响系统的整体性能。下面我们将针对内存关于时序设置参数逐一解释,以求能让大家在内存参数设置中能有清晰的思路,提高电脑系统的性能。 涉及到的参数分别为: CPC : Command Per Clock tCL : CAS Latency Control tRCD : RAS to CAS Delay tRAS : Min RAS Active Timing tRP : Row Precharge Timing tRC : Row Cycle Time tRFC : Row Refresh Cycle Time tRRD : Row to Row Delay(RAS to RAS delay) tWR : Write Recovery Time ……及其他参数的设置 CPC : Command Per Clock 可选的设置:Auto,Enable(1T),Disable(2T)。 Command Per Clock(CPC:指令比率,也有翻译为:首命令延迟),一般还被描述为DRAM Command Rate、CMD Rate等。由于目前的DDR内存的寻址,先要进行P-Bank的选择(通过DIMM上CS片选信号进行),然后才是L-Bank/行激活与列地址的选择。这个参数的含义就是指在P-Bank选择完之后多少时间可以发出具体的寻址的L-Bank/行激活命令,单位是时钟周期。 显然,CPC越短越好。但当随着主板上内存模组的增多,控制芯片组的负载也随之增加,过短的命令间隔可能会影响稳定性。因此当你的内存插得很多而出现不太稳定的时间,才需要将此参数调长。目前的大部分主板都会自动设置这个参数。 该参数的默认值为Disable(2T),如果玩家的内存质量很好,则可以将其设置为Enable(1T)。 tCL : CAS Latency Control(tCL) 可选的设置:Auto,1,1.5,2,2.5,3,3.5,4,4.5。 一般我们在查阅内存的时序参数时,如“3-4-4-8”这一类的数字序列,上述数字序列分别对应的参数是“CL-tRCD-tRP-tRAS”。这个3就是第1个参数,即CL参数。 CAS Latency Control(也被描述为tCL、CL、CAS Latency Time、CAS Timing Delay),CAS latency是“内存

竭诚为您提供优质文档/双击可除 8086总线时序协议 篇一:8086cpu系统、总线操作和时序 8086cpu系统、总线操作和时序 第一节8086的引脚信号与功能 回顾:8086/8088微型计算机的组成、结构及微机系统的工作过程,微机 系统的存储器组织及相关概念。 本讲重点:8086/8088cpu的两种工作模式, 8086/8088cpu的外部结构,即引 脚信号及其功能。 讲授内容: 一、8086/8088微处理器工作模式及外部结构 1.8086/8088cpu的两种工作模式 为了适应各种使用场合,在设计8088/8086cpu芯片时,就考虑了其应能够使它工作在两种模式下,即最小模式与最大模式。 所谓最小模式,就是系统中只有一个8088/8086微处理器,在这种情况下,所有的总线控制信号,都是直接由

8088/8086cpu产生的,系统中的总线控制逻辑电路被减到最少,该模式适用于规模较小的微机应用系统。 最大模式是相对于最小模式而言的,最大模式用在中、大规模的微机应用系统中,在最大模式下,系统中至少包含两个微处理器,其中一个为主处理器,即8086/8086cpu,其它的微处理器称之为协处理器,它们是协助主处理器工作的。 与8088/8086cpu配合工作的协处理器有两类,一类是 数值协处理器8087另一类是输入/输出协处理器8089。 8087是一种专用于数值运算的协处理器,它能实现多种类型的数值运算,如高精度的整型和浮点型数值运算,超越函数(三角函数、对数函数)的计算等,这些运算若用软件的方法来实现,将耗费大量的机器时间。换句话说,引入了8087协处理器,就是把软件功能硬件化,可以大大提高主处理器的运行速度。 8089协处理器,在原理上有点像带有两个dma通道的处理器,它有一套专门用于输入/输出操作的指令系统,但是8089又和dma控制器不同,它可以直接为输入/输出设备服务,使主处理器不再承担这类工作。所以,在系统中增加8089协处理器之后,会明显提高主处理器的效率,尤其是在输入/输出操作比较频繁 的系统中。 2.8086/8088cpu的引脚信号和功能

BCG矩阵详解 BCG矩阵又称波士顿矩阵,最先由波士顿咨询集团提出,目的是协助企业分析其业务和产品系列的表现,从而协助企业更妥善地分配资源,及作为品牌建立和营销、产品管理、战略管理及公司整体业务的分析工具。BCG矩阵由二乘二方格及对应的横轴纵轴组成,横轴是相对市场占有率,纵轴是销售增长率,方格中间的圆环表示各业务类型可能按圆环方向进行转化。 BCG矩阵 备注:以10%的销售增长率为高低分界,以20%的市场占有率为高低分界。 说明: a)明星类业务 处于成长期,是指处于高增长率、高市场占有率象限内的产品群,这类产品 可能成为企业的现金牛产品,需要加大投资以支持其迅速发展。 发展战略:积极扩大经济规模和市场机会,以长远利益为目标,提高市场占 有率,加强竞争地位。发展战略:产品的管理与组织最好采用事业部形式, 由对生产技术和销售两方面都很内行的经营者负责。 b) c)现金牛业务 处于成熟期,是指低市场成长率、高相对市场份额的业务,这是成熟市场中的领导者,它是企业现金的来源。其财务特点是销售量大,产品利润率高、负债比率低、市场已经成熟,可以为企业提供资金,而且由于增长率低,也无需增大投资。因而成为企业回收

资金,支持其它产品,尤其明星产品投资的后盾。公司应多积累此类业务,以提供稳定的现金流。 发展战略:使所投入资源以达到短期收益最大化为目标。①把设备投资和其它投资尽量压缩;②采用榨油式方法,争取在短时间内获取更多利润,为其它产品提供资金;③对于这一象限内的销售增长率仍有所增长的产品,应进一步进行市场细分,维持现存市场增长率或延缓其下降速度;④对于现金牛产品,适合于用事业部制进行管理,其经营者最好是市场营销型人物。 d)瘦狗业务 处于重启期或衰退期,是指处在低增长率、低市场占有率象限内的产品群。其财务特点是利润率低、处于保本或亏损状态,负债比率高,无法为企业带来收益。 发展战略:采用撤退战略。①应减少批量,逐渐撤退,对那些销售增长率和市场占有率均极低的产品应立即淘汰。②是将剩余资源向其它产品转移。③整顿产品系列,最好将瘦狗产品与其它事业部合并,统一管理。 e)发展类业务 处于发展期,是指处于高增长率、低市场占有率象限内的产品群。市场机会大,前景好,但在在市场营销上存在问题。其财务特点是利润率较低,所需资金不足,负债比率高。例如在产品生命周期中处于引进期、因种种原因未能开拓市场局面的新产品即属此类问题的产品。 发展战略:对问题产品应采取选择性投资战略。①确定对该象限中那些经过改进可能会成为明星的产品进行重点投资,提高市场占有率,使之转变成“明星产品”; ②对其它将来有希望成为明星的产品则在一段时期内采取扶持的对策。对问题产品 的改进与扶持方案一般均列入企业长期计划中。③对问题产品的管理组织,最好是采取智囊团或项目组织等形式,选拔有规划能力,敢于冒风险、有才干的人负责。 波士顿矩阵的应用法则 按照波士顿矩阵的原理,产品市场占有率越高,创造利润的能力越大;另一方面,销售增长率越高,为了维持其增长及扩大市场占有率所需的资金亦越多。这样可以使企业的产品结构实现产品互相支持,资金良性循环的局面。按照产品在象限内的位置及移动趋势的划分,形成了波士顿矩阵的基本应用法则。 第一法则:成功的月牙环 在企业所从事的事业领域内各种产品的分布若显示月牙环形,这是成功企业的象征,因为盈利大的产品不只一个,而且这些产品的销售收入都比较大,还有不少明星产品。问题产品和瘦狗产品的销售量都很少。若产品结构显示的散乱分布,说明其事业内的产品结构未规划好,企业业绩必然较差。这时就应区别不同产品,采取不同策略。