第20章习题 门电路和组合逻辑电路

S10101B

为实现图逻辑表达式的功能,请将TTL 电路多余输入端C 进行处理(只需一种处理方法),Y 1的C 端应接

,Y 2的C 端应接 ,

解:接地、悬空

S10203G

在F = AB +CD 的真值表中,F =1的状态有( )。 A. 2个 B. 4个

C. 3个

D. 7个

解:D

S10203N

某与非门有A 、B 、C 三个输入变量,当B =1时,其输出为( )。 A. 0 B. 1

C. AC

D. AC

解:C

S10204B

在数字电路中,晶体管的工作状态为( )。 A. 饱和 B. 放大

C. 饱和或放大

D. 饱和或截止

解:D

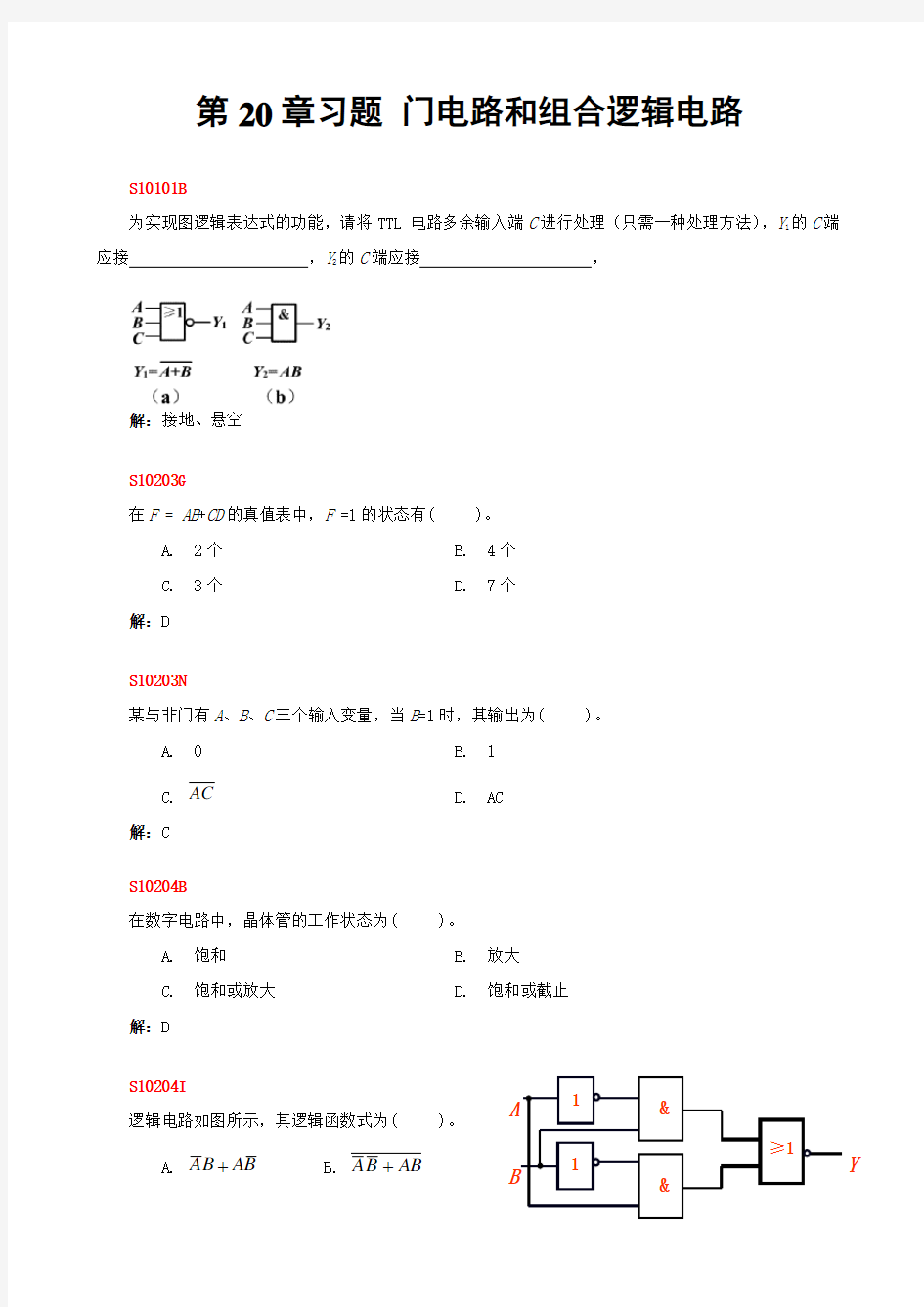

S10204I

逻辑电路如图所示,其逻辑函数式为( )。

A. B A B A +

B. AB B A +

1

&

Y

1

&

≥1

C. B A B A +

D. A AB +

解:C

S10204N

已知F =AB +CD ,选出下列可以肯定使F = 0的情况( )。 A. A = 0,BC = 1

B. B = C = 1

C. C = 1,D = 0

D. AB = 0,CD = 0

解:D

S10110B

三态门电路的三种可能的输出状态是 , , 。 解:逻辑1、逻辑0、高阻态

S10214B

逻辑图和输入A ,B 的波形如图所示,分析当输出F 为“1”的时刻应是( )。

A. t 1

B. t 2

C. t 3

解:A S10211I

图示逻辑电路的逻辑式为( )。 A. F =A B AB + B. B A AB F =

C. F =()A B AB +

解:B S10212I

逻辑电路如图所示,其功能相当于一个( )。

A. 门

B. 与非门

C. 异或门 解:C

S10216B

图示逻辑电路的逻辑式为( )。

A. F =A B +A B

B. F =AB AB +

C. F =AB +A B 解:C

S10217B

逻辑图如图(a )所示,输入A 、B 的波形如图(b ),试分析在t 1瞬间输出F 为( )。

A. “1”

B. “0”

C. 不定 解:B S10218B

图示逻辑符号的逻辑状态表为( )。

A.

B.

C.

解:B

A

B

F

A B

F

A

B

F

0 0 0 0 0 0 0 0 1 0 1 0 0 1 1 0 1 1 1 0 0 1 0 1 1 0 1 1

1

1

1

1

1

1

1

S10219B

逻辑图和输入A的波形如图所示,输出F的波形为( )。解:(b)

S10220B

图示逻辑符号的状态表为( )。

A. B. C.

解:C

S10221B

逻辑图和输入A,B的波形如图所示,分析当输出F为“1”的时刻,应是( )。

A.t1

B.t2

C.t3

解:A

S10225B

逻辑门电路的逻辑符号如图所示,能实现F=AB逻辑功能的是( )。

解:(a)

S10214I

逻辑图和输入A,B的波形如图所示,分析当输出F为""0的时刻应是( )。A.t1

A B F

A B F A B F 000000001 010011011 100101101 111111110

B. t2

C. t3

解:C S10217I

图示逻辑电路的逻辑式为( )。

A. C AB F +=

B. C B A F )(+=

C. C AB F +=

解:A S10221I

逻辑图和输入A ,B 的波形如图所示,分析当输出F 为“0”的时刻应是( )。

A. t 1

B. t 2

C. t 3

解:C S10222I

逻辑图和输入A ,B 的波形如图所示,分析当输出F 为“0”的时刻应是( )。 A. t 1

B. t 2

C. t 3

解:B

S10226B

三态输出“与非”门电路的输出比正常的“与非”门电路多一个状态是( )。 A. 高电平 B. 低电平

C. 高阻

解:C

S10229B

逻辑图和输入A ,B 的波形如图所示,分析当输出F 为“1”的时刻应是( )。

A. t 1

B.

t 2 C.

t 3

解:C

S10209B

逻辑符号如图所示,其中表示“与非”门的是( )。 解:(d )

S10210B

“异或”门的逻辑式为( )。 A. F =AB +AB

B. F =AB +AB

C. F =AB AB +

解:C

S10223I

图示逻辑电路的逻辑式为( )。 A. )(C B A F ?= B. )(C B A F +=

C. BC A F +=

解:A

S10401I

已知各逻辑门输入A 、B 和输出F 的波形如下图所示,要求写出F 的逻辑表达式,并画出逻辑电路。

解

S10503B

写出如图所示电路的输出函数Y 的表达式,并分析逻辑功能。 解:逻辑函数Y 的表达式

ABC Y =1

C

B A AB

C C B A ABC C B A ABC ABC C ABC B ABC A CY BY AY Y +=+++=++=++=++=)()(1

11

列出真值表:

A B C

Y

A B C

Y

0 0 0 1 1 0 0 0 0 0 1 0 1 0 1 0 0 1 0 0 1 1 0 0 0 1 1

1 1 1

1

Y = 1,否则Y = 0。 即该电路具有“判一致”的逻辑功能。

S10504B

证明图(a )、(b )两电路具有相同的逻辑功能。 解:

图(a )逻辑函数Y 的表达式

B A B A Y +=

图(b )逻辑函数Y 的表达式

B

A B A B B B A B A A A B A B A Y +=+++=++=))((

可见,两电路具有“异或”的逻辑功能。

S10505G

为提高报警信号的可靠性,在有关部位安置了3个同类型的危险报警器,只有当3个危险报警器中至少有两个指示危险时,才实现关机操作。试画出具有该功能的逻辑电路。

解:在危急情况下,报警信号A 、B 、C 为高电平1,且当输出状态F 为高电平1

时,设备应关机。其真值表如下:

由真值表可写出“与或”表达式:

ABC BC A C B A C AB L +++=

化简为:AC BC AB L ++= 逻辑图,如下图所示。 或者:用与非门

AC BC AB L ++=

=AC BC AB ++=AC BC AB ??其逻辑电路略。

S10504N

某设备有开关A 、B 、C ,要求:只有开关A 接通的条件下,开关B 才能接通;开关C 只有在开关B 接通的条件下才能接通。违反这一规程,则发出报警信号。设计一个由“与非门”组成的能实现这一功能的报警控制电路。

解:

由题意可知,该报警电路的输入变量是三个开关A 、B 、C 的状态,设开关接通用1表示,开关断开用0表示;设该电路的输出报警信号为F ,F 为1表示报警,F 为0表示不报警。可列出真值表:

根据真值表做出卡诺图如下图(a )所示。利用卡诺图对逻辑函数进行化简,得到最简逻辑表达式:

C B B A C B B A F ?=+=

根据逻辑表达式画出逻辑图,就得到题目所要求的控制电路如图(b )所示。

S10405G

可否将“与非门”、“或非门”、“异或门”当做“反相器”使用如果可以,其输入端应如何处理并画出电路图。

C B A

L

0 0 0 0 0 1 0 1 0 0 1 1 1 0 0 1 0 1 1 1 0 1 1 1

0 0 0 1 0 1 1 1

A B C

F

0 0 0 0 0 1 0 1 0 0 1 1 1 0 0 1 0 1 1 1 0 1 1 1

0 1 1 1 0 1 0 0

解:

如右图所示。

组合逻辑电路的设计步骤为:

(1) ;(2) ;(3)简化和变换逻辑表达式,从而画出逻辑图。

解:

⑴由电路的功能要求,列出真值表;(2)由真值表写出逻辑表达式;

S11102B

分析组合逻辑电路的步骤为:

(1) ; (2) ; (3) ;

(4)根据真值表和逻辑表达对逻辑电路进行分析,最后确定其功能。 解:

由逻辑图写出个输出端逻辑表达式、化简和变换各逻辑表达式、列出真值表

S11102I

如图所示逻辑图,逻辑表达式1F = ;

F = 。

解:

01101==??=A F ;B B F F =+=1

S11201I

如图所示逻辑电路其逻辑表达式为( )。 A. B A Y += B. ))((B A B A Y +?= C. ()B A Y ?=

D. ()()B A B A Y +??=

解:D

组合逻辑电路任何时刻的输出信号与该时刻的输入信号( ),与电路原来所处的状态( )。

A. 无关,无关

B. 无关,有关

C. 有关,无关

D. 有关,有关

解:C

S11202I

半加器的本位和输出端的逻辑关系是( )。

A. 与非

B. 或非

C. 与或非

D. 异或

解:D

已知CD ABC F +=选出下列可以肯定使0=F 的情况是( )。 A. 1,0==BC A B. 1,1==C B C. 0,1==D C D. 1,1==D BC

E. 0,1==CD AB

解:D

S11203N

图示为一简单的编码器,其中E 、F 、G 是一般信号,A 、B 是输出量,为二进制代码变量。今令 AB = 10 ,则输入的信号为1的是( )。

A. E

B. F

C. G

解:B

S11301B

编码器,译码器,数据选择器都属于组合逻辑电路。( ) 解:√

S11301N

全加器的输出不仅取决于输入,同时还取决于相邻低位的进位,因此说全加器属于时序逻辑电路。( )

解:×

S11302B

用二进制代码表示某一信息称为编码。反之把二进制代码所表示的信息翻译出来称为译码。( ) 解:√

S11302G

在下列电路中,试问哪些电路能实现B A Y ⊕=的逻辑关系 解:

A.√、

B.×、

C.×

S11102G

一个三变量排队电路,在同一时刻只有一个变量输出,若同时有两个或两个以上变量为1时,则按A 、

B 、

C 的优先顺序通过,若F A =1表示A 通过,F B 、F C 为1表示B 、C 通过,F A 、F B 、F C 为0时表示其不通过,

则表示变量A 、B 、C 通过的表达式:

F A = ,F B = ,F C = 。

解:A 、B A 、C B A

S11213B

半加器逻辑符号如图所示,当A “0”,B “0”时,C 和S 分别为( )。

A. 0=C 、1=S

B. 1=C 、0=S

C. 0=C 、0=S 解:C

S11218B

半加器的逻辑图如下,指出它的逻辑式为( )。 A. B A S ⊕=、AB C = B. B A B A S +=、B A C =

C. B A S ⊕=、AB C =

解:A

S11219B

全加器逻辑符号如图所示,当A i =“1”,B i =“1”,C i-1=“1”时,C i 和S i 分别为( )。

A. C i = 1 、S i = 0

B. C i = 0 、S i = 1

C. C i = 1 、S i = 1

解:C

S11207B

全加器逻辑符号如图所示,当A i =“1”,B i =“1”,C i-1=“0”时,C i 和S i 分别为( )。

A. C i = 0、S i =0

B. C i =1、S i =1

C. C i =1、S i =0 解:C

S11206B

半加器逻辑符号如图所示,当A “1”,B “1”时,C 和S 分别为( )。

A. C = 0、S = 0

B. C = 0、S = 1

C. C = 1、S = 0 解:C

S11403B

设计一个半加器电路(要求:列出真值表,写出逻辑式,画出逻辑电路)。 解:

由半加器概念即只考虑两个一位二进制数A 和B 相加,不考虑低

位来的进位数称半加:

列出半加器真值表(a ),其中,S 为本位和数,C 为向高位送出进位数由真值表可直接得出逻辑式:

B A B A S +=、B A

C ?= 由逻辑式可画出逻辑电路(b )。

S11220B

图示逻辑电路的逻辑式为( )。 A. =F A B C ++ B. =F A B C ++

C. C B A F =

解:C

S11213I

逻辑电路如图所示,其逻辑功能相当于一个( )。 A. “与”非门 B. “异或”门

C. “与或非”门

解:C

S11404I

写出图中所示电路的最简“与或”表达式。

解:

F = AB A C AB B AB A AB A C AB B AB A +??=???

= BC A B A B A BC A C B A +=++

S11501B

写出如图所示电路的逻辑表达式,并将其化简再用最简单的组合电路实现之。

解:

+

=

+

+

=

=

+

=

?

(

)

(

(

=)

+

?

B Y⊕

A

B

A

B

A

A

B AB

B

AB

A

A

B

AB

B

A

最简电路如下图所示。

S11501G

组合逻辑电路设计:

某产品有A 、B 、C 、D 四项质量指标,A 为主要指标。检验合格品时,每件产品如果有包含主要指标A 在内的三项或三项以上质量指标合格则为正品,否则即为次品。试设计一个全部用“与非门”组成的结构最简的正品检验机。

解:

(1)对于A 、B 、C 、D 中任何指标,合格时用1表示,不合格时用0表示,检验结果正品用1表示,次品用0表示,列真值表如(a )。

(2)化简

作卡诺图(b ),得表达式:

ABC ACD ABD ABC

ACD ABD Y ??=++=

(3)逻辑电路如图(c )。

S11502G

用“与非门”设计一组合逻辑电路,输入为四位二进制数,当数9≥N 时,输出1=L ,其余情况0=L 。

解:

AD

AC AB AD AC AB L D C B A L m ??=++==∑)

,15,14,13,12,11,10,9(),,,(

S11405I

有一个能将两个一位二进制数A 、B 进行比较的数字比较器,其逻辑状态列于下表中。试写出各输出的逻辑式,并画出逻辑图。

输 入 输 出

A B Y 1(A >B ) Y 1(A <B ) Y 1(A =B )

解:

填写真值表:

输入输出

A B Y1(A>B) Y1(A<B) Y1(A=B)

0 0

0 1

1 0 1 10 0 1

0 1 0

1 0 0 0 0 1

B

A

Y=

1,

B

A

Y=

2,

B

A

AB

Y+

=

3

逻辑图如右图所示。

组合逻辑电路的分析(大题)一.目的 由逻辑图得出逻辑功能 二.方法(步骤) 1.列逻辑式: 由逻辑电路图列输出端逻辑表达式; (由输入至输出逐级列出) 2.化简逻辑式: 代数法、卡诺图法; (卡诺图化简步骤保留) 3.列真值表: 根据化简以后的逻辑表达式列出真值表;4.分析逻辑功能(功能说明): 分析该电路所具有的逻辑功能。 (输出与输入之间的逻辑关系); (因果关系) (描述函数为1时变量取值组合的规律) 技巧:先用文字描述真值表的规律(即叙述函数值为1时变量组合所有的取值),然后总结归纳电路实现的具体功能。

5.评价电路性能。三.思路总结: 组合逻辑 电路逻辑表达式最简表达式真值表逻辑功能化简 变换 四.注意: 关键:列逻辑表达式; 难点:逻辑功能说明 1、逻辑功能不好归纳时,用文字描述真值表的规律。(描述函数值为1时变量组合所有的取值)。 2、常用的组合逻辑电路。 (1)判奇(偶)电路; (2)一致性(不一致性)判别电路; (3)相等(不等)判别电路; (4)信号有无判别电路; (5)加法器(全加器、半加器); (6)编码器、优先编码器; (7)译码器; (8)数值比较器; (9)数据选择器; (10)数据分配器。

3、多输出组合逻辑电路判别: 1)2个输出时考虑加法器:2输入半加;3输入全加。 2)4输出时考虑编码器:4输入码型变换;编码器。 五.组合逻辑电路分析实例 例1 电路如图所示,分析电路的逻辑功能。 A B Y 解: (1)写出输出端的逻辑表达式:为了便于分析可将电路自左至右分三级逐级写出Z1、Z2、Z3和Y的逻辑表达式为:

第六章组合逻辑电路 一、概述 1、组合逻辑电路的概念 数字电路根据逻辑功能特点的不同分为: 组合逻辑电路:指任何时刻的输出仅取决于该时刻输入信号的组合,而与电路原有的状态无关的电路。 时序逻辑电路:指任何时刻的输出不仅取决于该时刻输入信号的组合,而且与电路原有的状态有关的电路。 2、组合逻辑电路的特点 逻辑功能特点:没有存储和记忆作用。 组成特点:由门电路构成,不含记忆单元,只存在从输入到输出的通路,没有反馈回路。 3、组合逻辑电路的描述 4、组合逻辑电路的分类 按逻辑功能分为:编码器、译码器、加法器、数据选择器等; 按照电路中不同基本元器件分为:COMS、TTL等类型; 按照集成度不同分为:SSI、MSI、LSI、VLSI等。 二、组合逻辑电路的分析与设计方法 1、分析方法 根据给定逻辑电路,找出输出输入间的逻辑关系,从而确定电路的逻辑功能,其基本步骤为: a、根据给定逻辑图写出输出逻辑式,并进行必要的化简; b、列出函数的真值表; c、分析逻辑功能。 2、设计方法 设计思路:分析给定逻辑要求,设计出能实现该功能的组合逻辑电路。 基本步骤:分析设计要求并列出真值表→求最简输出逻辑式→画逻辑图。 首先分析给定问题,弄清楚输入变量和输出变量是哪些,并规定它们的符号与逻辑取值(即规定它们何时取值0 ,何时取值1) 。然后分析输出变量和输入变量间的逻辑关系,列出真值表。根据真值表用代数法或卡诺图法求最简与或式,然后根据题中对门电路类型的要求,将最简与或式变换为与门类型对应的最简式。

三、若干常用的组合逻辑电路 (一)、编码器 把二进制码按一定规律编排,使每组代码具有特定的含义,称为编码。具有编码功能的逻辑电路称为编码器。 n 位二进制代码有n 2种组合,可以表示n 2个信息;要表示N 个信息所需的二进制代码应满足n 2≥ N 。 1、普通编码器 (1)、二进制编码器 将输入信号编成二进制代码的电路。下面以3位二进制编码器为例分析普通编码器的工作原理。 3位二进制编码器的输入为70~I I 共8个输入信号,输出是3位二进制代码012Y Y Y ,因此该电路又称8线-3线编码器。它有以下几个特征: a 、将70~I I 8个输入信号编成二进制代码。 b 、编码器每次只能对一个信号进行编码,不允许两个或两个以上的信号同时有效。 c 、设输入信号高电平有效。 由此可得3位二进制编码器的真值表如右图所示,那么由真值表可知: 765476542I I I I I I I I Y =+++= 763276321I I I I I I I I Y =+++= 753175310I I I I I I I I Y =+++= 进而得到其逻辑电路图如下:

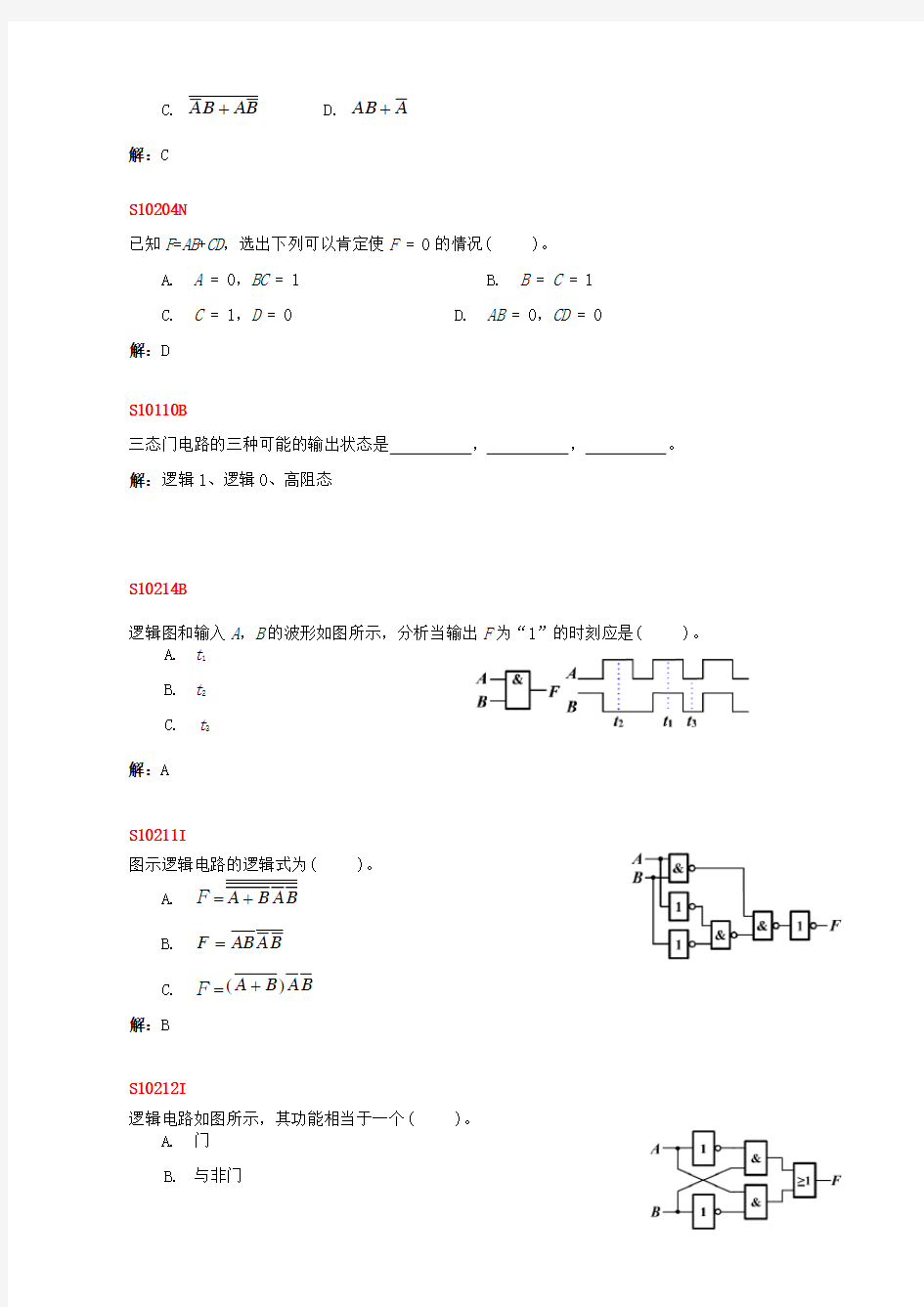

第20章习题 门电路和组合逻辑电路 S10101B 为实现图逻辑表达式的功能,请将TTL 电路多余输入端C 进行处理(只需一种处理方法),Y 1的C 端应接 ,Y 2的C 端应接 , 解:接地、悬空 S10203G 在F = AB +CD 的真值表中,F =1的状态有( )。 A. 2个 B. 4个 C. 3个 D. 7个 解:D S10203N 某与非门有A 、B 、C 三个输入变量,当B =1时,其输出为( )。 A. 0 B. 1 C. AC D. AC 解:C S10204B 在数字电路中,晶体管的工作状态为( )。 A. 饱和 B. 放大 C. 饱和或放大 D. 饱和或截止 解:D S10204I 逻辑电路如图所示,其逻辑函数式为( )。 A. B A B A + B. AB B A + C. B A B A + D. A AB + 解:C S10204N 已知F =AB +CD ,选出下列可以肯定使F = 0的情况( )。 A. A = 0,BC = 1 B. B = C = 1 C. C = 1,D = 0 D. AB = 0,CD = 0 解:D S10110B 三态门电路的三种可能的输出状态是 , , 。 解:逻辑1、逻辑0、高阻态 1 & B 1 & ≥1

逻辑图和输入A ,B 的波形如图所示,分析当输出F 为“1”的时刻应是( )。 A. t 1 B. t 2 C. t 3 解:A S10211I 图示逻辑电路的逻辑式为( )。 A. F =A B AB + B. B A AB F = C. F =()A B AB + 解:B S10212I 逻辑电路如图所示,其功能相当于一个( )。 A. 门 B. 与非门 C. 异或门 解:C S10216B 图示逻辑电路的逻辑式为( )。 A. F =A B +A B B. F =AB AB + C. F =AB +A B 解:C S10217B 逻辑图如图(a )所示,输入A 、B 的波形如图(b ),试分析在t 1瞬间输出F 为( )。 A. “1” B. “0” C. 不定 解:B S10218B 图示逻辑符号的逻辑状态表为( )。 A. B. C. 解:B A B F A B F A B F 0 0 0 0 0 0 0 0 1 0 1 0 0 1 1 0 1 1 1 0 0 1 0 1 1 0 1 1 1 1 1 1 1 1 1

第10章组合逻辑电路 一、基本要求 1.掌握组合电路的特点及其分析方法和设计方法; 2.理解几种常用的组合逻辑电路及其中规模器件的功能并掌握使用方法; 3.了解组合逻辑电路中的竟争——冒险现象。 二、阅读指导 1、组合逻辑电路的特点 组合逻辑电路在逻辑功能上的特点是电路任意时刻的输出状态,只取决于该时刻的输入状态,而与该时刻之前的电路输入状态和输出状态无关。 组合逻辑电路在结构上的特点是不含有具有存储功能的电路。可以由逻辑门或者由集成组合逻辑单元电路组成,从输出到各级门的输入无任何反馈线。 组合逻辑电路的输出信号是输入信号的逻辑函数。这样,逻辑函数的四种表示方法,都可以用来表示组合逻辑电路的功能。 2、组合逻辑电路的分析 组合逻辑电路的分析就是根据给定的逻辑电路,通过分析找出电路的逻辑功能,或是检验所设计的电路是否能实现预定的逻辑功能,并对功能进行描述。其一般步骤为:(1)根据逻辑图写出输出逻辑函数表达式 由输入端逐级向后推(或从输出向前推到输入),写出每个门的输出逻辑函数表达式,最后写出组合电路的输出与输入之间的逻辑表达式。有时需要对函数式进行适当的变换,以使逻辑关系简单明了。 (2)列出真值表 列出输入逻辑变量全部取值组合,求出对应的输出取值,列出真值表。 (3)说明电路的逻辑功能 根据逻辑表达式或真值表确定电路的逻辑功能,并对功能进行描述。 3、组合逻辑电路的设计 根据给定的逻辑功能要求,设计出能实现这一功能要求的最简组合逻辑电路,就是设计组合逻辑电路的任务。 在设计组合逻辑电路时,电路的最简是我们追求的目标之一。电路的“最简”含意是指所用器件数最少、器件的品种最少、器件间的连线也最少。 组合逻辑电路设计的一般步骤如下: (1)进行逻辑规定 根据设计要求设计逻辑电路时,首先应分析事件的因果关系,确定输入与输出逻辑变量,并规定变量何时取1何时取0,即所谓逻辑状态赋值。 (2)列真值表并写出逻辑函数式 根据输入、输出之间的因果关系,列出真值表。至此,便将一个具有因果关系的事件表示为逻辑函数,并且是以真值表的形式给出。 真值表中输出为1时所对应的各最小项之和就是输出逻辑函数式。 (3) 对输出逻辑函数式化简

第七章门电路与组合逻辑电路 习题一 一、选择题 1. 三态门输出高阻状态时,是正确的说法。 A.用电压表测量指针不动 B.相当于悬空 C.电压不高不低 D.测量电阻指针不动 2. 以下电路中可以实现“线与”功能的有。 A.与非门 B.三态输出门 C.集电极开路门 D.漏极开路门 3.以下电路中常用于总线应用的有。 A.T S L门 B.O C门 C.漏极开路门 D.C M O S与非门 4.逻辑表达式Y=A B可以用实现。 A.正或门 B.正非门 C.正与门 D.负或门 5.T T L电路在正逻辑系统中,以下各种输入中相当于输入逻辑“1”。 A.悬空 B.通过电阻 2.7kΩ接电源 C.通过电阻 2.7kΩ接地 D.通过电阻510Ω接地 6.对于T T L与非门闲置输入端的处理,可以。 A.接电源 B.通过电阻3kΩ接电源 C.接地 D.与有用输入端 并联 7.要使T T L与非门工作在转折区,可使输入端对地外接电阻R I。 A.>R O N B.<R O F F C.R O F F<R I<R O N D.>R O F F 8.三极管作为开关使用时,要提高开关速度,可。 A.降低饱和深度 B.增加饱和深度 C.采用有源泄放回路 D.采用抗饱和三极管 9.C M O S数字集成电路与T T L数字集成电路相比突出的优点是。 A.微功耗 B.高速度 C.高抗干扰能力 D.电源范围宽 10.与C T4000系列相对应的国际通用标准型号为。 A.C T74S肖特基系列 B.C T74L S低功耗肖特基系列 C.C T74L低功耗系列 D.C T74H高速系列 二、判断题(正确打√,错误的打×) 1.TTL与非门的多余输入端可以接固定高电平。() 2.当TTL与非门的输入端悬空时相当于输入为逻辑1。() 3.普通的逻辑门电路的输出端不可以并联在一起,否则可能会损坏器件。() 4.两输入端四与非门器件74LS00与7400的逻辑功能完全相同。() 5.CMOS或非门与TTL或非门的逻辑功能完全相同。()

第九章 门电路及组合逻辑电路 一、填空题 1、模拟信号的特点是在 和 上都是 变化的。(幅度、时间、连续) 2、数字信号的特点是在 和 上都是 变化的。(幅度、时间、不连续) 3、数字电路主要研究 与 信号之间的对应 关系。(输出、输入、逻辑) 4、最基本的三种逻辑运算是 、 、 。(与、或、非) 5、逻辑等式三个规则分别是 、 、 。(代入、对偶、反演) 6、逻辑函数常用的表示方法有 、 和 。(真值表、表达式、卡诺图、逻辑图、波形图五种方法任选三种即可) 7、半导体二极管具有 性,可作为开关元件。(单向导电) 8、半导体二极管 时,相当于短路; 时,相当于开路。(导通、截止) 9、半导体三极管作为开关元件时工作在 状态和 状态。(饱和、截止) 10、在逻辑门电路中,最基本的逻辑门是 、 和 。(与门、或门、非门) 11、与门电路和或门电路具有 个输入端和 个输出端。(多、一) 12、非门电路是 端输入、 端输出的电路。(单、单) 13、根据逻辑功能的不同特点,逻辑电路可分为两大类: 和 。(组合逻辑电路、时序逻辑电路) 14、组合逻辑电路主要是由 、 和 三种基本逻辑门电路构成的。(与门、或门、非门) 15、(1)2(10011011)(= 8)(= 16) 答:233、9B (2)16()(AE = 2)(= 8) 答:10101110、256 (3)()125(10= 2) (4)()375.13(10= 2) 答:(1)1111101(2)1101.011 二、判断题 1、十进制数74转换为8421BCD 码应当是BCD 8421)01110100(。 (√) 2、十进制转换为二进制的时候,整数部分和小数部分都要采用除2取余法。(╳) 3、若两个函数相等,则它们的真值表一定相同;反之,若两个函数的真值表完全相同,则这两个函数未必相等。(╳)

第三章组合逻辑电路 基本要求: 熟练掌握组合逻辑电路的分析方法;掌握组合逻辑电路的设计方法;理解全加器、译码器、编码器、数据选择器、数据比较器的概念和功能,并掌握它们的分析与实现方法;了解组合逻辑电路中的险象 本章主要内容:组合逻辑电路的分析方法和设计方法。 本章重点: 组合逻辑电路的分析方法 组合逻辑电路的设计方法 常用逻辑部件的功能 本章难点: 组合逻辑电路的设计 一、组合逻辑电路的特点 若一个逻辑电路,在任一时刻的输出仅取决于该时刻输入变量取值组合,而与电路以前的状态无关,则电路称为组合逻辑电路(简称组合电路)。可用一组逻辑函数描述。 组合电路根据输出变量分为单输出组合逻辑电路和多输出组合逻辑电路。 注意:1.电路中不存在输出端到输入端的反馈通路。 2.电路不包含记忆元件。 3.电路的输出状态只由输入状态决定。 二、组合逻辑电路的分析方法 分析的含义:给出一个组合逻辑电路,分析它的逻辑功能。 分析的步骤: 1.根据给出的逻辑电路图,逐级推导,得到输出变量相对于

输入变量的逻辑函数。 2.对逻辑函数化简。 3.由逻辑函数列出对应的真值表。 4.由真值表判断组合电路的逻辑功能。 三、组合电路的分析举例 1、试分析图3-1所示的单输出组合逻辑电路的功能 解:(1)由G1、G2、G3各个门电路的输入输出关系,推出整个电路的表达式: Z1=ABC F=Z1+Z2 (2)对该逻辑表达式进行化简: (3)根据化简后的函数表达式,列出真值表3-1。 (4)从真值表中可以看出:当A、B、C三个输入一致时(或者全为“0”、或者全为“1”),输出才为“1”,否则输出为“0”。所以,这个组合逻辑电路具有检测“输入不一致”的功能,也称为“不一致电路”。

第十六章 门电路和组合逻辑电路 一 选择题 1、下列逻辑表达式正确的是( )。 .0A A A += .11B A ?= .C A AB A B +=+ .D A AB AB += 2、时序逻辑电路中,以下说法正确的是( )。 A 、电路中任意时刻的输出只取决于当时的输入信号,与电路原来的 状态无关。 B 、电路中任意时刻的输出不仅与当时的输入信号有关,同时还取决于 电路原来的状态。 C 、电路中任意时刻的输出只取决于电路原来的状态,与当时的输入 信号无关。 D 、以上均不正确。 3、数据选择器的地址输入端有2个时,最多可以有( )个数据信号 输入。 A 、1 B 、2 C 、4 D 、8 4、数据选择器的地址输入端有3个时,最多可以有( )个数据信号输入。 A 、4 B 、6 C 、8 D 、16 5、组合逻辑电路中,以下说法正确的是( )。 A 、电路中任意时刻的输出只取决于当时的输入信号,与电路原来的状态无关。 B 、电路中任意时刻的输出不仅与当时的输入信号有关,同时还取决于电路原来的状态。 C 、电路中任意时刻的输出只取决于电路原来的状态,与当时的输入信号无关。 D 、以上均不正确。 6、下列几种TTL 电路中,输出端可实现线与功能的电路是( )。 A 、或非门 B 、与非门 C 、异或门 D 、OC 门 7、数据选择器有10个数据信号输入端时,至少得有( )个地址输入端。 A 、2 B 、3 C 、4 D 、5 8、以下哪个电路不是组合逻辑电路( )。 A 、编码器 B 、计数器 C 、译码器 D 、加法器

9、下列逻辑表达式正确的是( )。 .0A A A += .11B A ?= .C A AB A B +=+ .D A AB AB += 10、衡量集成逻辑电路优劣的因数是用它的:( ) A .增益×带宽; B .传输延迟时间×功耗; C .扇出系数×传输延迟时间; D .噪声容限×功耗。 11、以下诸论述中,唯一正确的是:( ) A .可以用OC 门构成电平变换电路; B .ECL 门电路主要用于集成度要求高的场合; C .CM0S 器件不可以和TTL 器件兼容; D .CMOS 器件的电源电压使用范围特别小,对电源的准确性要求严格. 12、集成门电路(不论是与、或、与非…等)的输入端若超过了需要,则这些多余的输入端应按哪种方式去处置才是正确的?( ) A .让它们开路; B .让它们通过电阻接最高电平(例如电源电压); C .让它们接地,或接电源的最低电平; D .让它们和使用中的输入端并接。 13、 以下表达式中符合逻辑运算法则的是( ) A.C ·C=C 2 B.1+1=10 C.0<1 D.A+1=1 14、 当逻辑函数有n 个变量时,共有( )个变量取值组合? A. n B. 2n C. n 2 D. 2n 15、. 逻辑函数的表示方法中具有唯一性的是( ) A .真值表 B.表达式 C.逻辑图 D.卡诺图 16、F=A B +BD+CDE+A D=( ) A.D B A + B.D B A )(+ C.))((D B D A ++ D.))((D B D A ++ 二 填空题 1.电子电路按功能可分为 电路和 电路。 2.根据电路的结构特点及其对输入信号响应规则的不同,数字电路可分为 和 。 3.数字电路的分析方法主要用 、功能表、 、波形图。 4.数字信号是一系列时间和数值都 的信号。 5.在数字电路中有两种数字逻辑状态分别是逻辑 和逻辑 。 6.逻辑函数F=)(B A A ⊕⊕ =

第九章门电路及组合逻辑电路 一、填空题 1、 模拟信号的特点是在 ______ 和 ______ 上都是 __________ 变化的。(幅度、时间、连续) 2、 数字信号的特点是在 ______ 和 ______ 上都是 __________ 变化的。(幅度、时间、不连续) 3、 数字电路主要研究 ______ 与 ______ 信号之间的对应 ________ 关系。(输出、输入、逻辑) 4、 最基本的三种逻辑运算是 _______ 、 ________ 、 _________ 。(与、或、非) 5、 逻辑等式三个规则分别是 _______ 、 ________ 、 _________ 。(代入、对偶、反演) 6 逻辑函数常用的表示方法有 _________ 、 ________ 和 __________ o (真值表、表达式、卡诺图、逻 辑图、波形图五种方法任选三种即可) 7、 半导体二极管具有 ______ 性,可作为开关元件。(单向导电) 8、 半导体二极管 __________ 时,相当于短路; ______ 时,相当于开路。(导通、截止) 9、 半导体三极管作为开关元件时工作在 __________ 状态和 ___________ 状态。(饱和、截止) 10、 在逻辑门电路中,最基本的逻辑门是 _____ 、 ______ 和 ______ o (与门、或门、非门) 11、 与门电路和或门电路具有 _____ 个输入端和 _____ 个输出端。(多、一) 12、 非门电路是 ___ 端输入、 _______ 端输出的电路。(单、单) 13、 根据逻辑功能的不同特点,逻辑电路可分为两大类: _________ 和 ________ 。(组合逻辑电路、 、判断题 1、十进制数74转换为8421BC [码应当是(01110100) 8421 BCD 。 (V ) 2、 十进制转换为二进制的时候,整数部分和小数部分都要采用除 2取余法。(X ) 3、 若两个函数相等,贝尼们的真值表一定相同;反之,若两个函数的真值表完全相同,贝U 这两个 函数未必相等。(X ) 4、 证明两个函数是否相等,只要比较它们的真值表是否相同即可。 (V ) 时序逻辑电路) 14、组合逻辑电路主要是由 ____ 、 ____ 和 15、 (1) (10011011)2 ( )8 ( (2) (AE )16 ( ) 2 ( )8 (3) (125)10 ( ) 2 (4) (13.375)10 ( )2 答:(1) _三种基本逻辑门电路构成的。(与门、或门、非门) )16 答:233、9B 答:10101110 256 1111101 (2) 1101.011

20章 组合电路 20-0XX 选择与填空题 20-1XX 画简题 20-2XX 画图题 20-3XX 分析题 20-XX 设计题 十二、[共8分]两个输入端的与门、 或门和与非门的输入波形如图 12 所示, 试画出其输出信号的波形。 解: 设与门的输出为F 1, 或门的输出为F 2,与非门的输出为F 3,根据逻辑关系其输出波形如图所示。 20-0XX 选择与填空题 20-001试说明能否将与非门、或非门、异或门当做反相器使用?如果可以,其他输入端应如何连接? 答案 与非门当反相器使用时,把多余输入端接高电平 或非门当反相器使用时,把多余输入端接低电平 异或门当反相器使用时,把多余输入端接高电平 20-002、试比较TTL 电路和CMOS 电路的优、缺点。 A B F 1F 2F 3 (a) (b)

答案 COMS 电路抗干扰能力强,速度快,静态损耗小,工作电压范围宽, 有取代TTL 门电路的趋势。 20-003简述二极管、三极管的开关条件。 答案 二极管:加正向电压导通,相当于开关闭合;反向电压截止,相当于 开关断开。三极管:U BE <0V 时,三极管可靠截止,相当于开关断开; i B 》I BS 时,三极管饱和,相当于开关闭合。 20-0004、同或运算关系,当两输入不相等时,其输出为1;异或运算关系,当两输入相等时,其输出为0; 20-0005、 若各门电路的输入均为A 和B ,且A=0,B=1;则与非门的输出为 _________,或非门的输出为___ ___,同或门的输出为__ __。 20-0006、逻辑代数中有3种基本运算: 、 和 。 A. 或非,与或,与或非 B. 与非,或非,与或非 C. 与非,或,与或 D. 与,或,非 20-0007、逻辑函数有四种表示方法,它们分别是( )、( )、( )和( )。 20-0008、将2004个“1”异或起来得到的结果是( )。 20-0009、是8421BCD 码的是( )。 A 、1010 B 、0101 C 、1100 D 、1101 2)、和逻辑式BC A A + 相等的是( )。 A 、ABC B 、1+B C C 、A D 、BC A + 3)、二输入端的或非门,其输入端为A 、B ,输出端为Y ,则其表达式 Y= ( )。 A 、A B B 、AB C 、B A + D 、A+B 20-0010、若在编码器中有50个编码对象,则要求输出二进制代码位数为 位。 A.5 B.6 C.10 D.50

组合逻辑电路的分析与设计 实验报告 院系:电子与信息工程学院班级:电信13-2班 组员姓名: 一、实验目的 1、掌握组合逻辑电路的分析方法与测试方法。 2、掌握组合逻辑电路的设计方法。 二、实验原理 通常逻辑电路可分为组合逻辑电路和时序逻辑电路两大类。电路在任何时刻,输出状态只取决于同一时刻各输入状态的组合,而与先前的状态无关的逻辑电路称为组合逻辑电路。 1.组合逻辑电路的分析过程,一般分为如下三步进行:①由逻辑图写输出端的逻辑表达式;②写出真值表;③根据真值表进行分析,确定电路功能。 2.组合逻辑电路一般设计的过程为图一所示。 图一组合逻辑电路设计方框图 3.设计过程中,“最简”是指按设计要求,使电路所用器件最少,器件的种类最少,而且器件之间的连线也最少。 三、实验仪器设备 数字电子实验箱、电子万用表、74LS04、74LS20、74LS00、导线若干。 74LS00 74LS04 74LS20 四、实验内容及方法

1 、设计4线-2线优先编码器并测试其逻辑功能。 数字系统中许多数值或文字符号信息都是用二进制数来表示,多位二进制数的排列组合叫做代码,给代码赋以一定的含义叫做编码。 (1)4线-2线编码器真值表如表一所示 4线-2线编码器真值表 (2)由真值表可得4线-2线编码器最简逻辑表达式为 Y=((I0′I1′I2I3′)′(I0′I1′I2′I3)′)′ 1 Y=((I0′I1I2′I3′)′(I0′I1′I2′I3)′)′ (3)由最简逻辑表达式可分析其逻辑电路图 4线-2线编码器逻辑图 (4)按照全加器电路图搭建编码器电路,注意搭建前测试选用的电路块能够正常工作。 (5)验证所搭建电路的逻辑关系。 I=1 1Y0Y=0 0 1I=1 1Y0Y=0 1 I=1 1Y0Y=1 0 3I=1 1Y0Y=1 1 2 2、设计2线-4线译码器并测试其逻辑功能。 译码是编码的逆过程,它能将二进制码翻译成代表某一特定含义的号.(即电路的某种状态),具有译码功能的逻辑电路称为译码器。 (1)2线-4线译码器真值表如表二所示

第三章组合逻辑电路的分析和设计 [教学要求] 1.掌握逻辑代数的三种基本运算、三项基本定理、基本公式和常用公式; 2.掌握逻辑函数的公式化简法和卡诺图化简法; 3.了解最小项、最大项、约束项的概念及其在逻辑函数化简中的使用。 4.掌握组合逻辑电路的分析和设计方法; 5.了解组合电路中的竞争和冒险现象、产生原因及消除方法。 [教学内容] 1.逻辑代数的三种基本运算、三项基本定理、基本公式和常用公式 2.逻辑函数的公式化简法和卡诺图化简法 3.最小项、最大项、约束项的概念及其在逻辑函数化简中的使用 4.组合逻辑电路的分析方法 5.组合逻辑电路的设计方法 6.组合电路中的竞争和冒险现象、产生原因及消除方法 组合逻辑电路――在任何时刻,输出状态只决定于同一时刻各输入状态的组合,而和先前状态无关的逻辑电路。 组合逻辑电路具有如下特点: (1)输出、输入之间没有反馈延迟通路; (2)电路中不含记忆单元。 3.1 逻辑代数 逻辑代数是分析和设计逻辑电路不可缺少的数学工具。逻辑代数提供了一种方法,即使用二值函数进行逻辑运算。逻辑代数有一系列的定律和规则,用它们对数学表达式进行处理,可以完成对电路的化简、变换、分析和设计。

一、逻辑代数的基本定律和恒等式 常用逻辑代数定律和恒等式表:P90 加乘非 基本定律 结合律 交换律 分配律 反演律(摩根定律) 吸收律 其他常用恒等式 表中的基本定律是根据逻辑加、乘、非三种基本运算法则,推导出的逻辑运算的一些基本定律。对于表中所列的定律的证明,最有效的方法就是检验等式左边的函数和右边函数的真值表是否吻合。 证明: 证明如下: 二、逻辑代数的基本规则

第20章习题门电路和组合逻辑电路 S10101B 为实现图逻辑表达式的功能,请将TTL电路多余输入端 C进行处理(只需一种处理方法),Y i 端应接________________________ ,丫2的C端应接 _______________________ , 费二FqlFl Y I=A+Π S10203G 在F = AB+CD的真值表中,F =1的状态有()。 A. 2个 B. 4个 C. 3个 D. 7个 解:D S10203N 某与非门有A、B、C三个输入变量,当 B=I时,其输出为()。 A. 0 B. 1 C. AC D. AC 解:C S10204B 在数字电路中,晶体管的工作状态为( A. 饱和 C.饱和或放大 解:D S10204I 逻辑电路如图所示,其逻辑函数式为()。 A. AB AB B. AB AB C. AB AB D. AB A 解:C S10204N 已知F=AB+CD ,选出下列可以肯定使 F = 0的情况()。 S10110B (a) 解:接地、悬空 (b) )。 B.放大 D.饱和或截止 t≈—Y A. C. 解: D A = 0,BC = 1 C = 1, D = 0 B. B = C = 1 D. AB = 0,CD = 0 A ≥ 1 B

三态门电路的三种可能的输出状态是_____________ 解:逻辑1、逻辑O、高阻态

S10214B 逻辑图和输入A, B 的波形如图所示,分析当输出 F 为“1”的时刻应是( )。 A. t ι B. t 2 C. t 3 解:A S10211I 图示逻辑电路的逻辑式为 ( )。 A. F =A B AB B. F=ABAB C. F=(A B)AB 解:B S10212I 逻辑电路如图所示,其功能相当于一个 ( A.门 B.与非门 C.异或门 解:C S10216B 图示逻辑电路的逻辑式为 ( )。 A. F =A B +A B A B. F =AB AB C. F =AB+ A B 解:C S10217B 逻辑图如图(a )所示,输入 A 、B 的波形如图 (b ),试分析在t ι瞬间输出F 为( )。 A. “1” B. “ 0” C. 不定 解:B h (a) (b) S10218B 图示逻辑符号的逻辑状态表为 ( A. B. A B F 0 0 0 0 1 0 1 0 0 1 1 1 A B F 0 0 0 0 1 1 1 0 1 1 1 1 A B F 0 0 1 0 1 1 1 0 1 1 1 C. 解:B T&] A —

一.目的 由逻辑图得出逻辑功能 二.方法(步骤) 1.列逻辑式: 由逻辑电路图列输出端逻辑表达式; (由输入至输出逐级列出) 2.化简逻辑式: 代数法、卡诺图法; (卡诺图化简步骤保留) 3.列真值表: 根据化简以后的逻辑表达式列出真值表;4.分析逻辑功能(功能说明): 分析该电路所具有的逻辑功能。 (输出与输入之间的逻辑关系); (因果关系) (描述函数为1时变量取值组合的规律) 技巧:先用文字描述真值表的规律(即叙述函数值为1时变量组合所有的取值),然后总结归纳电路实现的具体功能。 5.评价电路性能。 三.思路总结:

四.注意: 关键:列逻辑表达式; 难点:逻辑功能说明 1、逻辑功能不好归纳时,用文字描述真值表的规律。(描述函数值为1时变量组合所有的取值)。 2、常用的组合逻辑电路。 (1)判奇(偶)电路; (2)一致性(不一致性)判别电路; (3)相等(不等)判别电路; (4)信号有无判别电路; (5)加法器(全加器、半加器); (6)编码器、优先编码器; (7)译码器; (8)数值比较器; (9)数据选择器; (10)数据分配器。 3、多输出组合逻辑电路判别: 1)2个输出时考虑加法器:2输入半加;3输入全加。 2)4输出时考虑编码器:4输入码型变换;编码器。

五.组合逻辑电路分析实例 例1 电路如图所示,分析电路的逻辑功能。 A B Y 解: (1)写出输出端的逻辑表达式:为了便于分析可将电路自左至右分三级逐级写出Z 1、Z 2、Z 3和Y 的逻辑表达式为: 321 3121Z Z Y BZ Z AZ Z AB Z ==== (2)化简与变换:将Z 1、Z 2、和Z 3代入到公式Y 中进行公式化简得: B A B A BZ AZ BZ AZ Z Z Z Z Y +=+=+=+==11113232 (3)列出真值表:根据化简以后的逻辑表达式列出真值表如表所示。

第15章 组合逻辑电路 习题选解及参考答案 一、填空题: 1.组合逻辑电路的输出仅与 有关。 2.74LS48使能端LT 的作用是 。 3.共阳极的数码管输入信号的有效电平是 电平。 二、选择题: 1.八输入端的编码器按二进制数编码时,输出端的个数是( )。 A 、2个 B 、3个 C 、4个 D 、8个 2.四个输入的译码器,其输出端最多为( )。 A 、4个 B 、8个 C 、10个 D 、16个 3.当74LS148的输入端0I ~7I 按顺序输入11011101时,输出0Y ~2Y 为( )。 A 、101 B 、010 C 、001 D 、110 4.一个两输入端的门电路,当输入为1和0时,输出不是1的门是( )。 A 、与非门 B 、或门 C 、或非门 D 、异或门 5.多余输入端可以悬空使用的门是( )。 A 、与门 B 、TTL (加上TTL )与非门 C 、或门 D 、或非门 6.数字电路中使用的数制是( )。 A 、二进制 B 、八进制 C 、十进制 D 、十六进制 7.能驱动七段数码管显示的译码器是( )。 A 、74LS48 B 、74LS138 C 、74LS148 D 、TS547 四、分析、化简: 1.写出图示逻辑电路的逻辑表达式及真值表。 2.写出下列逻辑函数的最小项表示形式。 ① ()B A C B A F ++= ② BC B A C A F ++= 3.用代数法化简下列逻辑函数 ① ABC C B A C AB BC A C B A ++++ ② D C B AB BC A +++ F B (a ) F C (b)

第10章组合逻辑电路 (1)数字电路分类:①组合逻辑电路(简称组合电路);②时序逻辑电路(简称时序电路,第10章介绍)。 (2)组合逻辑电路:任何时刻电路的输出状态只取决于该时刻的输入状态,而与该时刻以前的电路状态无关。 (例如:编码器、译码器、全加器等等) (组合逻辑电路的基本单元电路是门电路,描述组合逻辑电路逻辑功能的方法主要有:逻辑表达式、真值表和工作波形图。) 10.1 组合逻辑电路的分析和设计 10.1.1 组合逻辑电路的分析 组合电路分析:就是根据已知的组合逻辑电路,找出组合电路的输出与输入的关系,指出电路所能实现的逻辑功能。 (电路图已知,求真值表。) 分析步骤: (1)由逻辑图写出输出端的逻辑表达式; (2)运用逻辑代数将所得逻辑函数表达式化简或变换; (3)列出输入输出关系的逻辑状态表(即真值表); (4)分析电路的逻辑功能。 (书上206页,例题10-1) 10.1.2 组合逻辑电路的设计 组合电路设计的含义:组合电路的“设计”(或称“综合”)与组合电路的分析方法相反,它是根据要完成的逻辑功能,画出实现该功能的最简逻辑电路。 最简的含义:器件数最少,器件种类最少,连线最少。 组合逻辑电路的设计步骤: (1)根据逻辑问题的逻辑关系,确定输入变量和输出变量; (引起事件的原因定为输入变量;事件的结果定为输出变量。) (2)根据给定的因果关系写出逻辑真值表; (3)由真值表写出逻辑函数表达式; (4)根据所用的器件类型,将函数化简,把变量变换成所需要的形式; (5)根据化简或者变化后的逻辑表达式画出电路图。 注意:在设计当中,应该根据所用门电路的类型来化简逻辑表达式。 (例如:用与非门设计时,应把逻辑函数表达式变换为最简的与非表达式。) (书上208页,例题10-3、10-4、10-5、10-6) 10.2 常用集成组合逻辑电路 (在数字电路中,常用的组合电路有加法器、编码器、译码器、数据分配器和多路选择器等。下面几节分别介绍这)几种典型组合逻辑电路的基本结构、工作原理和使用方法。. 10.2.1 编码器 在数字电路中,为了区分一系列不同的事物,将其中的每个事物用一系列逻辑“0”和逻辑“1”按一定规律编排起来,组成不同的代码来表示,这就是编码的含意。) (1)编码:把二进制码按一定规律编排,使每组代码具有一特定的含义,称为编码。 (2)编码器:完成编码功能的电路统称为编码器。 1、二进制编码器 n2N n位二进制代码对(1)普通二进制编码器:用个信号进行编码的电路称为二进制编码器。

第一到四章 复习总结 一、基本要求 1.正确理解以下基本概念:逻辑变量、逻辑函数、“与、或、非”基本逻辑关系、数制及码制。 2.熟练掌握逻辑函数的几种常用的表示方法:真值表、逻辑表达式、逻辑图、卡诺图。并能熟练的相互转换。 3. 熟练掌握逻辑代数基本定律、基本运算规则,能够熟练用其对逻辑函数进行代数化简及表达式转换。 4. 熟练掌握卡诺图化简法。 5.熟练掌握组合逻辑电路的分析方法和设计方法。 6.熟练掌握译码器、编码器、数据选择器、数值比较器的逻辑功能及常用中规模集成电路的应用。 7.熟练掌握半加器、全加器的逻辑功能,设计方法。 二、 解答示例及解题技巧 1. 用代数法化简下列各式: (1)C AB C B BC A AC +++ =C AB C B BC A AC ++?(摩根定律) =C AB C B C B A C A ++++?+)()((摩根定律) =C AB C B C C B C A C A B A ++++++(分配律) =C B C B A ++(吸收律) =B C B A ++(吸收律) =B +(吸收律) =BC (摩根定律)

(2)C B A ABC C B A+ + ⊕) ( =C B A C B A) ( ) (⊕ + ⊕(分配律) =C B A B A]) ( ) [(⊕ + ⊕(分配律) =C (互补律) 2.用卡诺图法化简下列各式: (1)L(A,B,C,D)=∑m(3,4,5,6,9,10,12,13,14,15) 解:将逻辑函数填入卡诺图并圈“1”,如图所示。对应写出逻辑表达式: CD B A D AC A AB D B B L+ + + + + = AB CD L A B C D 1 1 1 1 1 1 1 1 1 1 L CD 1 C B 1 1 A AB D 1 1 (a) (b) (2)L(A,B,C,D)=∑m(1,4,6,9,13)+∑d (0,3,5,7,11,15) 解:将逻辑函数填入卡诺图并圈“1”,如图所示。对应写出逻辑表达式: D C B A L+ = *讨论:在对逻辑函数进行卡诺图化简时,要注意下列几个问题:

《组合逻辑电路分析》练习题及答案 [4.1] 分析图P4.1电路的逻辑功能,写出Y 1、、Y 2的逻辑函数式,列出真值表,指出电路完成什么逻辑功能。 图P4.1 [解] BC AC AB Y BC AC AB C B A ABC Y ++=+++++=21)( 真值表: A B C Y 1 Y 2 000 0 0 00 1 1 0 010 1 0 01 1 0 1 100 1 0 10 1 0 1 1 1 0 0 1 11 1 1 1 由真值表可知:电路构成全加器,输入A 、B 、C 为加数、被加数和低位的进位,Y 1为“和”,Y 2为“进位”。 [4.2] 图P4.2是对十进制数9求补的集成电路CC14561的逻辑图,写出当COMP=1、Z=0、和COMP=0、Z=0时,Y 1~Y 4的逻辑式,列出真值表。

图P4.2 [解] (1)COMP=1、Z=0时,TG 1、TG 3、TG 5导通,TG 2、TG 4、TG 6关断。 3232211 , ,A A Y A Y A Y ⊕===, 4324A A A Y ++= (2)COMP=0、Z=0时, Y 1=A 1, Y 2=A 2, Y 3=A 3, Y 4=A 4。 COMP=1、Z=0时的真值表 COMP=0、Z=0的真值表从略。 [题4.3] 用与非门设计四变量的多数表决电路。当输入变量A 、B 、C 、D 有3个或3个以上为1时输出为1,输入为其他状态时输出为0。 [解] 题4.3的真值表如表A4.3所示,逻辑图如图A4.3所示。 表A4.3 ABCD D ABC D C AB CD B A BCD A Y ++++= BCD ACD ABC ABC +++= 十进制数 A 4A 3A 2A 1 Y 4Y 3Y 2 Y 1 十进制数 A 4 A 3 A 2 A 1 Y 4 Y 3 Y 2 Y 1 0 0 0 0 0 100 1 8 1000 000 1 1 000 1 1000 9 100 1 0000 2 0010 011 1 伪 码 1010 011 1 3 001 1 0110 101 1 0110 4 0100 010 1 1100 010 1 5 010 1 0100 110 1 0100 6 0110 001 1 1110 001 1 7 011 1 0010 111 1 0010 A B C D Y A B C D Y 0 0 0 0 0 1000 0 000 1 0 100 1 0 0010 0 1010 0 001 1 0 101 1 1 0100 0 1100 0 010 1 0 110 1 1 0110 0 1110 1 011 1 1 111 1 1

D C D C +第20章 门电路和组合逻辑电路 一、填空题 1、在逻辑器件中,半加器是 逻辑电路,计数器是 逻辑电路。 2、(C8A)16 = ( )2, (57)10 = ( ) 2。 3、逻辑函数Y AD CD BC DC =+++的最简与或表达式为 Y = 。 二、选择题 1、由开关组成的逻辑电路如图1所示。设开关投向上方为 1 态,投向下方为 0 态,则灯亮否与开关状态之间的逻辑关系为: (A) A B A B + (B) AB AB + (C) A B A B + (B) AB AB + 2、图2所示组合逻辑电路的逻辑表达式为 。 (A) BC B A + (B)C A B A + (C) AC B A + (B) C A B A + 3、比较三个数的大小:A=(1110000)2,B=(125)10,C=(9A)16 (A) A 2、列出逻辑状态表分析图中电路的逻辑功能。 3、甲、乙两校举行联欢会,入场券分红、黄两种,甲校学生持红票入场,乙校学生持黄票入场。会场入口处如设一自动检票机:符合条件者放行,否则不准入场。根据命题列出真值表,写出表达式并化简;画出用与非门实现的逻辑电路。 A L L