实验一、寄存器实验

一、实验目的

了解模型机中各种寄存器的结构、工作原理及其控制方法,掌握运算器中寄存器的数据传输方法和基本控制原理,为后续学习CPU中数据在各寄存器之间的传输做必要的知识储备。

二、实验要求

使用CP226 实验平台,将要求的数据写入相关的寄存器,并能得到准确的实验结果。

三、实验内容

利用CP226 实验平台上的K23-K16开关作为DBUS 的数据,K7..K0中的某些开关作为控制信号(控制方式见六),将K23-K16上的数据写入累加器A、工作寄存器W、数据寄存器组R0、R1、R2、R3中。其具体内容如下(本实验为脱机实验):

1.将二位学生学号的最后2位以BCD码的方式分别写入累加器A和工作寄存器W中,

并将实验结果的局部贴图粘贴在实验报告上;

2.将二位学生学号的最后2位以BCD码的方式分别写入R0和R1、R2和R3工作寄

存器中,并将实验结果的局部贴图粘贴在实验报告上。

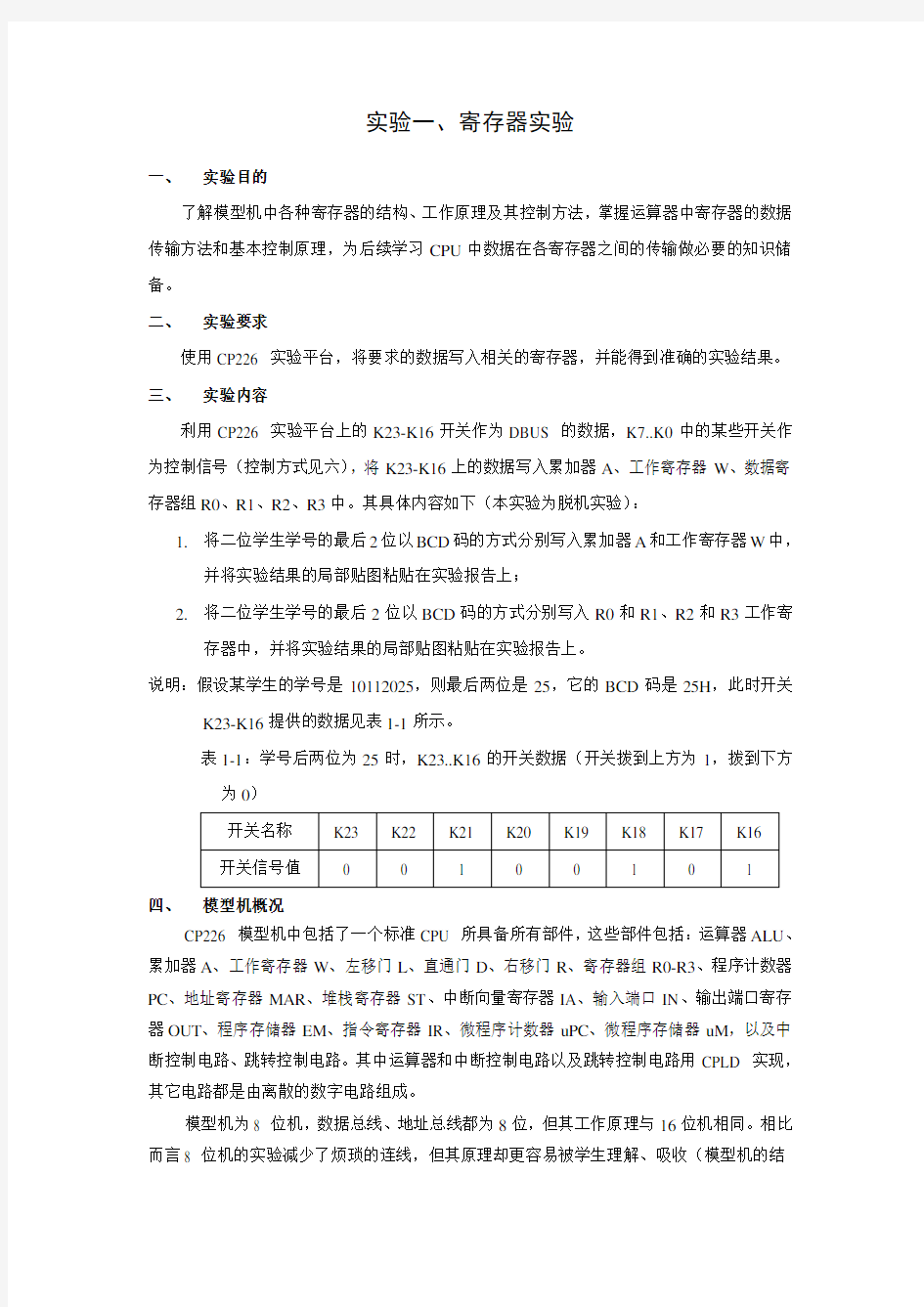

说明:假设某学生的学号是10112025,则最后两位是25,它的BCD码是25H,此时开关K23-K16提供的数据见表1-1所示。

表1-1:学号后两位为25时,K23..K16的开关数据(开关拨到上方为1,拨到下方为0)

四、模型机概况

CP226 模型机中包括了一个标准CPU 所具备所有部件,这些部件包括:运算器ALU、累加器A、工作寄存器W、左移门L、直通门D、右移门R、寄存器组R0-R3、程序计数器PC、地址寄存器MAR、堆栈寄存器ST、中断向量寄存器IA、输入端口IN、输出端口寄存器OUT、程序存储器EM、指令寄存器IR、微程序计数器uPC、微程序存储器uM,以及中断控制电路、跳转控制电路。其中运算器和中断控制电路以及跳转控制电路用CPLD 实现,其它电路都是由离散的数字电路组成。

模型机为8 位机,数据总线、地址总线都为8位,但其工作原理与16位机相同。相比而言8 位机的实验减少了烦琐的连线,但其原理却更容易被学生理解、吸收(模型机的结

构见附件1)。

五、实验电路

1.实验平台中累加器A和工作寄存器W的电路图

图1-1 累加器A的电路图

图1-2 工作寄存器W的电路图

2.工作寄存器R0-R3的电路图

图1-3 工作寄存器R0-R3的电路图

六、实验接线与控制信号设置

1.实验内容1

从图1-1和1-2可见,要使K23-K16上的数据写入到累加器A和工作寄存器W,必须要使DBUS数据线与开关K23-K16相连,使AEN和WEN分别为低电平,并在CK信号产生上升沿(74HC574是上升沿触发)。由于CK内部已连接到STEP按键上,所以要用STEP 按键提供写入累加器A和工作寄存器W的控制信号。写入寄存器A和W的实验连线如表1-2所示。

表1-2:将学号的最后2位写入累加器A和工作寄存器W的连线与电平设置表

表1-2-1:写入累加器A的控制信号

表1-2-2:写入工作寄存器W的控制信号

2.实验内容2

按着对实验内容1的分析方法,写入寄存器R0..R3的实验连线如表1-3所示。

表1-3:将学号的最后4位写入工作寄存器R0..R3的连线与电平设置表

表1-3-1写入工作寄存器R0..R3的控制信号

六、实验步骤

请按下述步骤操作:

●关闭实验箱的电源,分别按实验连线表(表1-2或表1-3)连接线路;

●将K23-K16开关置零(全部拨到下方),然后打开实验箱的电源,按[RST]钮,再

按[TV/ME]键三次(不要过快),即进入“Hand......”手动状态;

●按输入数据要求改变波动开关K23..K16位置(表1-1),形成不同学生学号的BCD

码;

●分别按控制信号设置的要求(表1-2-1和表1-2-2或表1-3-1)改变控制值,然后按

动STEP按键,此时数据被写入相应的寄存器中。

电子通信与软件工程 系2013-2014学年第2学期 《数字电路与逻辑设计实验》实验报告 --------------------------------------------------------------------------------------------------------------------- 班级: 姓名: 学号: 成绩: 同组成员: 姓名: 学号: --------------------------------------------------------------------------------------------------------------------- 一、 实验名称:集成计数器及寄存器的运用 二、实验目的: 1、熟悉集成计数器逻辑功能与各控制端作用。 2、掌握计数器使用方法。 三、 实验内容及步骤: 1、集成计数器74LS90功能测试。74LS90就是二一五一十进制异步计数器。逻辑简图为图8、1所示。 四、 五、 图8、1 六、 74LS90具有下述功能: ·直接置0(1)0(2)0(.1)R R ,直接置9(S9(1,·S,.:,=1) ·二进制计数(CP 、输入QA 输出) ·五进制计数(CP 2输入Q D Q C Q B 箱出) ·十进制计数(两种接法如图8.2A 、B 所示) ·按芯片引脚图分别测试上述功能,并填入表 8、1、表8、2、表8、3中。

图8、2 十进制计数器 2、计数器级连 分别用2片74LS90计数器级连成二一五混合进制、十进制计数器。 3、任意进制计数器设计方法 采用脉冲反馈法(称复位法或置位法)。可用74LS90组成任意模(M)计数器。图8、3就是用74LS90实现模7计数器的两种方案,图(A)采用复位法。即计数计到M异步清0。图(B)采用置位法,即计数计到M一1异步置0。 图8、3 74LS90 实现七进进制计数方法 (1)按图8、3接线,进行验证。 (2)设计一个九进制计数器并接线验证。 (3)记录上述实验的同步波形图。 四、实验结果:

成绩:计算机原理实验室实验报告 课程:计算机组成原理 姓名:李文周 专业:计算机科学与技术 学号:132054237 日期:2015.12 太原工业学院 计算机工程系

实验二:寄存器实验 实验环境PC机+Win7+74LS373+proteus仿真器实验日期2015.12一.实验内容 (1)基本内容 1.理解CPU运算器中寄存器的作用 2.设计并验证4位算数逻辑单元的功能 (2)扩展要求 1.实现更多的寄存器(至少8个)

二.理论分析或算法分析 74ls373是常用的地址锁存器芯片,它实质是一个是带三态缓冲输出的8D 触发器,在单片机系统中为了扩展外部存储器,通常需要一块74ls373芯片。74ls373工作原理简述: (1).1脚是输出使能(OE),是低电平有效,当1脚是高电平时,不管输入3、4、7、8、13、14、17、18如何,也不管11脚(锁存控制端,G)如何,输出2(Q0)、5(Q1)、6(Q2)、9(Q3)、12(Q4)、15(Q5)、16(Q6)、19(Q7)全部呈现高阻状态(或者叫浮空状态); (2).当1脚是低电平时,只要11脚(锁存控制端,G)上出现一个下降沿,输出2(Q0)、5(Q1)、6(Q2)、9(Q3)、12(Q4)、15(Q5)、16(Q6)、19(Q7)立即呈现输入脚3、4、7、8、13、14、17、18的状态.锁存端LE由高变低时,输出端8位信息被锁存,直到LE 端再次有效。当三态门使能信号OE为低电平时,三态门导通,允许Q0~Q7输出,OE为高电平时,输出悬空。

L——低电平;H——高电平;X——不定态;Q0——建立稳态前Q的电平;G——输入端,与8031ALE连高电平:畅通无阻低电平:关门锁存。图中OE——使能端,接地。当G=“1”时,74LS373输出端1Q—8Q与输入端1D—8D相同;当G 为下降沿时,将输入数据锁存。 三.实现方法(含实现思路、程序流程图、实验电路图和源程序列表等)

福建农林大学计算机与信息学院信息工程类实验报告系:计算机科学与技术专业:计算机科学与技术年级: 09级 姓名:张文绮学号: 091150022 实验课程:计算机组成原理 实验室号:___田405 实验设备号: 43 实验时间:2010.12.19 指导教师签字:成绩: 实验一算术逻辑运算实验 1.实验目的和要求 1. 熟悉简单运算器的数据传送通路; 2. 验证4位运算功能发生器功能(74LS181)的组合功能。 2.实验原理 实验中所用到的运算器数据通路如图1-1所示。其中运算器由两片74181

以并/串形式构成8位字长的ALU。运算器的输出经过一个三态门(74245)和数据总线相连,运算器的两个数据输入端分别由两个锁存器(74373)锁存,锁存器的输入连接至数据总线,数据开关INPUT DEVICE用来给出参与运算的数据,并经过一个三态门(74245)和数据总线相连,数据显示灯“BUS UNIT”已和数据总线相连,用来显示数据总线内容。 图1-2中已将用户需要连接的控制信号用圆圈标明(其他实验相同,不再说明),其中除T4为脉冲信号,其它均为电平信号。由于实验电路中的时序信号均已连至W/R UNIT的相应时序信号引出端,因此,在进行实验时,只需将W/R UNIT 的T4接至STATE UNIT的微动开关KK2的输出端,按动微动开关,即可获得实验所需的单脉冲,而S3,S2,S1,S0,Cn,LDDR1,LDDR2,ALU-B,SW-B各电平控制信号用SWITCH UNIT中的二进制数据开关来模拟,其中Cn,ALU-B,SW-B为低电平控制有效,LDDR1,LDDR2为高电平有效。 3.主要仪器设备(实验用的软硬件环境) ZYE1603B计算机组成原理教学实验系统一台,排线若干。 4.操作方法与实验步骤

寄存器实验报告

一、实验目的 1. 了解寄存器的分类方法,掌握各种寄存器的工作原理; 2. 学习使用V erilog HDL 语言设计两种类型的寄存器。 二、实验设备 PC 微机一台,TD-EDA 实验箱一台,SOPC 开发板一块。 三、实验内容 寄存器中二进制数的位可以用两种方式移入或移出寄存器。第一种方法是以串行的方式将数据每次移动一位,这种方法称之为串行移位(Serial Shifting),线路较少,但耗费时间较多。第二种方法是以并行的方式将数据同时移动,这种方法称之为并行移位(Parallel Shifting),线路较为复杂,但是数据传送的速度较快。因此,按照数据进出移位寄存器的方式,可以将移位寄存器分为四种类型:串行输入串行输出移位寄存器(Serial In- Serial Out)、串行输入并行输出移位寄存器(Serial In- Parallel Out)、并行输入串行输出移位寄存器(Parallel In- Serial Out)、并行输入并行输出移位寄存器(Parallel In-Parallel Out)。 本实验使用V erilog HDL 语言设计一个八位并行输入串行输出右移移位寄存器(Parallel In- Serial Out)和一个八位串行输入并行输出寄存器(Serial In- Parallel Out),分别进行仿真、引脚分配并下载到电路板进行功能验证。 四、实验步骤 1.并行输入串行输出移位寄存器实验步骤 1). 运行Quartus II 软件,选择File New Project Wizard 菜单,工程名称及顶层文件名称为SHIFT8R,器件设置对话框中选择Cyclone 系列EP1C6Q240C8 芯片,建立新工程。 2.) 选择File New 菜单,创建V erilog HDL 描述语言设计文件,打开文本编辑器界面。 3.) 在文本编辑器界面中编写V erilog HDL 程序,源程序如下: module SHFIT8R(din,r_st,clk,load,dout); input [7:0]din; input clk,r_st,load; output dout; reg dout; reg [7:0]tmp; always @(posedge clk) if(!r_st) begin dout<=0; end else begin if(load) begin tmp=din; end else

重庆理工大学 《计算机组成原理》 实验报告 学号 __11503080109____ 姓名 __张致远_________ 专业 __软件工程_______ 学院 _计算机科学与工程 二0一六年四月二十三实验一基本运算器实验报告

一、实验名称 基本运算器实验 二、完成学生:张致远班级115030801 学号11503080109 三、实验目的 1.了解运算器的组成结构。 2.掌握运算器的工作原理。 四、实验原理: 两片74LS181 芯片以并/串形式构成的8位字长的运算器。右方为低4位运算芯片,左方为高4位运算芯片。低位芯片的进位输出端Cn+4与高位芯片的进位输入端Cn相连,使低4位运算产生的进位送进高4位。低位芯片的进位输入端Cn可与外来进位相连,高位芯片的进位输出到外部。 两个芯片的控制端S0~S3 和M 各自相连,其控制电平按表2.6-1。为进行双操作数运算,运算器的两个数据输入端分别由两个数据暂存器DR1、DR2(用锁存器74LS273 实现)来锁存数据。要将内总线上的数据锁存到DR1 或DR2 中,则锁存器74LS273 的控制端LDDR1 或LDDR2 须为高电平。当T4 脉冲来到的时候,总线上的数据就被锁存进DR1 或DR2 中了。 为控制运算器向内总线上输出运算结果,在其输出端连接了一个三态门(用74LS245 实现)。若要将运算结果输出到总线上,则要将三态门74LS245 的控制端ALU-B 置低电平。否则输出高阻态。数据输入单元(实验板上印有INPUT DEVICE)用以给出参与运算的数据。其中,输入开关经过一个三态门(74LS245)和内总线相连,该三态门的控制信号为SW-B,取低电平时,开关上的数据则通过三态门而送入内总线中。 总线数据显示灯(在BUS UNIT 单元中)已与内总线相连,用来显示内总线上的数据。控制信号中除T4 为脉冲信号,其它均为电平信号。 由于实验电路中的时序信号均已连至“W/R UNIT”单元中的相应时序信号引出端,因此,需要将“W/R UNIT”单元中的T4 接至“STATE UNIT”单元中的微动开关KK2 的输出端。在进行实验时,按动微动开关,即可获得实验所需的单脉冲。 S3、S2、 S1、S0 、Cn、M、LDDR1、LDDR2、ALU-B、SW-B 各电平控制信号则使用“SWITCHUNIT”单元中的二进制数据开关来模拟,其中Cn、ALU-B、SW-B 为低电平有效,LDDR1、LDDR2 为高电平有效。 对于单总线数据通路,作实验时就要分时控制总线,即当向DR1、DR2 工作暂存器打入数据时,数据开关三态门打开,这时应保证运算器输出三态门关闭;同样,当运算器输出结果至总线时也应保证数据输入三态门是在关闭状态。 运算结果表

成绩:实验报告 课程名称:计算机组成原理 实验项目:寄存器的原理及操作 姓名: 专业:计算机科学与技术 班级: 学号:

计算机科学与技术学院 实验教学中心 20 16年6月20日

实验项目名称:寄存器的原理及操作 一、实验目的 1.了解模型机中 A, W 寄存器结构、工作原理及其控制方法。 2.了解模型机中寄存器组 R0..R3 结构、工作原理及其控制方法。 3.了解模型机中地址寄存器 MAR,堆栈寄存器 ST,输出寄存器 OUT寄存器结构、工作原理及其控 制方法。 二、实验内容 1、A、W寄存器:利用 COP2000实验仪上的K16..K23 开关做为DBUS的数据,其它开关做为控制信号, 将数据写入寄存器A, W。 2、R0、R1、R2、R3 寄存器实验:利用COP2000实验仪上的K16..K23 开关做为DBUS的数据,其它开 关做为控制信号,对数据寄存器组R0..R3 进行读写。 3、MAR、ST、OUT寄存器:利用COP2000实验仪上的K16..K23 开关做为DBUS的数据,其它开关做为 控制信号,将数据写入地址寄存器MAR,堆栈寄存器ST,输出寄存器OUT。 三、实验用设备仪器及材料 伟福 COP2000 系列计算机组成原理实验系统 四、实验原理及接线 实验 1:A,W 寄存器实验

实验 2 :R0,R1, R2,R3寄存器实验

MAR为存储器地址寄存器,其功能是存储操作数在内存中的地址,信号MAREN的功能是将数据总线DBUS上数据 MAR,信号 MAROE的功能是将MAR的值送到地址总线ABUS上 ST 堆栈寄存器的作用,是出现中断或子程序调用时,保存断点处PC 的值,以便中断或子程序结束时, 能继续执行原程序。图中,信号STEN的作用是将数据总线DBUS上数据存入堆栈寄存器ST 中

西华大学数学与计算机学院实验报告 课程名称:计算机组成原理年级:2011级实验成绩: 指导教师:祝昌宇姓名:蒋俊 实验名称:通用寄存器单元实验学号:312011*********实验日期:2013-12-15 一、目的 1.了解通用寄存器的组成和硬件电路 2. 利用通用寄存器实现数据的置数、左移、右移等功能 二、实验原理 (1)寄存器实验构成 1、通用寄存器由2片GAL构成8位字长的寄存器单元。8芯插座RA-IN作为数据输入端,可通过端8芯扁平电缆,把数据数据输入端连接到数据总线上。 2、数据输出由一片74LS244(输出缓冲器)来控制。用8芯插座RA-OUT作为数据输出端,可通过端8芯扁平电缆,把数据数据输出端连接到数据总线上。 3、判零和进位电路由1片GAL、1片7474和一些常规芯片组成,用2个LED(ZD、CY)发光管分别显示其状态。 (2)通用寄存器单元的工作原理 通用寄存器的核心部件为2片GAL,它具有锁存、左移、右移、保存等功能。各个功能都由X1、X2信号和工作脉冲RACK来决定。当置ERA=0、X0=1、X1=1,RACK有上升沿时,把总线上的数据打入通用寄存器。可通过设置X1、X0来指定通用寄存器工作方式,通用寄存器的输出端Q0~Q7接入判零电路。LED(ZD)亮时,表示当前通用寄存器内数据为0。 输出缓冲器采用74LS244,当控制信号RA-O为低时,74LS244开通,把通用寄存器内容输出到总线;当控制信号RA-O为高时,74LS244的输出为高阻。 图1 通用寄存器原理图 三、使用环境 计算机组成原理实验箱 四、实验步骤

(一)数据输入通用寄存器 1.把RA-IN(8芯的盒型插座)与CPT-B板上二进制开关单元中的J1插座相连(对应二进制开关H16~H23),把RA-OUT(8芯的盒型插座)与数据总线上的DJ6相连。 2.把RACK连到脉冲单元的PLS1,把ERA、X0、X1、RA-0、M接入二进制拨动开关。请按下表接线。 信号定义接入开关位号 RACK PLS1孔 X0 H12孔 X1 H11孔 ERA H10孔 RA-O H9孔 M H4孔 3.二进制开关H16~H23作为数据输入,置42H(对应开关如下表) H23 H22 H21 H20 H19 H18 H17 H16 数据总线值 D7 D6 D5 D4 D3 D2 D1 D0 8位数据 0 1 0 0 0 0 1 0 42H 置各控制信号如下: H12 H11 H10 H9 H4 X0 X1 ERA RA-O M 1 1 0 0 1 4.按启停单元中的有效按钮,置实验机为运行状态。 5.按脉冲单元中的PLS1脉冲按键,在RACK上产生一个上升沿,把42H打入通用寄存器。 $ 此时数据总线上的指示灯IDB0~IDB7显示为42H。由于通用寄存器内容不为0,所以ZD (LED)灯灭。 (二)寄存器内容无进位位左移 1.把42H打入通用寄存器中,数据总线上显示42H。 2.实现左移功能,置各控制信号如下: H12 H11 H10 H9 H4 X0 X1 ERA RA-O M 1 1 0 0 1 3.按启停单元中的有效按钮,置实验机为运行状态。 4.按脉冲单元中的PLS1脉冲按键,在RACK上产生一个上升沿,使通用寄存器的值左移。 $ 此时数据总线上的LED指示灯IDB0~IDB7应该显示为84H。由于通用寄存器内容不为0,所以ZD (LED)灯灭。 5.按脉冲单元中的PLS1脉冲按键,使通用寄存器的值左移,此时数据总线上的LED指示灯IDB0~IDB7显示为09H。若一直按PLS1,在总线上看见数据循环左移的现象。

实验一寄存器实验 一、实验目的 1. 了解模型机中A, W寄存器结构、工作原理及其控制方法。 2. 了解模型机中寄存器组R0..R3结构、工作原理及其控制方法。 3. 了解模型机中地址寄存器MAR,堆栈寄存器ST,输出寄存器OUT寄存器结构、 工作原理及其控制方法。 二、实验要求 1、A、W寄存器:利用COP2000实验仪上的K16..K23开关做为DBUS的数据,其它 开关做为控制信号,将数据写入寄存器A,W。 2、R0、R1、R2、R3寄存器实验:利用COP2000实验仪上的K16..K23开关做为 DBUS的数据,其它开关做为控制信号,对数据寄存器组R0..R3进行读写。 3、MAR、ST、OUT寄存器:利用COP2000实验仪上的K16..K23开关做为DBUS的 数据,其它开关做为控制信号,将数据写入地址寄存器MAR,堆栈寄存器ST,输出寄存器OUT。 三、实验原理 寄存器的作用是用于保存数据的,因为我们的模型机是8位的,因此在本模型机中大部分寄存器是8位的,标志位寄存器(Cy, Z)是二位的。 COP2000用74HC574来构成寄存器。74HC574的功能如下: 说明: 1. 在CLK的上升沿将输入端的数据打入到8个触发器中 2. 当OC = 1 时触发器的输出被关闭,当OC=0时触发器的输出数据 注意: 1. 数据是在放开CLK键后改变的,也就是CLK的上升沿数据被打入。 2. 当允许打入信号为高时,即使CLK有上升沿,寄存器的数据也不会改变。

74HC574工作波形图四、实验原理 (一)A,W寄存器实验 1. 原理图 寄存器A原理图 寄存器W原理图2.工作波形图 寄存器A,W写工作波形图

实验二寄存器(二)+ALU 2.1寄存器(二)实验 (MAR地址寄存器,ST 堆栈寄存器,OUT输出寄存器) 一.原理图 1. MAR地址寄存器 2. ST 堆栈寄存器 3. OUT输出寄存器

二.连接线表 三.写寄存器 1.将12H写入MAR寄存器 步骤: (1)二进制开关K23-K16用于DBUS[7:0]的数据输入,置数据12H (2) 置控制信号为: 按住STEP脉冲键,CK由高变低,这时寄存器MAR的黄色选择指示灯亮,表明选择MAR寄存器。放开STEP键,CK由低变高,产生一个上升沿,数据12H被写入MAR寄存器。 K14(MAROE)为0,MAR寄存器中的地址输出,MAR 红色输出指示灯亮。 将K14(MAROE)置为1,关闭MAR输出。 2. 将34H写入ST寄存器 步骤: (1)二进制开关K23-K16用于DBUS[7:0]的数据输入,置数据34H (2)置控制信号为: 按住STEP 脉冲键,CK 由高变低,这时寄存器ST 的黄色选择指示灯亮,表明选择ST 寄存器。放开STEP键,CK由低变高,产生一个上升沿,数据34H被写入ST 寄存器。

3. 将56H写入OUT寄存器 步骤: (1)二进制开关K23-K16用于DBUS[7:0]的数据输入,置数据56H (2)置控制信号为: 按住STEP 脉冲键,CK 由高变低,这时寄存器OUT 的黄色选择指示灯亮,表明选择OUT 寄存器。放开STEP 键,CK 由低变高,产生一个上升沿,数据56H 被写入OUT寄存器。 2.2 运算器实验 实验要求:利用CPTH 实验仪的K16..K23 开关做为DBUS 数据,其它开关做为控制信号,将数据写累加器A和工作寄存器W,并用开关控制ALU的运算方式,实现运算器的功能。 实验目的:了解模型机中算术、逻辑运算单元的控制方法。 实验电路:CPTH 中的运算器由一片CPLD实现,有8 种运算,通过S2,S1,S0 来选择,运算数据由寄存器A及寄存器W 给出,运算结果输出到直通门D。 一.功能描述 二.连接线表

《计算机组成原理实验》课程实验报告 实验题目组成原理上机实验 班级1237-小 姓名 学号 时间2014年5月 成绩

实验一基本运算器实验 1.实验目的 (1)了解运算器的组成原理 (2)掌握运算器的工作原理 2.实验内容 输入数据,根据运算器逻辑功能表1-1进行逻辑、移位、算术运算,将运算结果填入表1-2。 表 1-1运算器逻辑功能表 运算类 A B S3 S2 S1 S0 CN 结果 逻辑运算65 A7 0 0 0 0 X F=( 65 ) FC=( ) FZ=( ) 65 A7 0 0 0 1 X F=( A7 ) FC=( ) FZ=( ) 0 0 1 0 X F=( ) FC=( ) FZ=( ) 0 0 1 1 X F=( ) FC=( ) FZ=( ) 0 1 0 0 X F=( ) FC=( ) FZ=( ) 移位运算0 1 0 1 X F=( ) FC=( ) FZ=( ) 0 1 1 0 0 F=( ) FC=( ) FZ=( ) 1 F=( ) FC=( ) FZ=( ) 0 1 1 1 0 F=( ) FC=( ) FZ=( ) 1 F=( ) FC=( ) FZ=( ) 算术运算 1 0 0 0 X F=( ) FC=( ) FZ=( ) 1 0 0 1 X F=( ) FC=( ) FZ=( ) 1 0 1 0X F=( ) FC=( ) FZ=( ) 1 0 1 0X F=( ) FC=( ) FZ=( ) 1 0 1 1 X F=( ) FC=( ) FZ=( ) 1 1 0 0 X F=( ) FC=( ) FZ=( ) 1 1 0 1 X F=( ) FC=( ) FZ=( ) 表1-2运算结果表

成绩: 计算机原理实验室实验报告 本说明打印前删除!!proteus 实验报告格式必须保持原样,蓝色部分按照实验内容自行填写;全班统一使用A4大小纸张,部分困难学生可以使用等大小纸张,自绘实验报告格式;全部实验完成后,学委按照实验顺序把每个学生的实验报告(含首页)装订成册,按照学号顺序排列,提交给实验指导老师(询问代课老师,学校将实验工作指派给了哪位老师)。 学委提交报告时,需要同时提交(附录)实验成绩登记表一份。其中表头部分课程,班级,班级总人数照实填写,项目填写本学期本课程的实验数量;学号姓名栏按照顺序填写,报告一栏填写该同学交报告的份数(每项目每人一份报告);出勤和成绩栏留空,由实验室填写;特殊情况填写在备注处,若空间不够请写于背面并在备注处标明;若有学号超过58号的情况,请在背后按照格式登记所有项目;空学号可以不留空位置,顺序递进。 课程:计算机组成原理 姓名:刘翔翔 专业:软件工程 学号:1420561 21 日期:2016年6月 太原工业学院 计算机工程系

实验二:输寄存器实验 实验环境PC机+Win 7+proteus仿真器实验日期2016.06.01 一.实验内容 基本要求 1.理解CPU运算器中寄存器的作用 2.设计并验证寄存器组(至少四个寄存器) 扩展要求 3.实现更多的寄存器(至少8个) 思考题: 思考随着寄存器的增多,电路设计的复杂度是什么比例增大? 二.理论分析或算法分析 1.基本要求 使用74LS373充当寄存器,74LS139做地址译码,74LS245用作输入,数码管显示寄存器内的数据。74LS139为二-四译码器,用两根线作为地址线接到74LS139的输入端,输出端分别接到每个74LS373的OE上,再用一个74LS139配合反相器产生控制每个74LS373的LE的信号。74LS245的输出端分别对应接到373输入端的每个管脚上的。74LS373的输出端对应接到数码管的对应管教上,以实现数据的显示。先在各个寄存器中输入不同的数据,然后关闭74ls248(输入),选择不同的373(寄存器),在数码管上显示不同的数据。 2.扩展要求 与基本要求相比大体不变,地址译码部分选择74LS138来做地址译码器。原理图连接方式原理不变,验证方式不变。

实验一基础汇编语言程序设计 一、实验目的: 1、学习和了解TEC-XP16教学实验系统监控命令的用法。 2、学习和了解TEC-XP16教学实验系统的指令系统。 3、学习简单的TEC-XP16教学实验系统汇编程序设计。 二、预习要求: 1、学习TEC-XP16机监控命令的用法。 2、学习TEC-XP16机的指令系统、汇编程序设计及监控程序中子程序调用。 3、学习TEC-XP16机的使用,包括开关、指示灯、按键等。 4、了解实验内容、实验步骤和要求。 三、实验步骤: 在教学计算机硬件系统上建立与调试汇编程序有几种操作办法。 第一种办法,是使用监控程序的A命令,逐行输入并直接汇编单条的汇编语句,之后使用G命令运行这个程序。缺点是不支持汇编伪指令,修改已有程序源代码相对麻烦一些,适用于建立与运行短小的汇编程序。 第二种办法,是使用增强型的监控程序中的W命令建立完整的汇编程序,然后用M命令对建立起来的汇编程序执行汇编操作,接下来用G命令运行这个程序。适用于比较短小的程序。此时可以支持汇编伪指令,修改已经在内存中的汇编程序源代码的操作更方便一些。 第三种办法,是使用交叉汇编程序ASEC,首先在PC机上,用PC机的编辑程序建立完整的汇编程序,然后用ASEC对建立起来的汇编程序执行汇编操作,接下来把汇编操作产生的二进制的机器指令代码文件内容传送到教学机的内存中,就可以运行这个程序了。适用于规模任意大小的程序。

在这里我们只采用第一种方法。 在TEC-XP16机终端上调试汇编程序要经过以下几步: 1、使教学计算机处于正常运行状态(具体步骤见附录联机通讯指南)。 2、使用监控命令输入程序并调试。 ⑴用监控命令A输入汇编程序 >A 或>A 主存地址 如:在命令行提示符状态下输入: A 2000↙;表示该程序从2000H(内存RAM区的起始地址)地址开始 屏幕将显示: 2000: 输入如下形式的程序: 2000: MVRD R0,AAAA ;MVRD 与R0 之间有且只有一个空格,其他指令相同 2002: MVRD R1,5555 2004: ADD R0,R1 2005: AND R0,R1 2006: RET ;程序的最后一个语句,必须为RET 指令 2007:(直接敲回车键,结束A 命令输入程序的操作过程) 若输入有误,系统会给出提示并显示出错地址,用户只需在该地址重新输入正确的指令即可。 ⑵用监控命令U调出输入过的程序并显示在屏幕上 >U 或>U 主存地址

移位寄存器实验报告 姓名:陈素学号:3120100621 专业:软件工程课程名称:逻辑与计算机设计基础实验同组学生姓名:张闻 实验时间:y yyy-mm-dd 实验地点:紫金港东4-509 指导老师:一、实验目的和要求 掌握移位寄存器的工作原理及设计方法 掌握串、并数据转换的概念与方法 了解序列信号在CPU控制器设计中的应用 二、实验内容和原理 2.1 实验原理 带并行置入的移位寄存器 移位寄存器:每来一个时钟脉冲,寄存器中的数据按顺序向左或向右移动一位必须采用主从触发器或边沿触发器 不能采用电平触发器 数据移动方式:左移、右移 数据输入输出方式 串行输入,串行输出 串行输入,并行输出 并行输入,串行输出 串行输入的移位寄存器 使用D触发器,可构成串行输入的移位寄存器 2.2 标题 <正文>

带并行输入的右移移位寄存器 数据输入移位寄存器的方式:串行输入、并行输入 带并行输入的8位右移移位寄存器 module shift_reg(clk, S, s_in, p_in, Q); input wire clk, S, s_in; input wire [7:0] p_in; output wire [7:0] Q; wire [7:0] D; wire nS; FD FDQ0(.C(clk), .D(D[0]), .Q(Q[0])), FDQ1(.C(clk), .D(D[1]), .Q(Q[1])), FDQ2(.C(clk), .D(D[2]), .Q(Q[2])), FDQ3(.C(clk), .D(D[3]), .Q(Q[3])), FDQ4(.C(clk), .D(D[4]), .Q(Q[4])), FDQ5(.C(clk), .D(D[5]), .Q(Q[5])), FDQ6(.C(clk), .D(D[6]), .Q(Q[6])), FDQ7(.C(clk), .D(D[7]), .Q(Q[7])); OR2 D0_L(.I0(L_0), .I1(R_0), .O(D[0])), D1_L(.I0(L_1), .I1(R_1), .O(D[1])), D2_L(.I0(L_2), .I1(R_2), .O(D[2])), D3_L(.I0(L_3), .I1(R_3), .O(D[3])), D4_L(.I0(L_4), .I1(R_4), .O(D[4])), 串行输入 S

实验四移位寄存器及其应用 一、实验目的: 1、熟悉中规模4位双向移位寄存器的逻辑功能并掌握其使用方法; 2、熟悉移位寄存器的应用典例一——构成串行累加器和环形计数器。 二、实验原理: 1、移位寄存器是一种具有移位功能的寄存器,是指寄存器中所存的代码能够在移位脉冲的作用下依次左移或右移。既能左移又能右移的移位寄存器称为双向移位寄存器,只需要改变左、右移的控制信号便可实现双向移位。根据存取信息的方式不同移位寄存器可分为:串入串出、串入并出、并入串出、并入并出四种形式。 本实验选用的4位双向通用移位寄存器,型号为74LS194或CC40194,两者功能相同, S L为左移串行输入端;S1、S0为异步清零端;CP为时钟脉冲输入端。 74LS194有5种不同操作模式:并行送数寄存,右移(方向由Q0至Q3),左移(方向由Q3至Q0),保持及清零。S1、S0和CR 端的控制作用如表 1所示。 2、移位寄存器的应用很广,可构成移位寄存器型计数器;顺序脉冲发生器;串行累加器;可用作数据转换,即把串行数据转换为并行数据,或把并行数据转换为串行数据等。本实验主要研究移位寄存器用作环形计数器和串行累加器的线路连接及其原理。

(1)环形计数器 把移位寄存器的输出反馈到它的串行输入端,就可以进行循环移位,如图11-2所示,把输出端Q3和右移串行输入端S R相连接,设初始状态Q0Q1Q2Q3=1000,则在时钟脉冲的作用下Q0Q1Q2Q3将依次变为0100、0010、0001、1000-----,可见它是一个具有四个有效状态的计数器,这种类型的计数器通常称为环形计数器。图 2电路可以由各个输出端输出在时间上有先后顺序的脉冲,因此也可作为顺序脉冲发生器。 (2)串行累加器 累加器是由移位寄存器和全加器组成的一种求和电路,它的功能是将本身寄存的数和另一个输入的数相加,并存放在累加器中。 图 2 图 3是由两个右向移位寄存器、一个全加器和一个进位触发器组成的串行累加器。 设开始时,被加数A=A N-1.....A O和加数B=B N-1......B O已分别存入N+1位累加数移位寄存器和加数移位寄存器。再设进位触发器D已被清零。 在第一个CP脉冲到来之前,全加器各输入、输出端的情况为:A N=A0,B N=B0,C N-1=0,S N=A0+B0+0=S0,C N=C0。

6.9 通用寄存器实验报告 一、实验目的: 1、了解通用寄存器组的用途及对CPU的重要性。 2、掌握通用寄存器组的设计方法。 二、实验内容: 1、通用寄存器组的作用 通用寄存器组是CPU的重要组成部分。 (1)从存储器和外部设备(除DMA方式外)取来的数据要放在通用寄存器中; (2)向存储器和外部设备(除DMA方式外)输出的数据从通用寄存器中取出; (3)参加算术运算和逻辑运算的数据从通用寄存器组中取出,同时通用寄存器也是运算结果的暂存地。 (4)通用寄存器组有两个读端口,负责提供进行算术逻辑单元需要的源操作数和目的操作数;有一个写端口,负责将运算结果保存到指定的寄存器内。 2、通用寄存器组功能实现 根据通用寄存器组的功能要求,一个只有四个16位寄存器的通用寄存器组的框图如下图所示: ⑴寄存器部分: 当reset为低电平时,将四个16位寄存器R0-R3复位为0;当寄存器的write和sel

为高电平时,在时钟信号clk的上升沿将D端的输入D[15-0]写入寄存器,然后送到寄存器的输出Q[15-0]。4个寄存器的允许写信号write和外部产生的目的寄存器写信号DRWr 直接相连。每个寄存器还有另一个选择信号sel,它决定哪一个寄存器进行写操作。4个寄存器的选择信号分别和2-4译码器产生的sel00、sel01、sel10、sel11相连。只有当一个寄存器被选中(sel为高电平时),才允许对该寄存器进行写操作。 ⑵ 2-4译码器: 2-4译码器的输入sel[1-0]接DR[1-0],2-4译码器对2位的输入信号sel[1-0]进行2-4译码,产生4个输出sel00、sel01、sel10、sel11,分别送往4个寄存器R0、R1、R2和R3的选择端sel。 ⑶ 4选1多路器 4选1多路选择器1从4个寄存器R0、R1、R2和R3的输出Q[15-0]选择1路送到DR_data[15-0],给算术逻辑单元提供目的操作数;选择信号sel[1-0]接DR[1-0]。4选1多路选择器2从4个寄存器R0、R1、R2和R3的输出Q[15-0]选择1路送到SR_data[15-0],给算术逻辑单元提供源操作数;选择信号sel[1-0]接SR[1-0]。 三、实验要求: 1、实验设计目标 设计一个通用寄存器组满足以下要求: (1)通用寄存器组中有4个16位的寄存器。 (2)当复位信号reset=0时,将通用寄存器组中的4个寄存器清零。 (3)通用寄存器组中有1个写入信号,当DRWr=1时,在时钟clk的上升沿将数据总线上的数写入DR[1-0]指定的寄存器。 (4)通用寄存器组中有两个读出端口,一个对应算术逻辑单元的目的操作数DR,另一个对应算术逻辑单元的源操作数SR。DR[1-0]选择目的操作数;SR[1-0]选择源操作数。 (5)设计要求层次设计。底层的设计实体有三个:16位寄存器,具有复位功能和允许写功能;一个2-4译码器,对应寄存器写选择;一个4选1多路开关,负责选择寄存器的读出。顶层设计构成一个完整的通用寄存器组。 2、顶层设计实体的引脚要求 引脚要求对应关系如下: (1)clk对应试验台上的时钟(单脉冲)。 (2)reset对应实验台上的CPU复位信号CPU_RST。 (3)SR[1-0]对应实验台开关SA1,SA0。

实验二通用寄存器实验 一、实验目的 1.熟悉通用寄存器的数据通路。 2.了解通用寄存器的构成和运用。 二、实验要求 掌握通用寄存器R3~R0的读写操作。 三、实验原理 实验中所用的通用寄存器数据通路如下图所示。由四片8位字长的74LS574组成R1 R0(CX)、R3 R2(DX)通用寄存器组。图中X2 X1 X0定义输出选通使能,SI、XP控制位为源选通控制。RWR为寄存器数据写入使能,DI、OP为目的寄存器写选通。DRCK信号为寄存器组打入脉冲,上升沿有效。准双向I/O输入输出端口用于置数操作,经2片74LS245三态门与数据总线相连。 图2-3-3 通用寄存器数据通路

四、实验内容 1. 实验连线 K23~K0置“1”,灭M23~M0控位显示灯。然后按下表要求“搭接”部件控制电路。 连线 信号孔 接入孔 作用 有效电平 1 DRCK CLOCK 单元手动实验状态的时钟来源 上升沿打入 2 X2 K10(M10) 源部件译码输入端X2 三八译码 八中选一 低电平有效 3 X1 K9(M9) 源部件译码输入端X1 4 X0 K8(M8) 源部件译码输入端X0 5 XP K7(M7) 源部件奇偶标志:0=偶寻址,1=奇寻址 6 SI K20(M20) 源寄存器地址:0=CX ,1=DX 7 RWR K18(M18) 通用寄存器写使能 低电平有效 8 DI K17(M17) 目标寄存器地址:0=CX ,1=DX 9 OP K16(M16) 目标部件奇偶标志:0=偶寻址,1=奇寻址 2. 寄存器的读写操作 ① 目的通路 当RWR=0时,由DI 、OP 编码产生目的寄存器地址,详见下表。 通用寄存器“手动/搭接”目的编码 目标使能 通用寄存器目的编址 功能说明 RW(K18) DI(K17) OP(K16) T 0 0 0 ↑ R0写 0 0 1 ↑ R1写 0 1 0 ↑ R2写 0 1 1 ↑ R3写 ② 通用寄存器的写入 通过“I/O 输入输出单元”向R0、R1寄存器分别置数27h 、37h ,操作步骤如下: 通过“I/O 输入输出单元”向R2、R3寄存器分别置数47h 、57h ,操作步骤如下: ③ 源通路 当X2~X0=001时,由SI 、XP 编码产生源寄存器,详见下表。 通用寄存器“手动/搭接”源编码 置数 I/O=XX01h 数据来源 I/O 单元 寄存器 R0=01h K10~K7=1000 按【单拍】按钮 置数 I/O=XX11h 寄存器 R1=11h 按【单拍】按钮 K18~K16=000 K18~K16=001 置数 I/O=XX21h 数据来源 I/O 单元 寄存器 R2=21h K10~K7=1000 按【单拍】按钮 置数 I/O=XX31h 寄存器 R3=31h 按【单拍】按钮 K18~K16=010 K18~K16=011

河南农业大学 计算机组成原理实验报告 题目简单机模型实验 学院信息与管理科学学院 专业班级计算机科学与技术2010级1班 学生姓名张子坡(1010101029) 指导教师郭玉峰 撰写日期:二○一二年六月五日

一、实验目的: 1.在掌握各部件的功能基础上,组成一个简单的计算机系统模型机; 2.了解微程序控制器是如何控制模型机运行的,掌握整机动态工作过程; 3定义五条机器指令,编写相应微程序并具体上机调试。 二、实验要求: 1.复习计算机组成的基本原理; 2.预习本实验的相关知识和内容 三、实验设备: EL-JY-II型计算机组成原理试验系统一套,排线若干。 四、模型机结构及工作原理: 模型机结构框图见实验书56页图6-1. 输出设备由底板上上的四个LED数码管及其译码、驱动电路构成,当D-G和W/R均为低电平时将数据结构的数据送入数据管显示注:本系统的数据总线为16位,指令、地址和程序计数器均为8位。当数据总线上的数据打入指令寄存器、地址寄存器和程序寄存器时,只有低8位有效。 在本实验我们学习读、写机器指令和运行机器指令的完整过程。在机器指令的执行过程中,CPU从内存中取出一条机器指令到执行结束为一个指令周期,指令由微指令组成的序列来完成,一条机器指令对应一段微程序。另外,读、写机器指令分别由相应的微程序段来完成。

为了向RAM中装入程序和数据,检查写入是否正确,并能启动程序执行,必须设计三个控制操作微程序。 存储器读操作(MRD):拨动清零开关CLR对地址、指令寄存器清零后,指令译码器输入CA1、CA2为“00”时,按“单步”键,可对RAM连续读操作。 存储器写操作(MWE):拨动清零开关CLR对地址、指令寄存器清零后,指令译码器输入CA1、CA2为“10”时,按“单步”键,可对RAM连续写操作。 启动程序(RUN):拨动开关CLR对地址、指令寄存器清零后,指令译码器输入CA1、CA2为“11”时,按“单步”键,即可转入第01号“取指”微指令,启动程序运行。 注:CA1、CA2由控制总线的E4、E5给出。键盘操作方式有监控程序直接对E4、E5赋值,无需接线。开关方式时可将E4、E5接至控制开关CA1、CA2,由开关控制。 五、实验内容、分析及参考代码: 生成的下一条微地址 UA5 UA0 MS5 MS0 微地址

寄 存 器 实 验 报 系别:信息技术系 专业:计算机科学与技术 班级:计科142 姓名:康道顺 学号:201401014233

实验一寄存器实验 一、实验目的 (1)了解模型机中A, W寄存器结构、工作原理及其控制方法。 (2)了解模型机中寄存器组R0..R3结构、工作原理及其控制方法。 二、实验要求 (1)A、W寄存器:利用COP2000实验仪上的K16..K23开关做为DBUS的数据, 其它开关做为控制信号,将数据写入寄存器A,W。 (2)R0、R1、R2、R3寄存器实验:利用COP2000实验仪上的K16..K23开关 做为DBUS的数据,其它开关做为控制信号,对数据寄存器组R0..R3进 行读写。 三、实验说明 寄存器的作用是用于保存数据的,因为我们的模型机是8位的,因此在本模型机中大部寄存器是8位的,标志位寄存器(Cy, Z)是二位的。 COP2000用74HC574来构成寄存器。74HC574的功能如下: 注意: 1. 在CLK的上升沿将输入端的数据打入到8个触发器中

74HC574工作波形图 四、实验原理 实验1:A,W寄存器实验 (1)原理图 寄存器A原理图 寄存器W原理图(2)工作波形图

寄存器A,W写工作波形图 (4)实验数据 例:将55H写入A寄存器 二进制开关K23-K16用于DBUS[7:0]的数据输入,置数据55H。 置控制信号为: 按住CLOCK脉冲键,CLOCK由高变低,这时寄存器A的黄色选择指示灯亮,表明选择A寄存器。放开CLOCK键,CLOCK由低变高,产生一个上升沿,数据55H 被写入A寄存器。 a)将66H写入W寄存器 。。。。。。 实验2:R0,R1,R2,R3寄存器实验 (1)原理图

实验十一移位寄存器及其应用 一、实验目的: 1、熟悉中规模4位双向移位寄存器的逻辑功能并掌握其使用方法; 2、熟悉移位寄存器的应用典例一——构成串行累加器和环形计数器。 二、实验原理: 1、移位寄存器是一种具有移位功能的寄存器,是指寄存器中所存的代码能够在移位脉冲的作用下依次左移或右移。既能左移又能右移的移位寄存器称为双向移位寄存器,只需要改变左、右移的控制信号便可实现双向移位。根据存取信息的方式不同移位寄存器可分为:串入串出、串入并出、并入串出、并入并出四种形式。 本实验选用的4位双向通用移位寄存器,型号为74LS194或CC40194,两者功能相同, S L为左移串行输入端;S1、S0为操作模式控制端;CR为异步清零端;CP为时钟脉冲输入端。 74LS194有5种不同操作模式:并行送数寄存,右移(方向由Q3至Q0),左移(方向由Q0至Q3),保持及清零。S1、S0和CR 端的控制作用如表11-1所示。表11-1

2、移位寄存器的应用很广,可构成移位寄存器型计数器;顺序脉冲发生器;串行累加器;可用作数据转换,即把串行数据转换为并行数据,或把并行数据转换为串行数据等。本实验主要研究移位寄存器用作环形计数器和串行累加器的线路连接及其原理。 (1)环形计数器 把移位寄存器的输出反馈到它的串行输入端,就可以进行循环移位,如图11-2所示,把输出端Q3和右移串行输入端S R相连接,设初始状态Q3Q2Q1Q0=1000,则在时钟脉冲的作用下Q3Q2Q1Q0将依次变为0100、0010、0001、1000-----,可见它是一个具有四个有效状态的计数器,这种类型的计数器通常称为环形计数器。图11-2电路可以由各个输出端输出在时间上有先后顺序的脉冲,因此也可作为顺序脉冲发生器。 (2)串行累加器 累加器是由移位寄存器和全加器组成的一种求和电路,它的功能是将本身寄存的数和另一个输入的数相加,并存放在累加器中。 图11-2 图11-3是由两个右向移位寄存器、一个全加器和一个进位触发器组成的串行累加器。 设开始时,被加数A=A N-1.....A O和加数B=B N-1......B O已分别存入N+1位累加数移位寄存器和加数移位寄存器。再设进位触发器D已被清零。 在第一个CP脉冲到来之前,全加器各输入、输出端的情况为:A N=A0,B N=B0,C N-1=0,S N=A0+B0+0=S0,C N=C0。 当第一个CP脉冲到来后,S0存入累加和移位寄存器的最高位,C0存入进位触发器D端,且两个移位寄存器中的内容都向右移动一位。全加器输出为S N=A1+B1+C0=S1,C N=C1。