1.集成电路重点知识复习点

1.芯片制作过程中主要的工艺有哪些?

主要的三项工艺:薄膜制备工艺、光刻/图形转移工艺、掺杂工艺

薄膜制备工艺:在晶圆表面生长或淀积数层材质不同,厚度不同的膜层,如器件工作区的外延层,绝缘介质层,金属层等。该工艺通过常用方法有:外延生长,氧化,淀积。

图形转移工艺:包括掩膜版的制作,涂光刻胶,曝光(光刻),显影,烘干,刻蚀。电路结构以图形的形式制作在光刻掩膜版上。然后通过图形转换工艺转移精确转移到硅晶片上。

掺杂工艺:包括扩散工艺和离子注入工艺。各种杂质按照设计要求掺杂到晶圆上,形成晶体管的源漏端以及欧姆接触等。

2.PN结形成的过程是什么?

在纯净的本增半导体中少量掺杂施主杂质,如磷,取代硅原子,就形成了N型半导体。参与导电的主要是带负电的电子,电子为多数载流子,又称多子。空穴为少数载流子,又称少子。

在纯净的本增半导体中少量掺杂受主杂质,如硼,取代硅原子,就形成了P型半导体。因为参与导电的主要是带正电的空穴,空穴为多子。

当P型半导体和N型半导体放在一起之后,多子和少子从浓度高的区域向浓度低的区域扩散,P区留下的不能移动的负离子和N区留下的不能移动的正离子在半导体交界面形成了一个很薄的空间电荷区,又称耗尽层。这就是PN结。

PN结有内电场,由N区指向P区,内电场阻止多子的扩散运动,促使少子的漂移运动。最终PN结达到动态平衡。

PN结具有单向导电性,当外加正向电压(P区接正电压)时,PN结处于导通状态,结电阻很小。当外加负向电压(N区接正电压)时,PN结处于截止状态,结电阻很大。当反向电压加到一定程度,PN结会击穿二损坏。

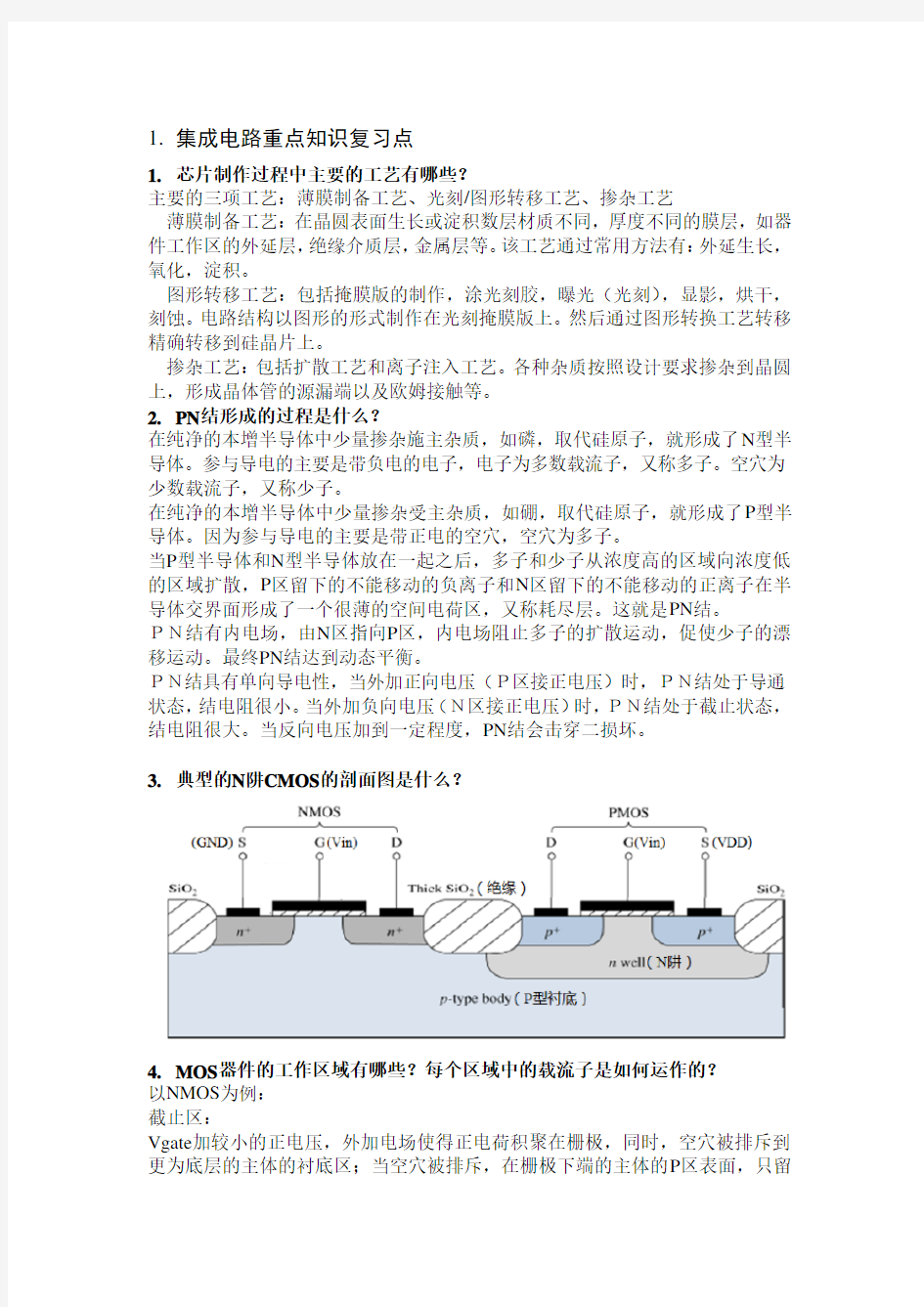

3.典型的N阱CMOS的剖面图是什么?

4.MOS器件的工作区域有哪些?每个区域中的载流子是如何运作的?

以NMOS为例:

截止区:

Vgate加较小的正电压,外加电场使得正电荷积聚在栅极,同时,空穴被排斥到更为底层的主体的衬底区;当空穴被排斥,在栅极下端的主体的P区表面,只留

下带负电的不可移动的离子,耗尽区在栅极下方形成;

Vgate进一步加大,更多衬底的少子被吸引到表面,当Vgs=VT时,表面将产生足够的电子,使得主体表面形成一层很薄的N型区,此N型区域中,电子的浓度大于空穴的浓度。这个过程叫做表面反型(surface inversion);

Vgate>Vth,栅氧下的薄反型层中产生更多的电子,这些电子是从重掺杂的n源区拉入到反型层中;源区和漏区之间形成一个连续的n型沟道。

线性区(三极管区):

假定源极source接地,漏极电压Vdd。在连续的n型沟道中,电子从源极向漏极移动,形成电流。

饱和区:

随着V DS增加,感应导电沟道向源极缩小,当V DS>(V GS-V TH),反型层将在x?L 处终止,导电沟道不再连续,I D相对恒定,发生“夹断”(pinch-off)现象。PMOS请自行总结。

5.什么是体效应?

没有特殊说明是,衬底接地,和源极有相同的电势。如果衬底电压小于源电压,V SB=V S?V B,耗尽层变宽。而阈值电压是耗尽层电荷总数的函数,耗尽层变宽,发生反型层所需要的电荷增加,则Vth增加。这种体电压(相对于源电压)的变化影响阈值电压的效应成为体效应。

6.什么是阈值电压?

开始形成反型层时,所需要的Vgs的电压,用Vth表示。

Vt=V t0+γ(√|2?f+V SB|?√|2?f|), 其中

当V SB为0时,V t0=V t,即V t0是没有”体效应”下的阈值电压;

γ是体效应系数,γ=√2qN Aεsi

C ox (NMOS),γ=?√2qN Dεsi

C ox

(PMOS),C ox=εox

t ox

;

εox和t ox是氧化物的介电常数和厚度。

7.什么是沟道调制效应?

饱和区,会发生沟道夹断,如果V DS继续增加,实际的反型沟道长度逐渐减小。有效沟道长度L’实际是V DS的函数,导致漏极电流略有上升。这一效应称为“沟道长度调制效应”。重新修正饱和区的漏极电流公式有

I D=1

2

u n C ox

W

L

(V GS?V TH)2(1+λV DS)

其中,λ为沟道长度修正系数。沟道长度效应使得电流在饱和区出现非零斜率。

8.什么是跨导?

传输管在饱和区可以看成是一个受栅源电压Vgs控制电流源。为了便于分析,用跨导来形容电压转化电流的能力。对饱和区的电流公式求导,可以得到

i d=eI D

eV GS V GS+eI D

eV DS

V DS+eI D

eV Bs

V BS,

=g m V GS+

1

r ds

V DS+g mb V BS

其中的g m是传输管的小信号跨导,

g m=eI d

GS

=

1

u n C ox

W

(V GS?V TH)=

2I d

(GS TH)

=√2u n C ox

W

I D

9.MOS管的电容如何分配?

(1)交叠电容(overlap capacitance):此电容是线性的,与偏置电压无关,不会随电压的改变而改变,是固有电容。

(2)沟道电容(gate capacitance):栅极至沟道的沟道电容C GC,总电容是C ox WL eff,大小取决于工作区域和端口电压。沟道电容由三部分构成:C GCS=C GCD栅极-沟道电容,栅极-漏极电容=栅极-源极电容;C GCB栅极-衬底电容;

(3)扩散电容/结电容(diffusion/junction capacitance):C SB、C DB源极-衬底电容/漏极-衬底电容

(4)布线电容(routing capacitance):C SD源极-漏极电容(Pwell为绝缘材质,距离较远,此电容较小,通常忽略)

12.共漏极的输入电阻,输出电阻,增益?

13.共源极的输入电阻,输出电阻,增益?

G m=i0

v i

|v o=0=?g m

R i=v i

i

=∞

R o=v o

i o

|v i=0=R D∕∕r o

A v=v o

v i

|i o=0=?g m(R D∕∕r o)

若是带源极反馈的共源极,

14.如何由电路图确定静态式互补电路?静态式互补电路的特点是什么?

静态式互补电路由上拉网络(pullup)和下拉网络(pulldown)构成,特点是:(1)Pullup和Pulldown是对偶逻辑网络。

(2)Pullup工作时,Pulldown是截止的;Pulldown工作时,Pullup是截止的。(3)互补门实质上是反相的,用单独一级实现非反相的布尔函数是不可能的。

15.静态式互补电路中,传输管的尺寸如何定义?

原则:上拉网络的等效电路和下拉网络的传输速率要均等,因此要有等价的上拉电阻和下拉电阻。具体要根据所给条件分析。可参考例题。

2.例题

1.已知:V dd=5V,u n Cox = 50uA/V2, W=40um, L=1um,V th=1V,它的工艺跨导

系数是多少?计算出Vgs和Id,当Rd = 3kΩ,60kΩ,1.6MΩ时。

M1为二极管链接,因此Vds = Vgs. 此时无论负载电阻大小如何M1都工作在饱和区。如Rd = 3kΩ,则

如Rd = 60kΩ,则

如Rd = 1.6MΩ,则

解决此方程前,可以先假设Vgs = Vtn = 1V ,则有

代入电流方程,可以得到Vgs的大小为

2.下图的静态互补电路中,定义所有传输管的尺寸比,确保最差路径下的t PHL和

t PLH都等于左图所示的反相器。

对于上拉网络R

p

是任意两个PMOS导通之后的电阻,假设是M1和M4导通,并

且电阻相同,就得出2R

ds1=R

p

对于下拉网络,R n是任意三个NMOS导通之后的电阻,假设M8,M9和M10导

通,并且电阻相同,就得出3R

ds8=R

n

3.根据板图画出静态式互补电路,写出逻辑关系。

下拉网络:

逻辑关系式:

F=A +B ????????,Z=F +AB ?????????, Z=A +B

????????+AB ??????????????? 4. 判断以下条件下NMOS 的工作区域,已知u n C ox =400uA/V 2,V t?=0.7V : (1) V GS =3.3V ,V DS =3.3V (2) V GS =0V ,V DS =3.3V (3) V GS =2V ,V DS =2V (4) V GS =1.5V ,V DS =0.5V (5) V GS =2V ,V GS =?0.5V (6) V GS =3V ,V GS =?3V

(a )V gs =3.3V >V tn ,V ds >V gs -V tn ,所以在饱和区 (b )V gs (c )V gs >V tn ,V ds >V gs -V tn ,所以在饱和区 (d )V gs >V tn ,V ds (e )V gs =2V , V ds =-0.5V ,D 极和S 极交换位置后V gs =2.5V ,V ds =0.5V ,在三极管区。 (f )V gs =3V ,V ds =-3V ,D 极和S 极交换位置后V gs =6V ,V ds =3V ,在三极管区。 5. 已知CMOS 工艺,其中L min =0.8um ,t ox =15um ,u n =550cm 2/Vs ,V t?=0.7V 。 (1)计算NMOS 的C ox 和K n ′(C ox =εox /t ox ,εox =3.9×8.85×10?14F/cm ) (2)现用此工艺制作一个NMOS ,此NMOS 的W/L=16um/0.8um 。若要使此NMOS 工作在饱和区,并且DC 电流ID=100uA ,计算出此时的V o v ,V GS 和V GSmin (=V GS(sat))大小。 a )C ox =εox /t ox =15nm F/cm 108.853.9-14??=2.3-310?F/m 2 ,n K =ox n C μ=550cm 2/Vs ?2.3-310?F/m 2=1.27?10 -4 F/Vs b )I n = 21,n K L W V 2 ov 100μA= 21?1.27?10-14F/Vs ?8 .016V 2ov V ov =0.28v V gs =V ov +V th =0.98v V DSm in =V ov =0.28 6. 已知一个NMOS 传输管工作在饱和区,其V t?=1V ,k n =0.1 mA/V 2,λn =0/V 。若I d =0.2mA ,计算出NMOS 所需要的V GS 和最小V DS 。如果I d =0.8mA ,NMOS 所需要的V GS 和最小V DS 又是多少? I D =21 n K (V gs -V th )2 V th =1v n K =0.1mA/V 2 如果I D =0.2mA 0.2m= 2 1 ?0.1m ?(V gs -1)2 V gs =3V V DSm in =V gs -V th =2V 如果I D =0.8mA 0.8m= 2 1 ?0.1m ?(V gs -1)2 V gs =5V V DSm in =V gs -V th =4V 7. 由NMOS 构成的反相放大器,其负载电阻R d 为20 kΩ。对放大器进行DC 和AC 仿真,由DC 仿真结果得,R d 上的压降为2V ,V GS 为1.2V 。由AC 仿真结果得,小信号放大增益为-10V/V 。计算出此NMOS 的V t?大小。如果u n C ox =50uA/V 2,计算出NMOS 的尺寸比(W/L )。